Improved Design of a SiC MOSFET Gate Drive with Crosstalk Suppression Capability

Abstract

:1. Introduction

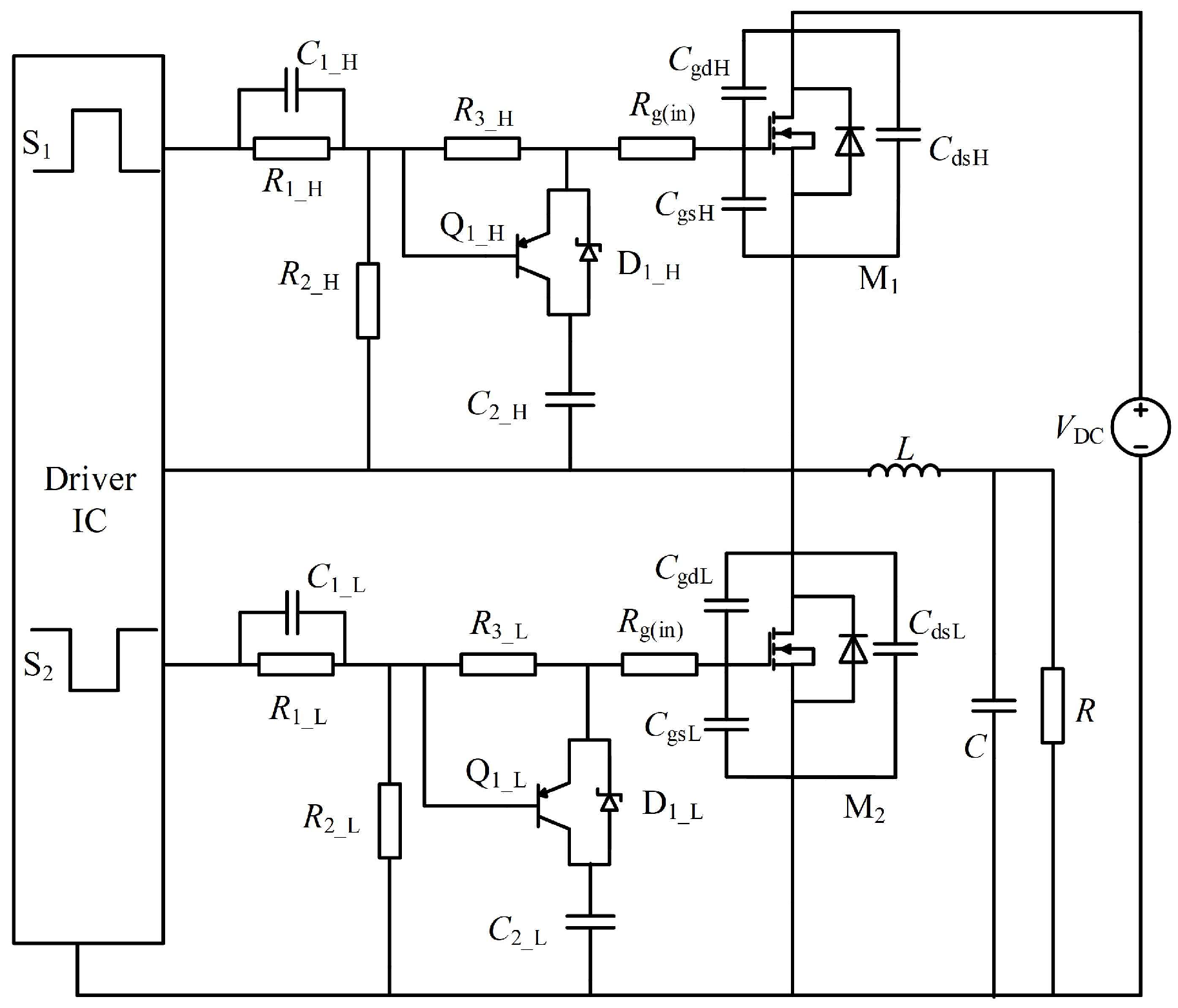

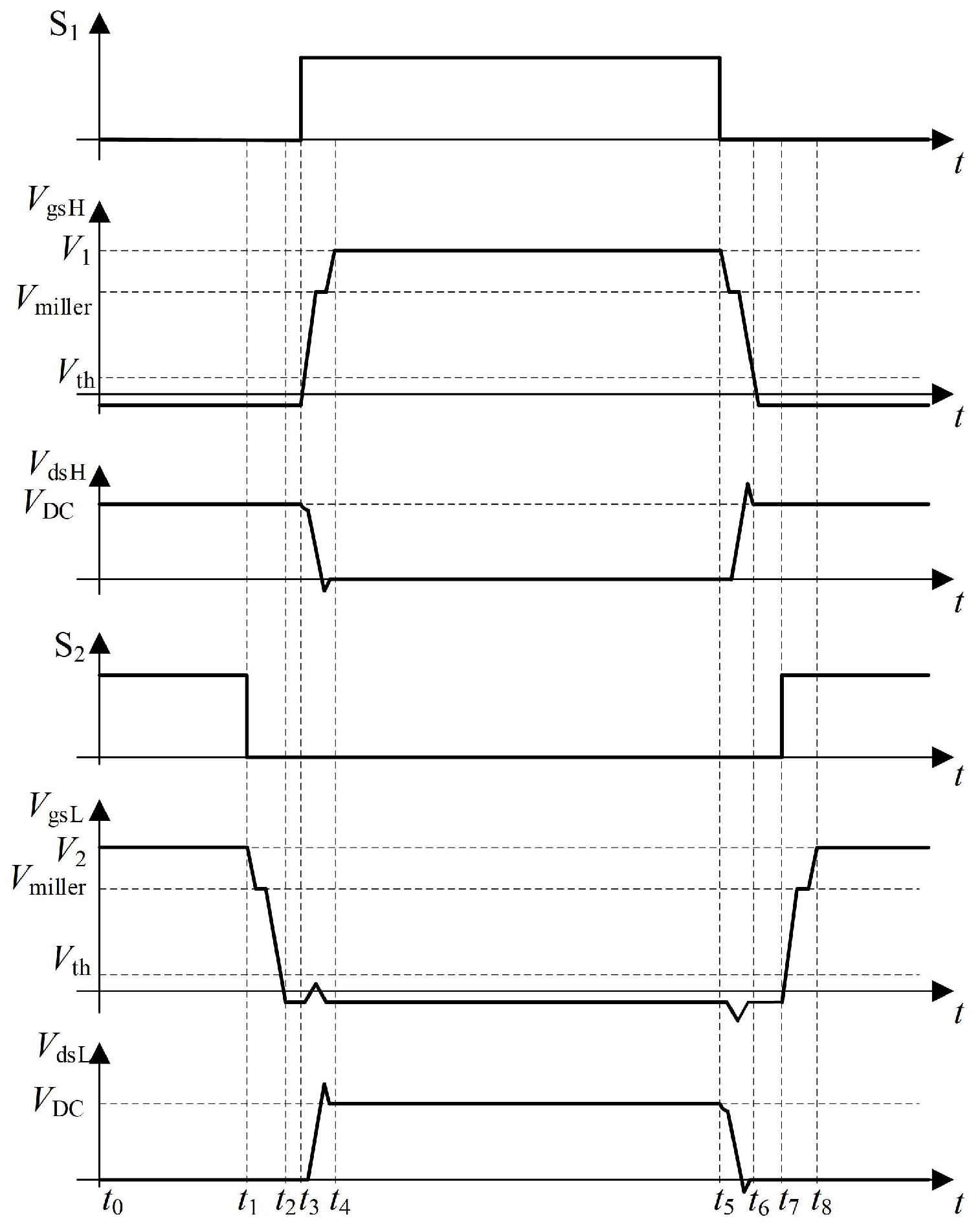

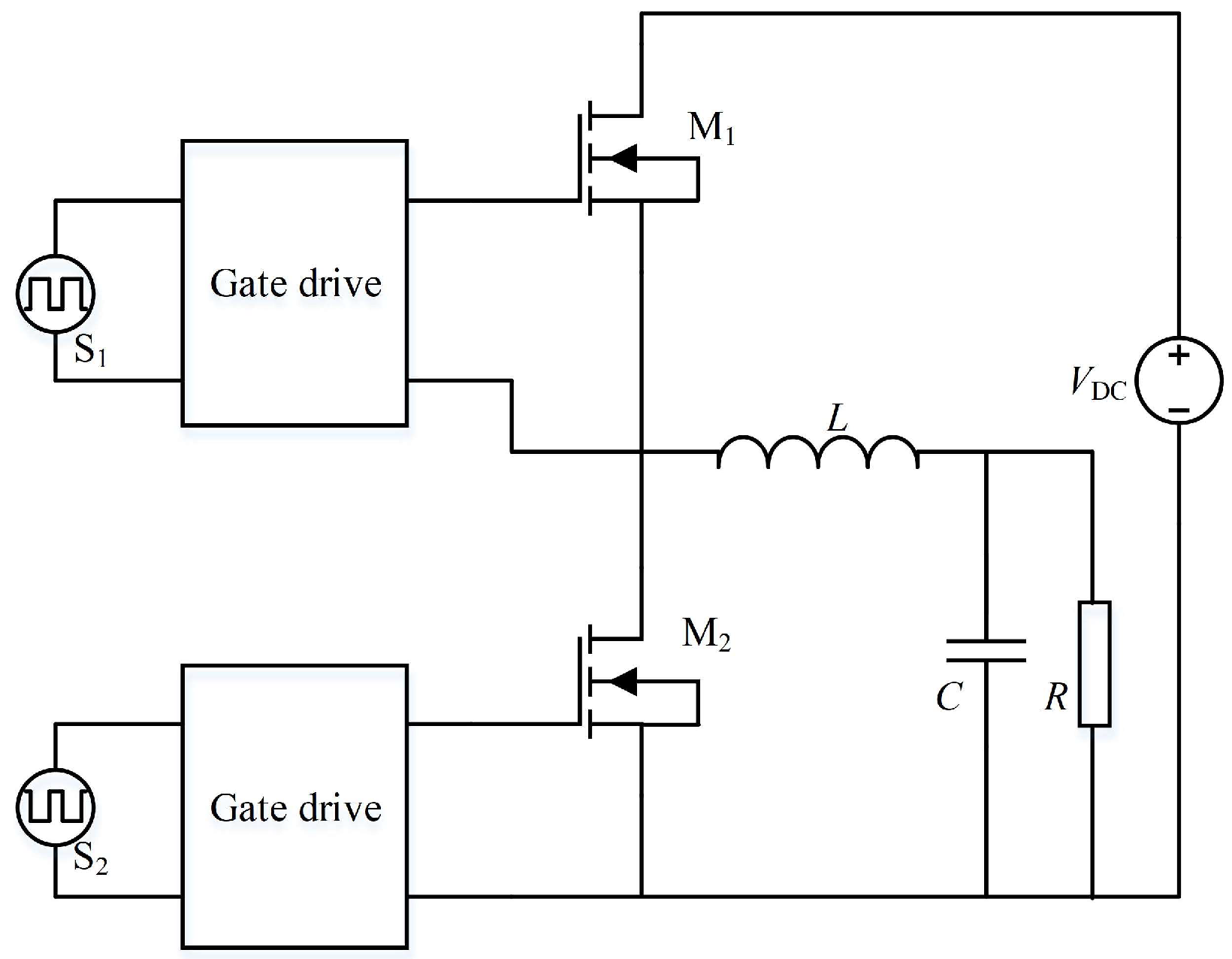

2. Analysis of the Production Mechanism of Crosstalk Voltage

3. Operation Principle of the Improved Crosstalk Suppress Gate Drive

3.1. Improved Gate Drive to Suppress Crosstalk

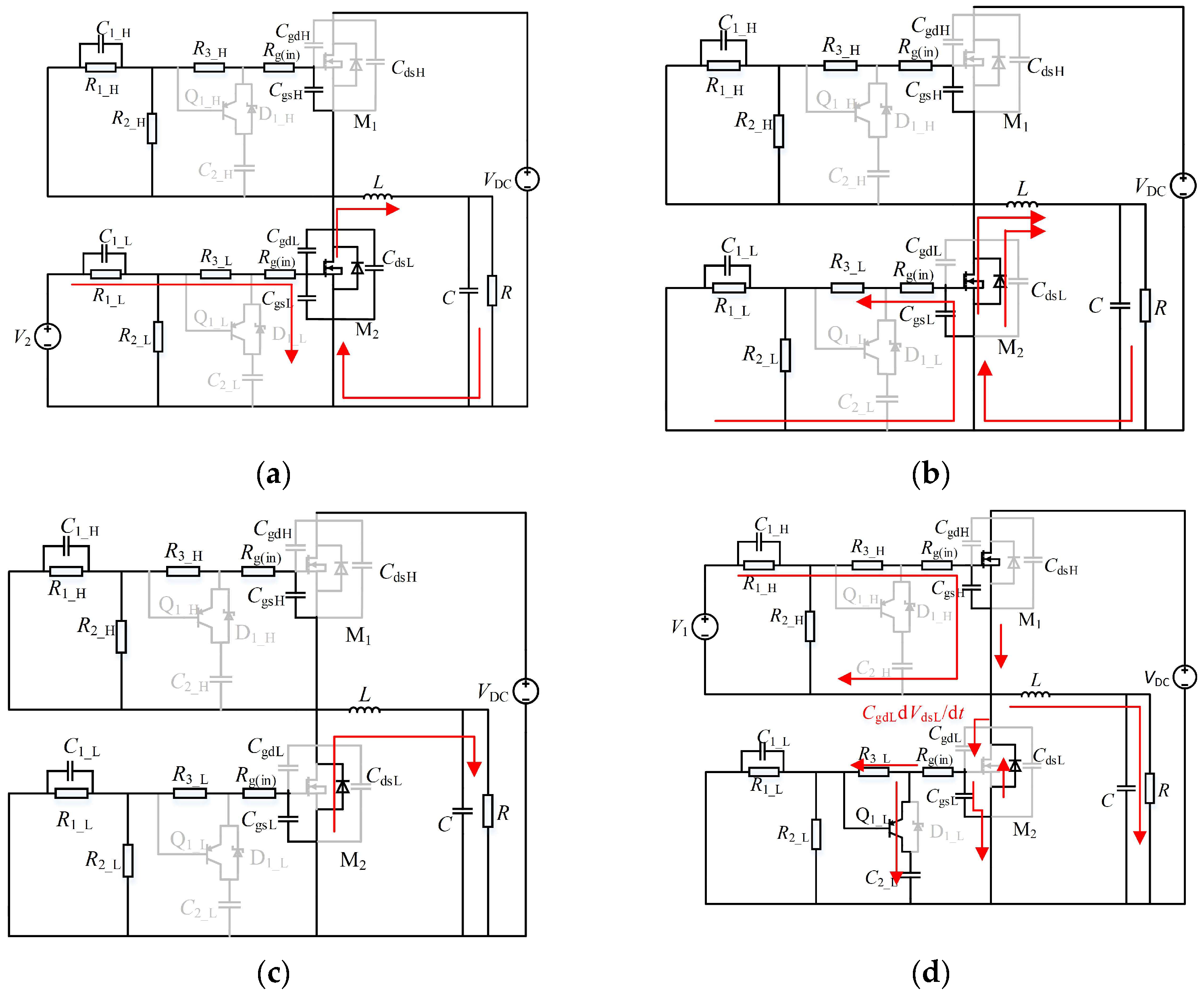

3.2. Analysis of Operation Principle of Improved Crosstalk Suppression Gate Drive

4. Parameter Design of Improved Crosstalk Suppress Gate Drive

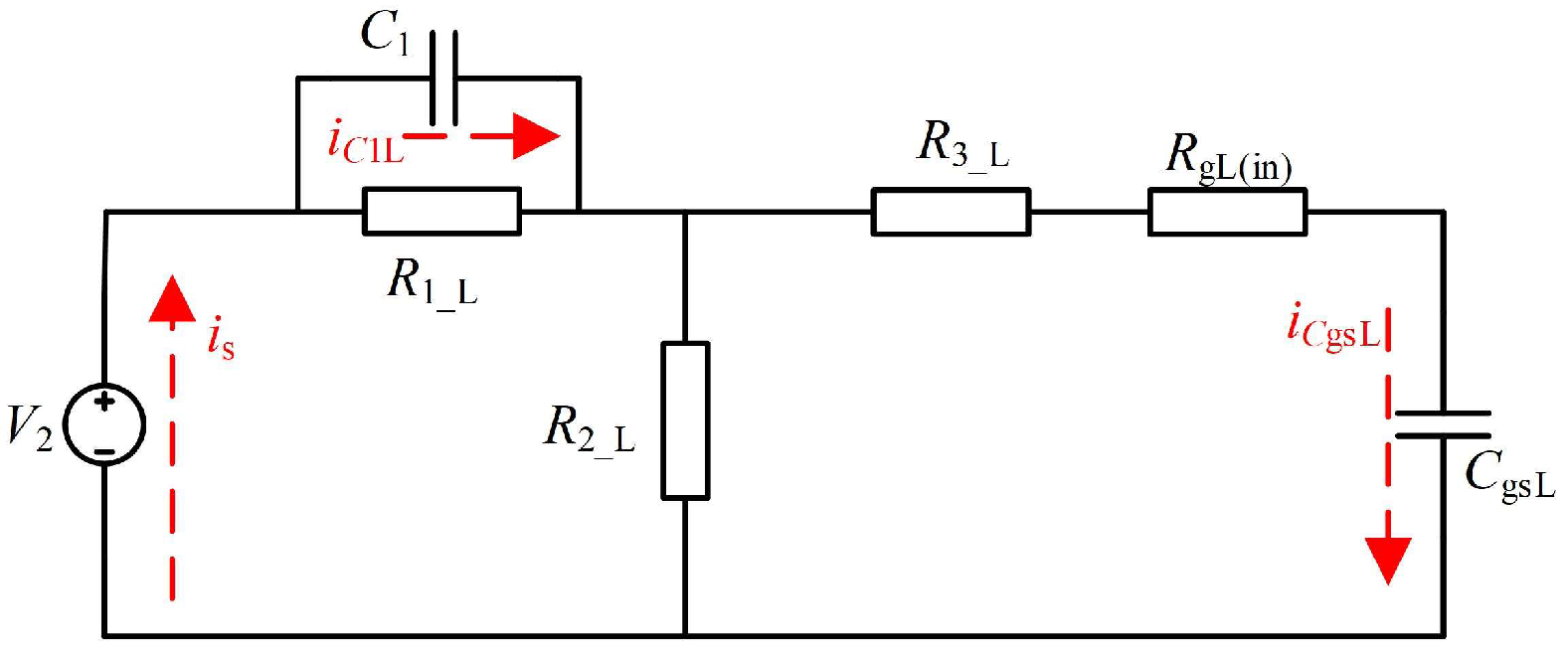

4.1. Pre-Charging Process

4.2. When the Auxiliary Branch Is Not Connected to the Gate Drive

4.3. When the Auxiliary Branch Is Connected to the Gate Drive

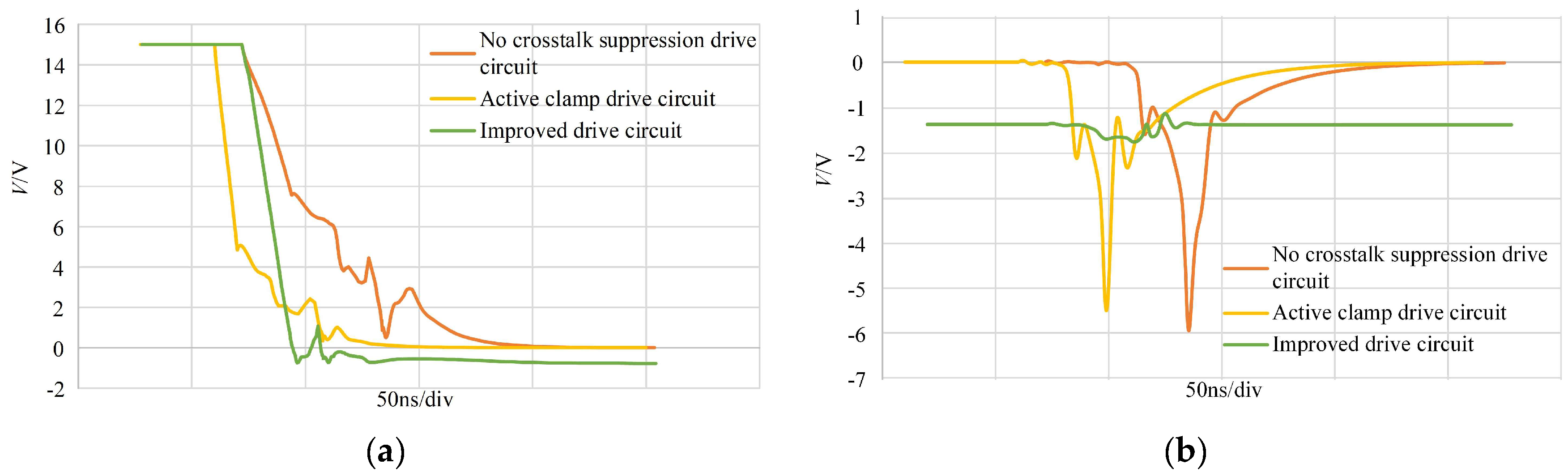

5. Simulation Verification of the Improved Crosstalk Suppression Gate Drive

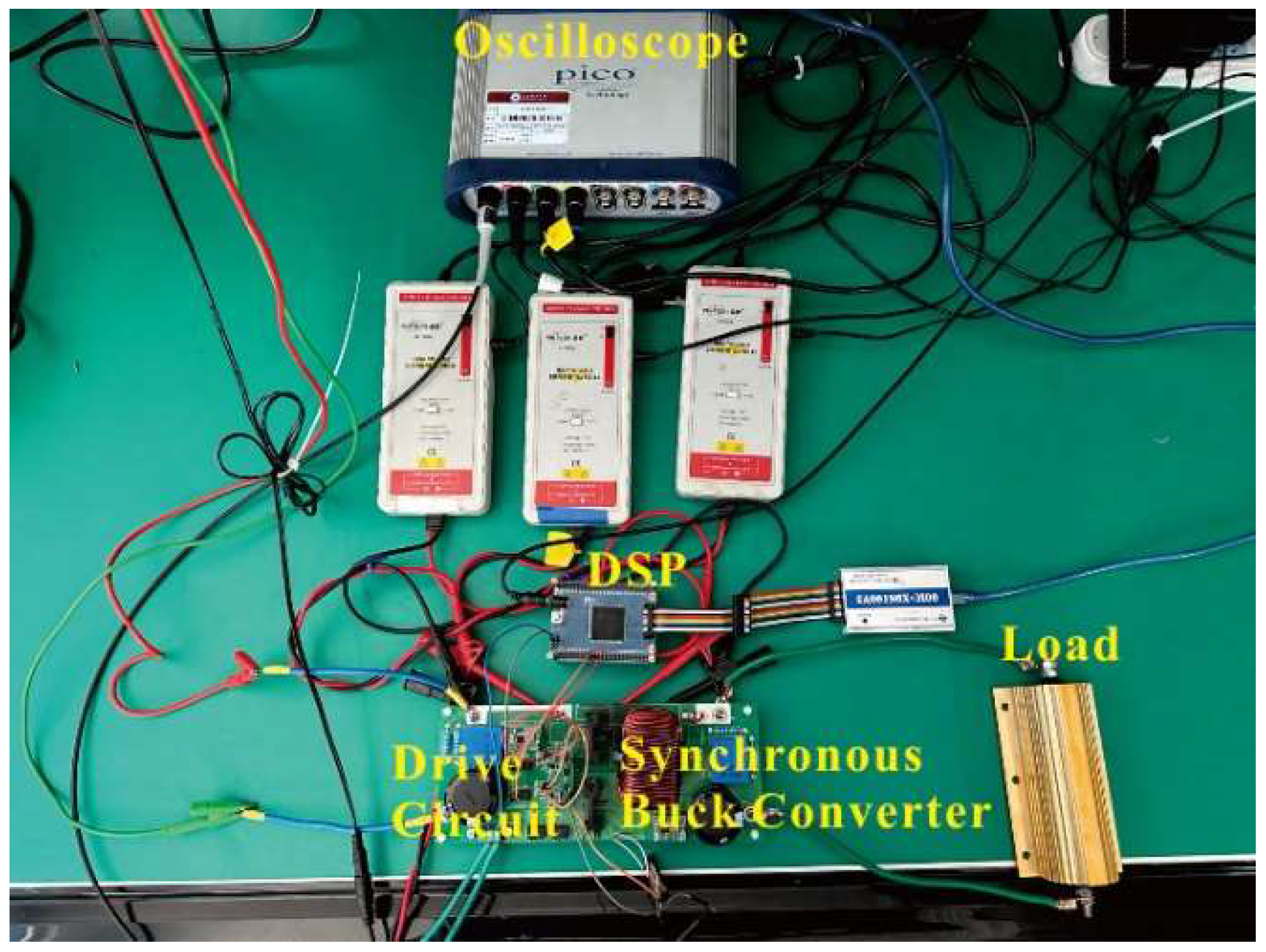

6. Experimental Verification of the Improved Crosstalk Suppression Gate Drive

7. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Wu, X.; Zaman, H.; Wu, P.; Jia, R.; Zhao, X.; Wu, X. A Quasi-Multilevel Gate Driver for Fast Switching and Crosstalk Suppression of SiC Devices. IEEE Access 2020, 8, 191403–191412. [Google Scholar]

- Zhang, B.; Wang, S. Miller Capacitance Cancellation to Improve SiC MOSFET’s Performance in a Phase-Leg Configuration. IEEE Trans. Power Electron. 2021, 36, 14195–14206. [Google Scholar] [CrossRef]

- Shao, T.; Zheng, T.Q.; Li, H.; Liu, J.; Li, Z.; Huang, B.; Qiu, Z. The Active Gate Drive Based on Negative Feedback Mechanism for Fast Switching and Crosstalk Suppression of SiC Devices. IEEE Trans. Power Electron. 2022, 37, 6739–6754. [Google Scholar] [CrossRef]

- Li, B.; Zhang, G.; Li, C.; Wang, G.; Liu, S.; Xu, D. Crosstalk Suppression Method for GaN-Based Bridge Configuration Using Negative Voltage Self-Recovery Gate Drive. IEEE Trans. Power Electron. 2022, 37, 4406–4418. [Google Scholar] [CrossRef]

- Huang, Y.; Zhang, J.; Wang, Z. A Resonant Auxiliary Drive Circuit for SiC MOSFET to Suppress Crosstalk. Trans. China Electrotech. Soc. 2022, 37, 3004–3015. [Google Scholar]

- Li, G.; Hang, L.; Tong, A.; Zeng, Q.; He, Y. The Driver Design of SiC MOSFET With Active Crosstalk Suppression. Proc. CSEE 2021, 41, 3915–3922. [Google Scholar]

- Li, H.; Huang, Z.; Liao, X. An Improved SiC MOSFET Gate Driver Design for Crosstalk Suppression in a Phase-Leg Configuration. Trans. China Electrotech. Soc. 2019, 34, 275–285. [Google Scholar]

- Li, H.; Jiang, Y.; Qiu, Z.; Shao, T.; Wang, Y. A Multi-step Active Gate Driver for Suppressing Crosstalk of SiC MOSFET. In Proceedings of the 2020 IEEE 9th International Power Electronics and Motion Control Conference (IPEMC2020-ECCE Asia), Nanjing, China, 29 November–2 December 2020; pp. 1868–1873. [Google Scholar]

- Lee, G.-Y.; Ju, C.-T.; Min, S.-S.; Kim, R.-Y. Gate Driver for Wide-Bandgap Power Semiconductors With Small Negative Spike and Switching Ringing in Zero-Voltage Switching Circuit. IEEE Access 2021, 9, 145774–145784. [Google Scholar] [CrossRef]

- Bi, C.; Ou, H.; Kang, Q.; Li, R.; Cheng, L. A Novel Driver Circuit on Crosstalk Suppression in SiC MOSFETs. In Proceedings of the 2021 IEEE International Symposium on Circuits and Systems (ISCAS), Daegu, Republic of Korea, 22–28 May 2021; pp. 1–5. [Google Scholar]

- Lu, Z.; Li, C.; Wu, H.; Li, W.; He, X.; Li, S. Design of Active SiC MOSFET Gate Driver for Crosstalk Suppression Considering Impedance Coordination between Gate Loop and Power Loop. In Proceedings of the 2019 IEEE Applied Power Electronics Conference and Exposition (APEC), Anaheim, CA, USA, 17–21 March 2019; pp. 986–990. [Google Scholar]

- Li, H.; Jiang, Y.; Qiu, Z.; Wang, Y.; Ding, Y. A Predictive Algorithm for Crosstalk Peaks of SiC MOSFET by Considering the Nonlinearity of Gate-Drain Capacitance. IEEE Trans. Power Electron. 2021, 36, 2823–2834. [Google Scholar] [CrossRef]

- Liang, M.; Li, Y.; Zheng, Q.; Zhao, H. Analysis for Crosstalk of SiC MOSFET with Different Packages in a Phase-Leg Configuration and a Low Gate Turn-Off Impedance Driver. Trans. China Electrotech. Soc. 2017, 32, 162–174. [Google Scholar]

- Zhang, Z.; Wang, F.; Tolbert, L.M.; Blalock, B.J. Active Gate Driver for Crosstalk Suppression of SiC Devices in a Phase-Leg Configuration. IEEE Trans. Power Electron. 2014, 29, 1986–1997. [Google Scholar] [CrossRef]

- Zhao, J.; Wu, L.; Li, Z.; Chen, Z.; Chen, G. Analysis and Suppression for Crosstalk in SiC MOSFET Turn-off Transient. In Proceedings of the 2020 IEEE 9th International Power Electronics and Motion Control Conference (IPEMC2020-ECCE Asia), Nanjing, China, 29 November–2 December 2020; pp. 1145–1150. [Google Scholar]

- Wang, J.; Chung, H.S.-H. A Novel RCD Level Shifter for Elimination of Spurious Turn-on in the Bridge-Leg Configuration. IEEE Trans. Power Electron. 2015, 30, 976–984. [Google Scholar] [CrossRef]

- Wang, P.; Zhang, L.; Lu, X.; Sun, H.; Wang, W.; Xu, D. An Improved Active Crosstalk Suppression Method for High-Speed SiC MOSFETs. IEEE Trans. Ind. Appl. 2019, 55, 7736–7744. [Google Scholar] [CrossRef]

- Gao, F.; Zhou, Q.; Wang, P.; Zhang, C. A Gate Driver of SiC MOSFET for Suppressing the Negative Voltage Spikes in a Bridge Circuit. IEEE Trans. Power Electron. 2017, 33, 2339–2353. [Google Scholar] [CrossRef]

- Zhang, B.; Wang, S. A crosstalk suppression technique for SiC MOSFETs in the bridge-leg configuration. In Proceedings of the 2020 IEEE Applied Power Electronics Conference and Exposition (APEC), New Orleans, LA, USA, 15–19 March 2020; pp. 1513–1520. [Google Scholar]

- Tang, B.H.-T.; Chung, H.S.-H.; Fan, J.W.-T.; Yeung, R.S.-C. Passive Resonant Level Shifter for Suppression of Crosstalk Effect and Reduction of Body-Diode Loss in SiC-Based Bridge Leg. In Proceedings of the 2018 IEEE Energy Conversion Congress and Exposition (ECCE), Portland, OR, USA, 23–27 September 2018; pp. 3510–3516. [Google Scholar]

- Xu, Y.; Duan, B.; Song, J.; Yang, D.; Zhang, C. A Novel Gate Driver of SiC MOSFET for Crosstalk Suppression in Bridge Configuration. In Proceedings of the 2020 Chinese Automation Congress (CAC), Shanghai, China, 6–8 November 2020; pp. 1173–1178. [Google Scholar]

- Li, G.; Tong, A.; Hang, L.; Zeng, Q.; Zhan, X.; Li, G.; He, Y.; Xie, X.; Shen, L.; Zhang, Y. A Level Shift Gate Driving Circuit of SiC MOSFET with Crosstalk Suppression Capability. In Proceedings of the 2020 IEEE Applied Power Electronics Conference and Exposition (APEC), New Orleans, LA, USA, 15–19 March 2020; pp. 1806–1812. [Google Scholar]

- Zhang, Z.; Wang, F.; Tolbert, L.M.; Blalock, B.J. A gate assist circuit for cross talk suppression of SiC devices in a phase-leg configuration. In Proceedings of the 2013 IEEE Energy Conversion Congress and Exposition, Denver, CO, USA, 15–19 September 2013; pp. 2536–2543. [Google Scholar]

- Zhang, B.; Xie, S.; Xu, J.; Qian, Q.; Zhang, Z.; Xu, K. A Magnetic Coupling Based Gate Driver for Crosstalk Suppression of SiC MOSFETs. IEEE Trans. Ind. Electron. 2017, 64, 9052–9063. [Google Scholar] [CrossRef]

| Parameters | Value |

|---|---|

| Gate-source capacitance Cgs | 1092 pF |

| Gate-drain capacitance Cgd | 8 pF |

| Drain-source capacitance Cds | 92 pF |

| Threshold voltage Vth | 3 V |

| Max negative gate-source voltage VMAX(neg) | −10 V |

| Internal gate resistance Rg(in) |

| Symbol | Value |

|---|---|

| C1_n | 100 pF |

| C2_n | 100 pF |

| R1_n | |

| R2_n | |

| R3_n |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hao, J.; Meng, R.; Guo, Z. Improved Design of a SiC MOSFET Gate Drive with Crosstalk Suppression Capability. Electronics 2024, 13, 2922. https://doi.org/10.3390/electronics13152922

Hao J, Meng R, Guo Z. Improved Design of a SiC MOSFET Gate Drive with Crosstalk Suppression Capability. Electronics. 2024; 13(15):2922. https://doi.org/10.3390/electronics13152922

Chicago/Turabian StyleHao, Jiade, Runquan Meng, and Zhuoyan Guo. 2024. "Improved Design of a SiC MOSFET Gate Drive with Crosstalk Suppression Capability" Electronics 13, no. 15: 2922. https://doi.org/10.3390/electronics13152922