Optimization Method of SiC MOSFET Switching Trajectory Based on Variable Current Drive

Abstract

1. Introduction

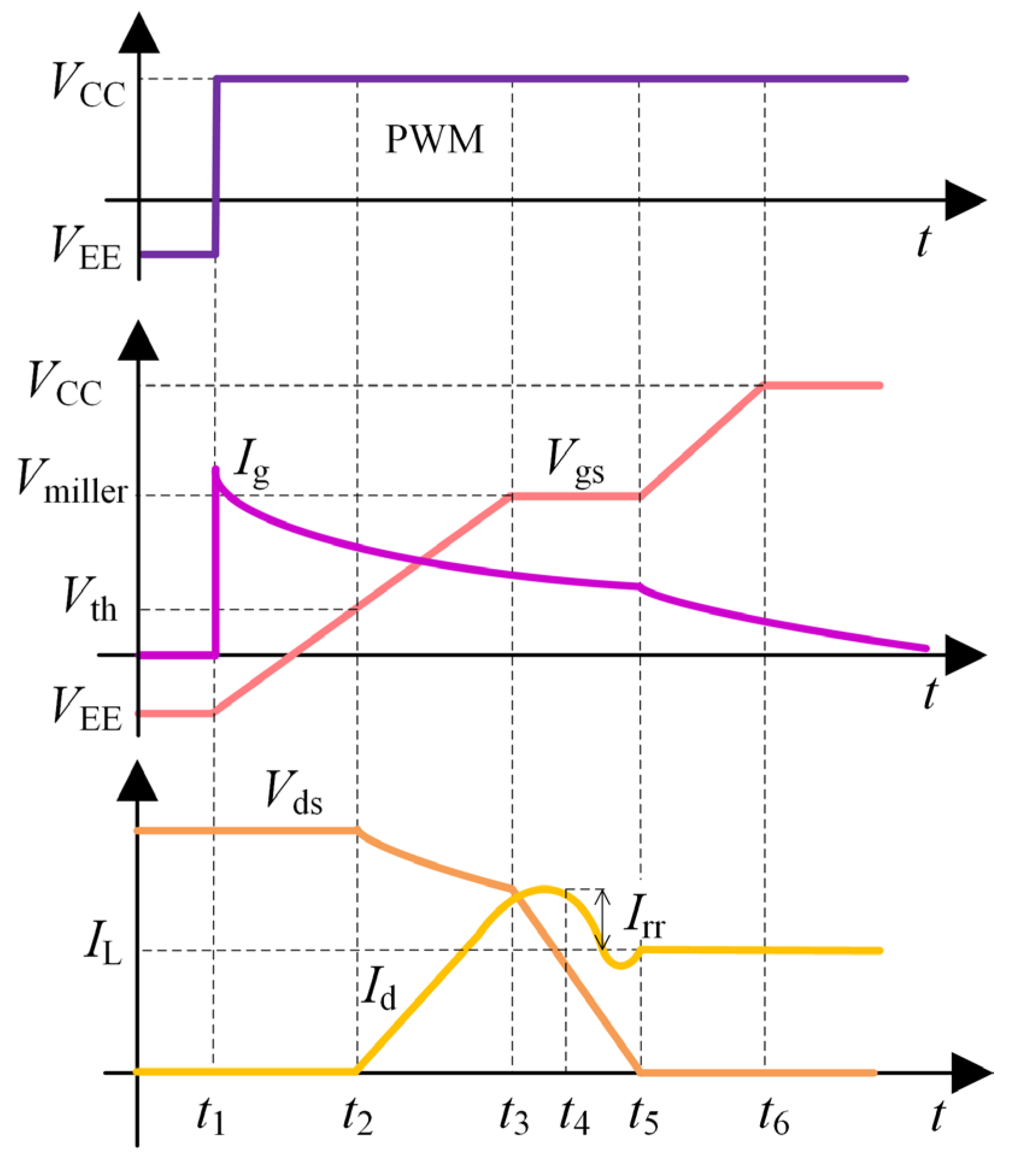

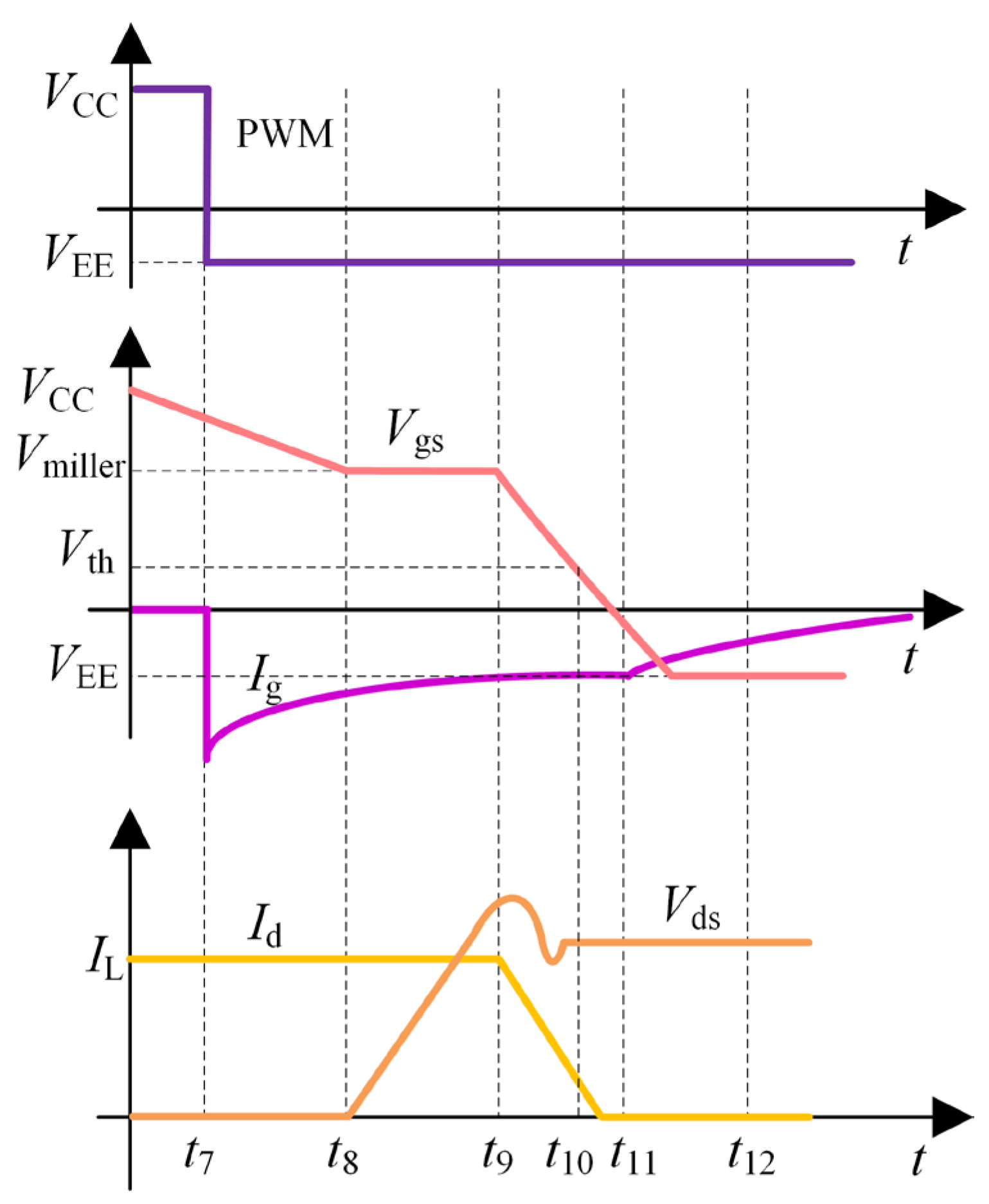

2. Overshoot Analysis of SiC MOSFET Switching Process

3. Oscillation Analysis of SiC MOSFET Switching Process

4. Active Gate Driver Circuit Analysis

5. Experimental Analysis

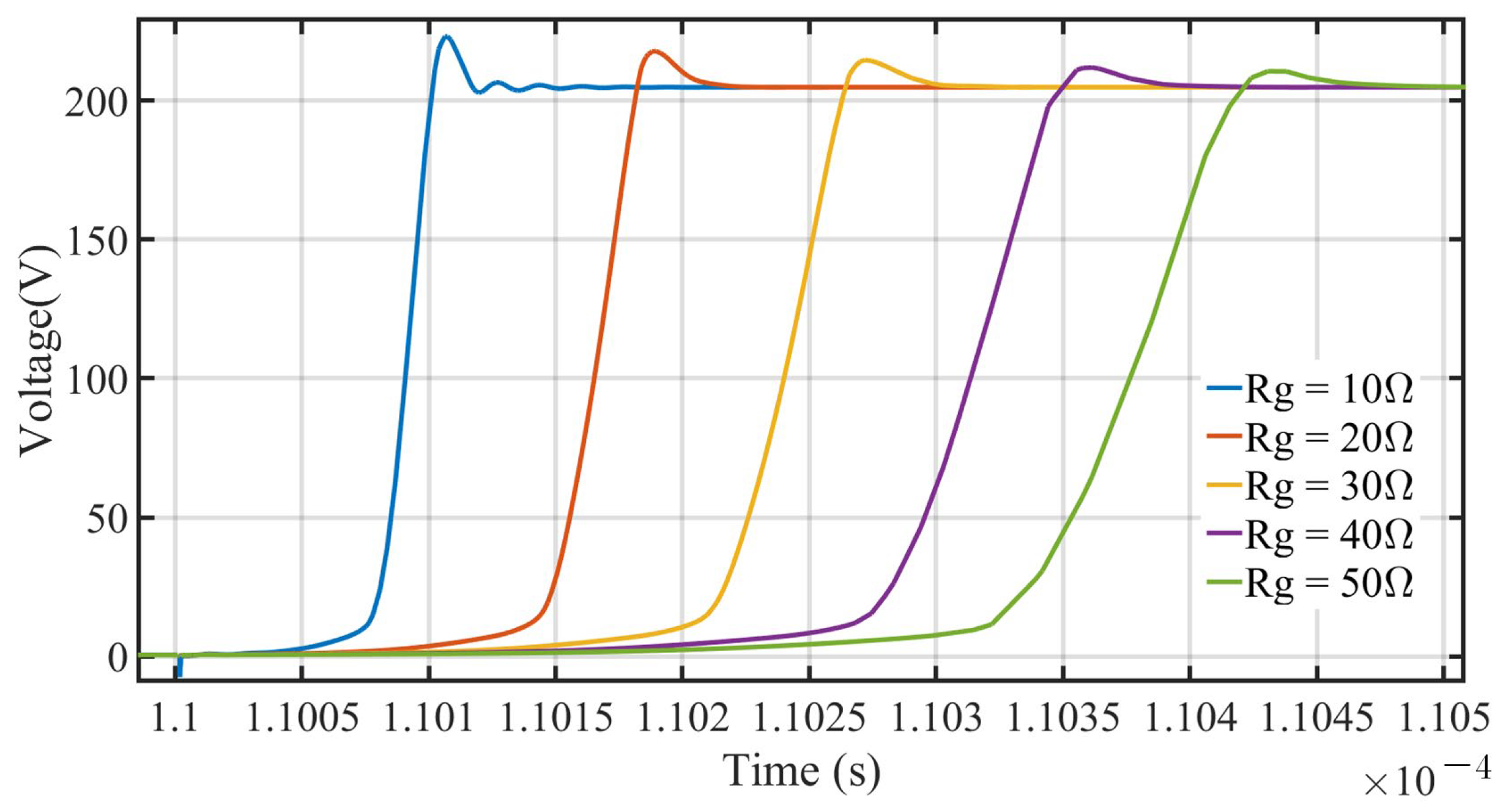

5.1. Experiments With Different Gate Resistors

5.2. Comparison of the Effects of AGD and CGD Circuits under Various Operational Conditions

5.3. Comparison of AGD Circuit and CGD Circuit Effects

5.4. Comparison of AGD Circuit and RCD Snubber Circuit Effects

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Sheng, K.; Renm, N.; Xu, H. A Recent Review on Silicon Carbide Power Devices Technologies. Proc. CSEE 2020, 40, 1741–1752. [Google Scholar]

- Zhang, L.; Yuan, X.; Wu, X.; Shi, C.; Zhang, J.; Zhang, Y. Performance evaluation of high-power SiC MOSFET modules in comparison to Si IGBT modules. IEEE Trans. Power Electron. 2019, 34, 1181–1196. [Google Scholar] [CrossRef]

- Yang, L.; Li, K.; Dai, J.; Corfield, M.; Harris, A.; Paciura, K.; O’Brien, J.; Johnson, C.M. Electrical performance and reliability characterization of a SiC MOSFET power module with embedded decoupling capacitors. IEEE Trans. Power Electron. 2018, 33, 10594–10601. [Google Scholar] [CrossRef]

- Zhao, S.; Zhao, X.; Dearien, A.; Wu, Y.; Zhao, Y.; Mantooth, H.A. An intelligent versatile model-based trajectory-optimized active gate driver for silicon carbide devices. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 8, 429–441. [Google Scholar] [CrossRef]

- Jacobs, K.; Heinig, S.; Johannesson, D.; Norrga, S.; Nee, H.P. Comparative evaluation of voltage source converters with silicon carbide semiconductor devices for high-voltage direct current transmission. IEEE Trans. Power Electron. 2021, 36, 8887–8906. [Google Scholar] [CrossRef]

- Sukhatme, Y.; Miryala, V.K.; Ganesan, P.; Hatua, K. Digitally controlled gate current source-based active gate driver for silicon carbide MOSFETs. IEEE Trans. Ind. Electron. 2020, 67, 10121–10133. [Google Scholar] [CrossRef]

- Lina, W.; Zeduo, Y.; Junming, C.; Wu, Z. Overview of Switching Transient Analytical Modeling of SiC MOSFET. Proc. CSEE 2023, 1–13. [Google Scholar]

- Xu, C.; Miao, Y. SiC MOSFET Active Gate Drive Circuit Based on Switching Transient Feedback. Energies 2024, 17, 1997. [Google Scholar] [CrossRef]

- Guo, R.; Yu, T.; Sun, G.; Liu, W. Optimization analysis and design of DC solid-state circuit breaker buffer circuit based on RCD and MOV. High Volt. Technol. 2019, 45, 2418–2424. [Google Scholar]

- Chen, J.; Zhang, W.J.; Shorten, A.; Yu, J.; Sasaki, M.; Kawashima, T.; Nishio, H.; Ng, W.T. A smart IGBT gate driver IC with temperature compensated collector current sensing. IEEE Trans. Power Electron. 2019, 34, 4613–4627. [Google Scholar] [CrossRef]

- Lobsiger, Y.; Kolar, J.W. Closed-loop IGBT gate drive featuring highly dynamic di/dt and dv/dt control. In Proceedings of the IEEE Energy Conversion Congress and Exposition (ECCE), Raleigh, NC, USA, 15–20 September 2012; pp. 4754–4761. [Google Scholar]

- Camacho, A.P.; Sala, V.; Ghorbani, H.; Martinez, J.L.R. A novel active gate driver for improving SiC MOSFET switching trajectory. IEEE Trans. Ind. Electron. 2017, 64, 9032–9042. [Google Scholar] [CrossRef]

- Paredes, A.; Fernandez, E.; Sala, V.; Ghorbani, H.; Romeral, L. Switching trajectory improvement of Sic MOSFET devices using a feedback gate driver. In Proceedings of the 2018 IEEE International Conference on Industrial Technology (ICIT), Lyon, France, 20–22 February 2018; pp. 847–852. [Google Scholar]

- Zhao, S.; Zhao, X.; Wei, Y.; Zhao, Y.; Mantooth, H.A. A review of switching slew rate control for silicon carbide devices using active gate drivers. IEEE J. Emerg. Sel. Topics Power Electron. 2021, 9, 4096–4114. [Google Scholar] [CrossRef]

- Cao, J.; Zhou, Z.-K.; Shi, Y.; Zhang, B. An integrated gate driver based on SiC MOSFETs adaptive multi-level control technique. IEEE Trans. Circuits Syst. I Reg. 2023, 70, 1805–1816. [Google Scholar] [CrossRef]

- Rødal, G.L.; Peftitsis, D. An adaptive current-source gate driver for high-voltage SiC MOSFETs. IEEE Trans. Power Electron. 2023, 38, 1732–1746. [Google Scholar] [CrossRef]

- Rødal, G.L.; Peftitsis, D. Gate-Drive Circuits for Adaptive Operation of SiC mosfets. IEEE Trans. Power Electron. 2024, 39, 8162–8186. [Google Scholar] [CrossRef]

- Ling, Y.; Zhao, Z.; Zhu, Y. A self-regulating gate driver for high-power IGBTs. IEEE Trans. Power Electron. 2021, 36, 3450–3461. [Google Scholar] [CrossRef]

- Chen, Y.; Guo, X.; Bu, X.; Hao, R.; You, X. Optimization method for turn-off trajectory of SiC MOSFET active driving circuit. J. Beijing Jiaotong Univ. 2023, 47, 126–135. [Google Scholar]

- Miryala, V.K.; Hatua, K. Low-cost analogue active gate driver for SiC MOSFET to enable operation in higher parasitic environment. IET Power Electron. 2020, 13, 463–474. [Google Scholar] [CrossRef]

- Li, X. An Active Gate Driver Circuit for Suppressing Voltage and Current Overshoots of SiC MOSFETs. J. Semicond. Technol. 2023, 48, 1006–1011+1029. [Google Scholar]

- Yang, C.; Pei, Y.; Wang, L.; Yu, L.; Zhang, F.; Ferreira, B. Overvoltage and oscillation suppression circuit with switching losses optimization and clamping energy feedback for SiC MOSFET. IEEE Trans. Power Electron. 2021, 36, 14207–14219. [Google Scholar] [CrossRef]

- Wu, Y.; Yin, S.; Li, H.; Ma, W. Impact of RC snubber on switch in go scillation damping of SiC MOSFET with analytical model. IEEE J. Emerg. 2020, 8, 163–178. [Google Scholar]

- Lee, S.; Chen, F.; Jahns, T.M.; Sarlioglu, B. Topological Equivalence of VSI and CSI Commutation Cells and Its Application to Switching Resonance Analysis and Damper Design. IEEE Trans. Transp. Electrif. 2024, 10, 1363–1376. [Google Scholar] [CrossRef]

- Wang, X.; Yang, X.; Liu, G. Investigation for Influence of Parasitic Inductances of Damping Resistors on Suppressing SiC MOSFET Switching Oscillation. In Proceedings of the 2023 IEEE 2nd International Power Electronics and Application Symposium (PEAS), Guangzhou, China, 10–13 November 2023; pp. 1819–1825. [Google Scholar]

- Li, J.; Yang, X.; Xu, M.; Wang, X.; Heng, K. A novel inductively coupled RLC damping circuits for eliminating switching oscillations of SiC MOSFET. IET Power Electron. 2023, 16, 1486–1498. [Google Scholar] [CrossRef]

- Wang, N.; Zhang, J. Review of Active Gate Driver for SiC MOSFET with Switching Trajectory Optimization. J. Electrotechnol. 2022, 37, 2523–2537. [Google Scholar]

- Peng, H.; Peng, H.; Yue, Q. Resonant gate driver with wide range adjustment of driving speed. In Proceedings of the 2021 IEEE Workshop on Wide Bandgap Power Devices and Applications in Asia (WiPDA Asia), Wuhan, China, 25–27 August 2021; pp. 371–375. [Google Scholar]

- Yue, Q.; Peng, H.; Tong, Q.; Kang, Y. A Novel Driving Current Control Approach in Enhanced Current-Source Gate Driver. IEEE Trans. Power Electron. 2023, 38, 10563–10568. [Google Scholar] [CrossRef]

- He, Y.; Wang, X.; Shao, S.; Zhang, J. Active gate driver for dynamic current balancing of parallel-connected SiC MOSFET. IEEE Trans. Power Electron. 2023, 38, 6116–6127. [Google Scholar] [CrossRef]

- Qiu, J. Modeling of SIC MOSFET And Research of Active Gate Drive Circuit. Master’s Thesis, Harbin Institute of Technology, Harbin, China, 2022. [Google Scholar]

| Stage | Programmatic | Overshoot | Switching Loss |

|---|---|---|---|

| Opening stage | CGD | 15 A | 1.859 mJ |

| AGD | 13.5 A | 1.448 mJ | |

| Closing stage | CGD | 180 V | 1.969 mJ |

| AGD | 160 V | 1.366 mJ |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lu, Y.; Yu, Y.; Huang, C.; Yan, J.; Wu, H. Optimization Method of SiC MOSFET Switching Trajectory Based on Variable Current Drive. Electronics 2024, 13, 3020. https://doi.org/10.3390/electronics13153020

Lu Y, Yu Y, Huang C, Yan J, Wu H. Optimization Method of SiC MOSFET Switching Trajectory Based on Variable Current Drive. Electronics. 2024; 13(15):3020. https://doi.org/10.3390/electronics13153020

Chicago/Turabian StyleLu, Yeqin, Yannan Yu, Changbin Huang, Jichi Yan, and Haoyuan Wu. 2024. "Optimization Method of SiC MOSFET Switching Trajectory Based on Variable Current Drive" Electronics 13, no. 15: 3020. https://doi.org/10.3390/electronics13153020

APA StyleLu, Y., Yu, Y., Huang, C., Yan, J., & Wu, H. (2024). Optimization Method of SiC MOSFET Switching Trajectory Based on Variable Current Drive. Electronics, 13(15), 3020. https://doi.org/10.3390/electronics13153020