Variable-Frequency Control for Totem-Pole Bridgeless Power Factor Correction Converter to Achieve Zero-Voltage Switching Without Zero-Crossing Detection Circuits

Abstract

:1. Introduction

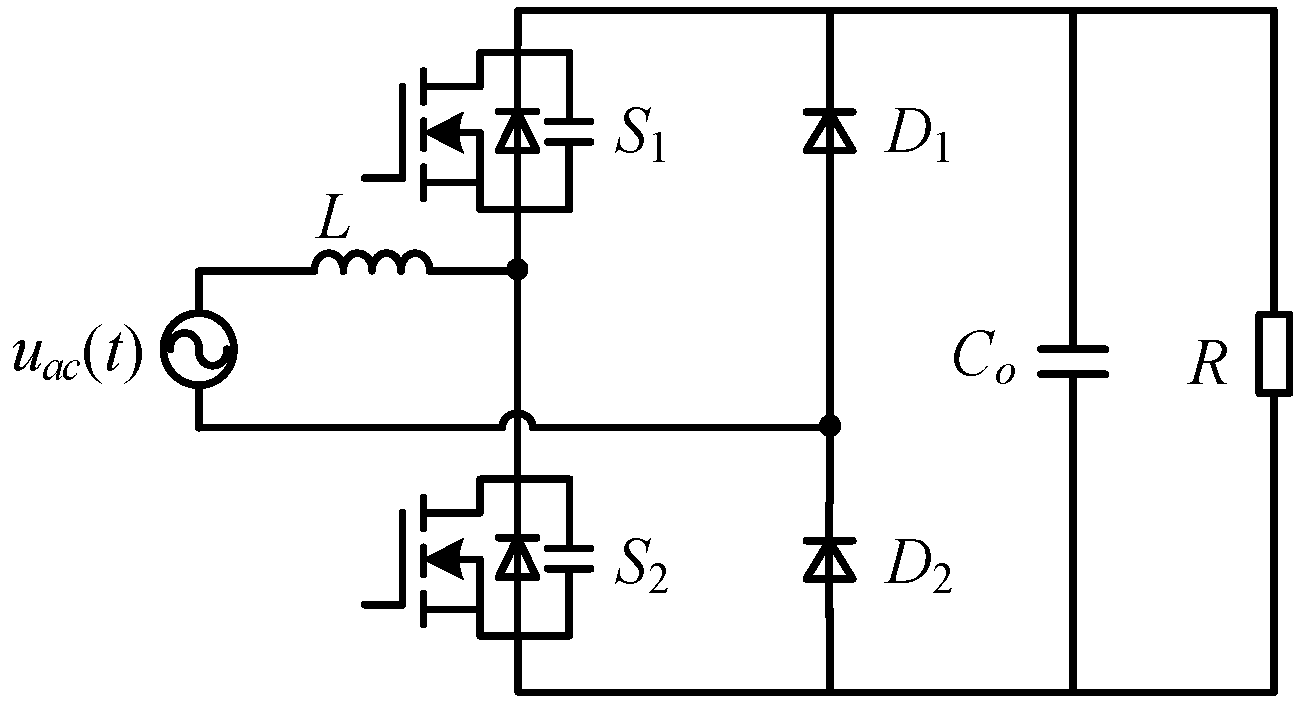

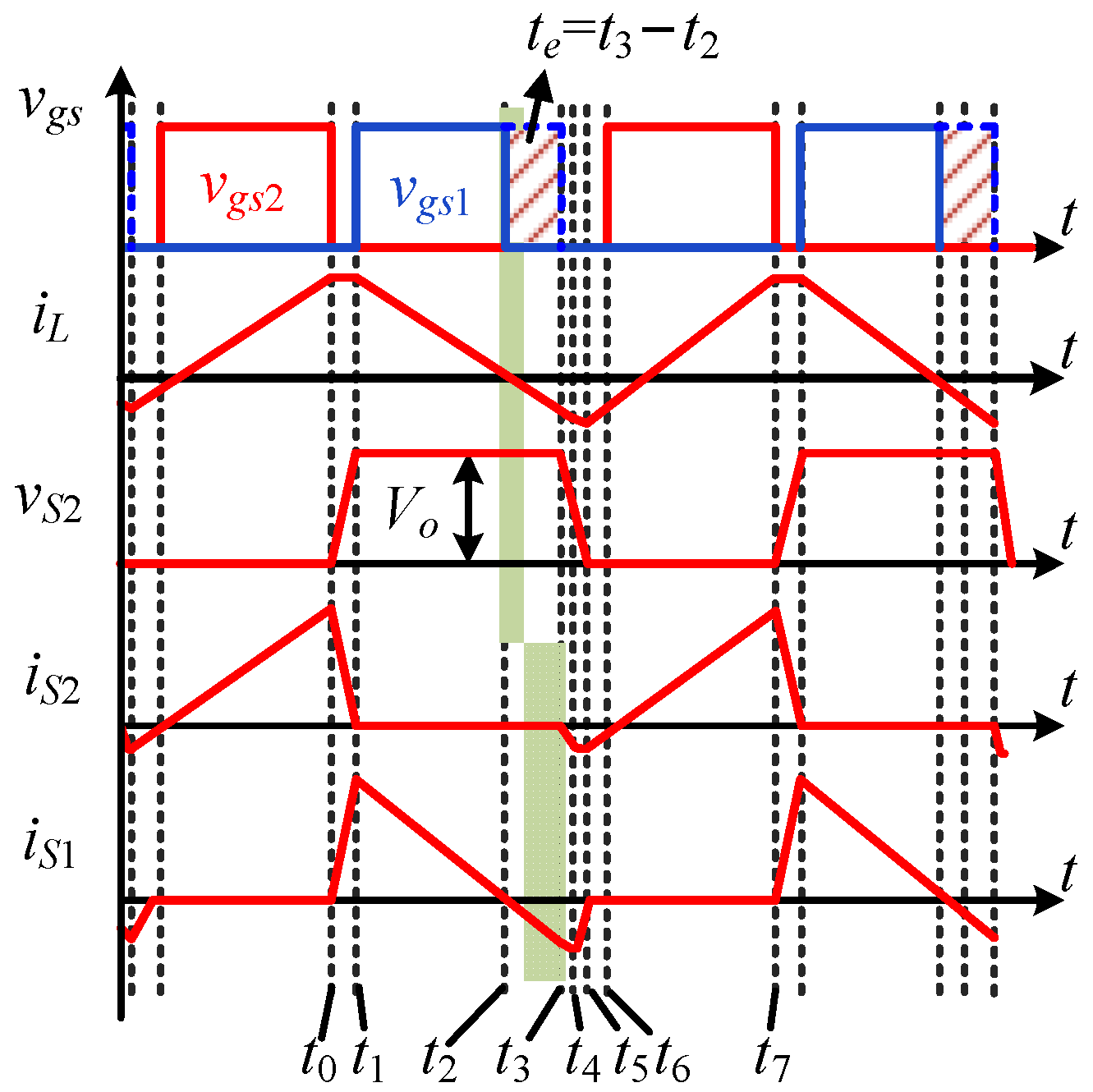

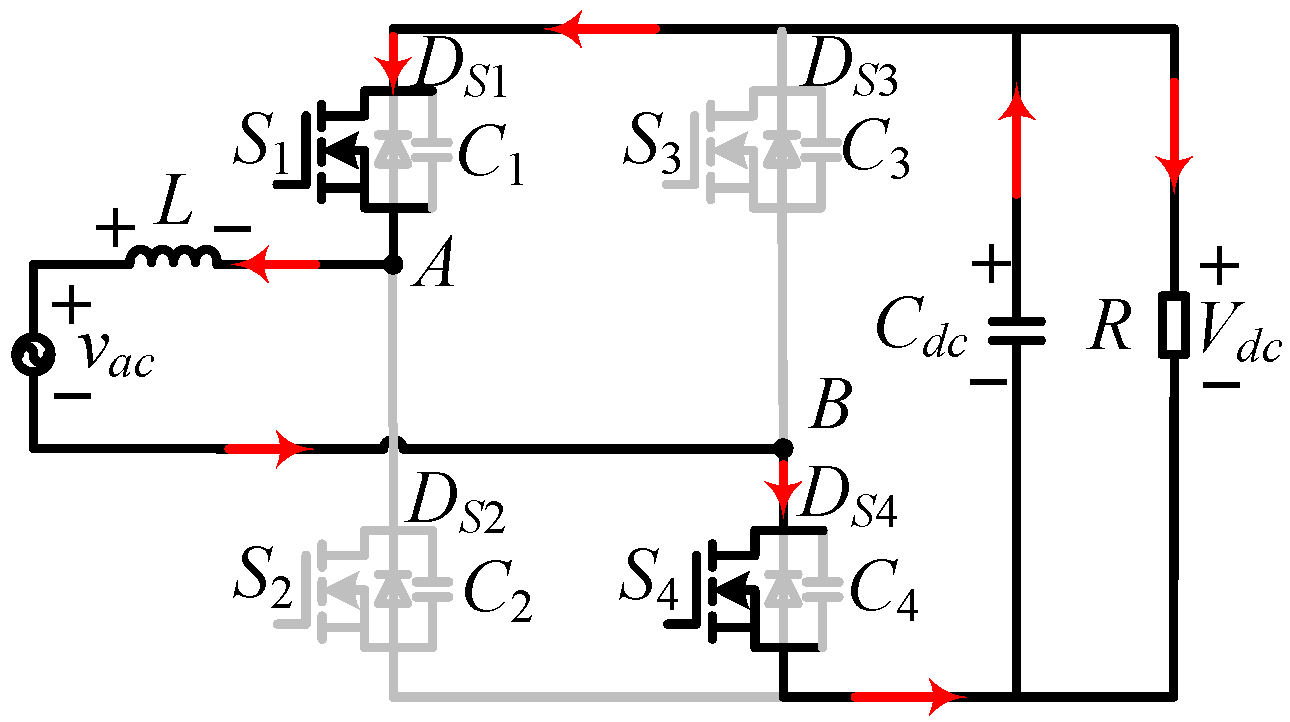

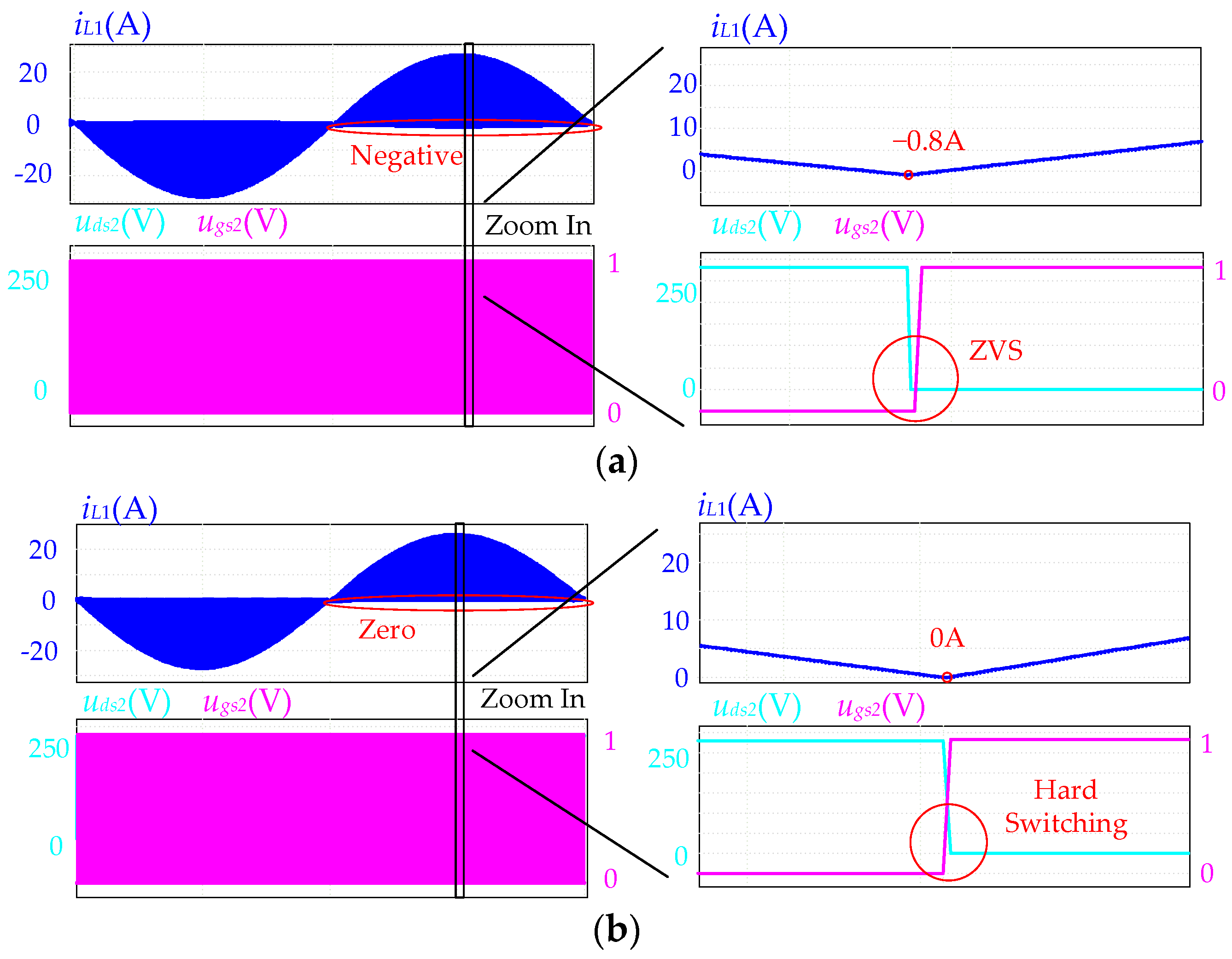

2. ZVS Analysis Considering Switch Junction Capacitors

2.1. ZVS Model Analysis with Junction Capacitors

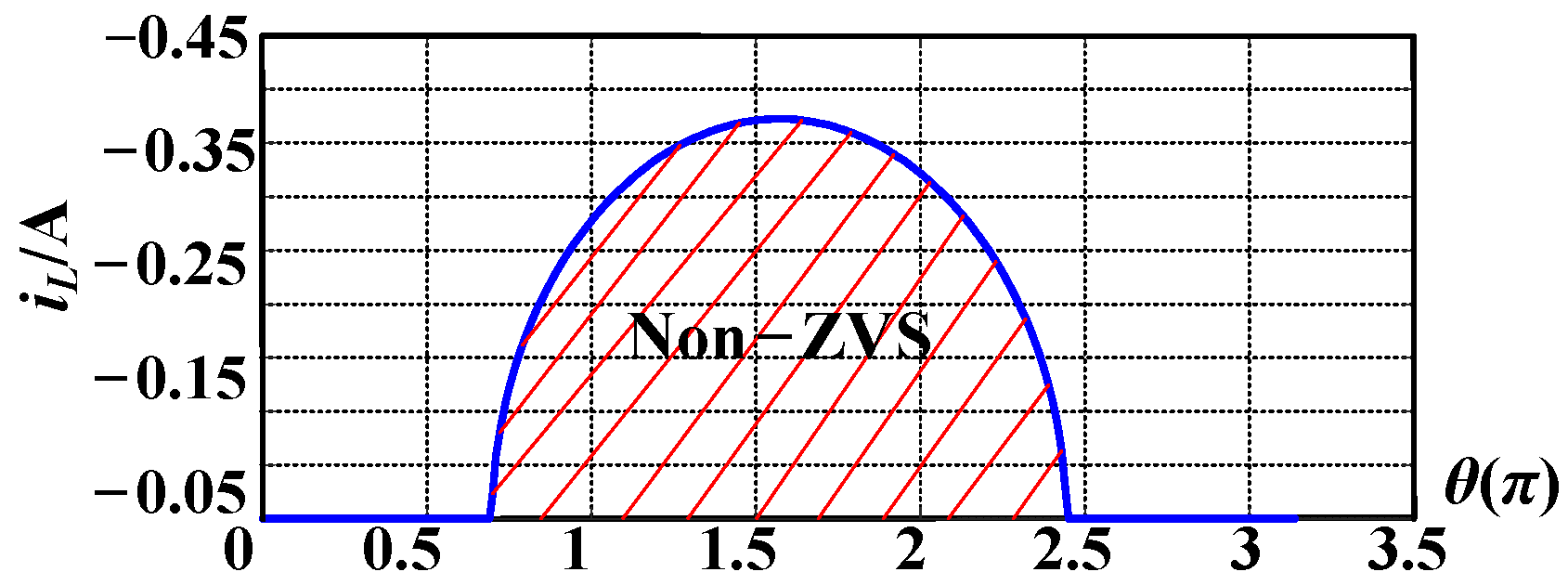

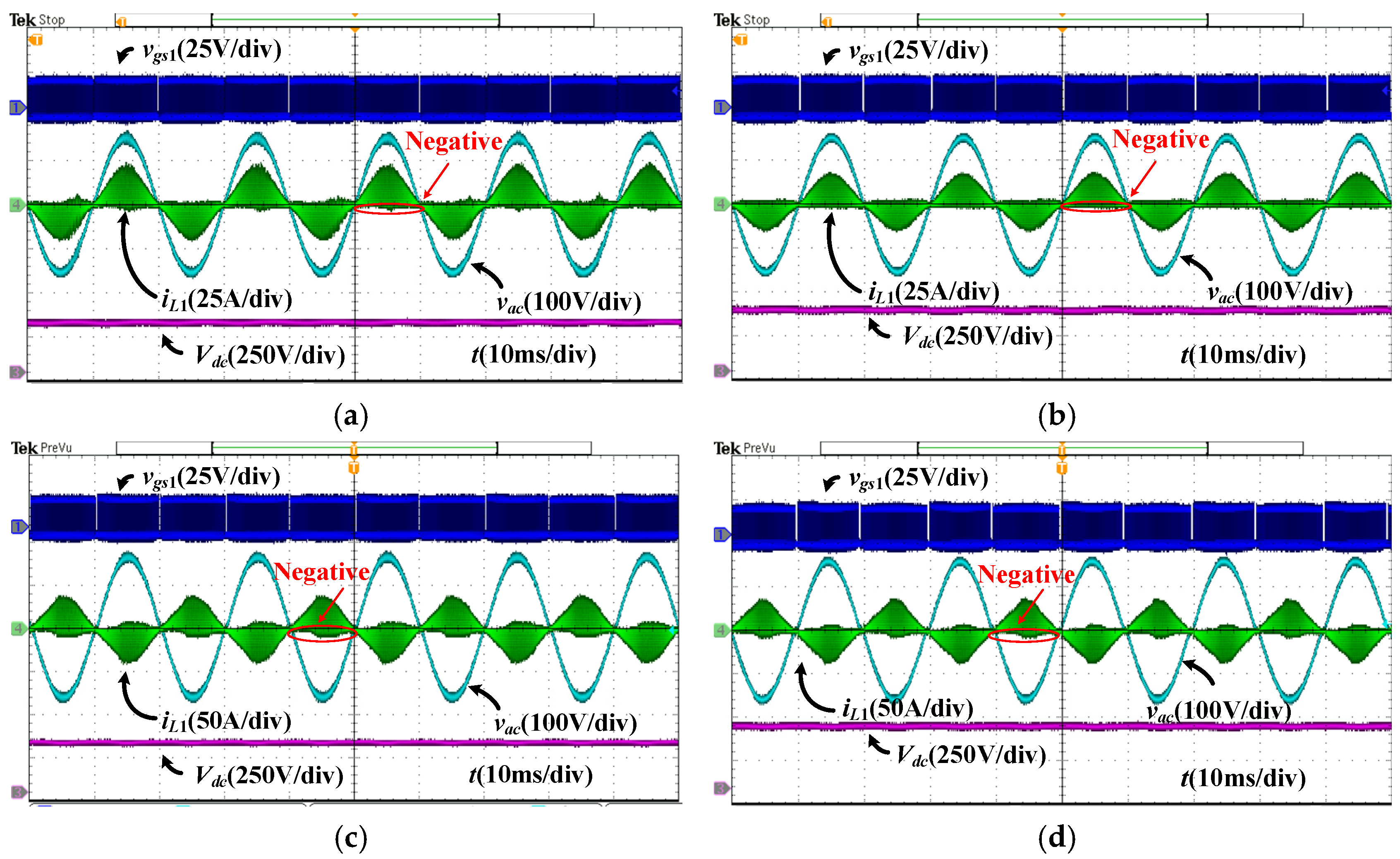

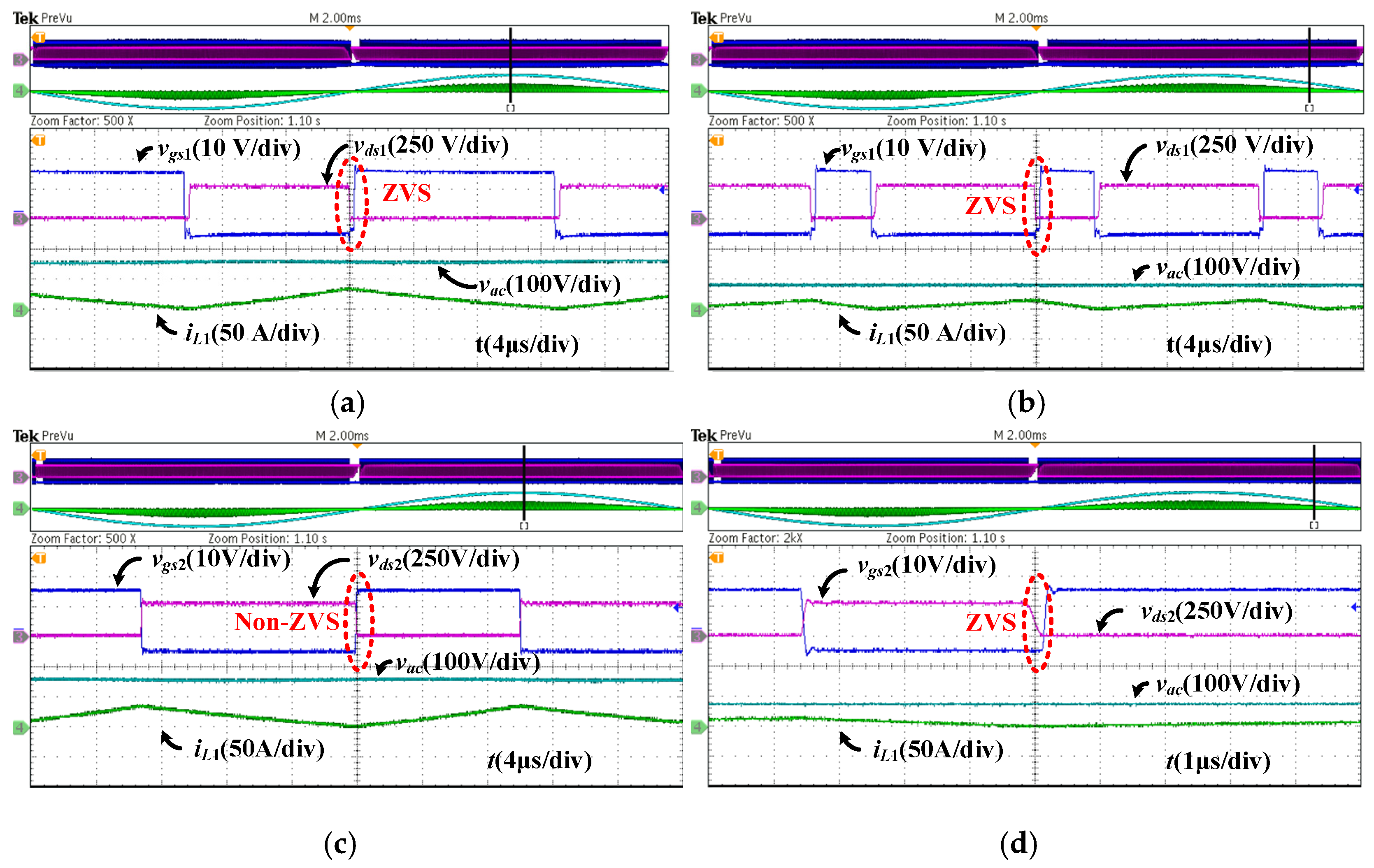

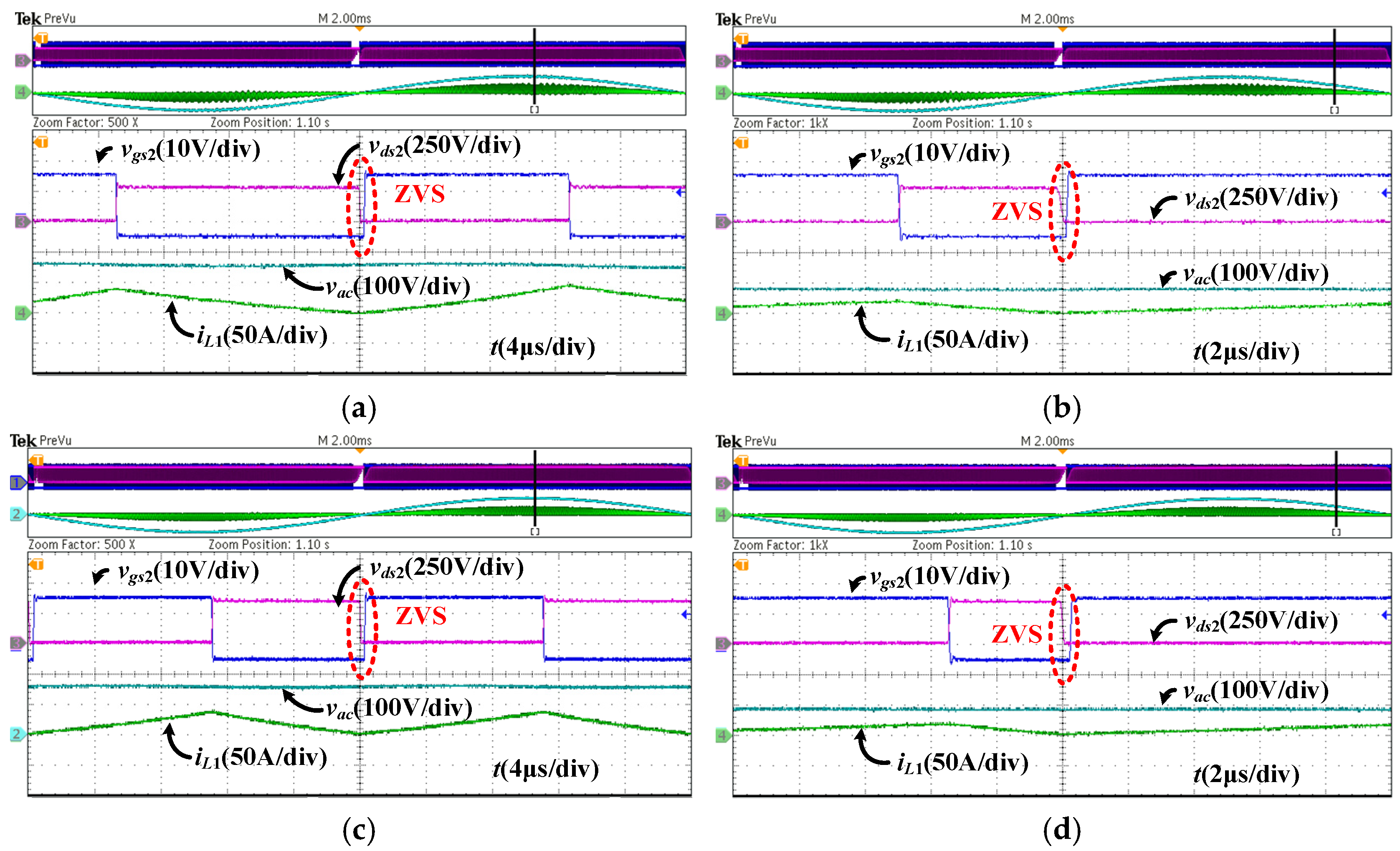

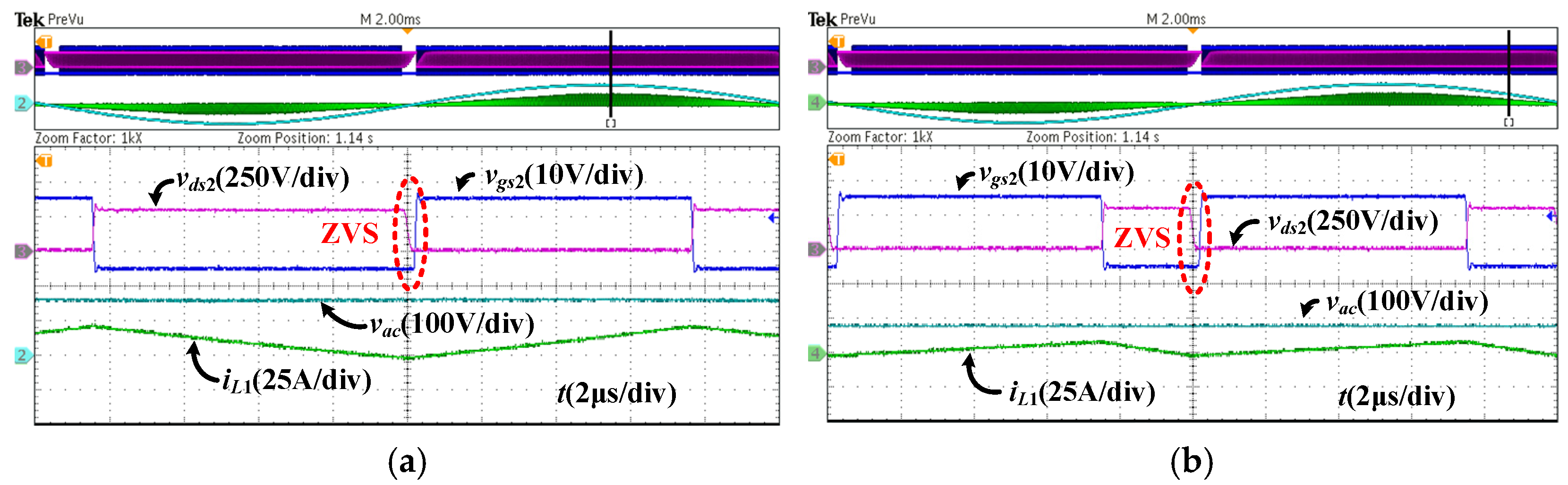

2.2. ZVS Condition and Region

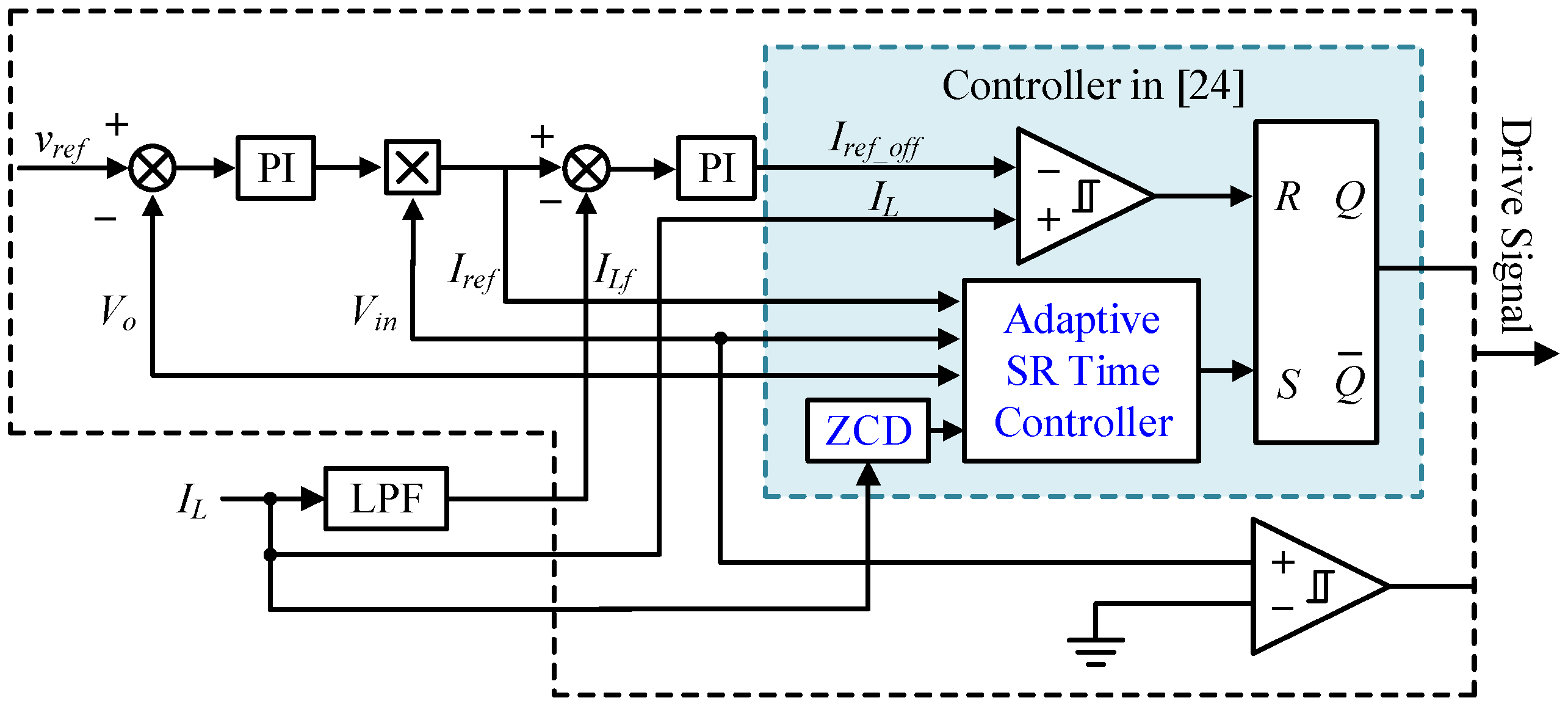

3. Variable-Frequency Control without ZCD Circuits to Achieve ZVS Considering Switch Junction Capacitors

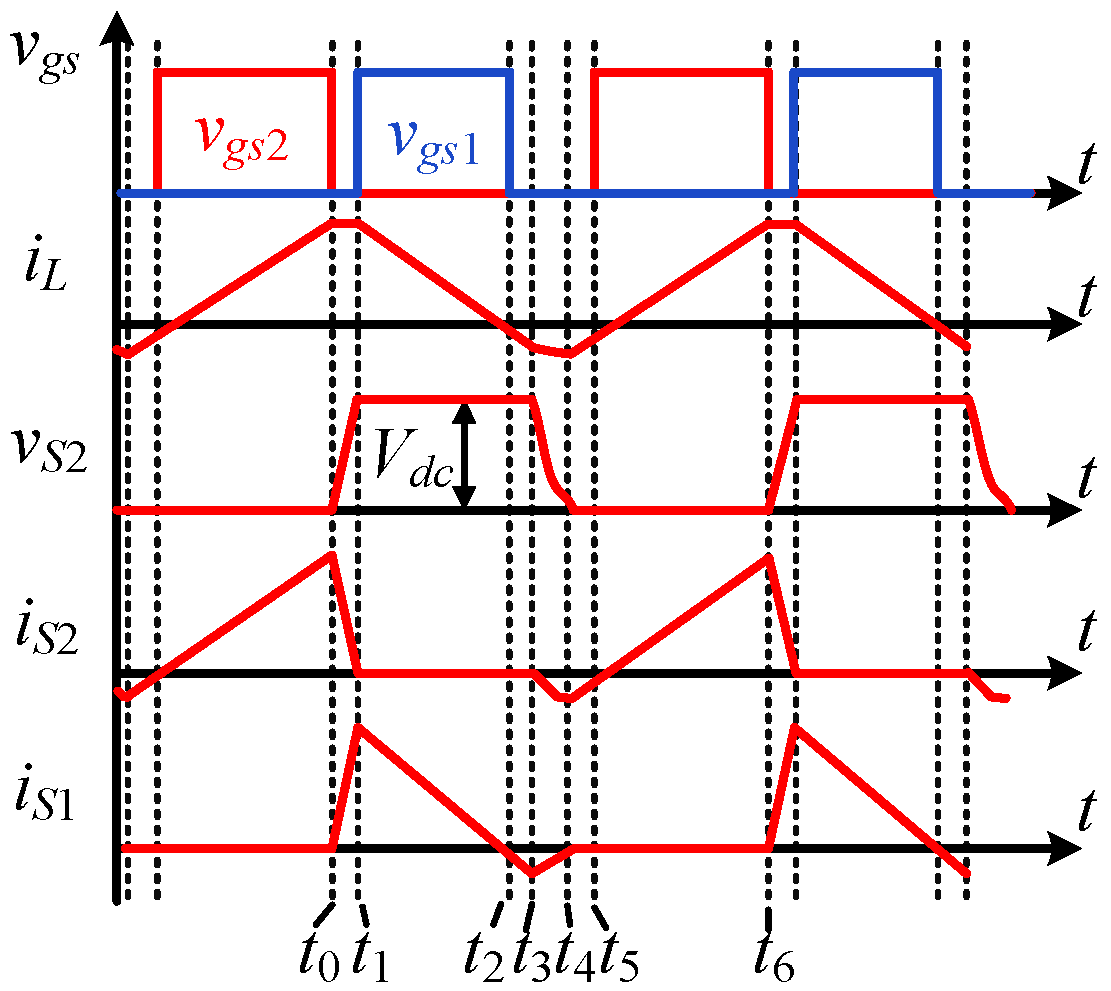

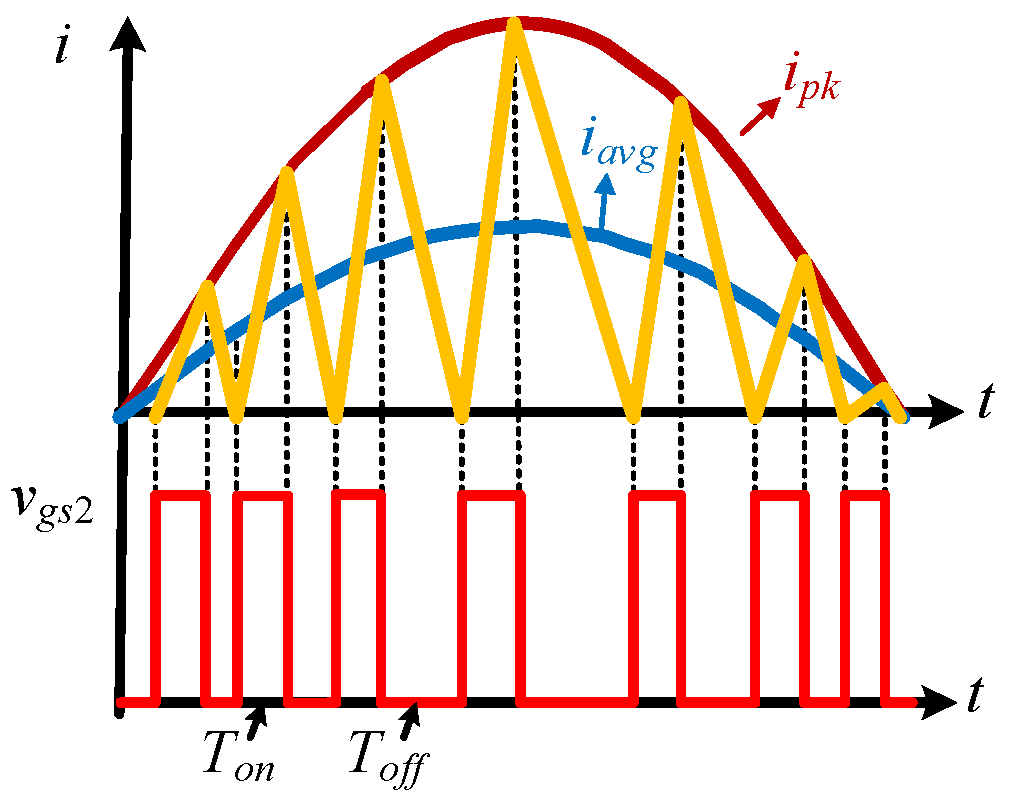

3.1. Conventional Method with ZCD and the Concept Diagram without ZCD

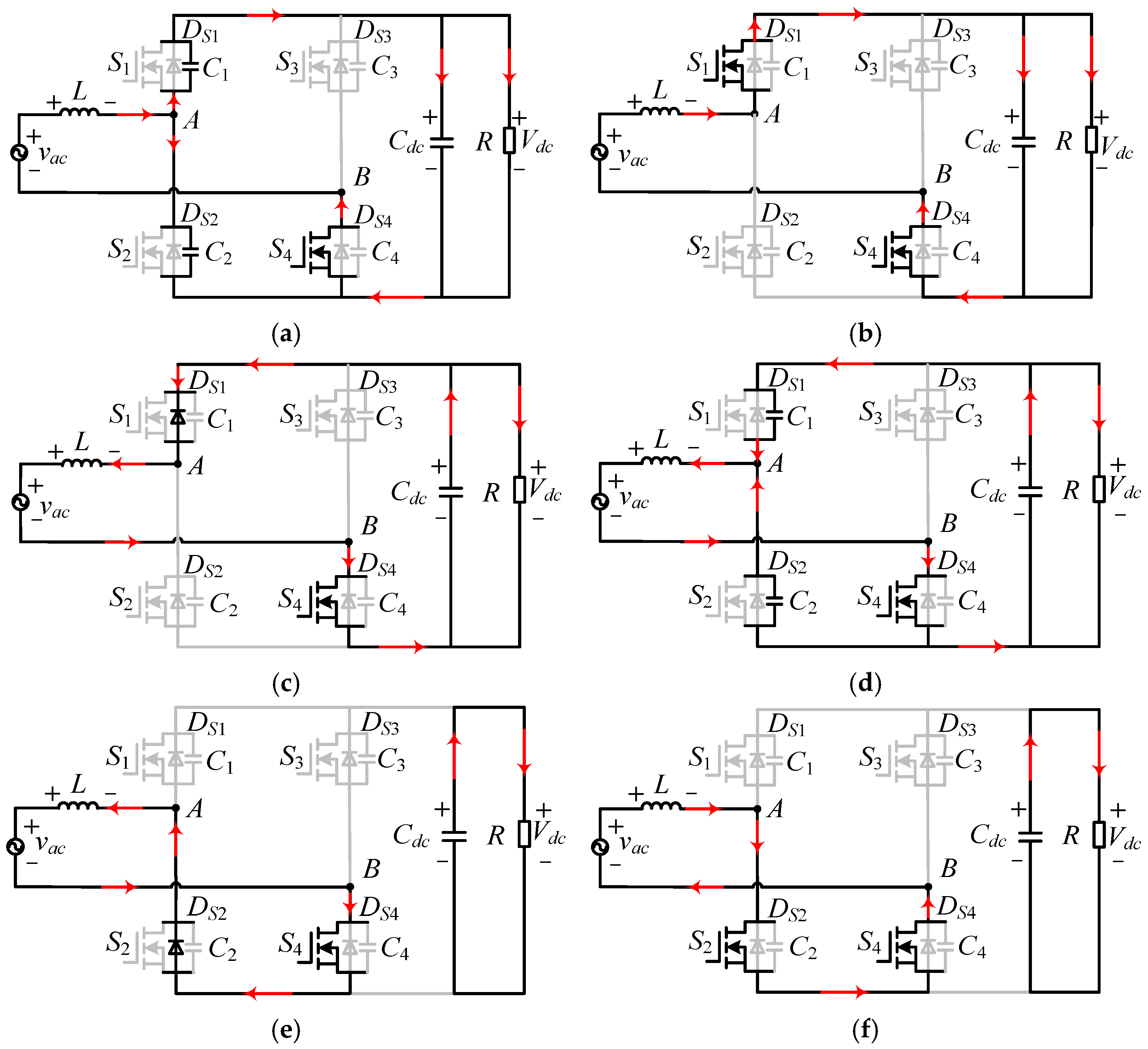

3.2. Working Principal Analysis and Variable Frequency Derivation without ZCD to Achieve ZVS

4. Current Ripple Reduction and Digital Implementation of the Proposed Control Method

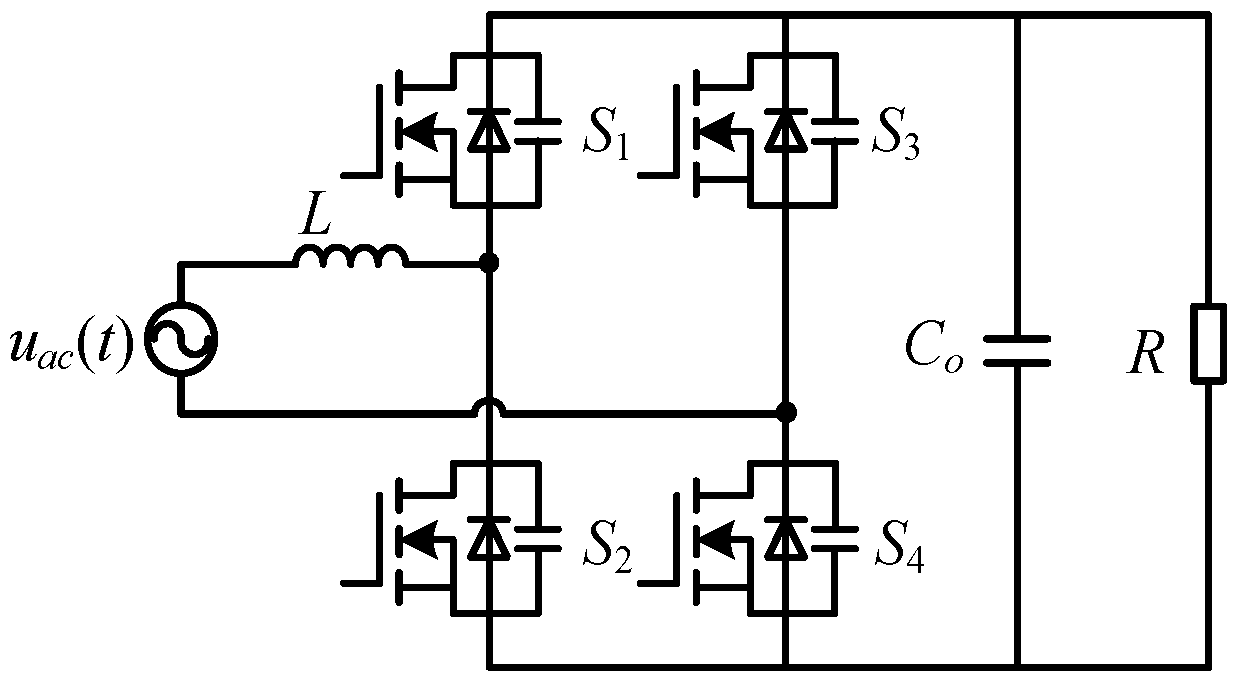

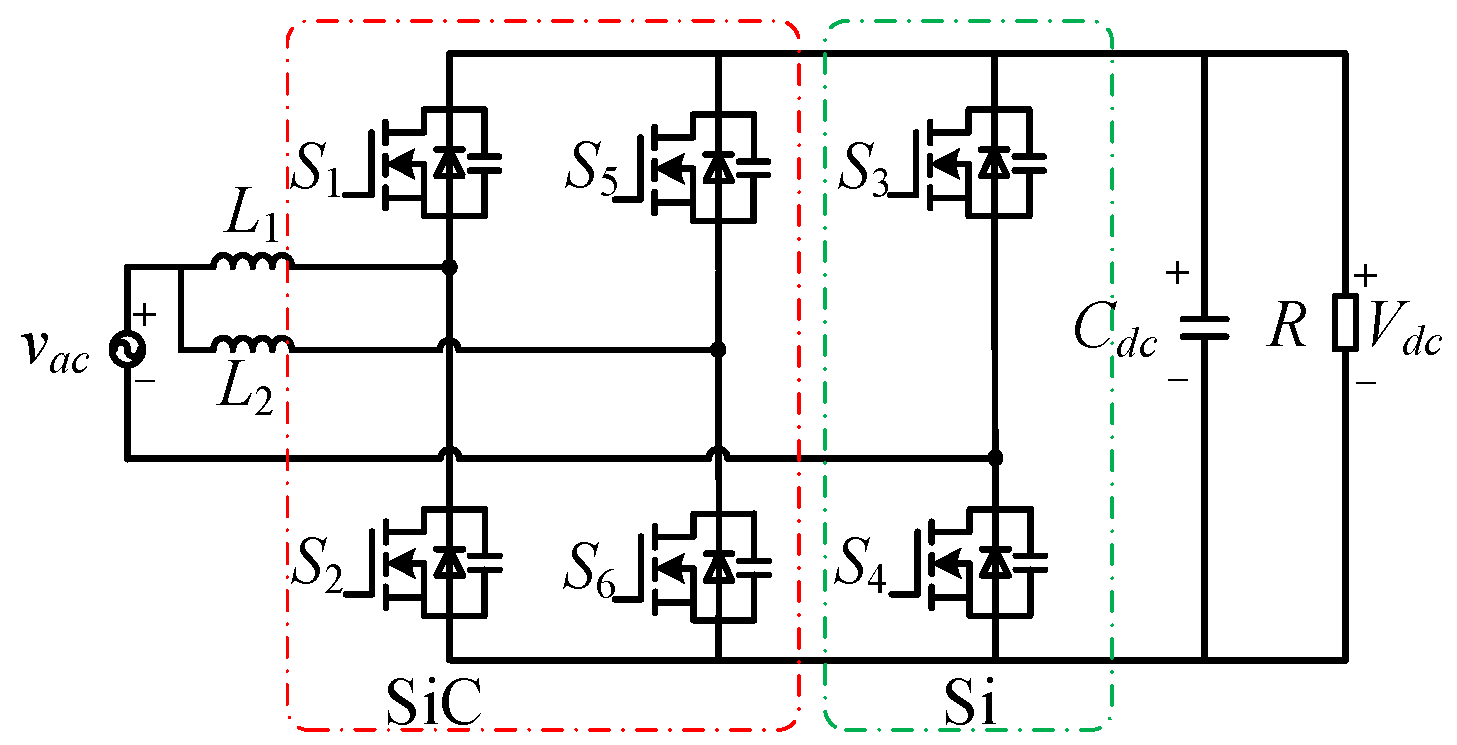

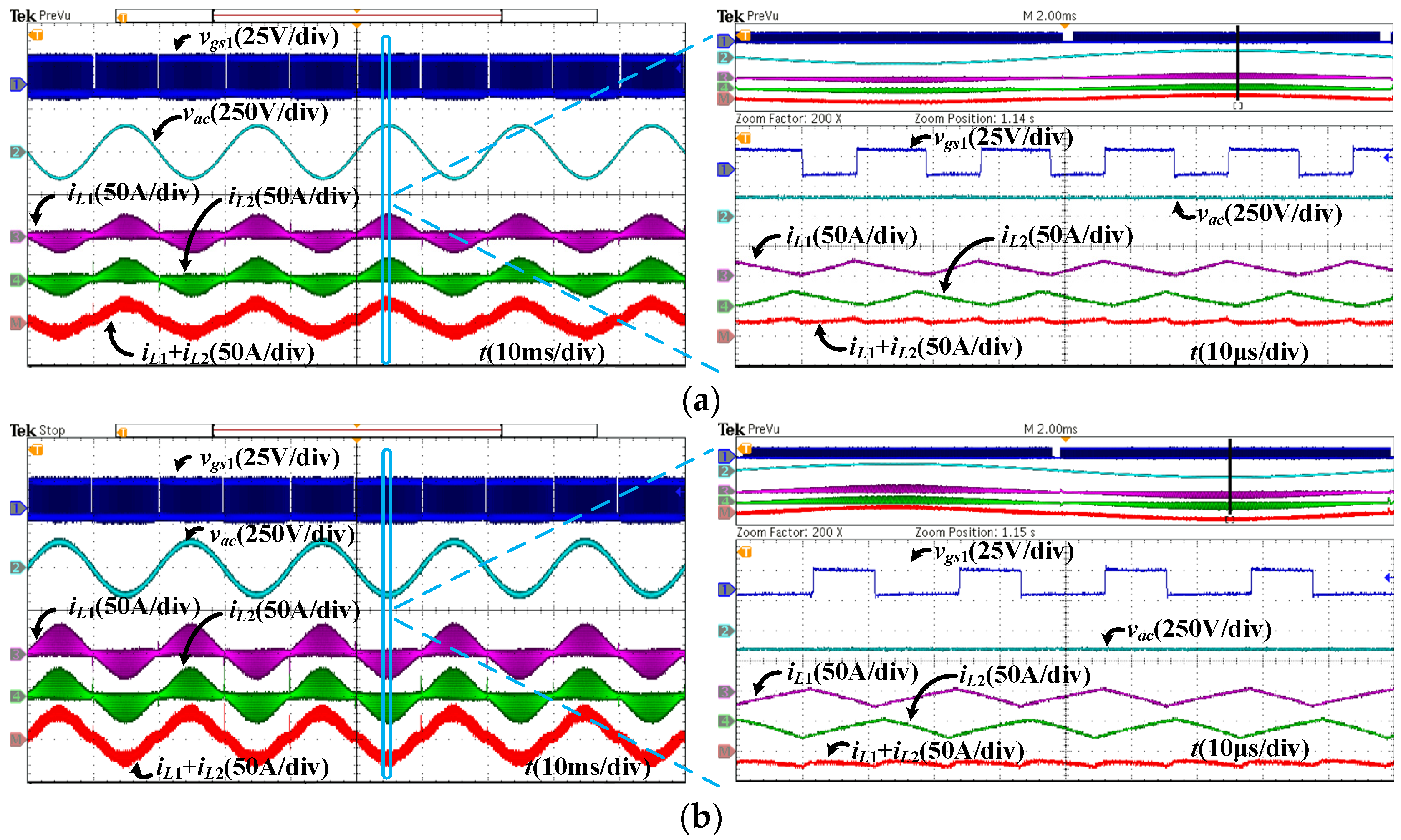

4.1. Current Ripple Reduction with Two-Phase Interleaving for Totem-Pole Bridgeless PFC Converter

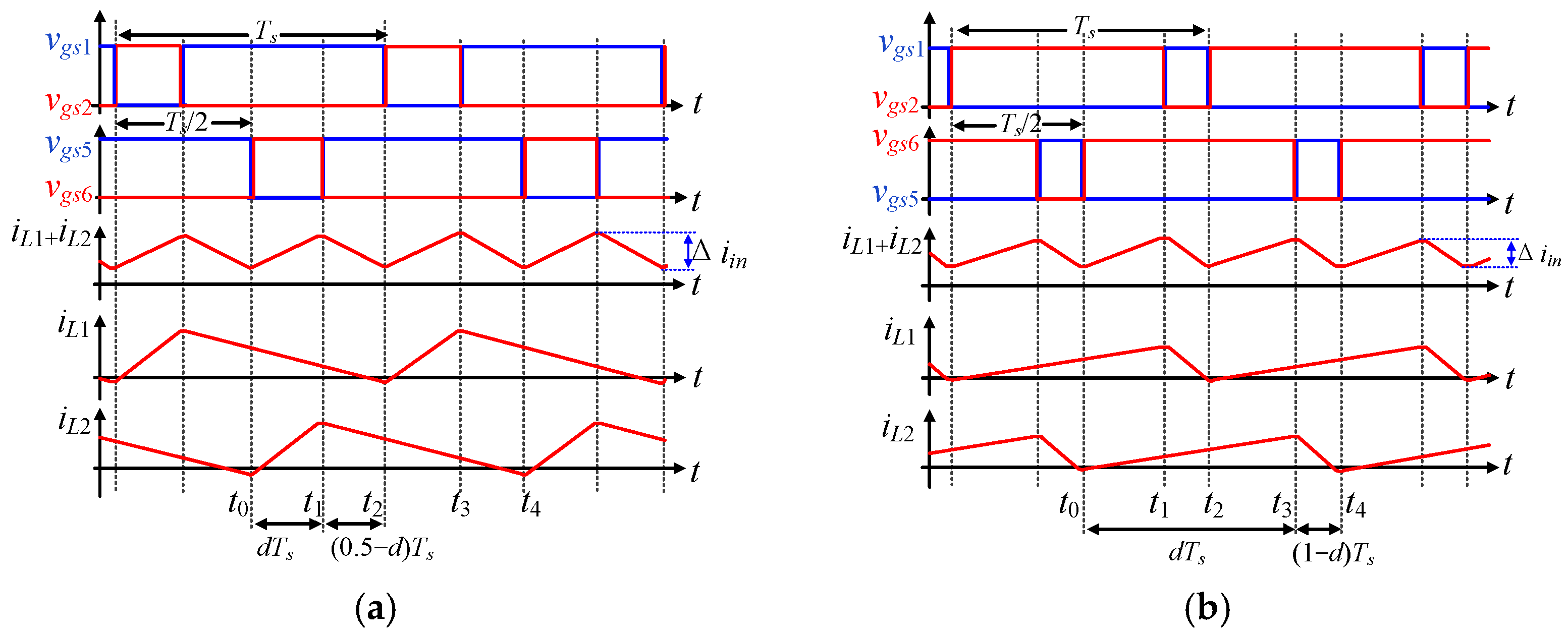

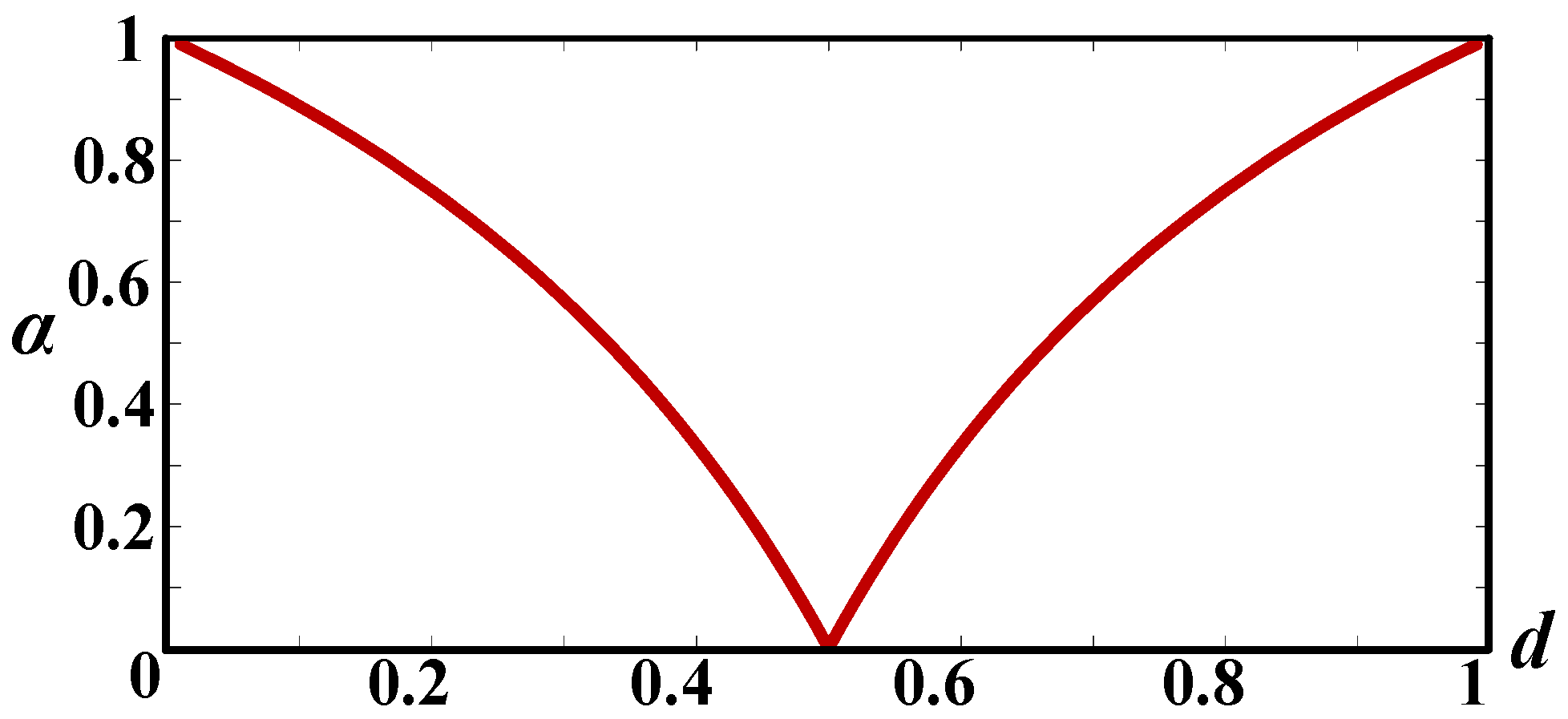

4.2. Analysis of Current Ripple Reduction with Two-Phase Interleaving

- (1)

- d ≤ 0.5

- (2)

- d > 0.5

4.3. Digital Implementation of the Proposed Control Method for Two-Phase Interleaved Parallel Totem-Pole Bridgeless PFC

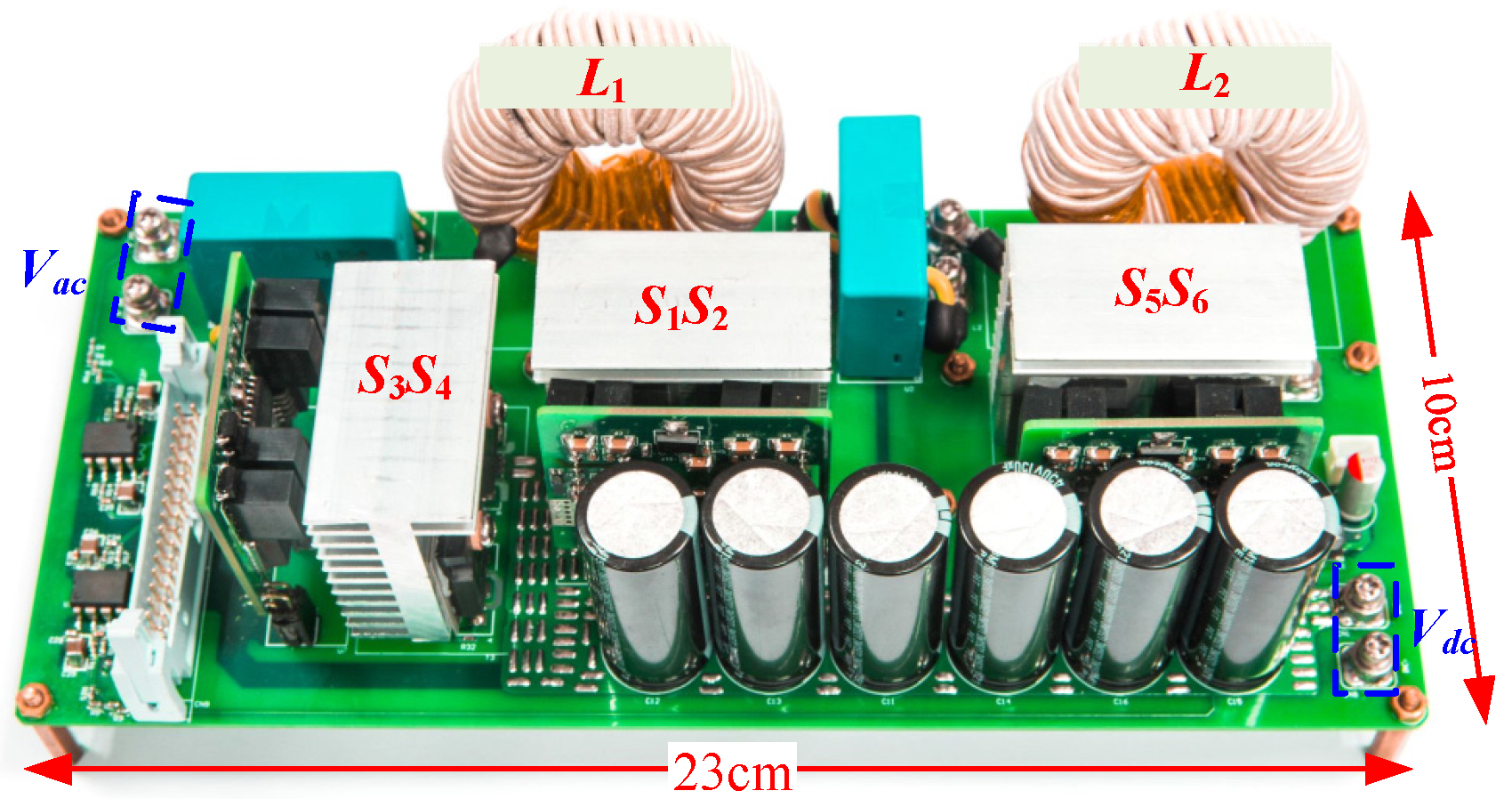

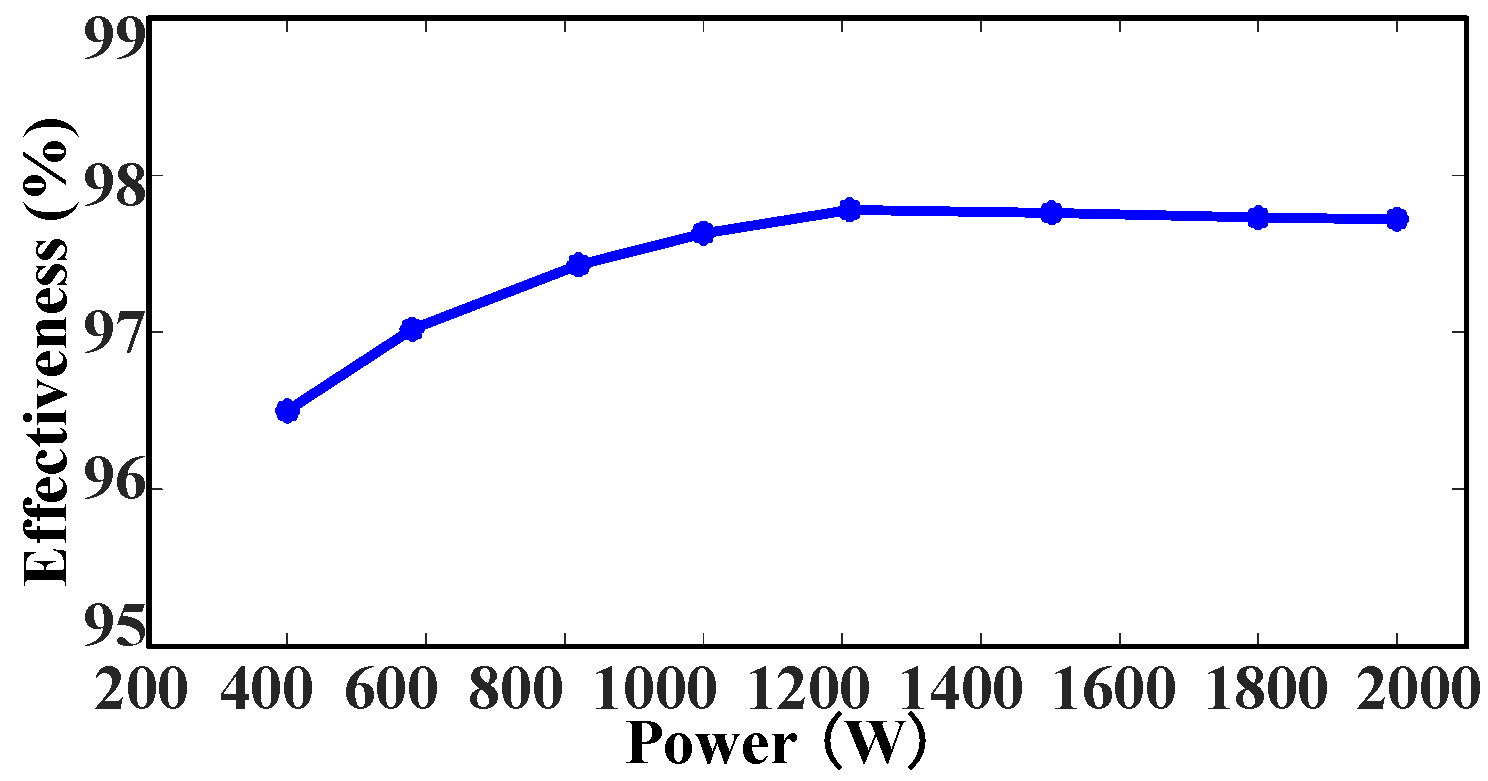

5. Experimental Verification

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Tseng, S.-Y.; Fan, J.-H. Bridgeless boost converter with an interleaving manner for PFC applications. Electronics 2021, 10, 296. [Google Scholar] [CrossRef]

- Park, M.-H.; Baek, J.; Jeong, Y.; Moon, G.-W. An interleaved totem-pole bridgeless boost PFC converter with soft-switching capability adopting phase-shifting control. IEEE Trans. Power Electron. 2019, 34, 10610–10618. [Google Scholar] [CrossRef]

- Wu, S.-T.; Chen, F.-Y.; Chien, M.-C.; Wang, J.-M.; Su, Y.-Y. A hybrid control scheme with fast transient and low harmonic for boost PFC converter. Electronics 2021, 10, 1848. [Google Scholar] [CrossRef]

- Kim, J.-W.; Moon, G.-W. Minimizing effect of input filter capacitor in a digital boundary conduction mode power factor corrector based on time-domain analysis. IEEE Trans. Power Electron. 2015, 31, 3827–3836. [Google Scholar] [CrossRef]

- Youn, H.-S.; Park, J.-S.; Park, K.-B.; Baek, J.-I.; Moon, G.-W. A digital predictive peak current control for power factor correction with low-input current distortion. IEEE Trans. Power Electron. 2015, 31, 900–912. [Google Scholar] [CrossRef]

- Salmon. Comparative evaluation of circuit topologies for 1-phase and 3-phase boost rectifiers operated with a low current distortion. In Proceedings of the 1994 Proceedings of Canadian Conference on Electrical and Computer Engineering, Halifax, NS, Canada, 25–28 September 1994; Volume 31, pp. 30–33. [Google Scholar]

- Martinez, R.; Enjeti, P.N. A high-performance single-phase rectifier with input power factor correction. IEEE Trans. Power Electron. 1996, 11, 311–317. [Google Scholar] [CrossRef]

- de Souza, A.F.; Barbi, I. High power factor rectifier with reduced conduction and commutation losses. In Proceedings of the 21st International Telecommunications Energy Conference, INTELEC’99 (Cat. No. 99CH37007), Copenhagen, Denmark, 9 June 1999; p. 158. [Google Scholar]

- Mansouri, M.; Kaboli, S.H.A.; Selvaraj, J.; Rahim, N.A. A review of single phase power factor correction AC-DC converters. In Proceedings of the 2013 IEEE Conference on Clean Energy and Technology (CEAT), Langkawi, Malaysia, 18–20 November 2013; pp. 389–394. [Google Scholar]

- Singh, B.; Singh, B.N.; Chandra, A.; Al-Haddad, K.; Pandey, A.; Kothari, D.P. A review of single-phase improved power quality AC-DC converters. IEEE Trans. Ind. Electron. 2003, 50, 962–981. [Google Scholar] [CrossRef]

- Huber, L.; Jang, Y.; Jovanovic, M.M. Performance evaluation of bridgeless PFC boost rectifiers. IEEE Trans. Power Electron. 2008, 23, 1381–1390. [Google Scholar] [CrossRef]

- Jang, Y.; Jovanovic, M.M. A bridgeless PFC boost rectifier with optimized magnetic utilization. IEEE Trans. Power Electron. 2009, 24, 85–93. [Google Scholar] [CrossRef]

- Muhammad, K.S.; Lu, D.D.-C. Two-switch ZCS totem-pole bridgeless PFC boost rectifier. In Proceedings of the 2012 IEEE International Conference on Power and Energy (PECon), Kota Kinabalu, Malaysia, 2–5 December 2012; pp. 1–6. [Google Scholar]

- Le, T.-T.; Lee, J.; Choi, S. Single-Stage Totem-Pole AC-DC Converter based on Boost-Half Bridge Structure for battery chargers. IEEE Trans. Power Electron. 2023, 39, 1060–1073. [Google Scholar] [CrossRef]

- Zhou, M.; Peng, C.; Liang, J.; Fu, M.; Wang, H. Current zero-crossing prediction based critical conduction mode control of totem-pole PFC rectifiers. IEEE Trans. Power Electron. 2023, 38, 8513–8527. [Google Scholar] [CrossRef]

- Yao, K.; Chen, K.; Mao, C.; Tang, H.; Li, L.; Wu, C.; Zhang, Z.; Ma, C. Optimal switching frequency variation range control for critical conduction mode boost power factor correction converter. IEEE Trans. Ind. Electron. 2020, 68, 1197–1209. [Google Scholar] [CrossRef]

- Ren, X.; Zhou, Y.; Guo, Z.; Wu, Y.; Zhang, Z.; Chen, Q. Simple analog-based accurate variable on-time control for critical conduction mode boost power factor correction converters. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 8, 4025–4036. [Google Scholar] [CrossRef]

- Wang, K.; Zhu, H.; Wu, J.; Yang, X.; Wang, L. Adaptive driving scheme for ZVS and minimizing circulating current in MHz CRM converters. IEEE Trans. Power Electron. 2020, 36, 3633–3637. [Google Scholar] [CrossRef]

- Yang, Y.; Li, Z.; Song, D.; Wang, S.; Zhang, Z.; Ren, X.; Chen, Q. SR control with zero current detection delay compensation for GaN CRM totem-pole PFC rectifier. IEEE Trans. Power Electron. 2023, 38, 7059–7068. [Google Scholar] [CrossRef]

- Jeong, Y.; Park, M.-H.; Moon, G.-W. High-efficiency zero-voltage-switching totem-pole bridgeless rectifier with integrated inrush current limiter circuit. IEEE Trans. Ind. Electron. 2019, 67, 7421–7429. [Google Scholar] [CrossRef]

- Belkamel, H.; Kim, H.; Choi, S. Interleaved totem-pole ZVS converter operating in CCM for single-stage bidirectional AC–DC conversion with high-frequency isolation. IEEE Trans. Power Electron. 2020, 36, 3486–3495. [Google Scholar] [CrossRef]

- Lee, Y.-D.; Moon, G.-W.; Baek, J.; Kim, C.-E. A reconfigurable totem-pole PFC rectifier with light load optimization control strategy and soft-switching capability. IEEE Trans. Power Electron. 2020, 36, 4371–4382. [Google Scholar] [CrossRef]

- Tausif, A.; Bakan, A.F.; Dusmez, S. A High Power Density Zero-Voltage-Switching Totem-Pole Power Factor Correction Converter. IEEE Trans. Power Electron. 2023, 39, 837–849. [Google Scholar] [CrossRef]

- Huang, Q.; Yu, R.; Huang, A.Q.; Yu, W. Adaptive zero-voltage-switching control and hybrid current control for high efficiency GaN-based MHz Totem-pole PFC rectifier. In Proceedings of the 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), Tampa, FL, USA, 26–30 March 2017; pp. 1763–1770. [Google Scholar]

- Tang, Y.; Ding, W.; Khaligh, A. A bridgeless totem-pole interleaved PFC converter for plug-in electric vehicles. In Proceedings of the 2016 IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 20–24 March 2016; pp. 440–445. [Google Scholar]

- Soares, J.W.M.; Badin, A.A. High-efficiency interleaved totem-pole pfc converter with voltage follower characteristics. IEEE J. Emerg. Sel. Top. Power Electron. 2022, 11, 1879–1887. [Google Scholar] [CrossRef]

| Parameters | Value | Parameters | Value |

|---|---|---|---|

| AC voltage (vac) | 110 V, 50 Hz | DC bus capacitor (Cdc) | 2000 μF |

| DC voltage (Vdc) | 280 V–370 V | AC inductance (L1, L2) | 56 μH |

| Rated power (Pdc) | 2000 W | Operating frequency (fs) | 40–200 kHz |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Xi, H.; Li, L.; Xu, G.; Su, M.; Cai, Z. Variable-Frequency Control for Totem-Pole Bridgeless Power Factor Correction Converter to Achieve Zero-Voltage Switching Without Zero-Crossing Detection Circuits. Electronics 2024, 13, 3108. https://doi.org/10.3390/electronics13163108

Xi H, Li L, Xu G, Su M, Cai Z. Variable-Frequency Control for Totem-Pole Bridgeless Power Factor Correction Converter to Achieve Zero-Voltage Switching Without Zero-Crossing Detection Circuits. Electronics. 2024; 13(16):3108. https://doi.org/10.3390/electronics13163108

Chicago/Turabian StyleXi, He, Liting Li, Guo Xu, Mei Su, and Zhiqiang Cai. 2024. "Variable-Frequency Control for Totem-Pole Bridgeless Power Factor Correction Converter to Achieve Zero-Voltage Switching Without Zero-Crossing Detection Circuits" Electronics 13, no. 16: 3108. https://doi.org/10.3390/electronics13163108