Design and Simulation of Low-Orbit Satellite Broadcast Signal Receiving and Processing Terminal

Abstract

1. Introduction

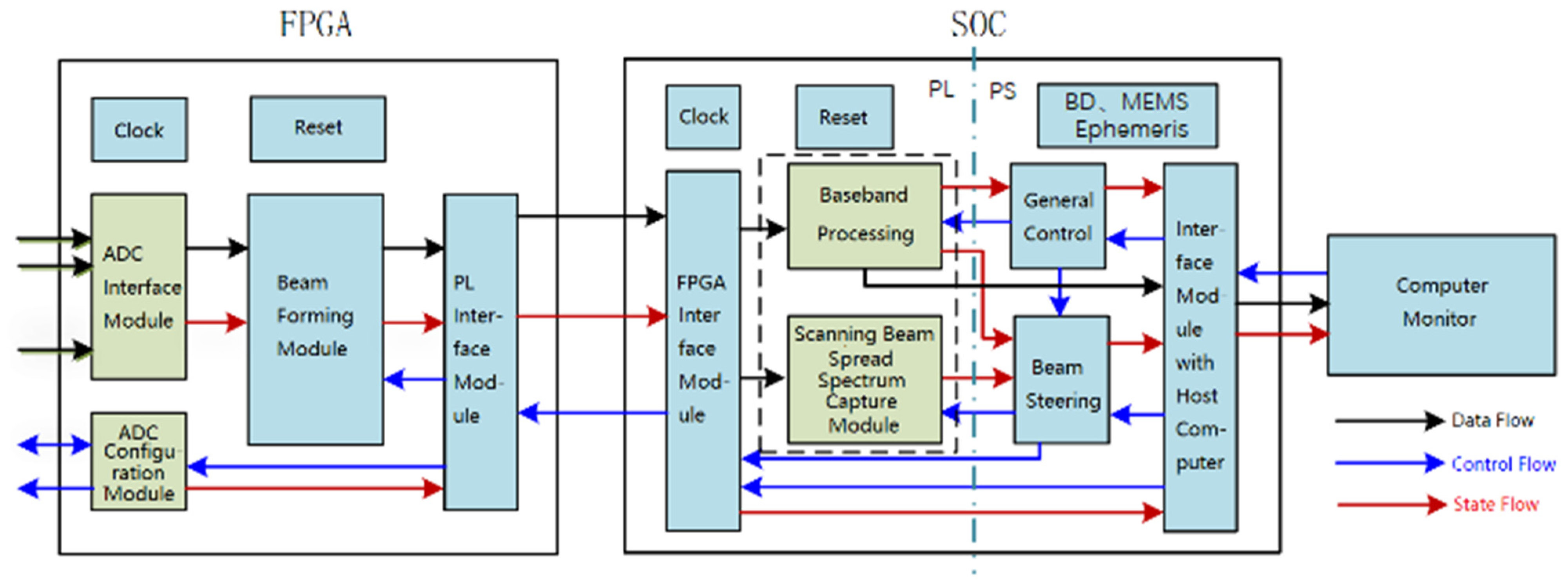

2. Overall System Design

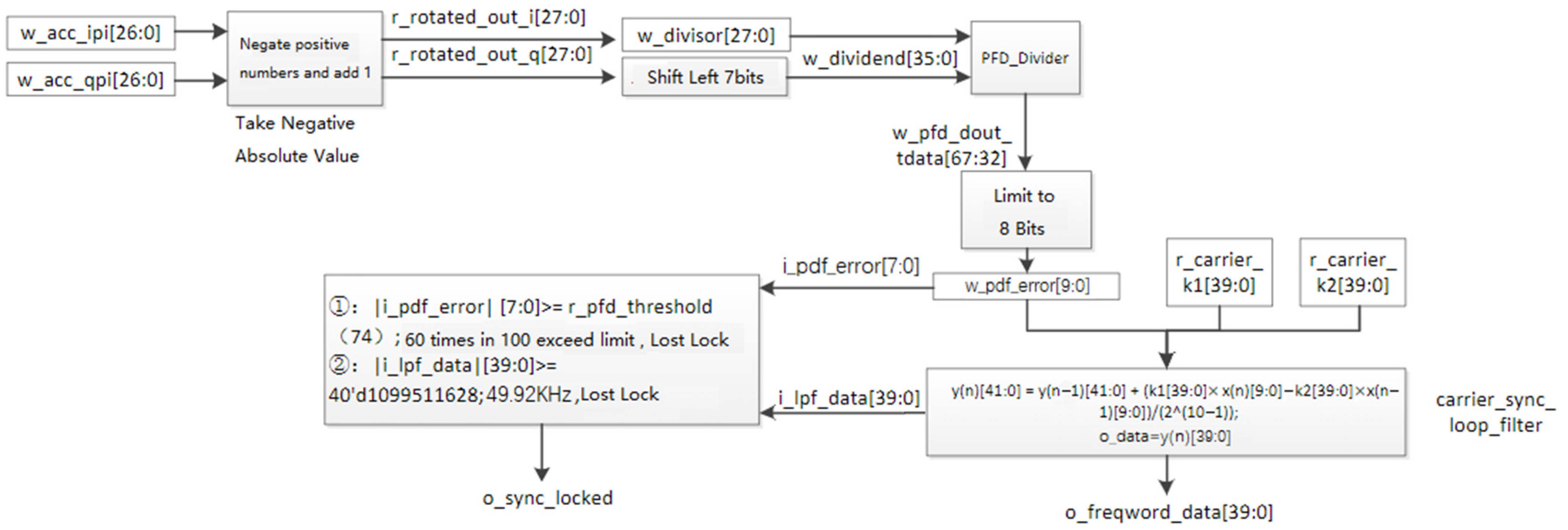

3. Key Technologies

3.1. Digital Beamforming Technology

3.2. Time–Frequency Domain Narrowband Anti-Interference Technology

3.3. FFT Fast Acquisition Method Introducing Bit Synchronization Loop

3.4. Overall Machine Design

4. Simulation Results

4.1. RF Link Simulation and Budgeting

4.2. Digital Beamforming Simulation

4.3. Time–Frequency Domain Narrowband Anti-Interference Simulation

4.4. Capture and Tracking Module Simulation

4.5. VTB Decoding Simulation

5. Conclusions and Future Work

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Zhou, J.; Sun, Z.; Zhang, R.; Lin, G.; Zhang, S.; Zhao, Y. A Cloud-Edge Collaboration CNN-Based Routing Method for ISAC in LEO Satellite Networks. In Proceedings of the 2nd Workshop on Integrated Sensing and Communications for Metaverse, Helsinki, Finland, 18 June 2023. [Google Scholar]

- Wang, C.; Wang, Z. Improved Acquisition Method of GPS Signal by Wavelet De-noising. In Proceedings of the International Conference on Industrial Technology and Management Science(ITMS 2015), Tianjin, China, 27–28 March 2015. [Google Scholar]

- Sun, Y.; Peng, M.; Zhang, S.; Lin, G.; Zhang, P. Integrated Satellite-Terristrial Networks: Architectures, Key Techniques, and Experimental Progress. IEEE Netw. 2022, 36, 191–198. [Google Scholar] [CrossRef]

- Cong, M. Research of Narrowband Anti-Interference Technologies in Satellite Navigation. Master’s Thesis, Beijing Institute of Technology, Beijing, China, 2016. [Google Scholar]

- Feng, H. Research on Estimation of ISAR Amplitude-Phase Error in Pulses and Narrow-Band Interference for Waveform Optimization Method. Master’s Thesis, Xidian University, Xi’an, China, 2022. [Google Scholar]

- Liu, J.; Du, X.; Cui, J.; Pan, M.; Wei, D. Task-Oriented Intelligent Networking Architecture for the Space-Air-Ground Aqua Integrated Network. IEEE Internet Things J. 2020, 7, 5345–5358. [Google Scholar] [CrossRef]

- Qian, Z. Complex Electromagnetic Signal Acquisition Technology Based on Radio Frequency Identification of Internet of Things. In Proceedings of the 2020 International Conference on Computer Information and Big Data Applications (CIBDA), Guiyang, China, 17–19 April 2020. [Google Scholar]

- Xu, W. Research on the Fast Acquisition Method of Beidou Satellite Signals. Master’s Thesis, Southeast University, Nanjing, China, 2022. [Google Scholar]

- Fenech, H.; Amo, S. The Role of Array Antennas in Commercial Telecommunication Satellites. In Proceedings of the 2016 10th European Conference on Antennas and Propagation (EuCAP), Davos, Switzerland, 10–15 April 2016; IEEE: New York, NY, USA, 2016. [Google Scholar]

- Gordana, B.; Marius, O.; Florin, A.; Ana, G. Digital Beamforming Techniques for Future Communications Systems. In Proceedings of the 2020 12th International Symposium on Communication Systems, Networks and Digital Signal Processing (CSNDSP), Porto, Portugal, 20–22 July 2020. [Google Scholar]

- Staileyand, J.E.; Hondl, K.D. Multifunction Phased Array Radar for Aircraft and Weather Surveillance. Proc. IEEE 2016, 104, 649–659. [Google Scholar] [CrossRef]

- Zhang, Q.; Feng, S.; Fu, L.; Wen, J.; Ge, J.; Ma, J. Design and Implementation of Adaptive Digital Beamforming Based on FPGA. In Proceedings of the 2023 4th China International SAR Symposium (CISS), Xi’an, China, 4–6 December 2023; IEEE: New York, NY, USA, 2023. [Google Scholar]

- Rui, C.; Xiaohui, T.; Lihui, J.; Zhang, J.; Peng, G.; Rong, D.; Xu, X.; Zhang, Y.; Xu, Y.; Yang, H. A Wideband Digital Beamforming System for Large Aperture Array Radio Telescope. In Proceedings of the 2022 Asia-Pacific Microwave Conference (APMC), Yokohama, Japan, 29 November–2 December 2022. [Google Scholar]

- Zhang, B.; Liu, H.; Zhai, G.; Meng, M. Comparative study on adaptive digital beamforming techniques. In Proceedings of the 2024 IEEE 6th Advanced Information Management, Communicates, Electronic and Automation Control Conference (IMCEC), Chongqing, China, 24–26 May 2024. [Google Scholar]

- Spoof, K.; Tenhunen, M.; Unnikrishnan, V.; Stadius, K.; Kosunen, M.; Ryynänen, J. True-Time-Delay Receiver IC With Reconfigurable Analog and Digital Beamforming. IEEE Access 2022, 10, 116375–116383. [Google Scholar] [CrossRef]

- Dusari, N.R.; Shipra, M.R. Digital Beamforming with Digital Predistortion using Xilinx RF SoC ZCU216. In Proceedings of the 2022 IEEE International Conference on Signal Processing and Communications (SPCOM), Bangalore, India, 11–15 July 2022. [Google Scholar]

- Li, Y.; He, S.; Ma, C.; Ma, S.; Li, C.; Yang, L. Channel Characteristic and Capacity Analysis of Millimeter Wave MIMO Beamforming System. In Proceedings of the 2016 IEEE 83rd Vehicular Technology Conference (VTC Spring), Nanjing, China, 15–18 May 2016. [Google Scholar]

- Subramaniyan, E.; Rajagopal, S. Wideband Beamforming using Digital Phase Only Compensation in Digital Array Radars. In Proceedings of the 2022 IEEE International Conference on Electronics, Computing and Communication Technologies (CONECCT), Bangalore, India, 8–10 July 2022. [Google Scholar]

- Liang, Y.; Xu, A.; Zhang, M.; Zhai, H.; Yuan, H. Research and Realization of Adaptive Digital Beamforming Technology Based on Spatial Spectrum Estimation. In Proceedings of the 2021 CIE International Conference on Radar (Radar), Haikou, China, 15–19 December 2021. [Google Scholar]

- Chen, Y.; Wang, D.; Liu, P.; Xu, Z.; Wei, C.; Dong, Q. An improved approach of SFAP algorithm for suppressing concurrent narrow and wide band interference. In Proceedings of the 7th Satellite Navigation Conference, Shanghai, China, 18–20 May 2016. [Google Scholar]

- Akho-Zahieh, M.M.; Abdellatif, N. Narrow-band Interference Suppression in Wavelet Packet Multirate Multicarrier CDMA System. In Proceedings of the 2nd International Conference on Communication Technology (ICCT 2015), Hangzhou, China, 18–20 October 2015. [Google Scholar]

- Lu, R.; Weston, C.; Weyer, D.; Buhler, F.; Lambalot, D.; Flynn, M.P. A 16-Element Fully Integrated 28-GHz Digital RX Beamforming Receiver. IEEE J. Solid State Circuits 2021, 56, 1374–1386. [Google Scholar] [CrossRef]

- Yao, R.; Chen, Y.; Li, G.; Feng, Z.; Wang, L. Iterative Threshold Algorithm for Narrow-band Interference Suppression. In Proceedings of the 2013 22nd Wireless and Optical Communication Conference, Chongqing, China, 16–18 May 2013. [Google Scholar]

- Cui, X.; Liu, Y.; Wei, W.; Liao, K.; Yu, D. An Improved Narrow-Band Interference Suppression Method for HINOC System. In Proceedings of the 2012 IEEE 11th International Conference on Solid-State and Integrated Circuit Technology(ICSICT-2012), Xi’an, China, 29 October–1 November 2012. [Google Scholar]

- Lyn, Q.S.; Qzin, H.L. A General Method to Mitigate the ContinuousWave Interference and Narrowband Interference for GNSS Receivers. IET Radar Sonar Navigation 2020, 14, 1430–1435. [Google Scholar]

- Huang, L.; Lu, Z.K.; Xiao, Z.; Ren, C.; Song, J.; Li, B. Suppression of Jammer Multipath in GNSS Antenna Array Receiver. Remote Sens. 2022, 14, 350. [Google Scholar] [CrossRef]

- Chen, C.; Zhuo, Y. A research on anti-jamming method based on compressive sensing for OFDM analogous system. In Proceedings of the 2017 IEEE 17th International Conference on Communication Technology (ICCT), Chengdu, China, 27–30 October 2017. [Google Scholar]

- Chen, Q.; Liang, J.; Zhang, F.; Bi, B. Research on Anti-jamming Algorithm of BDS Signal in WiFi6 Environment. In Proceedings of the 2020 IEEE 8th International Conference on Information, Communication and Networks (ICICN), Xi’an, China, 22–25 August 2020. [Google Scholar]

- Issam, S.M.; Adname, A.; Madiabdessalam, A. Anti-Jamming Techniques for Aviation GNSS-based Navigation systems: Survey. In Proceedings of the IEEE 2nd International Conference on Electronics, Control, Optimization and Computer Science, Kenitra, Morocco, 2–3 December 2020. [Google Scholar]

- Hao, Z.H.; Zhao, H.Z.; Shao, S.H.; Tang, Y. Suppression of Time-Varying Multi-Tone Interference Based on Frenquency Domain Interference Detection. Wirel. Pers. Commun. 2014, 75, 1051–1060. [Google Scholar] [CrossRef]

- Wei, D.; Cui, J.; Niu, L.; Zhang, R.; Hou, C. Research on Anti-interference Algorithm Based on FFT-Wavelet Threshold. In Proceedings of the 2020 7th International Forum on Electrical Engineering and Automation (IFEEA), Hefei, China, 25–27 September 2020. [Google Scholar]

- Han, Y.; Zhang, M.; Shen, L.; Wang, L. The Anti-Interference Algorithm of BPSK Spread Spectrum Signal Based on Generative Adversarial Networks. In Proceedings of the 2022 7th International Conference on Signal and Image Processing (ICSIP), Suzhou, China, 20–22 July 2022. [Google Scholar]

- Li, H.; Huo, Q.; Zheng, X.; Yan, S.; He, Y. High Dynamic GNSS Anti-Jamming Algorithms Based on Nuffling Widening and Depening. In Proceedings of the IEEE 4th Information Technology, Networking, Electronic and Automation Control Conference, Chongqing, China, 12–14 June 2020. [Google Scholar]

- Jianhua, C.; Naiping, C.; Panfeng, H. Adaptive anti jamming algorithm for GNSS software receiver. In Proceedings of the 2016 IEEE Information Technology, Networking, Electronic and Automation Control Conference, Chongqing, China, 20–22 May 2016. [Google Scholar]

- Zhong, W. Linear phase FIR Digital Filter Design Using Differential Evolution Algorithms. Master’s Thesis, University of Windsor, Windsor, ON, Canada, 2017. [Google Scholar]

- Guan, W.; Zheng, Z.; Chang, S.; Liu, Q.; Chen, X. A frequency-domain sparse multi-functional anti-jamming waveform design and processing method. In Proceedings of the IET International Radar Conference (IRC 2023), Chongqing, China, 3–5 December 2023. [Google Scholar]

- Ramanathan, R.; Soman, K.P.; Vidyapeetham, A. A Novel Methodology for Designing Linear Phase IIR Filters. Int. J. Recent Trends Eng. 2009, 1, 218. [Google Scholar]

- Kai, Z. Research on Fast Acquisition Method of High Dynamic Signals. Master’s Thesis, Xidian University, Xi’an, China, 2014. [Google Scholar]

- Cristallini, D.; Blazquez-Garcia, R.; Daniel, O’Hagan. K-space signal occupancy of Starlink signals and their applications in passive radar imaging. In Proceedings of the 2023 IEEE Radar Conference (RadarConf23), San Antonio, TX, USA, 1–5 May 2023. [Google Scholar]

- Jianjian, Y.; Ren, G.; Xuguo, Z. Frequency Domain Parallel Acquisition Algorithm Based on FFT. Comput. Eng. Appl. 2012, 48, 250–252. [Google Scholar]

- Jiao, X.; Wang, J.; Li, X. High Sensitivity GPS Acquisition Algorithm Based on Code Doppler Compensation. In Proceedings of the 2012 IEEE 11th International Conference on Signal Processing (ICSP 2012), Beijing, China, 21–25 October 2012. [Google Scholar]

- Zhou, C.; Wu, Z.; Cao, Y.; Xu, J.; Zhang, L.; Yang, L.; Guo, W. A novel unsupervised anti-intermittent sampling jamming method for intra-pulse and inter-pulse frequency agile radar. In Proceedings of the IET International Radar Conference (IRC 2023), Chongqing, China, 3–5 December 2023. [Google Scholar]

- Qiu, L.; Fan, Y. Smart Noise Jamming Suppression Method Based on Target Position Estimation. In Proceedings of the 2022 3rd International Conference on Computer Vision, Image and Deep Learning & International Conference on Computer Engineering and Applications (CVIDL & ICCEA), Changchun, China, 20–22 May 2022. [Google Scholar]

- Gang, X. Principles of GPS and Receiver Design; Publishing House of Electronics Industry: Beijing, China, 2009; p. 262. [Google Scholar]

- Yiming, F. A Survey on Low Earth Orbit Satellite Signal Acquisition and Tracking Technology. Radio Commun. Technol. 2023, 49, 816–825. [Google Scholar]

- Xunxiong, H. Research on Key Technologies of Beidou Third Generation Multifrequency Point Satellite Signal Acquisiton. Master’s Thesis, Guilin University of Electronic Technology, Guilin, China, 2022. [Google Scholar]

- Bhatt, H.S.; Garg, G. Comparative analysis of acquisition methods in digital forensics. In Proceedings of the 2021 Fourth International Conference on Computational Intelligence and Communication Technologies (CCICT), Sonepat, India, 3 July 2021. [Google Scholar]

- Kalita, S.; Kaushik, R.; Jajoo, M.; Sahu, P.P. Performance Enhancement of a Multichannel Uncoordinated Code Hopping DSSS Signaling Scheme Using Multipath Fading Compensator. J. Circuits Syst. Comput. 2016, 25, 1650145. [Google Scholar] [CrossRef]

- Cui, H.; Li, Z.; Dou, Z. Fast Acquisition Method of GPS Signal Based on FFT Cyclic Correlation. In Proceedings of the 13th International Conference on Wireless Communications, Networking and Mobile Computing (WiCOM 2017), Guilin, China, 21–23 August 2017. [Google Scholar]

- Guangyue, D.; Meili, L.; Feng’e, Y.; Xiaohong, W.; Xiaomeng, D.; Benlan, S. Study on synchronous method of multi-sensor data acquisition in space based on Single-bus digital temperature sensor. In Proceedings of the 2022 International Conference on Advanced Mechatronic Systems (ICAMechS), Toyama, Japan, 17–20 December 2022. [Google Scholar]

- Jiang, H.; Li, J.; Zhu, X.; Ou, G. Design and Validation of A Single Frequency GPS Software Receiver Acquisition and Tracking Method. In Proceedings of the 2017 IEEE 2nd Advanced Information Technology, Electronic and Automation Control Conference (IAEAC 2017), Chongqing, China, 25–26 March 2017. [Google Scholar]

- Zhang, S.; Wan, G.; Wang, S. 2017 IEEE 17th International Conference on Communication Technology (ICCT). In Proceedings of the 2023 3rd Asia-Pacific Conference on Communications Technology and Computer Science (ACCTCS), Shenyang, China, 25–27 February 2023. [Google Scholar]

- Lee, S.; Yoon, J.; Kang, S. Giga-sample Data Acquisition Method for High-speed DDR5 SDRAM. In Proceedings of the 2021 18th International SoC Design Conference (ISOCC), Jeju Island, Republic of Korea, 6–9 October 2021. [Google Scholar]

- Zhang, S.; Dai, Z.; He, H.; Zhang, W.; Liu, N.; Shi, C. A Study on One Fast Acquisition Method for DS/FH Hybrid Spread Spectrum Signal in Physical Layer of Aircraft Communication Network. In Proceedings of the 2022 International Symposium on Networks, Computers and Communications (ISNCC), Shenzhen, China, 19–22 July 2022. [Google Scholar]

- Pan, Y.; Zhang, T.; Zhang, G.; Luo, Z. A Novel Acquisition Algorithm Based on PMF-apFFT for BOC Modulated Signals. IEEE Access 2019, 7, 46686–46694. [Google Scholar] [CrossRef]

- Li, X.; Yingnan, C.; Bin, G. The Research on GPS Signal Acquisition Algorithm Based on Coherent Integration. In Proceedings of the 2020 39th Chinese Control Conference (CCC), Shenyang, China, 27–29 July 2020. [Google Scholar]

- Kai, C. RF and Microwave Wireless Systems; John Wiley & Sons: New York, NY, USA, 2004. [Google Scholar]

| Compared Items | FFT Frequency Domain Acquisition Method | FFT Fast Acquisition Method |

|---|---|---|

| Symbol rate | Can only be an integer multiple of the pseudocode period | Arbitrary proportional relationship |

| Pseudocode and symbol alignment | Necessary | Unnecessary |

| Accumulation method | Incoherent | Coherent |

| Cumulative length | Generally, 4 cycles | 4~8 cycles |

| Maximum value of Doppler frequency | ±100 kHz | ±250 kHz |

| Capture time | About 1 s | About 60 ms |

| Beam Pointing Angle (θ, φ) | Sidelobe Level Reduction (dB) | Gain (dBic) |

|---|---|---|

| (0°, 0°) | 5 | 15.00 |

| (20°, 0°) | 8 | 14.60 |

| (45°, 0°) | 3 | 14.89 |

| (65°, 0°) | 3 | 14.97 |

| (75°, 0°) | 7 | 14.63 |

| (75°, 30°) | 4.5 | 14.30 |

| (75°, 60°) | 1 | 14.57 |

| (75°, 90°) | 2.5 | 14.73 |

| (75°, 120°) | 2 | 14.71 |

| (75°, 150°) | 2 | 14.94 |

| (75°, 180°) | 1 | 14.92 |

| Simulation Parameters | Value | |

|---|---|---|

| Signal Parameters | RF carrier frequency | 2.29745 GHz |

| IF carrier frequency | 286.75 MHz | |

| Spreading code rate | 10.23 Mcps | |

| Code length | 1023 | |

| Symbol rate | 8 ksps | |

| Modulation | BPSK | |

| Carrier-to-noise ratio | 44 dBHz | |

| Simulation time | 100 s | |

| Dynamic Parameters | Initial distance | 2400 km |

| Initial velocity | 5 km/s | |

| Initial acceleration | 1.34 km/s2 | |

| Initial jerk | 98 m/s3 | |

| Bit Error Rate Pb | Soft Verdict Coding Gain (dB) | Hard Verdict Coding Gain (dB) |

|---|---|---|

| 10−3 | 3.24 | 5.15 |

| 10−4 | 4.17 | 6.06 |

| 10−5 | 4.68 | 6.50 |

| Upper bound | 5.00 | 7.00 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Shen, H.; Li, J.; Wang, Z. Design and Simulation of Low-Orbit Satellite Broadcast Signal Receiving and Processing Terminal. Electronics 2024, 13, 3270. https://doi.org/10.3390/electronics13163270

Shen H, Li J, Wang Z. Design and Simulation of Low-Orbit Satellite Broadcast Signal Receiving and Processing Terminal. Electronics. 2024; 13(16):3270. https://doi.org/10.3390/electronics13163270

Chicago/Turabian StyleShen, Haoran, Jian Li, and Ziwei Wang. 2024. "Design and Simulation of Low-Orbit Satellite Broadcast Signal Receiving and Processing Terminal" Electronics 13, no. 16: 3270. https://doi.org/10.3390/electronics13163270

APA StyleShen, H., Li, J., & Wang, Z. (2024). Design and Simulation of Low-Orbit Satellite Broadcast Signal Receiving and Processing Terminal. Electronics, 13(16), 3270. https://doi.org/10.3390/electronics13163270