Transient Synchronous Stability Analysis of Grid-Following Converter Considering Outer-Loop Control with Current Limiting

Abstract

:1. Introduction

2. Transient Synchronization Modeling of VSC

2.1. Second-Order Synchronization Model of VSC

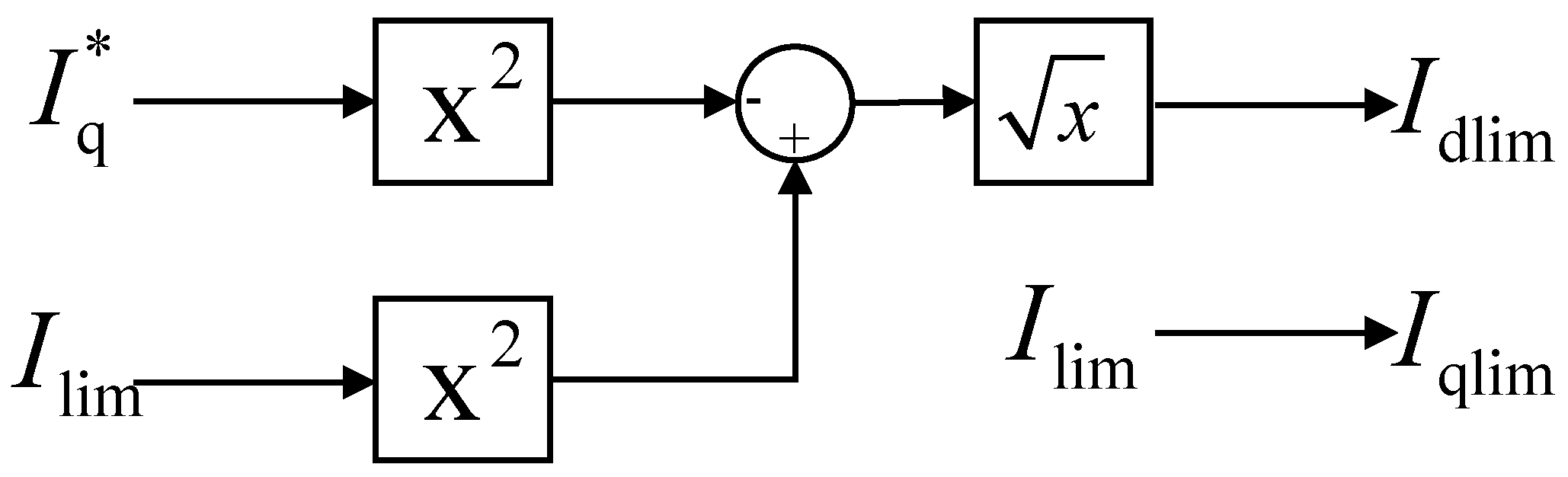

2.2. Outer-Loop Control of VSC

3. The Necessity of Considering Outer-Loop Control

4. Synchronous Stability of VSC Considering Outer-Loop Control

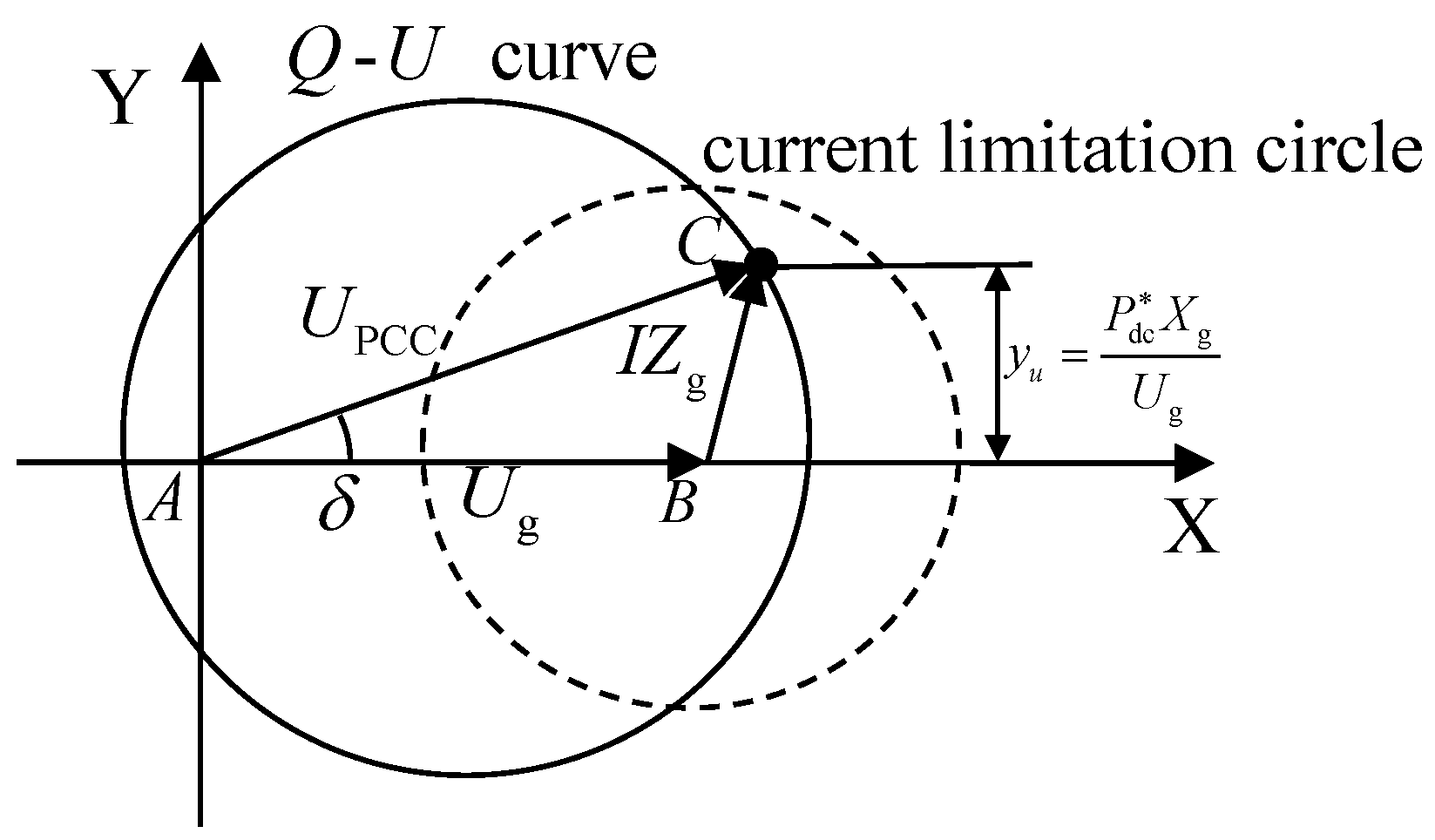

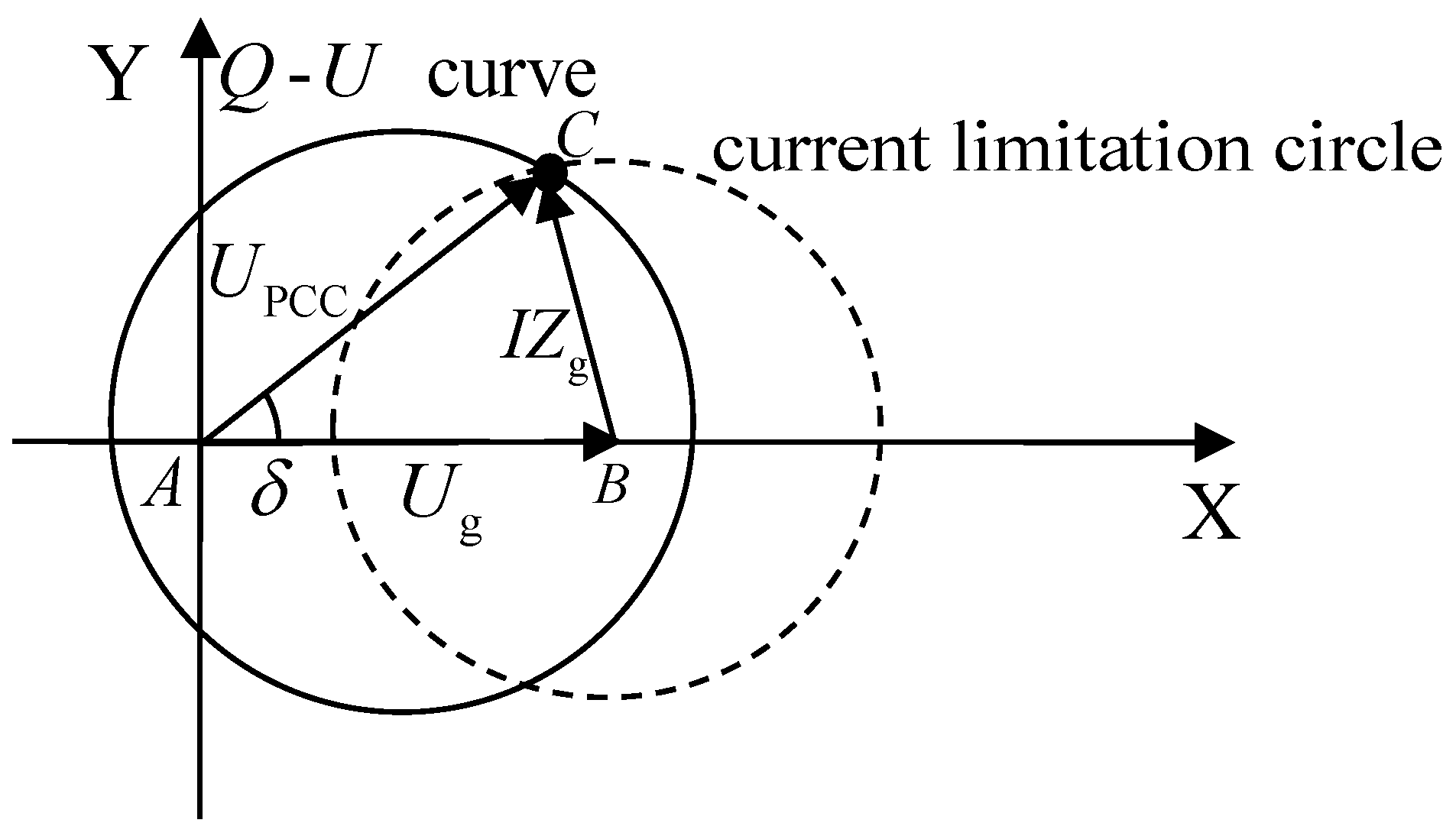

4.1. Synchronization Equation of PLL

4.2. SEP Analysis

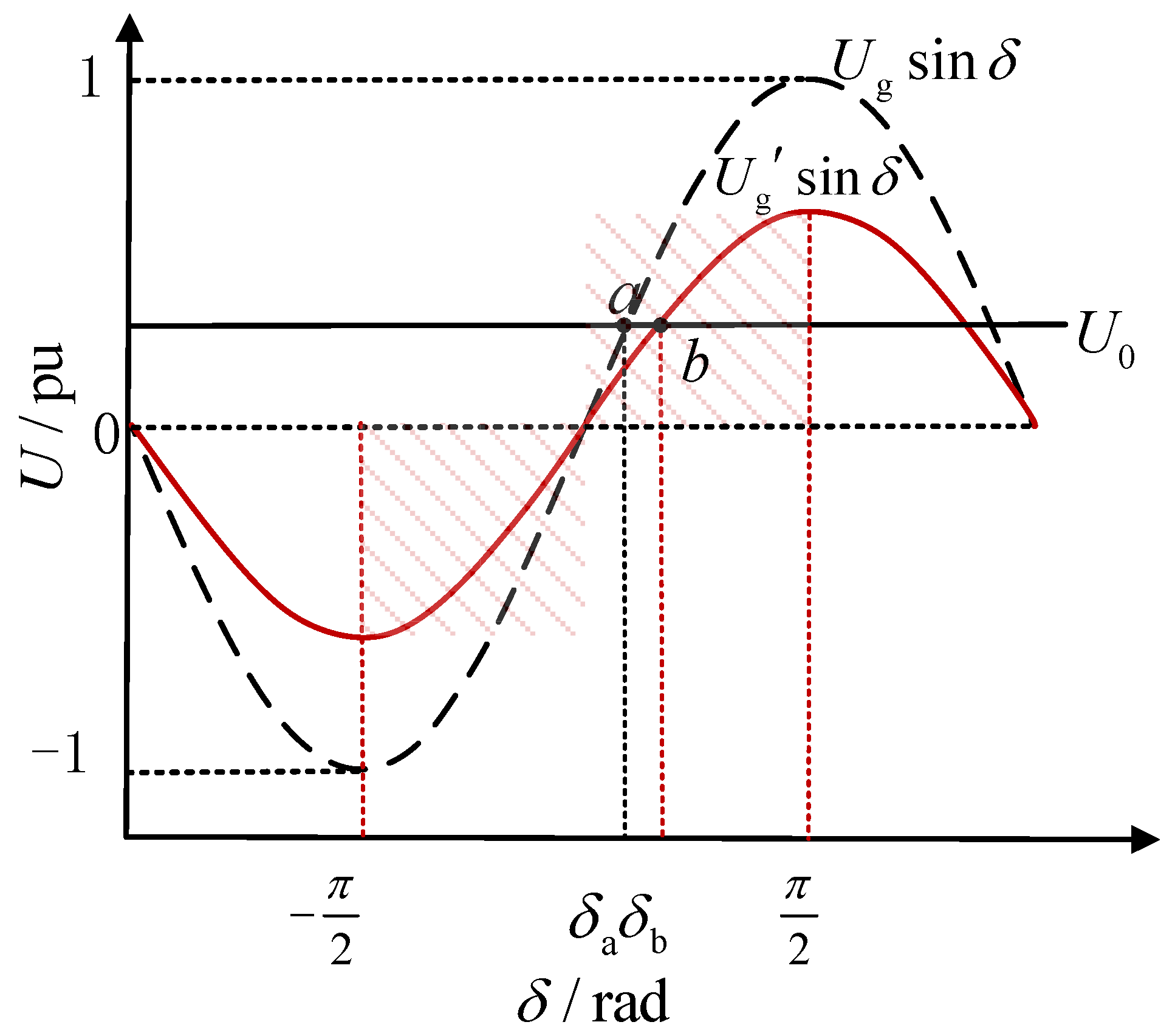

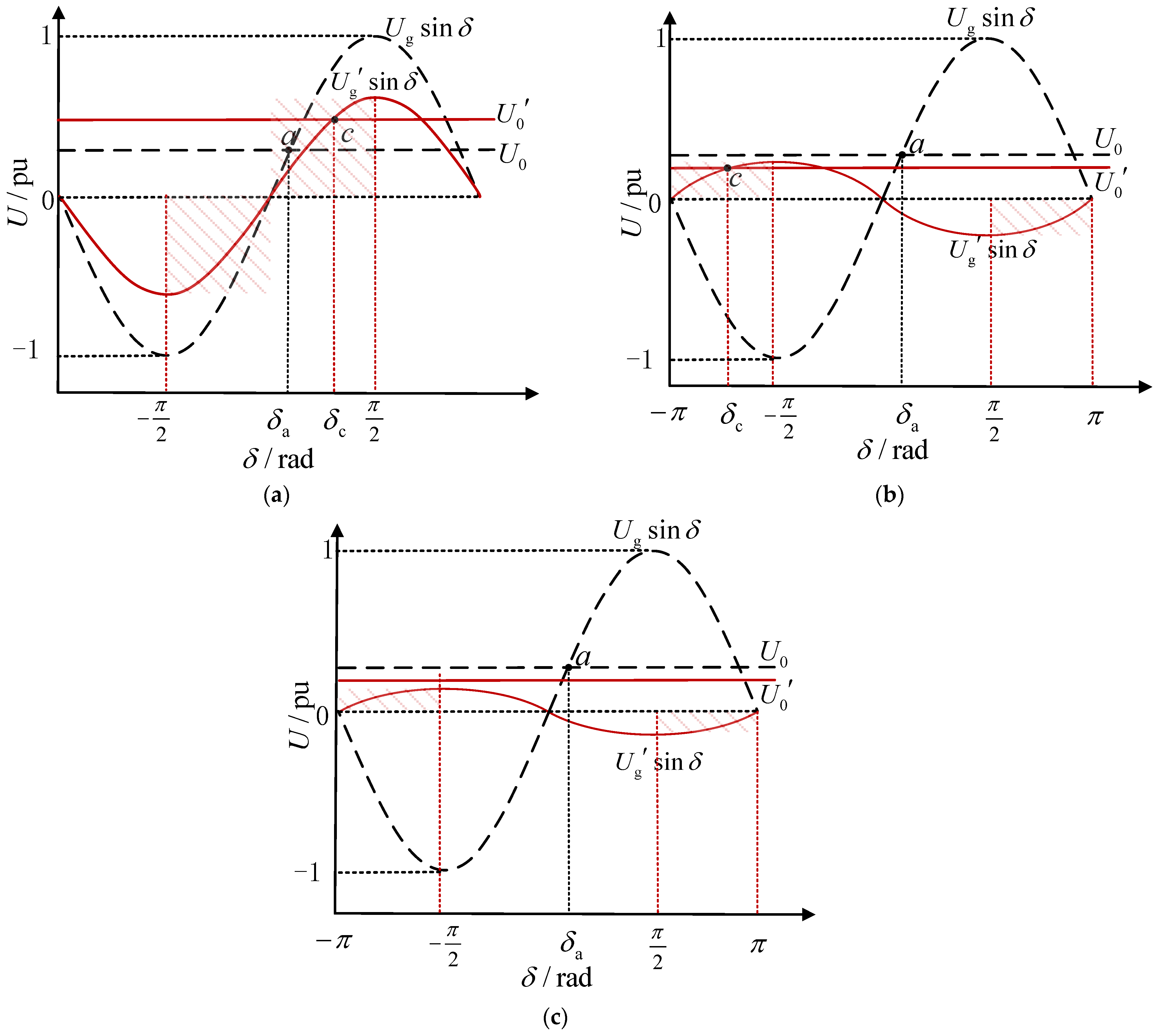

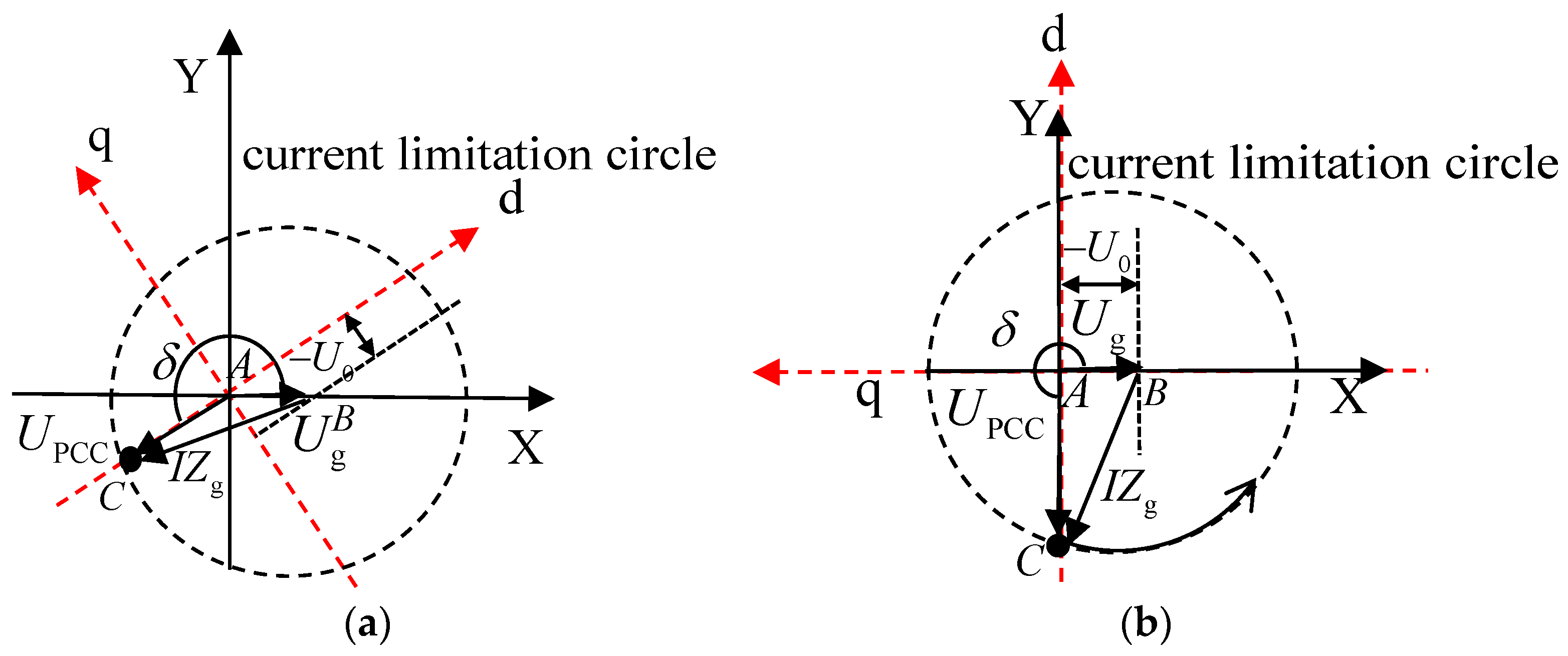

4.3. Effect of Outer-Loop Control on the Synchronization Process

- (1)

- Slight drop in grid voltage

- (2)

- Moderate drop in grid voltage

- (3)

- Severe drop in grid voltage

5. Case Study

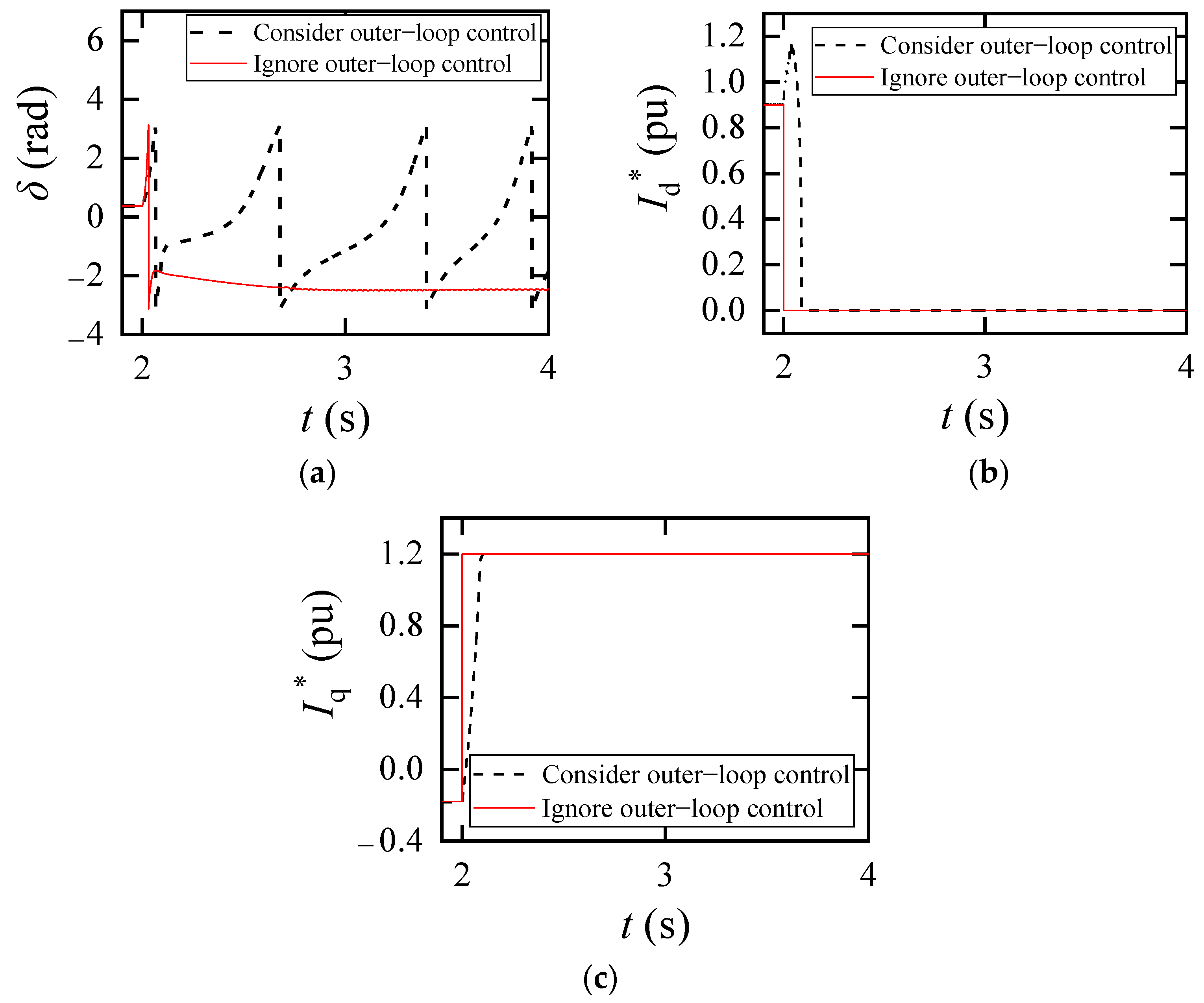

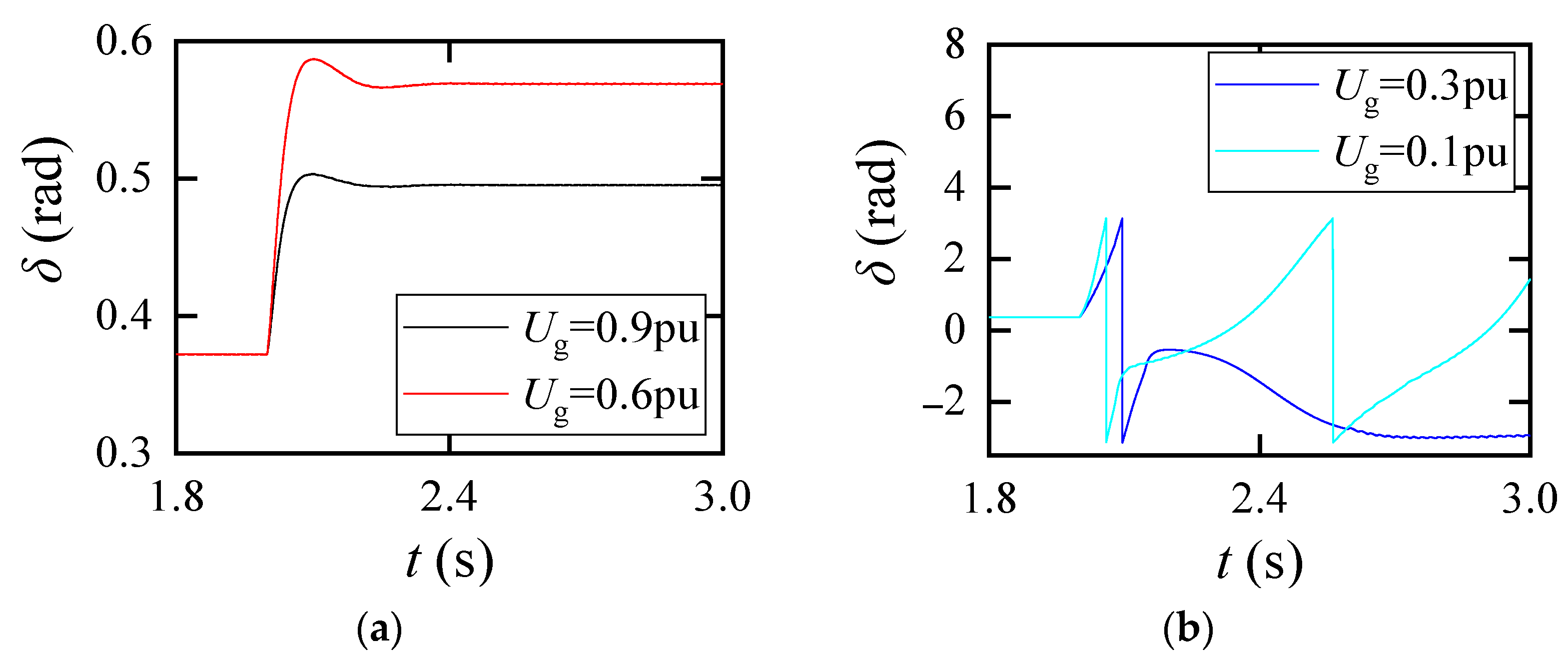

5.1. Impact of Outer-Loop Control on the Transient Synchronization Stability of VSC

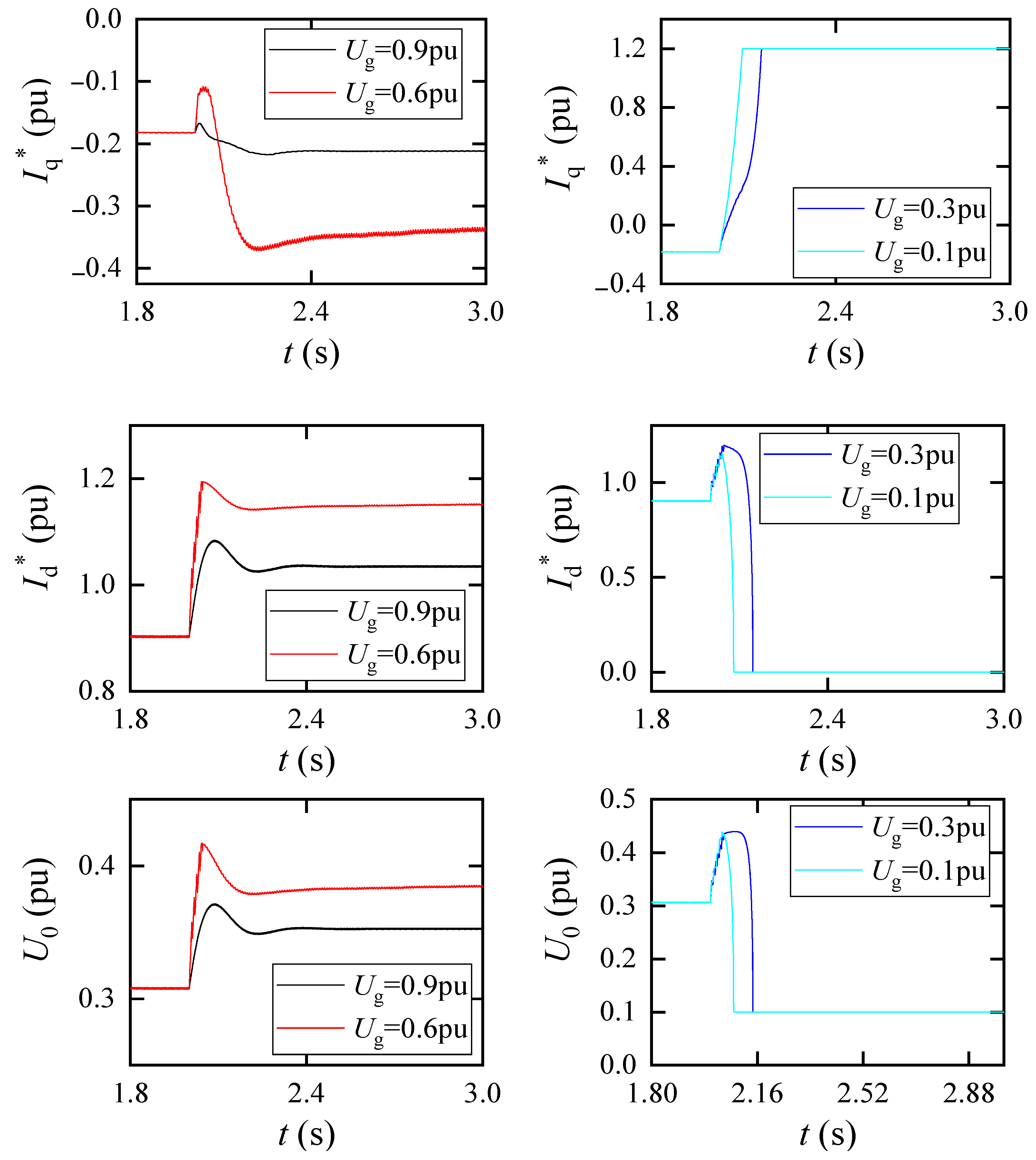

5.2. Changes in SEP

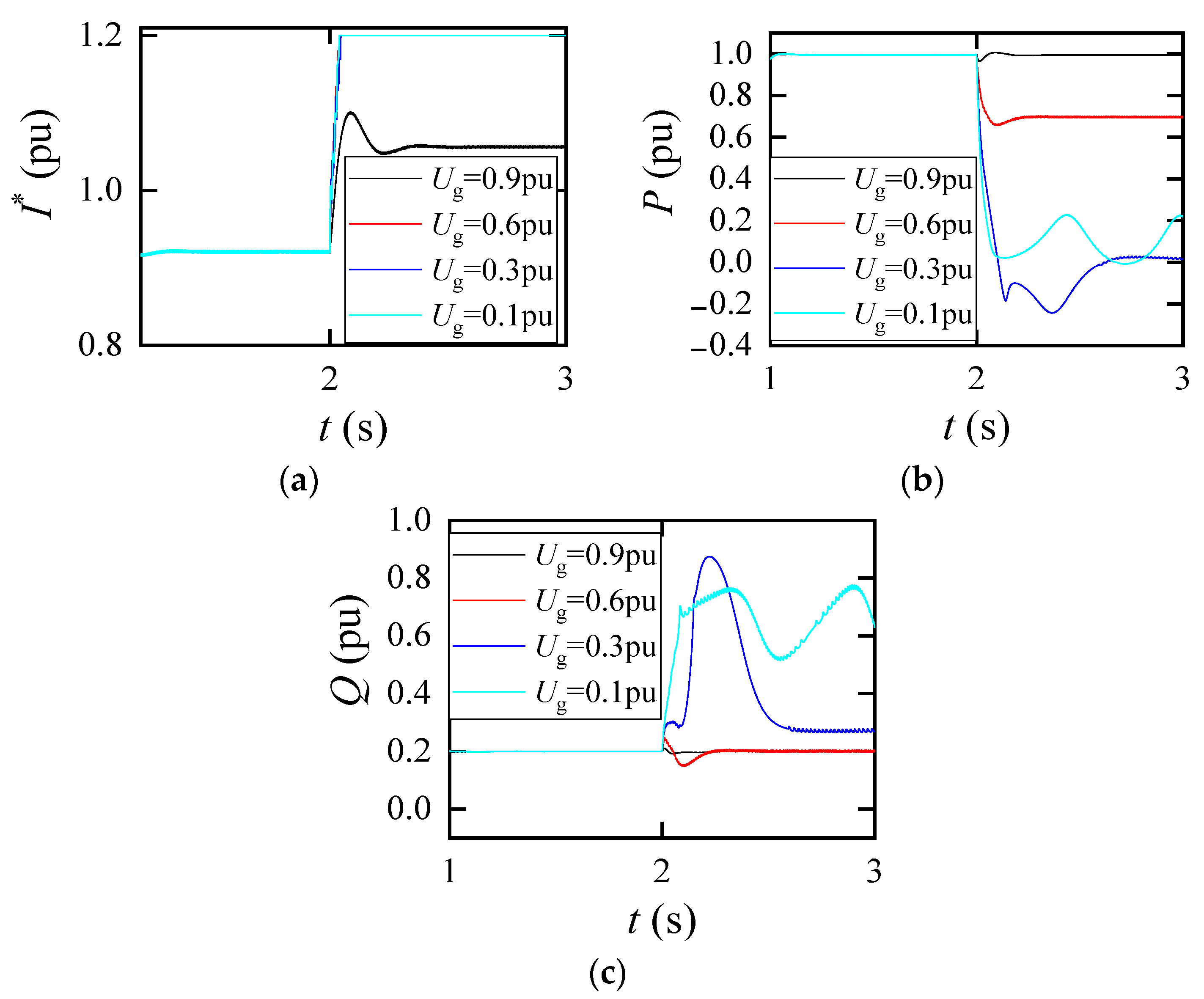

5.3. System Dynamics Considering Outer-Loop Control

5.4. Impact of Current Saturation Limits

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Li, X.; Liu, S.; Tian, Z.; Huang, M.; Sun, P.; Zha, X.; Hu, P. A Conservatism Improved Transient Stability Analysis of Grid-Following Converters Based on the Proposed Elliptic-Equal Area Criterion. IEEE Trans. Power Deliv. 2024, 39, 1110–1123. [Google Scholar] [CrossRef]

- Zhang, Y.; Zhang, C.; Yang, R.; Molinas, M.; Cai, X. Current-Constrained Power-Angle Characterization Method for Transient Stability Analysis of Grid-Forming Voltage Source Converters. IEEE Trans. Energy Convers. 2023, 38, 1338–1349. [Google Scholar] [CrossRef]

- Zhao, C.; Sun, D.; Duan, X.; Nian, H. Current Reference Optimization for Inverter-Based Resources to Mitigate Grid Voltage Unbalance Factor. IEEE Trans. Power Syst. 2024, 39, 6103–6106. [Google Scholar] [CrossRef]

- Patel, M. Opportunities for Standardizing Response, Modeling and Analysis of Inverter-Based Resources for Short Circuit Studies. IEEE Trans. Power Deliv. 2021, 36, 2408–2415. [Google Scholar] [CrossRef]

- Xing, G.; Chen, L.; Min, Y.; Tang, Y.; Li, Y.; Xu, S. Effects of PLL Frequency Limiters on Synchronization Stability of Grid Connected VSC and Strategy to Realize Global Stability. IEEE Trans. Energy Convers. 2023, 38, 2096–2107. [Google Scholar] [CrossRef]

- Fan, L.; Miao, Z. Root cause analysis of AC overcurrent in July 2020 San Fernando disturbance. IEEE Trans. Power Syst. 2021, 36, 4892–4895. [Google Scholar] [CrossRef]

- Taul, M.G.; Wang, X.; Davari, P.; Blaabjerg, F. An Overview of Assessment Methods for Synchronization Stability of Grid-Connected Converters Under Severe Symmetrical Grid Faults. IEEE Trans. Power Electron. 2019, 34, 9655–9670. [Google Scholar] [CrossRef]

- Wu, H.; Wang, X. Design-Oriented Transient Stability Analysis of PLL-Synchronized Voltage-Source Converters. IEEE Trans. Power Electron. 2020, 35, 3573–3589. [Google Scholar] [CrossRef]

- Wang, Z.; Guo, L.; Li, X.; Pang, X.; Li, X.; Zhou, X.; Wang, C. PLL Synchronization Transient Stability Analysis of a Weak-Grid Connected VSC During Asymmetric Faults. IEEE Trans. Power Electron. 2024, 39, 2140–2154. [Google Scholar] [CrossRef]

- He, X.; Geng, H. PLL Synchronization Stability of Grid-Connected Multiconverter Systems. IEEE Trans. Ind. Appl. 2022, 58, 830–842. [Google Scholar] [CrossRef]

- Pei, J.; Yao, J.; Liu, Y.; Chen, S.; Sun, P.; Huang, S. Modelling and Transient Synchronization Stability Analysis for PLL-Based Renewable Energy Generator Considering Sequential Switching Schemes. IEEE Trans. Power Electron. 2021, 37, 2165–2179. [Google Scholar] [CrossRef]

- Tang, Y.; Tian, Z.; Zha, X.; Li, X.; Huang, M.; Sun, J. An Improved Equal Area Criterion for Transient Stability Analysis of Converter-Based Microgrid Considering Nonlinear Damping Effect. IEEE Trans. Power Electron. 2022, 37, 11272–11284. [Google Scholar] [CrossRef]

- Luo, Y.; Yao, J.; Chen, Z.; Huang, S.; Chen, S.; Zhang, Q.; Qin, Z. Transient synchronous stability analysis and enhancement control strategy of a PLL-based VSC system during asymmetric grid faults. Prot. Control Mod. Power Syst. 2023, 8, 35. [Google Scholar] [CrossRef]

- Zhang, Y.; Zhang, C.; Cai, X. Large-Signal Grid-Synchronization Stability Analysis of PLL-Based VSCs Using Lyapunov’s Direct Method. IEEE Trans. Power Syst. 2022, 37, 788–791. [Google Scholar] [CrossRef]

- Li, X.; Wang, Z.; Liu, Y.; Wang, Z.; Zhu, L.; Guo, L.; Zhang, C.; Zhu, J.; Wang, C. The Largest Estimated Domain of Attraction and Its Applications for Transient Stability Analysis of PLL Synchronization in Weak-Grid-Connected VSCs. IEEE Trans. Power Syst. 2023, 38, 4107–4121. [Google Scholar] [CrossRef]

- Hu, B.; Zhao, C.; Sahoo, S.; Wu, C.; Chen, L.; Nian, H.; Blaabjerg, F. Synchronization Stability Enhancement of Grid-Following Converter Under Inductive Power Grid. IEEE Trans. Energy Convers. 2023, 38, 1485–1488. [Google Scholar] [CrossRef]

- Pan, D.; Wang, X.; Liu, F.; Shi, R. Transient Stability of Voltage-Source Converters With Grid-Forming Control: A Design-Oriented Study. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 8, 1019–1033. [Google Scholar] [CrossRef]

- Li, Y.; Wang, X.; Guo, J.; Wu, H.; Zhao, B.; Wang, S.; Wu, G.; Wang, T. PLL Synchronization Stability Analysis of MMC-Connected Wind Farms Under High-Impedance AC Faults. IEEE Trans. Power Syst. 2021, 36, 2251–2261. [Google Scholar] [CrossRef]

- Chen, J.; Si, W.; Liu, M.; Milano, F. On the Impact of the Grid on the Synchronization Stability of Grid-Following Converters. IEEE Trans. Power Syst. 2023, 38, 4970–4973. [Google Scholar] [CrossRef]

- He, X.; Geng, H.; Xi, J.; Guerrero, J.M. Resynchronization Analysis and Improvement of Grid-Connected VSCs During Grid Faults. IEEE J. Emerg. Sel. Top. Power Electron. 2021, 9, 438–450. [Google Scholar] [CrossRef]

- Zhang, C.; Molinas, M.; Li, Z.; Cai, X. Synchronizing Stability Analysis and Region of Attraction Estimation of Grid-Feeding VSCs Using Sum-of-Squares Programming. Front. Energy Res. 2020, 8, 56. [Google Scholar] [CrossRef]

- Wang, T.; Ji, T.; Jiao, D.; Li, Y.; Wang, Z. Transient synchronization stability analysis of PLL-based VSC using Lyapunov’s direct method. Int. J. Electr. Power Energy Syst. 2022, 141, 108135. [Google Scholar] [CrossRef]

- Guo, X.; Lin, X.; Huang, G.; Quan, X.; Chen, S. Transient Stability Analysis and Controller Optimization of Grid-Connected Converter Under Input Power Variation. In Proceedings of the 2021 International Conference on Power System Technology (POWERCON), Haikou, China, 8–9 December 2021; pp. 1606–1611. [Google Scholar]

- Taul, M.G.; Wu, C.; Chou, S.-F.; Blaabjerg, F. Optimal Controller Design for Transient Stability Enhancement of Grid-Following Converters Under Weak-Grid Conditions. IEEE Trans. Power Electron. 2021, 36, 10251–10264. [Google Scholar] [CrossRef]

- He, X.; Geng, H. Transient Stability of Power Systems Integrated with Inverter-Based Generation. IEEE Trans. Power Syst. 2021, 36, 553–556. [Google Scholar] [CrossRef]

- Li, X.; Tian, Z.; Zha, X.; Sun, P.; Hu, Y.; Huang, M.; Sun, J. Nonlinear Modeling and Stability Analysis of Grid-Tied Paralleled-Converters Systems Based on the Proposed Dual-Iterative Equal Area Criterion. IEEE Trans. Power Electron. 2023, 38, 7746–7759. [Google Scholar] [CrossRef]

- Si, W.; Chen, J.; Zhang, C.; Liu, M. Influence mechanism of DC-bus voltage on synchronization stability of grid-following converter. J. Shanghai Jiao Tong Univ. 2024, 1–19. [Google Scholar] [CrossRef]

- Rokrok, E.; Qoria, T.; Bruyere, A.; Francois, B.; Guillaud, X. Transient Stability Assessment and Enhancement of Grid-Forming Converters Embedding Current Reference Saturation as Current Limiting Strategy. IEEE Trans. Power Syst. 2022, 37, 1519–1531. [Google Scholar] [CrossRef]

- Gonzalez-Torres, J.C.; Damm, G.; Costan, V.; Benchaib, A.; Lamnabhi-Lagarrigue, F. A Novel Distributed Supplementary Control of Multi-Terminal VSC-HVDC Grids for Rotor Angle Stability Enhancement of AC/DC Systems. IEEE Trans. Power Syst. 2021, 36, 623–634. [Google Scholar] [CrossRef]

- Zheng, T.; Lv, W.; Wu, Q.; Li, R.; Liu, X.; Zhang, C.; Xu, L. An Integrated Control and Protection Scheme Based on FBSM-MMC Active Current Limiting Strategy for DC Distribution Network. IEEE J. Emerg. Sel. Top. Power Electron. 2021, 9, 2632–2642. [Google Scholar] [CrossRef]

| Outer-Loop Control | Changes in the PLL Equation | Changes in SEP | Transient Synchronization Stability |

|---|---|---|---|

| Constant DC voltage control and constant reactive power control | Unchanged | Unchanged | The system achieves synchronization under active power constraint and reactive power constraint. |

| Current-limiting control and constant reactive power control | Unchanged | Unchanged | The system achieves synchronization under reactive power constraint and current limiting constraint. |

| Current-limiting control | Changed | Changed | If , the system operates under current limit constraints, there is a risk of instability, and the stability decreases with the increase in . |

| , the absence of SEP, synchronous instability. |

| Parameter | Value (in pu If Not Specified) |

|---|---|

| Rated active power Pn | 2 MW |

| Reference AC voltage Un | 230 kV |

| Reference frequency fn | 50 Hz |

| Rated DC voltage Vdc | 1.45 kV |

| DC capacity Cdc | 0.015 F |

| Filter inductance Lf | 0.44 |

| Grid inductance Lg | 0.36 |

| Grid resistance Rg | 0.08 |

| DC voltage control coefficient | Kpdc = 1, Kidc = 50 |

| Reactive power control coefficient | KpQ = 1, KiQ = 50 |

| Current control coefficient | Kpi = 1, Kii = 20 |

| PLL control coefficient | Kppll = 50, Kipll = 100 |

| Current Saturation Limit/pu | Critical Grid Voltage Drop Amplitude/pu |

|---|---|

| 1.0 | 0.86 |

| 1.2 | 0.85 |

| 1.4 | 0.83 |

| 1.6 | 0.80 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chen, L.; Zhu, L.; Liu, Y.; Ye, N.; Hu, Y.; Guan, L. Transient Synchronous Stability Analysis of Grid-Following Converter Considering Outer-Loop Control with Current Limiting. Electronics 2024, 13, 3337. https://doi.org/10.3390/electronics13163337

Chen L, Zhu L, Liu Y, Ye N, Hu Y, Guan L. Transient Synchronous Stability Analysis of Grid-Following Converter Considering Outer-Loop Control with Current Limiting. Electronics. 2024; 13(16):3337. https://doi.org/10.3390/electronics13163337

Chicago/Turabian StyleChen, Leke, Lin Zhu, Yang Liu, Nan Ye, Yonghao Hu, and Lin Guan. 2024. "Transient Synchronous Stability Analysis of Grid-Following Converter Considering Outer-Loop Control with Current Limiting" Electronics 13, no. 16: 3337. https://doi.org/10.3390/electronics13163337