Analysis of the Second-Order NS SAR ADC Performance Enhancement Based on Active Gain

Abstract

:1. Introduction

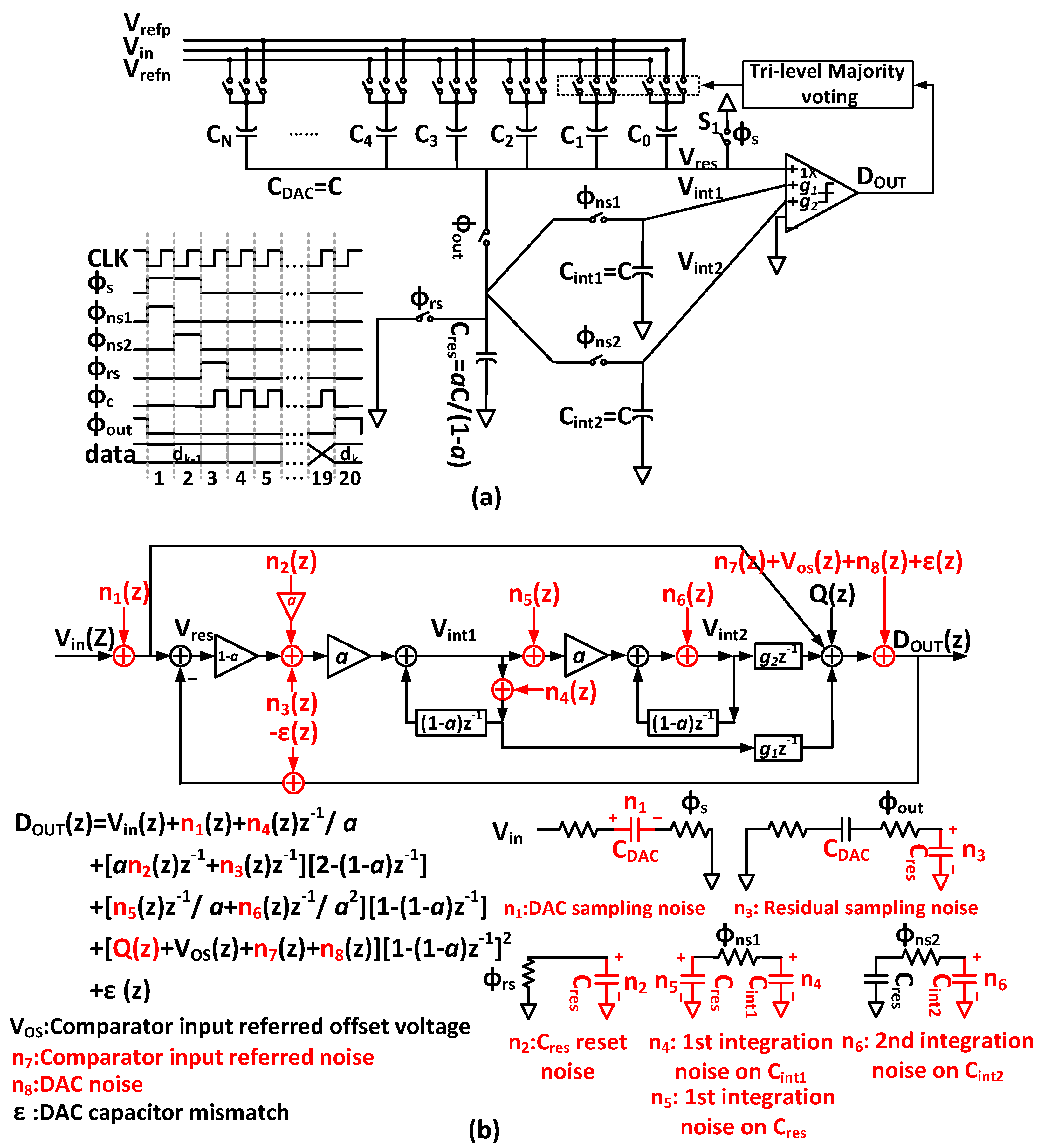

2. Mathematical Analysis of Previous Second-Order Fully-Passive NS SAR ADC

3. The Proposed Second-Order NS SAR ADC

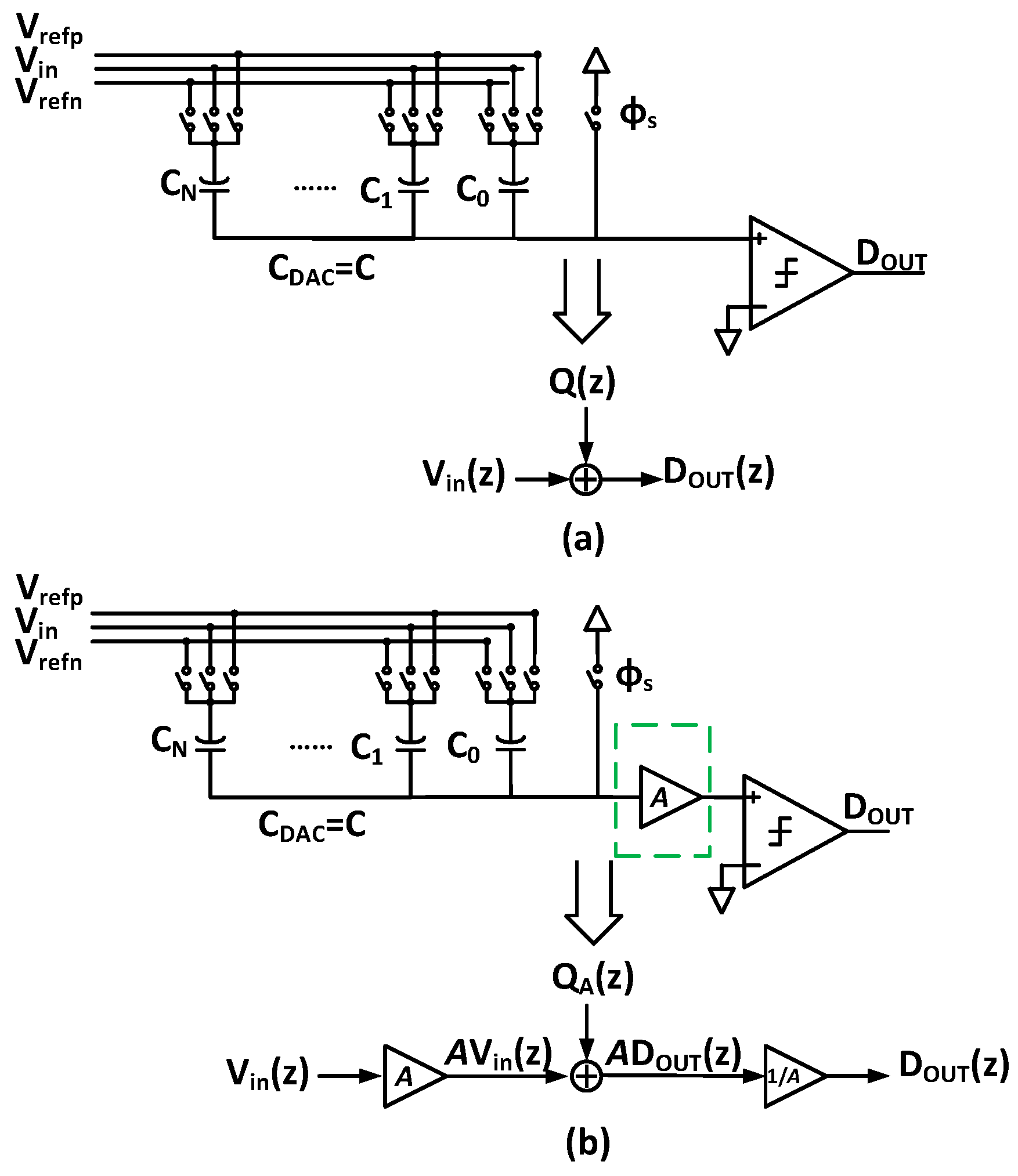

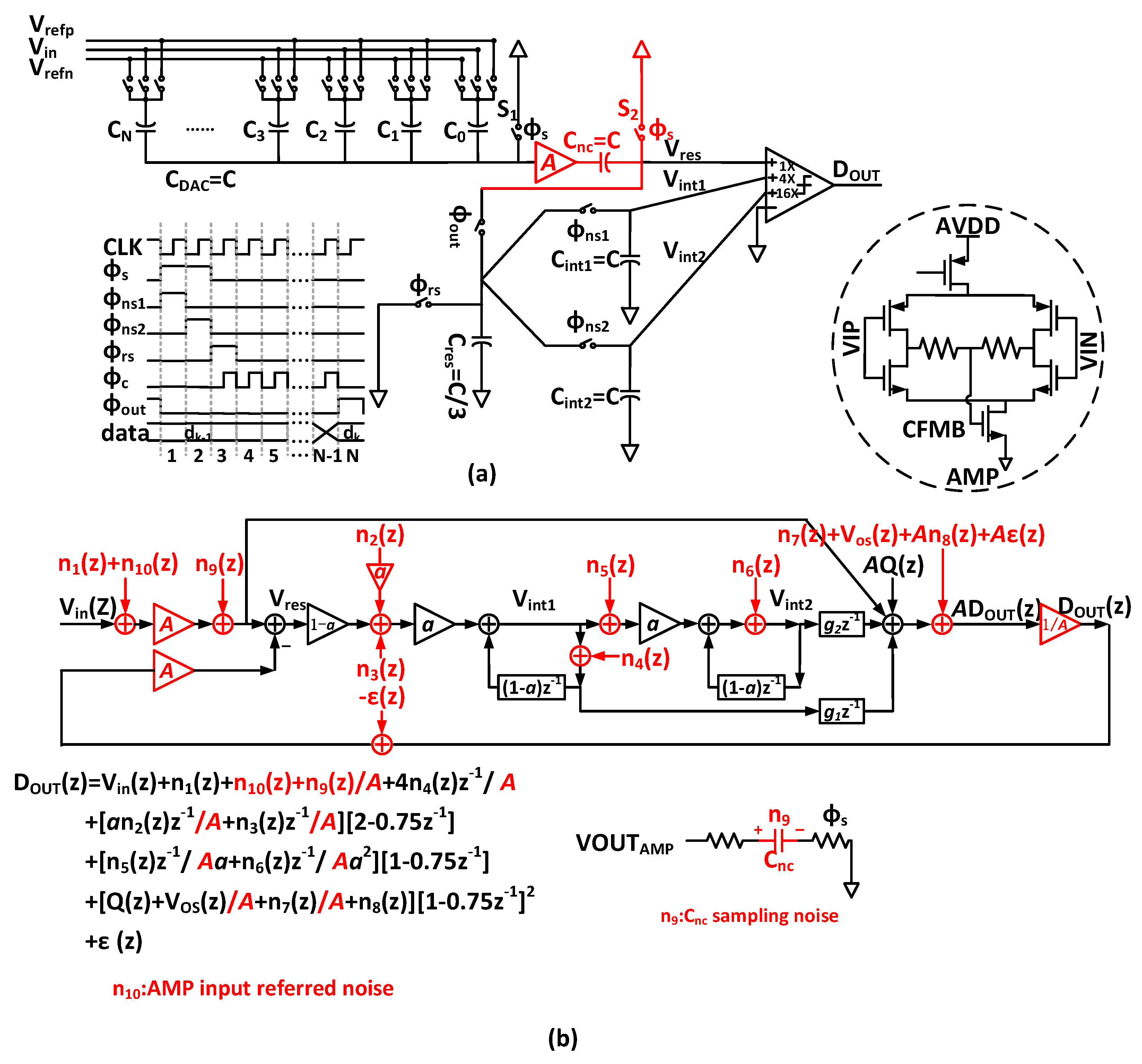

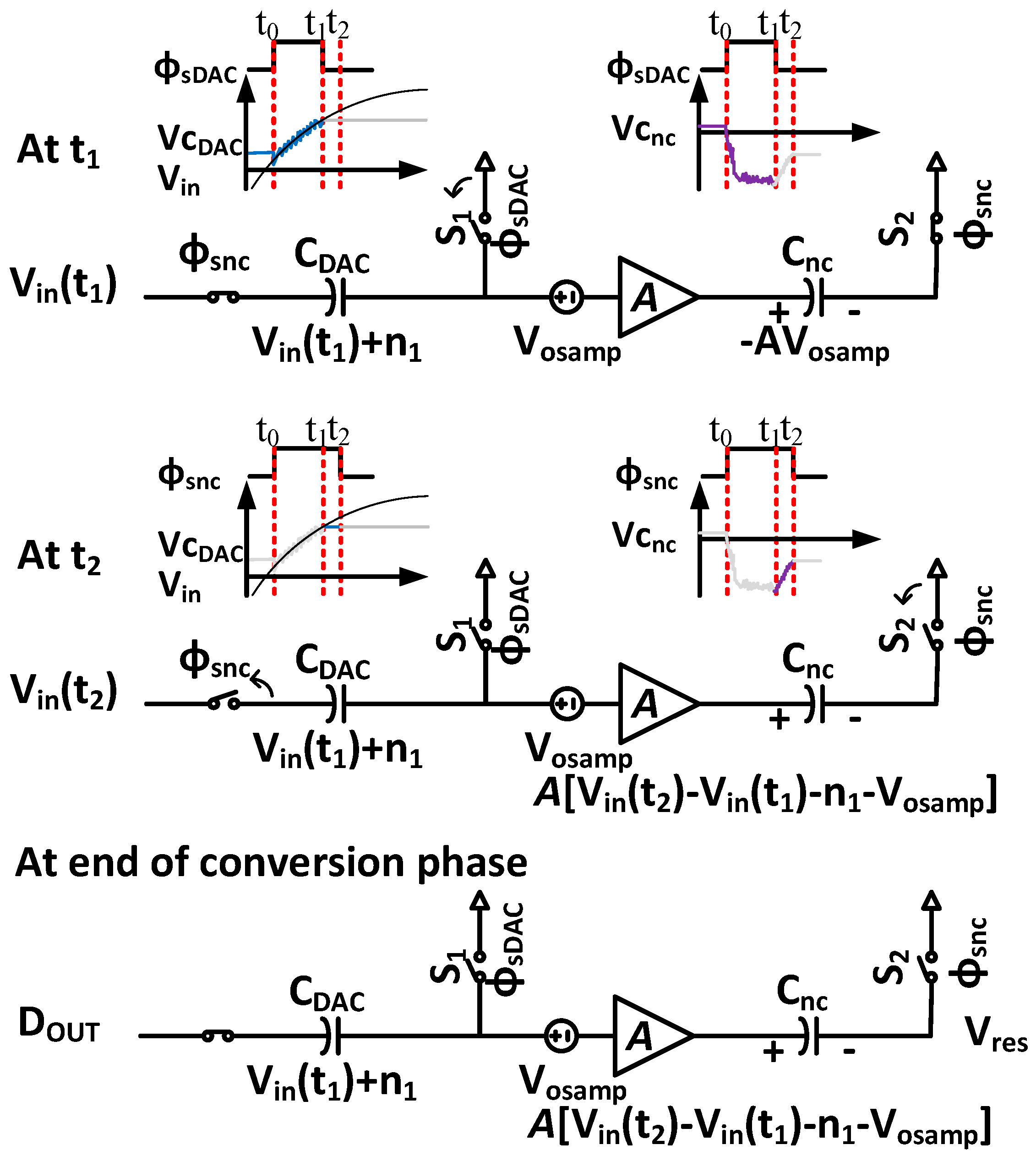

3.1. The Second-Order NS SAR ADC Based on Active Gain

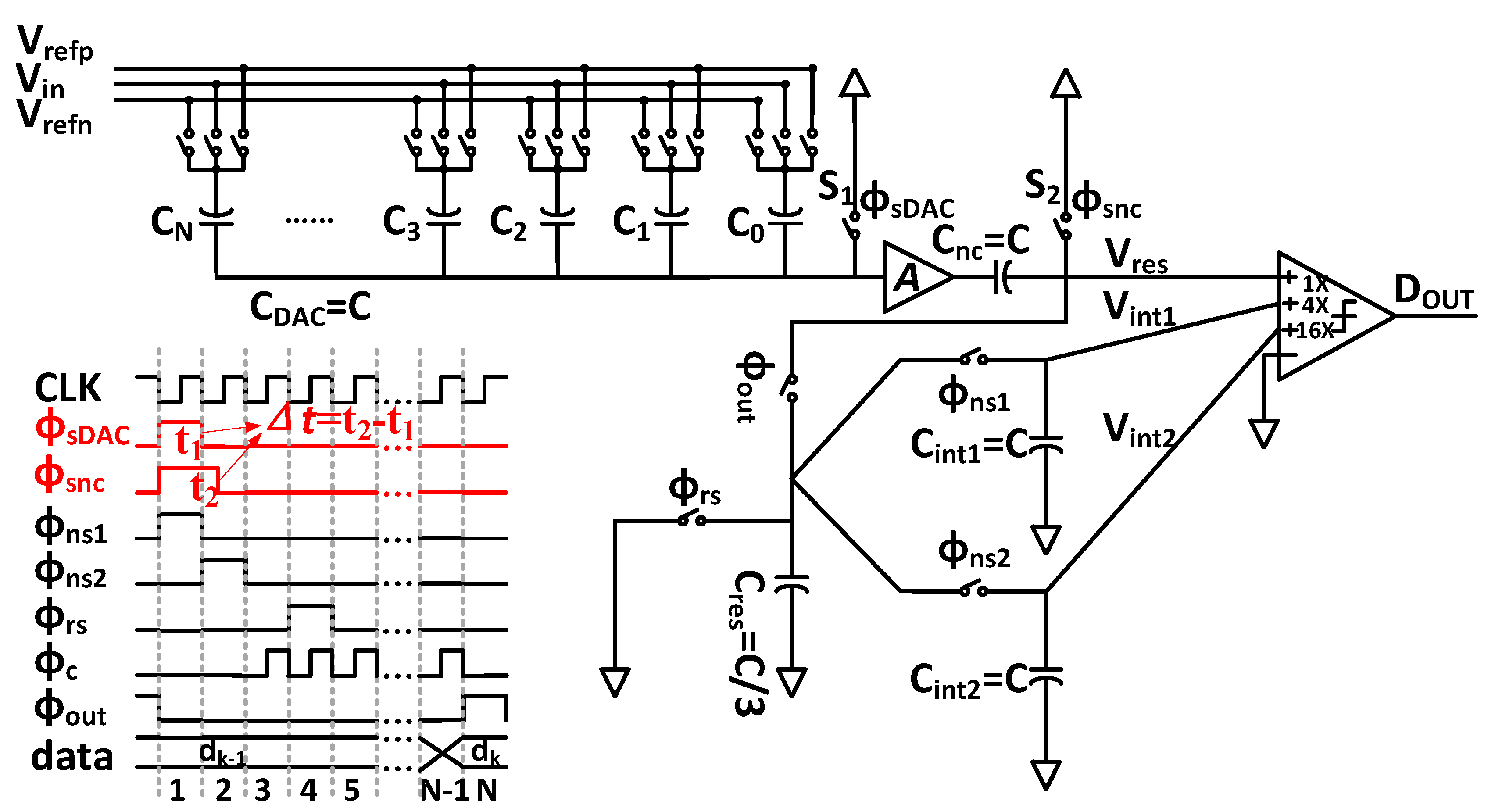

3.2. Improved Second-Order NS SAR ADC Based on Active Gain

3.3. The Values of A and Δt/τ

3.4. Improved Sampling Speed

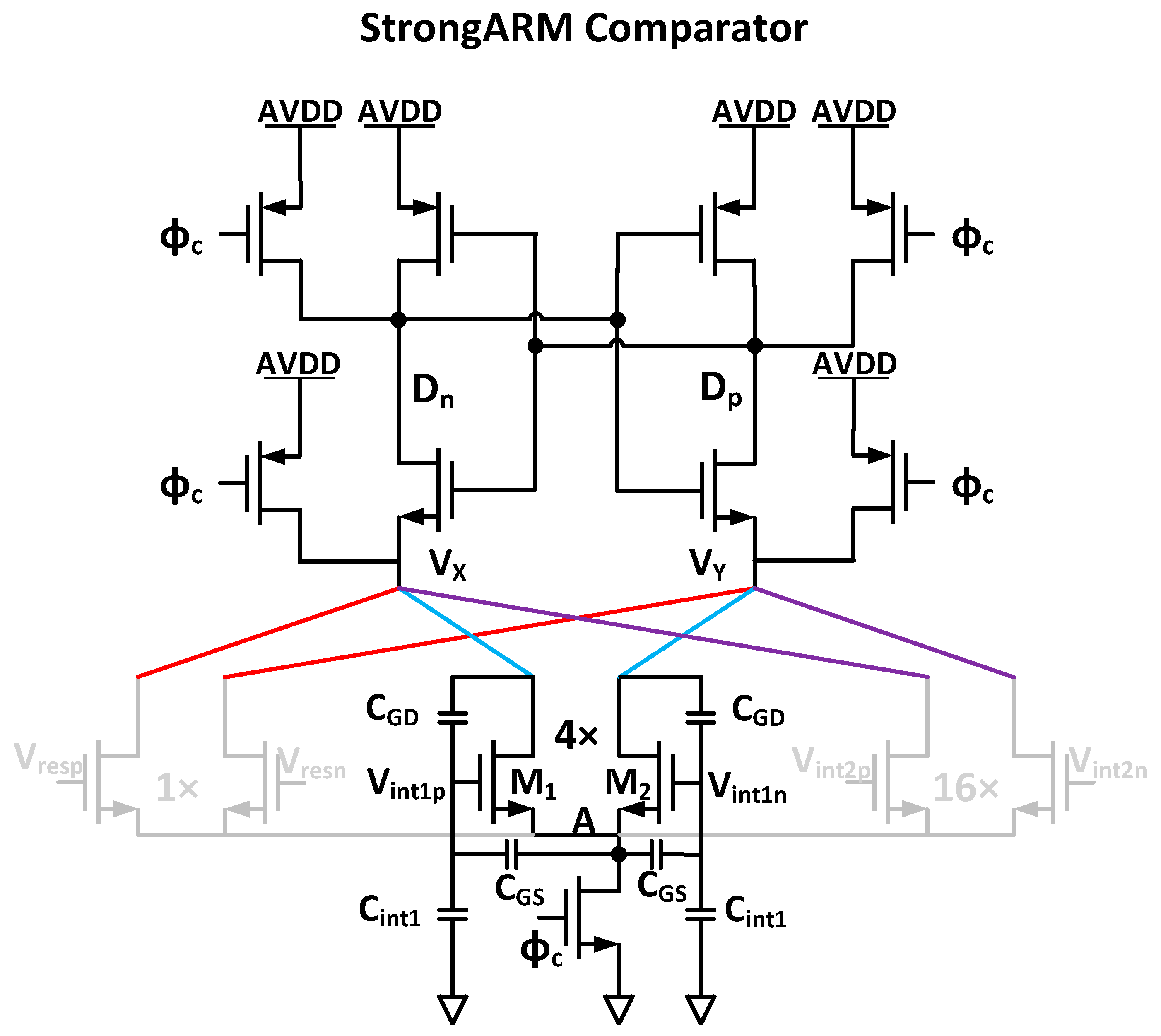

3.5. Kickback Noise

4. Performance Comparison

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Elzakker, M.v.; Tuijl, E.v.; Geraedts, P.; Schinkel, D.; Klumperink, E.A.M.; Nauta, B. A 10-bit Charge-Redistribution ADC Consuming 1.9 μW at 1 MS/s. IEEE J. Solid-State Circuits 2010, 45, 1007–1015. [Google Scholar] [CrossRef]

- Liu, C.C.; Chang, S.J.; Huang, G.Y.; Lin, Y.Z.; Huang, C.M. A 1V 11fJ/conversion-step 10bit 10MS/s asynchronous SAR ADC in 0.18µm CMOS. In Proceedings of the 2010 Symposium on VLSI Circuits, Honolulu, HI, USA, 16–18 June 2010; pp. 241–242. [Google Scholar]

- Shen, Y.; Tang, X.; Shen, L.; Zhao, W.; Xin, X.; Liu, S.; Zhu, Z.; Sathe, V.S.; Sun, N. A 10-bit 120-MS/s SAR ADC With Reference Ripple Cancellation Technique. IEEE J. Solid-State Circuits 2020, 55, 680–692. [Google Scholar] [CrossRef]

- Xu, D.G.; Xu, K.K.; Xu, S.L.; Liu, L.; Liu, T. A System-Level Correction SAR ADC with Noise-Tolerant Technique. J. Circuits Syst. Comput. 2018, 27, 1850202. [Google Scholar] [CrossRef]

- Obata, K.; Matsukawa, K.; Miki, T.; Tsukamoto, Y.; Sushihara, K. A 97.99 dB SNDR, 2 kHz BW, 37.1 µW noise-shaping SAR ADC with dynamic element matching and modulation dither effect. In Proceedings of the 2016 IEEE Symposium on VLSI Circuits (VLSI-Circuits), Honolulu, HI, USA, 15–17 June 2016; pp. 1–2. [Google Scholar]

- Shu, Y.S.; Kuo, L.T.; Lo, T.Y. An Oversampling SAR ADC With DAC Mismatch Error Shaping Achieving 105 dB SFDR and 101 dB SNDR Over 1 kHz BW in 55 nm CMOS. IEEE J. Solid-State Circuits 2016, 51, 2928–2940. [Google Scholar] [CrossRef]

- Chen, Z.; Miyahara, M.; Matsuzawa, A. A 2nd order fully-passive noise-shaping SAR ADC with embedded passive gain. In Proceedings of the 2016 IEEE Asian Solid-State Circuits Conference (A-SSCC), Toyama, Japan, 7–9 November 2016; pp. 309–312. [Google Scholar]

- Li, S.; Qiao, B.; Gandara, M.; Pan, D.Z.; Sun, N. A 13-ENOB Second-Order Noise-Shaping SAR ADC Realizing Optimized NTF Zeros Using the Error-Feedback Structure. IEEE J. Solid-State Circuits 2018, 53, 3484–3496. [Google Scholar] [CrossRef]

- Fredenburg, J.A.; Flynn, M.P. A 90-MS/s 11-MHz-Bandwidth 62-dB SNDR Noise-Shaping SAR ADC. IEEE J. Solid-State Circuits 2012, 47, 2898–2904. [Google Scholar] [CrossRef]

- Guo, W.; Zhuang, H.; Sun, N. A 13b-ENOB 173dB-FoM 2nd-order NS SAR ADC with passive integrators. In Proceedings of the 2017 Symposium on VLSI Circuits, Kyoto, Japan, 5–8 June 2017; pp. C236–C237. [Google Scholar]

- Miki, T.; Morie, T.; Matsukawa, K.; Bando, Y.; Okumoto, T.; Obata, K.; Sakiyama, S.; Dosho, S. A 4.2 mW 50 MS/s 13 bit CMOS SAR ADC With SNR and SFDR Enhancement Techniques. IEEE J. Solid-State Circuits 2015, 50, 1372–1381. [Google Scholar] [CrossRef]

- Kuo, H.L.; Lu, C.W.; Chen, P. An 18.39 fJ/Conversion-Step 1-MS/s 12-bit SAR ADC With Non-Binary Multiple-LSB-Redundant and Non-Integer-and-Split-Capacitor DAC. IEEE Access 2021, 9, 5651–5669. [Google Scholar] [CrossRef]

- Jiao, Z.; Luo, H.; Zhang, J.; Wang, X.; Chen, L.; Zhang, H. An 84dB-SNDR 1-0 Quasi-MASH NS SAR with LSB Repeating and 12-bit Bridge-Crossing Segmented CDAC. In Proceedings of the 2023 IEEE Custom Integrated Circuits Conference (CICC), San Antonio, TX, USA, 23–26 April 2023; pp. 1–2. [Google Scholar]

- Harpe, P.; Cantatore, E.; Roermund, A.v. A 10b/12b 40 kS/s SAR ADC with Data-Driven Noise Reduction Achieving up to 10.1b ENOB at 2.2 fJ/Conversion-Step. IEEE J. Solid-State Circuits 2013, 48, 3011–3018. [Google Scholar] [CrossRef]

- Hwang, Y.H.; Song, Y.; Park, J.E.; Jeong, D.K. A Fully Passive Noise-Shaping SAR ADC Utilizing Last-Bit Majority Voting and Cyclic Dynamic Element Matching Techniques. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2022, 30, 1381–1390. [Google Scholar] [CrossRef]

- Zhuang, H.; Guo, W.; Liu, J.; Tang, H.; Zhu, Z.; Chen, L.; Sun, N. A Second-Order Noise-Shaping SAR ADC with Passive Integrator and Tri-Level Voting. IEEE J. Solid-State Circuits 2019, 54, 1636–1647. [Google Scholar] [CrossRef]

- Chen, Z.; Miyahara, M.; Matsuzawa, A. A 9.35-ENOB, 14.8 fJ/conv.-step fully-passive noise-shaping SAR ADC. In Proceedings of the 2015 Symposium on VLSI Circuits (VLSI Circuits), Kyoto, Japan, 17–19 June 2015; pp. C64–C65. [Google Scholar]

- Guo, W.; Sun, N. A 12b-ENOB 61µW noise-shaping SAR ADC with a passive integrator. In Proceedings of the ESSCIRC Conference 2016: 42nd European Solid-State Circuits Conference, Lausanne, Switzerland, 12–15 September 2016; pp. 405–408. [Google Scholar]

- Kandala, M.; Sekar, R.; Chenglong, Z.; Haibo, W. A low power charge-redistribution ADC with reduced capacitor array. In Proceedings of the 2010 11th International Symposium on Quality Electronic Design (ISQED), San Jose, CA, USA, 22–24 March 2010; pp. 44–48. [Google Scholar]

- Zhan, M.; Jie, L.; Tang, X.; Sun, N. A 0.004mm2 200MS/S Pipelined SAR ADC with kT/C Noise Cancellation and Robust Ring-Amp. In Proceedings of the 2022 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 20–26 February 2022; pp. 164–166. [Google Scholar]

- Liu, J.; Tang, X.; Zhao, W.; Shen, L.; Sun, N. A 13-bit 0.005-mm2 40-MS/s SAR ADC With kT/C Noise Cancellation. IEEE J. Solid-State Circuits 2020, 55, 3260–3270. [Google Scholar] [CrossRef]

- Li, H.; Youssef, M.; Shen, Y.; Cantatore, E.; Harpe, P. Analysis of the Sampling Noise Cancellation Technique in a Track-and-Hold Amplifier. In Proceedings of the 2021 28th IEEE International Conference on Electronics, Circuits, and Systems (ICECS), Dubai, United Arab Emirates, 28 November–1 December 2021; pp. 1–5. [Google Scholar]

- Xu, K. Silicon electro-optic micro-modulator fabricated in standard CMOS technology as components for all silicon monolithic integrated optoelectronic systems*. J. Micromech. Microeng. 2021, 31, 054001. [Google Scholar] [CrossRef]

- Figueiredo, P.M.; Vital, J.C. Kickback noise reduction techniques for CMOS latched comparators. IEEE Trans. Circuits Syst. II Express Briefs 2006, 53, 541–545. [Google Scholar] [CrossRef]

- Razavi, B. The StrongARM Latch [A Circuit for All Seasons]. IEEE Solid-State Circuits Mag. 2015, 7, 12–17. [Google Scholar] [CrossRef]

- Wu, K.J.; Li, J.; Wang, X.Z.; Ning, N.; Xu, K.K.; Yu, Q. Switching sequence optimization for gradient errors compensation in the current-steering DAC design. Microelectron. J. 2020, 95, 104662. [Google Scholar] [CrossRef]

| Architecture | Second-Order Fully-Passive NS SAR | NS SAR Based on Active Gain | Improved NS SAR Based on Activegain |

|---|---|---|---|

| Ctotal | large | medium | small |

| ADC Input Cap | |||

| kT/C Suppressed? | × | √ | √ |

| Comparator Noise Suppressed? | √ | √ | √ |

| Extra Cycles? | √ | × | × |

| Static Power | × | √ | √ |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jia, S.; Ye, T.; Xiao, S. Analysis of the Second-Order NS SAR ADC Performance Enhancement Based on Active Gain. Electronics 2024, 13, 3400. https://doi.org/10.3390/electronics13173400

Jia S, Ye T, Xiao S. Analysis of the Second-Order NS SAR ADC Performance Enhancement Based on Active Gain. Electronics. 2024; 13(17):3400. https://doi.org/10.3390/electronics13173400

Chicago/Turabian StyleJia, Shichao, Tianchun Ye, and Shimao Xiao. 2024. "Analysis of the Second-Order NS SAR ADC Performance Enhancement Based on Active Gain" Electronics 13, no. 17: 3400. https://doi.org/10.3390/electronics13173400

APA StyleJia, S., Ye, T., & Xiao, S. (2024). Analysis of the Second-Order NS SAR ADC Performance Enhancement Based on Active Gain. Electronics, 13(17), 3400. https://doi.org/10.3390/electronics13173400