A Self-Biased Triggered Dual-Direction Silicon-Controlled Rectifier Device for Low Supply Voltage Application-Specific Integrated Circuit Electrostatic Discharge Protection

Abstract

1. Introduction

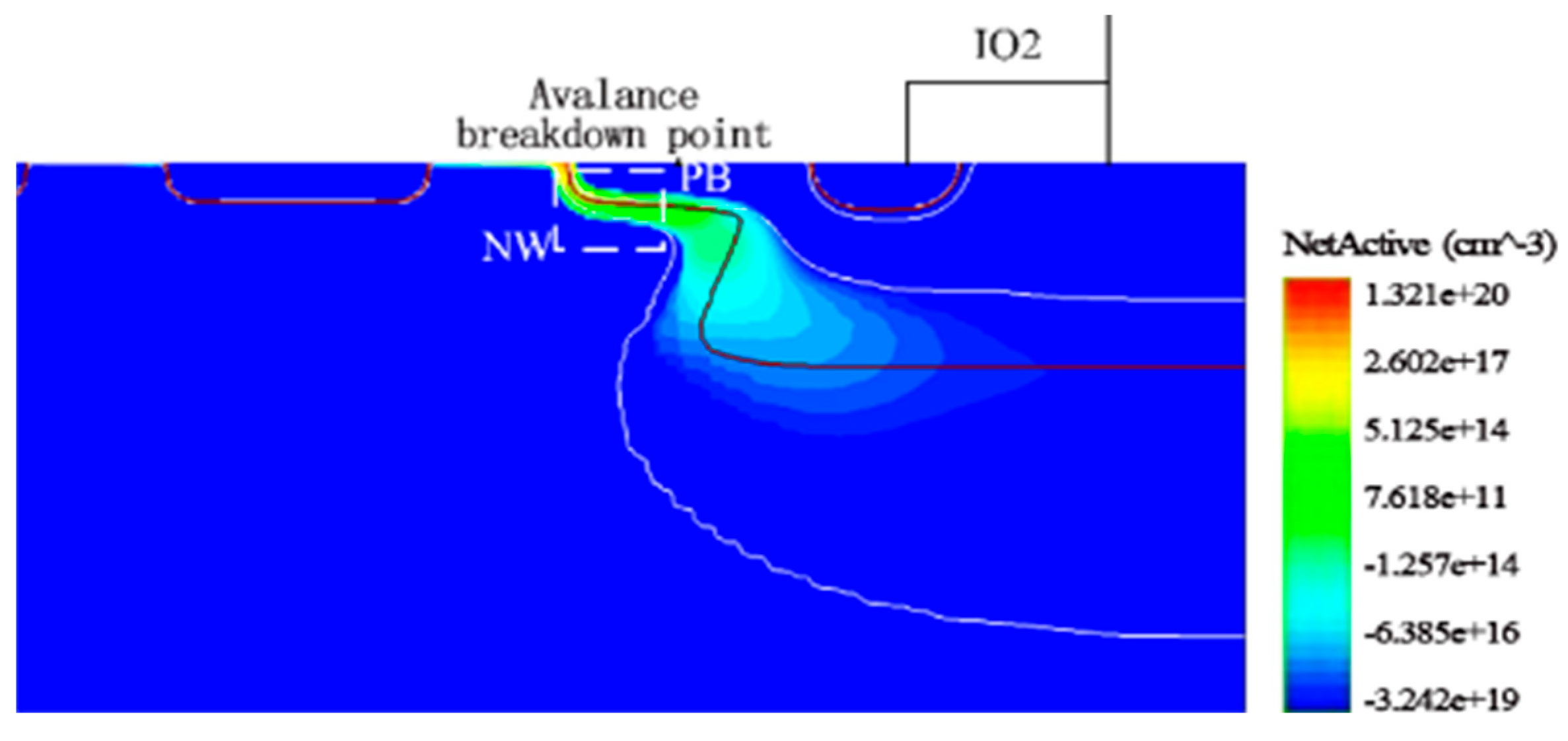

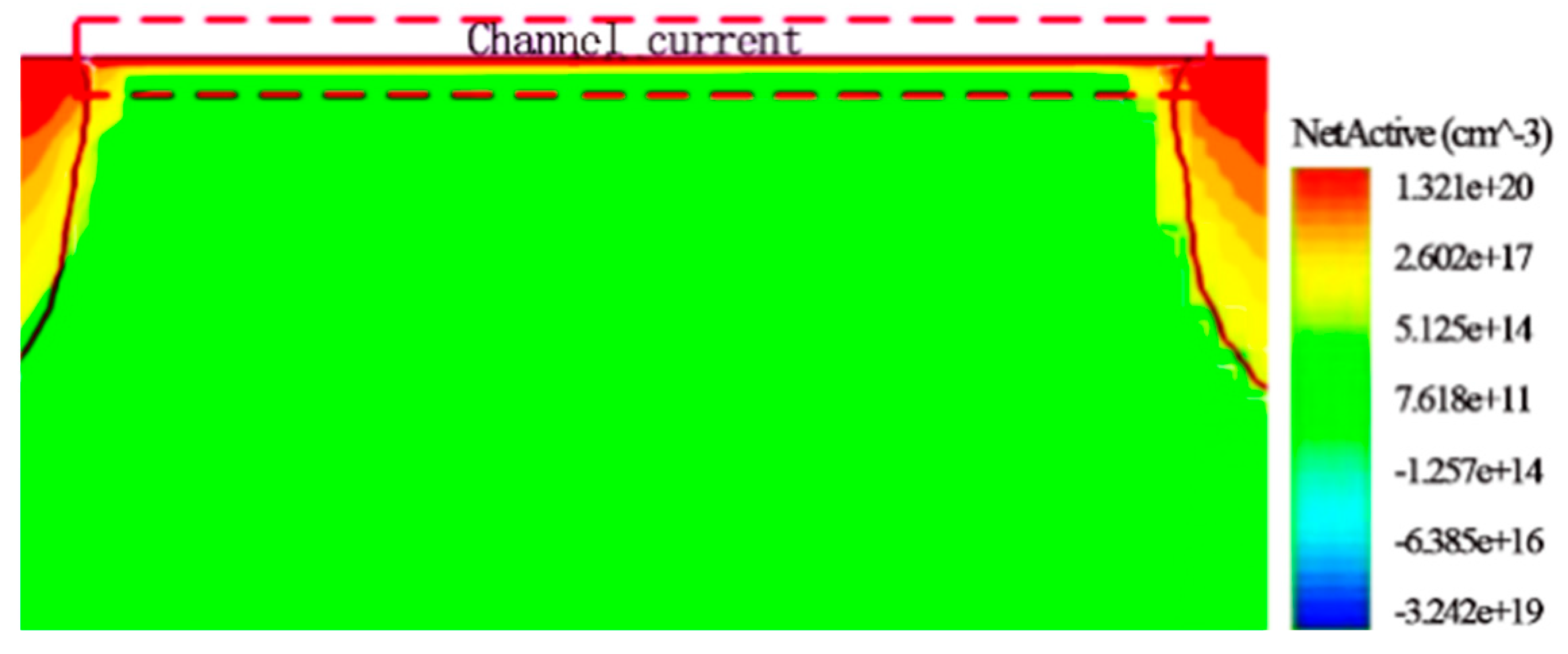

2. Device Description and Mechanism Analysis [1]

3. Simulation Analysis and Discussion

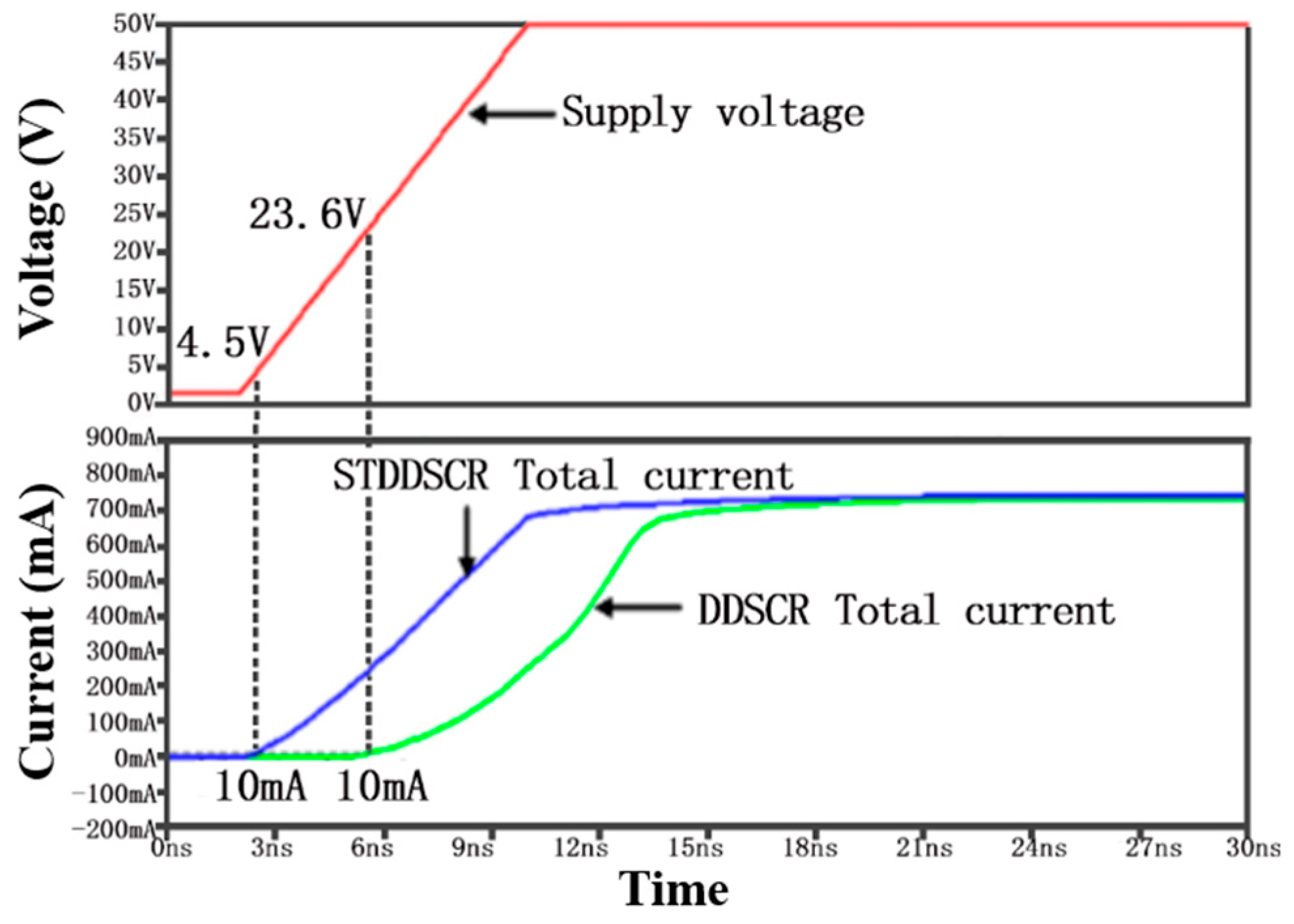

3.1. Overall Circuit Optimization Simulation Verification

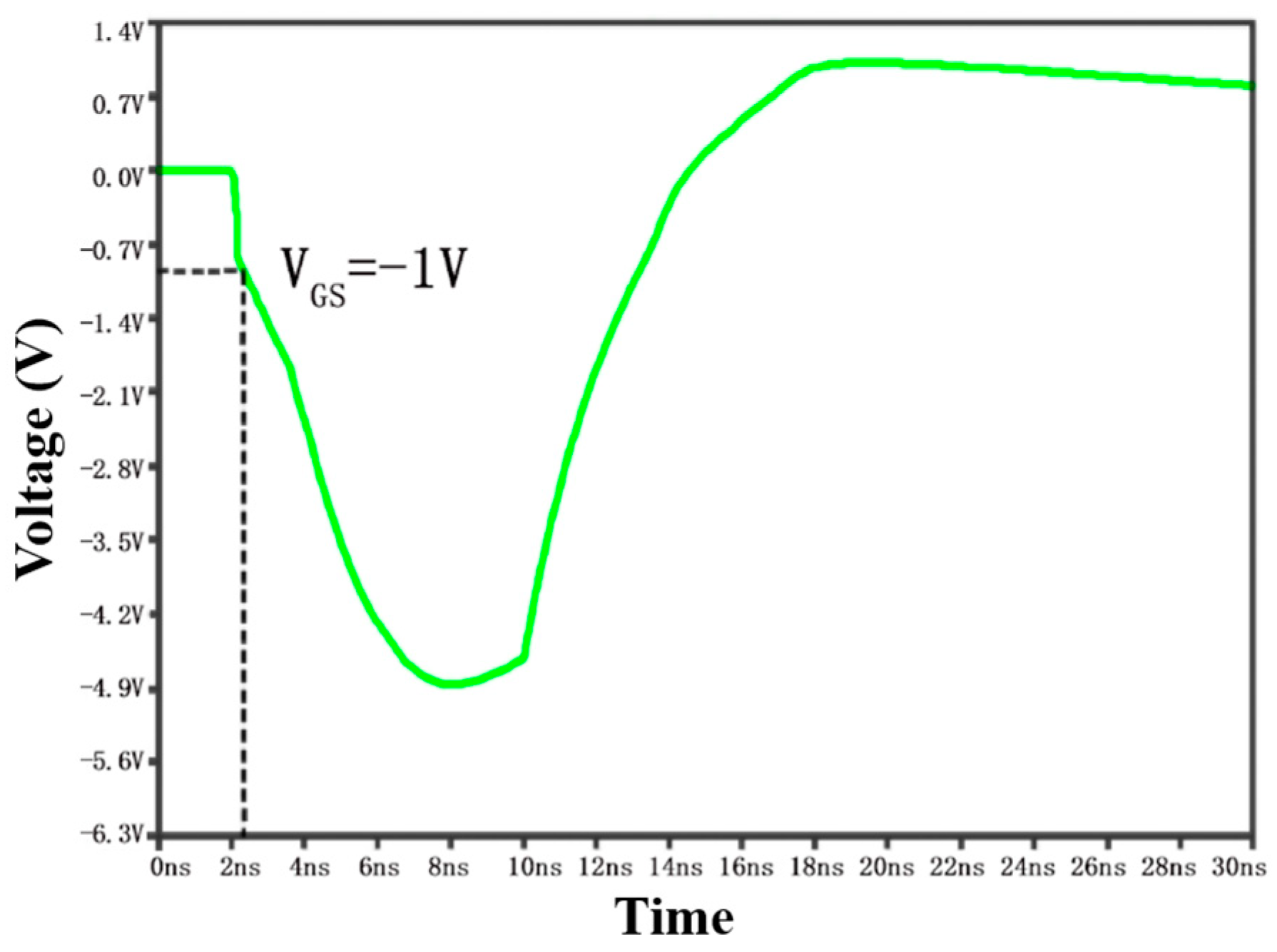

3.2. Fixed Gate Source Voltage Reasonableness Verification

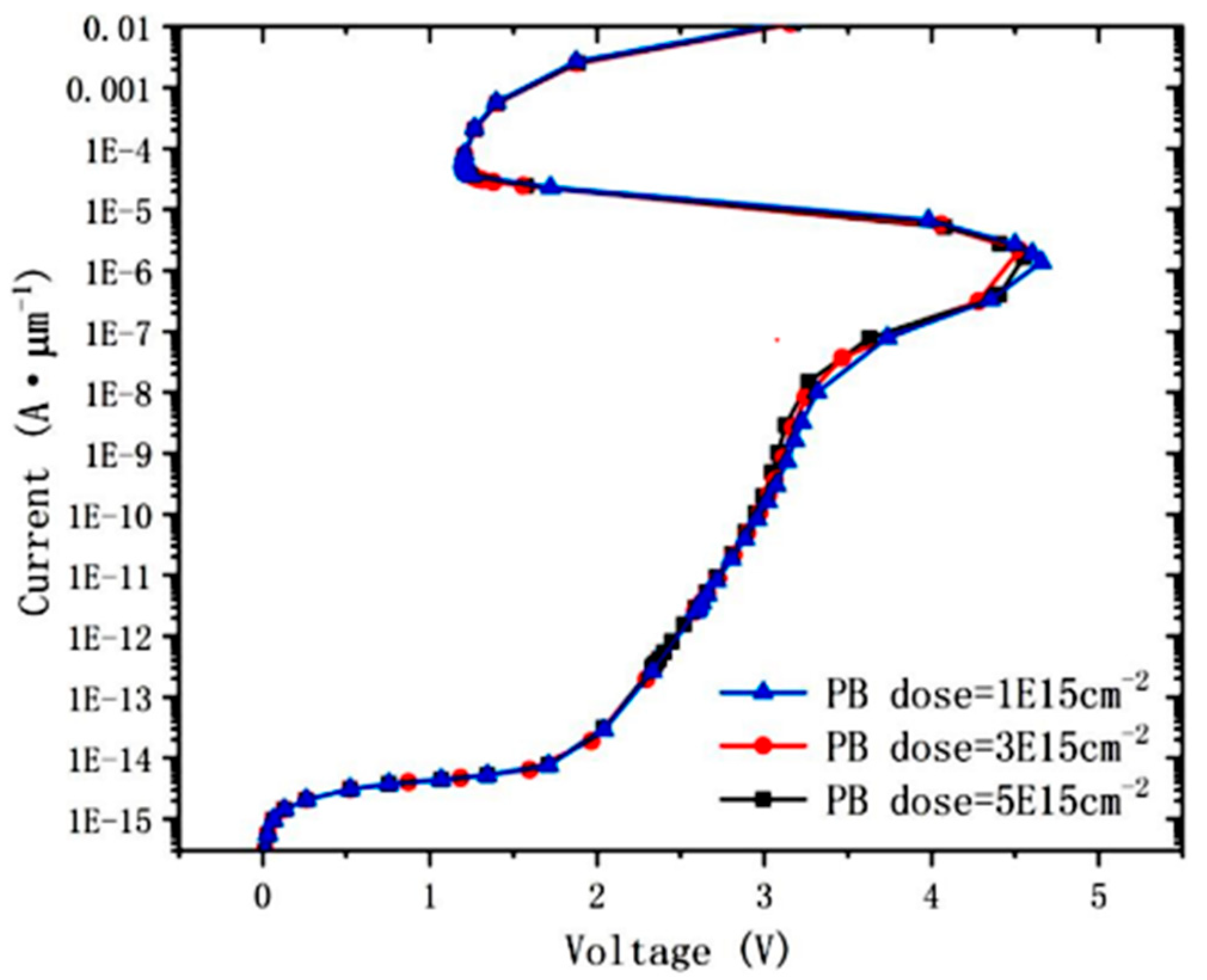

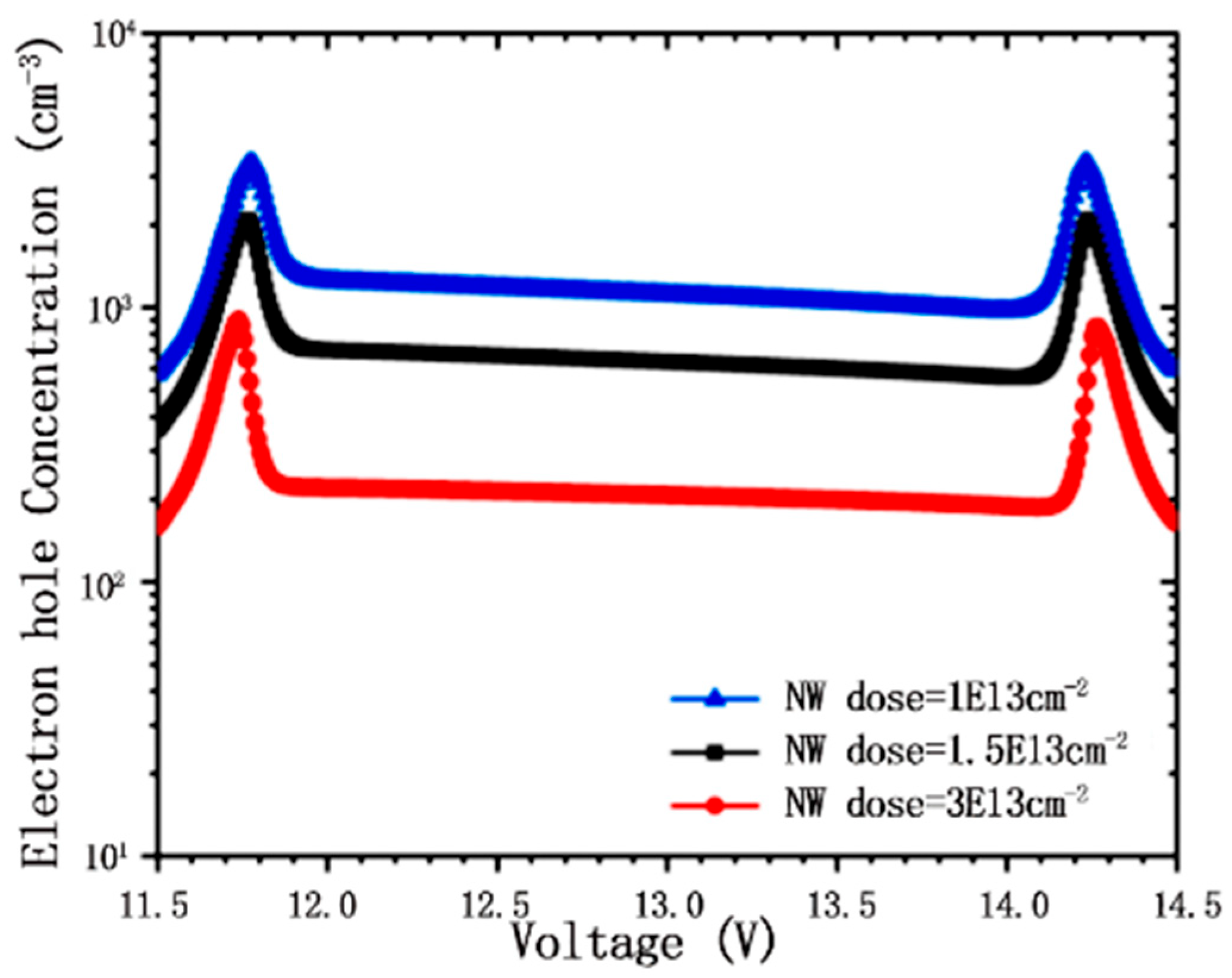

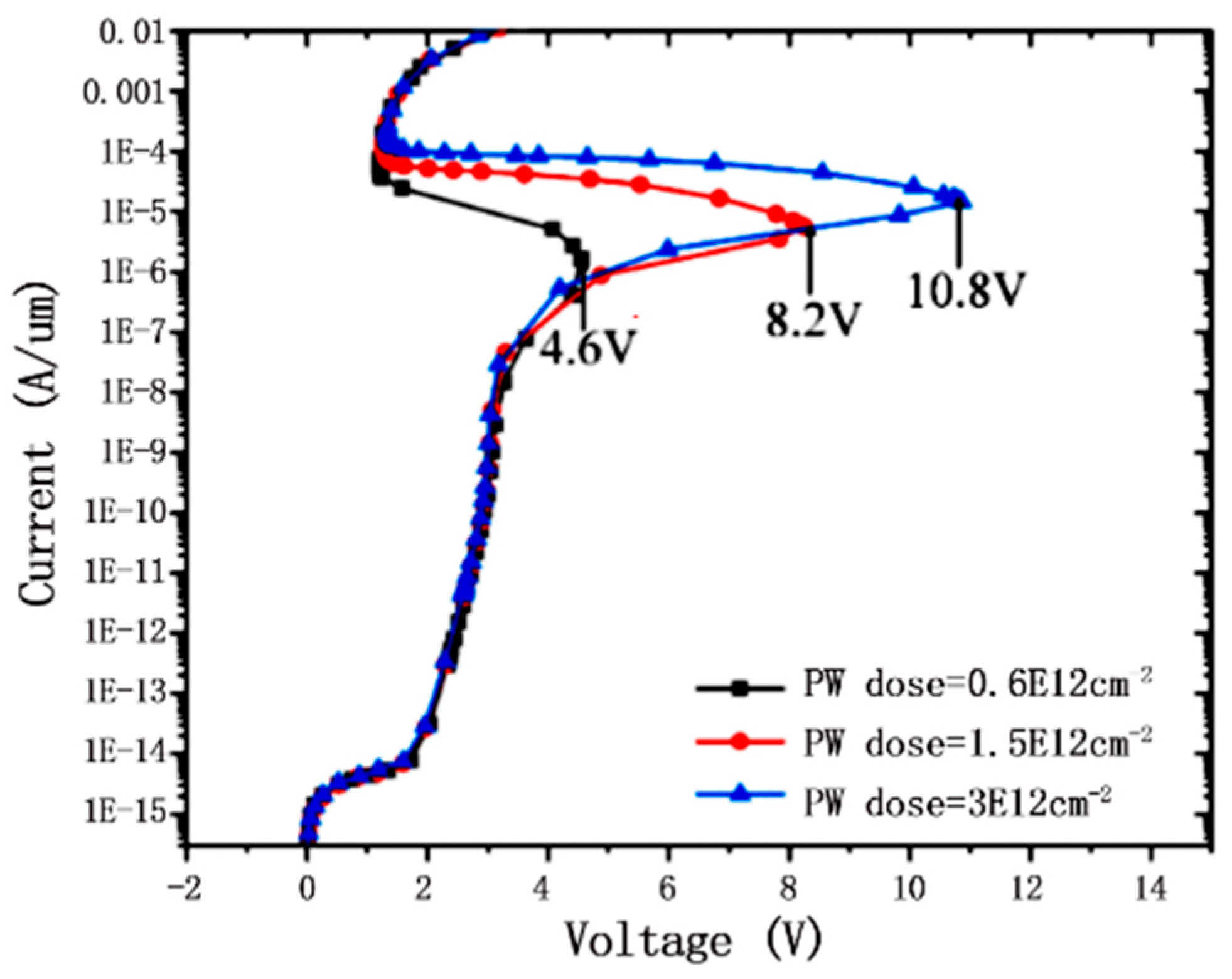

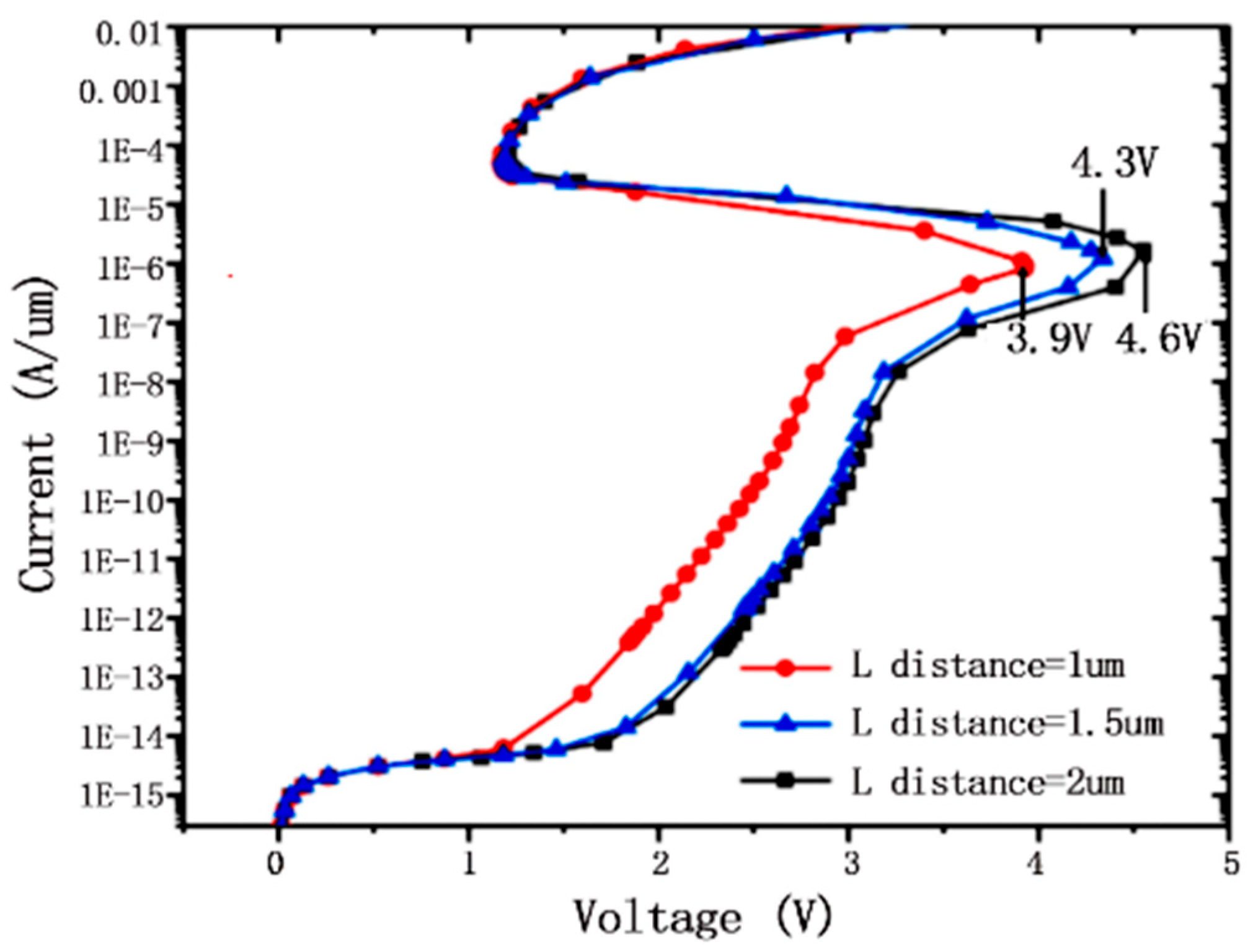

3.3. STDDSCR Parameter Optimization Simulation

3.4. Discussion

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Navid, R.; Chen, E.-H.; Hossain, M.; Leibowitz, B.; Ren, J.; Chou, C.-H.A.; Daly, B.; Aleksic, M.; Su, B.; Li, S.; et al. A 40 Gb/s Serial Link Transceiver in 28 nm CMOS Technology. IEEE J. Solid-State Circuits 2015, 50, 814–827. [Google Scholar] [CrossRef]

- Cui, Q.; Salcedo, J.A.; Parthasarathy, S.; Zhou, Y.; Liou, J.J.; Hajjar, J.J. High-Robustness and Low-Capacitance Silicon-Controlled Rectifier for High-Speed I/O ESD Protection. IEEE Electron. Device Lett. 2013, 34, 178–180. [Google Scholar] [CrossRef]

- Ker, M.-D.; Hsu, K.-C. Overview of on-chip electrostatic discharge protection design with SCR-based devices in CMOS integrated circuits. IEEE Trans. Device Mater. Reliab. 2005, 5, 235–249. [Google Scholar] [CrossRef]

- Chang, T.H.; Hsu, Y.Y.; Tsai, T.C.; Tseng, J.C.; Lee, J.W.; Song, M.H. High-k metal gate-bounded Silicon Controlled Rectifier for ESD protection. In Proceedings of the Electrical Overstress/Electrostatic Discharge Symposium Proceedings 2012, Tucson, AZ, USA, 9–14 September 2012. [Google Scholar]

- Lin, C.-Y.; Chang, R.-K. Design of ESD Protection Device for K/Ka-Band Applications in Nanoscale CMOS Process. IEEE Trans. Electron. Devices 2015, 62, 2824–2829. [Google Scholar] [CrossRef]

- Dong, A.; Salcedo, J.A.; Parthasarathy, S.; Zhou, Y.; Luo, S.; Hajjar, J.-J.; Liou, J.J. ESD protection structure with reduced capacitance and overshoot voltage for high speed interface applications. Microelectron. Reliab. 2017, 79, 201–205. [Google Scholar] [CrossRef]

- He, L.; Salcedo, J.A.; Parthasarathy, S.; Zhou, Y.; Hajjar, J.-J.; Sundaram, K. Compact and Fast-Response Voltage Clamp for Bi-Directional Signal Swing Interface Applications. IEEE Electron. Device Lett. 2018, 39, 1880–1883. [Google Scholar] [CrossRef]

- Wu, M.; Zhang, C.; Peng, W.; Xu, J.; Jin, H.; Zeng, Y.; Chen, Z. A Radiation-Hardened Dual-Direction SCR Based on LDMOS for ESD Protection in the Extreme Radiation Environment. IEEE Trans. Nucl. Sci. 2020, 67, 708–715. [Google Scholar] [CrossRef]

- Guan, J.; Wang, Y.; Hao, S.; Zheng, Y.; Jin, X. A Novel High Holding Voltage Dual-Direction SCR With Embedded Structure for HV ESD Protection. IEEE Electron. Device Lett. 2017, 38, 1716–1719. [Google Scholar] [CrossRef]

- Huang, X.; Liou, J.J.; Liu, Z.; Liu, F.; Liu, J.; Cheng, H. A New High Holding Voltage Dual-Direction SCR With Optimized Segmented Topology. IEEE Electron. Device Lett. 2016, 37, 1311–1313. [Google Scholar] [CrossRef]

- Do, K.-I.; Song, B.-B.; Koo, Y.-S. A Novel Dual-Directional SCR Structure with High Holding Voltage for 12-V Applications in 0.13-μm BCD Process. IEEE Trans. Electron. Devices 2020, 67, 5020–5027. [Google Scholar] [CrossRef]

- Do, K.-I.; Koo, Y.-S. A New SCR Structure with High Holding Voltage and Low ON-Resistance for 5-V Applications. IEEE Trans. Electron. Devices 2020, 67, 1052–1058. [Google Scholar] [CrossRef]

- Liang, H.; Gu, X.; Dong, S.; Liou, J.J. RC-Embedded LDMOS-SCR With High Holding Current for High-Voltage I/O ESD Protection. IEEE Trans. Device Mater. Reliab. 2015, 15, 495–499. [Google Scholar] [CrossRef]

- Yang, Z.; Liu, H.; Wang, S. A low leakage power-rail ESD detection circuit with a modified RC network for a 90-nm CMOS process. J. Semicond. 2013, 34, 45010. [Google Scholar] [CrossRef]

| Key Parameters | Numerical Value |

|---|---|

| NW dose/cm2 | 1.5 × 1013 |

| PW dose/cm2 | 0.6 × 1012 |

| L length/μm | 1.5 |

| Resistance/kΩ | 30 |

| Capacitance/pF | 30 |

| Device Structure | Trigger Voltage/V | Hold Voltage/V | Leakage Current at 25 °C (nA) @1.5 V |

|---|---|---|---|

| DDSCR | 23.9 | 1.23 | 10 |

| LVTDDSCR | 14.8 | 1.25 | <1 |

| DCSCR | 1.82 | 1.3 | >1000 |

| STDDSCR (Proposed) | 4.6 | 1.26 | <1 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Pan, J.; Li, F.; Wen, L.; Jin, J.; Huang, X.; Han, J. A Self-Biased Triggered Dual-Direction Silicon-Controlled Rectifier Device for Low Supply Voltage Application-Specific Integrated Circuit Electrostatic Discharge Protection. Electronics 2024, 13, 3458. https://doi.org/10.3390/electronics13173458

Pan J, Li F, Wen L, Jin J, Huang X, Han J. A Self-Biased Triggered Dual-Direction Silicon-Controlled Rectifier Device for Low Supply Voltage Application-Specific Integrated Circuit Electrostatic Discharge Protection. Electronics. 2024; 13(17):3458. https://doi.org/10.3390/electronics13173458

Chicago/Turabian StylePan, Jie, Fanyang Li, Liguo Wen, Jiazhen Jin, Xiaolong Huang, and Jiaxun Han. 2024. "A Self-Biased Triggered Dual-Direction Silicon-Controlled Rectifier Device for Low Supply Voltage Application-Specific Integrated Circuit Electrostatic Discharge Protection" Electronics 13, no. 17: 3458. https://doi.org/10.3390/electronics13173458

APA StylePan, J., Li, F., Wen, L., Jin, J., Huang, X., & Han, J. (2024). A Self-Biased Triggered Dual-Direction Silicon-Controlled Rectifier Device for Low Supply Voltage Application-Specific Integrated Circuit Electrostatic Discharge Protection. Electronics, 13(17), 3458. https://doi.org/10.3390/electronics13173458