Frequent Power-Up-and-Down-Induced Degradation of Device and Bandgap Voltage Reference in 14-nm FinFET Technology

Abstract

:1. Introduction

2. NBTI Degradation Model

3. Results and Discussion

3.1. Circuit Modules and Simulation

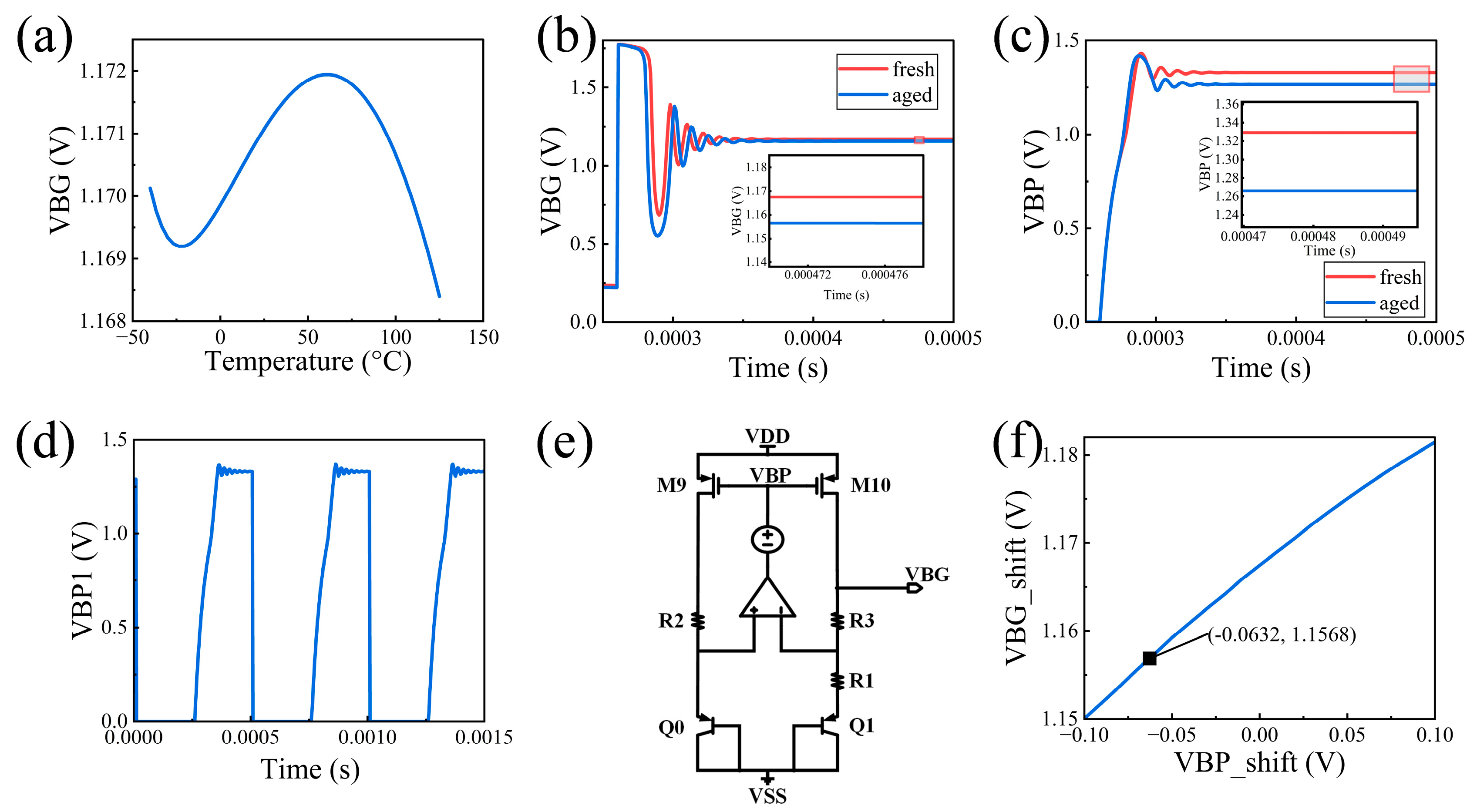

3.1.1. Configurations of Simulated Bandgap Voltage Reference

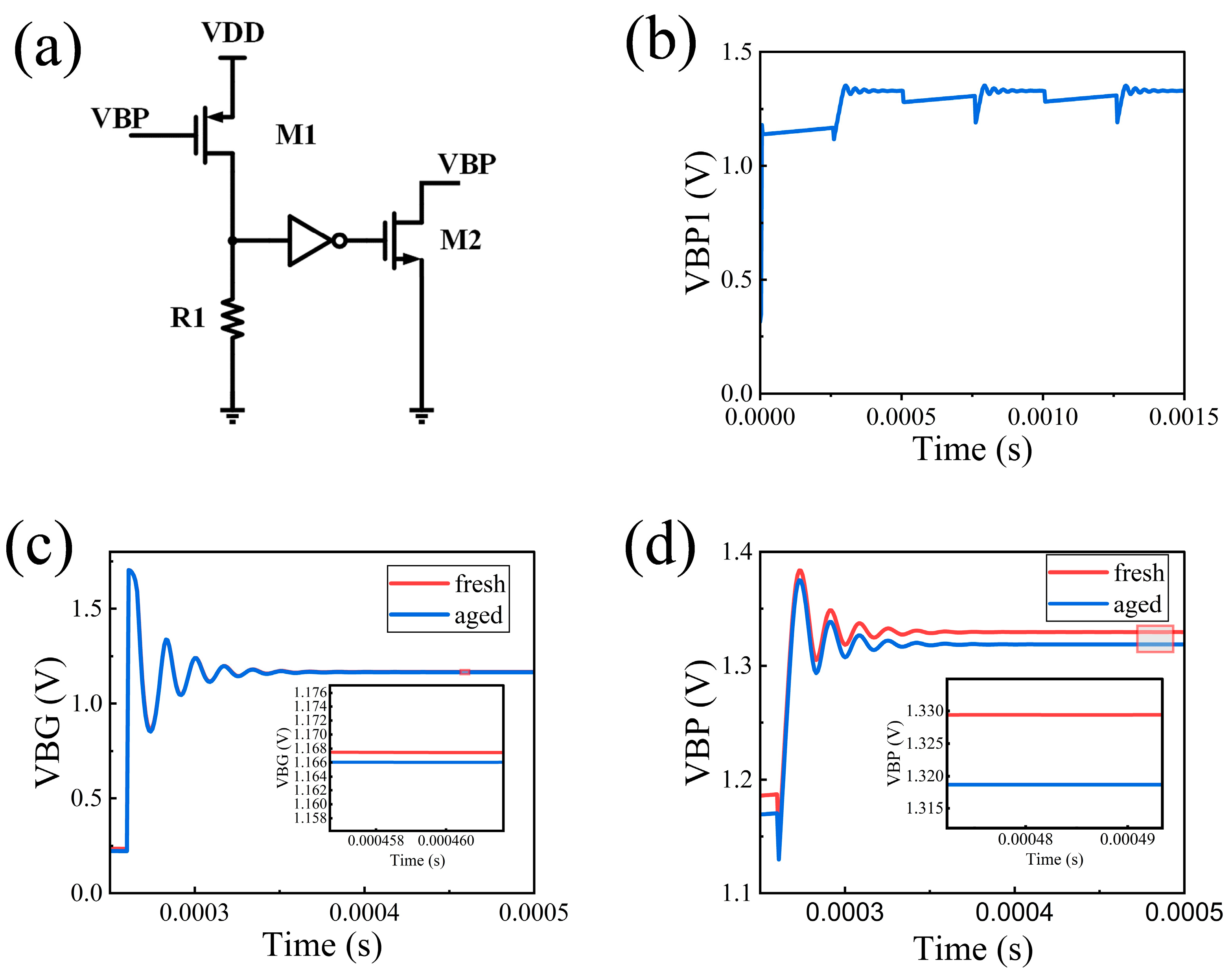

3.1.2. Aging Analysis and Problem Identification

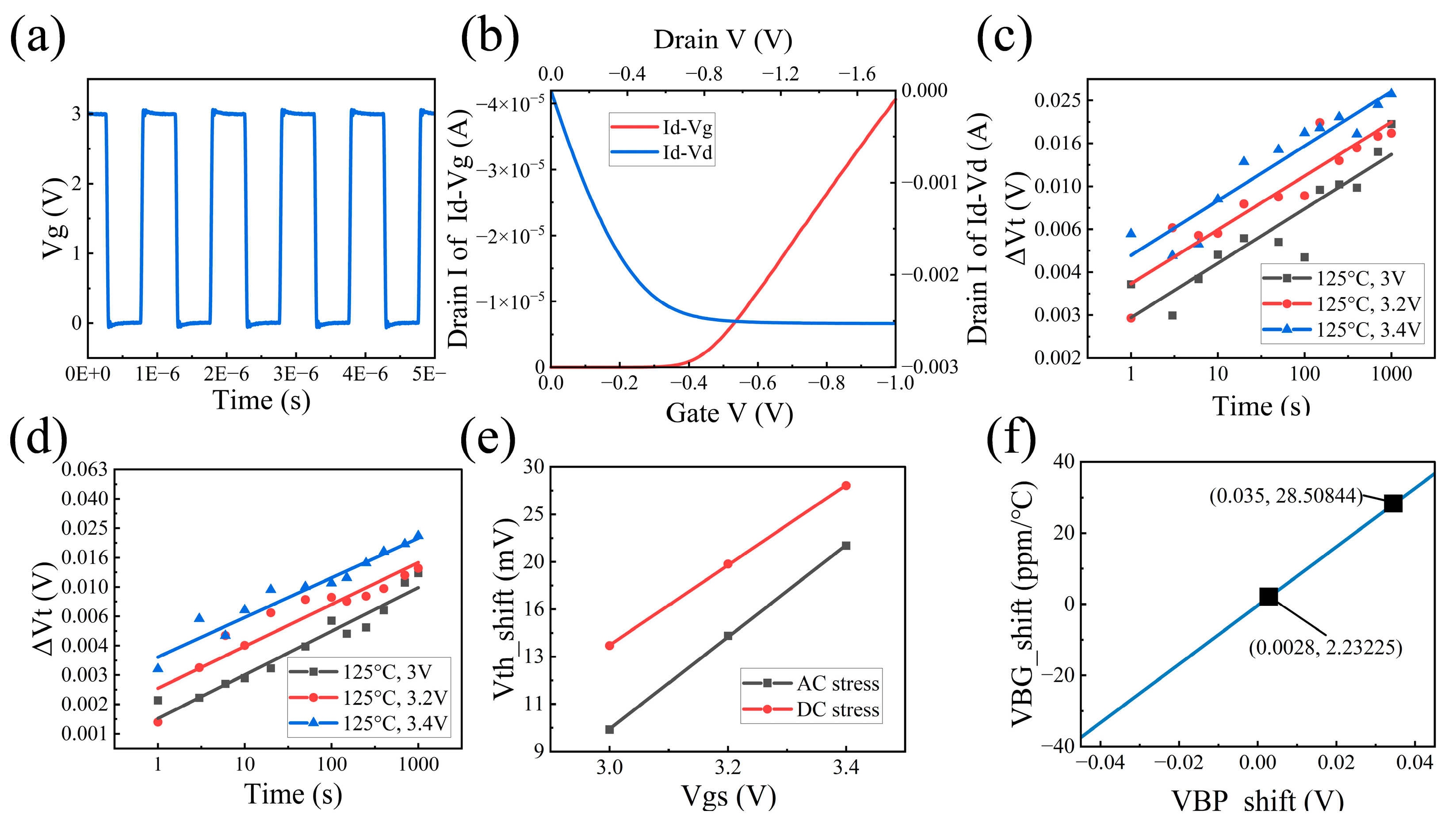

3.2. Device Aging Test Results and Discussion

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Hwang, W. New Trends in Low Power SoC Design Technologies. In Proceedings of the IEEE International [Systems-on-Chip] SOC Conference, Portland, OR, USA, 17–20 September 2003; p. 422. [Google Scholar]

- Sun, D.; Xu, S.; Sun, W.; Lu, S.; Shi, L. Low Power Design for SoC with Power Management Unit. In Proceedings of the 2011 9th IEEE International Conference on ASIC, Xiamen, China, 25–28 October 2011; pp. 719–722. [Google Scholar]

- Affes, H.; Auguin, M. SOC Power Management Strategy Based on Global Hardware Functional State Analysis. In Proceedings of the 2015 Euromicro Conference on Digital System Design, Madeira, Portugal, 26–28 August 2015; pp. 614–620. [Google Scholar]

- Serrano, R.; Sarmiento, M.; Duran, C.; Nguyen, K.-D.; Hoang, T.-T.; Ishibashi, K.; Pham, C.-K. A Low-Power Low-Area SoC Based in RISC-V Processor for IoT Applications. In Proceedings of the 2021 18th International SoC Design Conference (ISOCC), Jeju Island, Republic of Korea, 6–9 October 2021; pp. 375–376. [Google Scholar]

- Kumaran, S.; Arunachalam, S.; Surendar, V.; Sudharsan, T. IoT Based Smoke Detection with Air Temperature and Air Humidity; High Accuracy with Machine Learning. In Proceedings of the 2023 Third International Conference on Artificial Intelligence and Smart Energy (ICAIS), Coimbatore, India, 2–4 February 2023; pp. 604–610. [Google Scholar]

- Razavi, B. Design of Analog CMOS Integrated Circuits, 2nd ed.; McGraw-Hill Education: New York, NY, USA, 2001; ISBN 978-0-07-252493-2. [Google Scholar]

- Kim, J.J.; Jin, M.; Sagong, H.; Pae, S. Reliability Assessment of 10nm Finfet Process Technology. In Proceedings of the 2018 IEEE International Symposium on the Physical and Failure Analysis of Integrated Circuits (IPFA), Singapore, 16–19 July 2018. [Google Scholar] [CrossRef]

- Amouri, A.; Bruguier, F.; Kiamehr, S.; Benoit, P.; Torres, L.; Tahoori, M. Aging Effects in FPGAs: An Experimental Analysis. In Proceedings of the 2014 24th International Conference on Field Programmable Logic and Applications (FPL), Munich, Germany, 2–4 September 2014; pp. 1–4. [Google Scholar]

- Wang, W.; Reddy, V.; Krishnan, A.T.; Vattikonda, R.; Krishnan, S.; Cao, Y. Compact Modeling and Simulation of Circuit Reliability for 65-Nm CMOS Technology. IEEE Trans. Device Mater. Reliab. 2007, 7, 509–517. [Google Scholar] [CrossRef]

- Shakil, S.M.; Ullah, M.S. Effects of NBTI On PMOS Device with Technology Scaling. In Proceedings of the 2022 IEEE 13th Annual Ubiquitous Computing, Electronics & Mobile Communication Conference (UEMCON), New York, NY, USA, 26–29 October 2022; pp. 402–406. [Google Scholar]

- Li, X.; Qin, J.; Bernstein, J.B. Compact Modeling of MOSFET Wearout Mechanisms for Circuit-Reliability Simulation. IEEE Trans. Device Mater. Reliab. 2008, 8, 98–121. [Google Scholar] [CrossRef]

- Adesina, N.O.; Khan, M.A.U.; Xu, J. Modeling the Effects of SBD, HCI, and NBTI in CMOS Voltage Controlled Oscillator Design for PLL Applications. In Proceedings of the 2021 IEEE 12th Annual Information Technology, Electronics and Mobile Communication Conference (IEMCON), Vancouver, BC, Canada, 27–30 October 2021; pp. 720–725. [Google Scholar]

- Van Dam, C.; Hauser, M. Ring Oscillator Reliability Model to Hardware Correlation in 45nm SOI. In Proceedings of the 2013 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 14–18 April 2013; pp. CM.1.1–CM.1.5. [Google Scholar]

- Zhan, S.; Chen, C. Circuit Reliability Analysis with Considerations of Aging Effect. In Proceedings of the 2022 35th SBC/SBMicro/IEEE/ACM Symposium on Integrated Circuits and Systems Design (SBCCI), Porto Alegre, Brazil, 22–26 August 2022; pp. 1–5. [Google Scholar]

- Jha, N.K.; Reddy, P.S.; Sharma, D.K.; Rao, V.R. NBTI Degradation and Its Impact for Analog Circuit Reliability. IEEE Trans. Electron Devices 2005, 52, 2609–2615. [Google Scholar] [CrossRef]

- Latif, M.A.A.; Ali, N.B.Z.; Hussin, F.A. A Case Study for Reliability-Aware in SoC Analog Circuit Design. In Proceedings of the 2010 International Conference on Intelligent and Advanced Systems, Kuala Lumpur, Malaysia, 15–17 June 2010; pp. 1–6. [Google Scholar]

- Latif, M.A.A.; Ali, N.B.Z.; Hussin, F.A. NBTI-Induced 8-Bit DAC Circuit Mismatch in System-On-Chip (SoC). In Proceedings of the 2011 3rd Asia Symposium on Quality Electronic Design (ASQED), Kuala Lumpur, Malaysia, 19–20 July 2011; pp. 29–36. [Google Scholar]

- Yan, B.; Qin, J.; Dai, J.; Fan, Q.; Bernstein, J.B. Reliability Simulation and Design Consideration of High Speed ADC Circuits. In Proceedings of the 2008 IEEE International Integrated Reliability Workshop Final Report, South Lake Tahoe, CA, USA, 12–16 October 2008; pp. 125–128. [Google Scholar]

- Vijay, A.; Duari, C.; Garg, L.; Singh, A.K. Nanoscale CMOS Biasing Circuit for Analog Applications: The Impact of NBTI Degradation. In Proceedings of the 2023 International Conference for Advancement in Technology (ICONAT), Goa, India, 24–26 January 2023; pp. 1–3. [Google Scholar]

- Stathis, J.H.; Mahapatra, S.; Grasser, T. Controversial Issues in Negative Bias Temperature Instability. Microelectron. Reliab. 2018, 81, 244–251. [Google Scholar] [CrossRef]

- Tiwari, R.; Parihar, N.; Thakor, K.; Wong, H.-Y.; Mahapatra, S. TCAD Framework to Estimate the NBTI Degradation in FinFET and GAA NSFET Under Mechanical Strain. In Proceedings of the 2019 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), Udine, Italy, 4–6 September 2019; pp. 1–4. [Google Scholar]

- Parihar, N.; Goel, N.; Mukhopadhyay, S.; Mahapatra, S. BTI Analysis Tool—Modeling of NBTI DC, AC Stress and Recovery Time Kinetics, Nitrogen Impact, and EOL Estimation. IEEE Trans. Electron Devices 2018, 65, 392–403. [Google Scholar] [CrossRef]

- Song, B.S.; Gray, P.R. A Precision Curvature-Compensated CMOS Bandgap Reference. IEEE J. Solid-State Circuits 1983, 18, 634–643. [Google Scholar] [CrossRef]

- Chung, E.A.; Nam, K.J.; Nakanishi, T.; Park, S.; Yang, H.; Kauerauf, T.; Jiao, G.; Kim, D.W.; Hwang, K.H.; Kim, H.; et al. Investigation of Hot Carrier Degradation in Bulk FinFET. In Proceedings of the 2017 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 2–6 April 2017; pp. XT6.1–XT6.4. [Google Scholar] [CrossRef]

- Lu, M.; Chen, Y.; Liao, M.; Liu, C.; Zheng, S.; Gao, K. Degradation Mechanism of D-Mode GaN HEMT Based on High Temperature Reverse Bias Stress. In Proceedings of the 2021 IEEE Workshop on Wide Bandgap Power Devices and Applications in Asia (WiPDA Asia), Wuhan, China, 25–27 August 2021; pp. 167–170. [Google Scholar]

- Mahmud, M.I.; Gupta, A.; Toledano-Luque, M.; Mavilla, N.; Johnson, J.; Srinivasan, P.; Zainuddin, A.; Rao, S.; Cimino, S.; Min, B.; et al. Hot Carrier Reliability Improvement of Thicker Gate Oxide NFET Devices in Advanced FinFETs. In Proceedings of the 2019 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 31 March–4 April 2019; pp. 1–6. [Google Scholar]

- Takeda, E.; Suzuki, N. An Empirical Model for Device Degradation Due to Hot-Carrier Injection. IEEE Electron Device Lett. 1983, 4, 111–113. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Shi, Y.; Li, Y.; Li, M.; Xu, X.; Zhu, H.; Sun, Q. Frequent Power-Up-and-Down-Induced Degradation of Device and Bandgap Voltage Reference in 14-nm FinFET Technology. Electronics 2024, 13, 3506. https://doi.org/10.3390/electronics13173506

Shi Y, Li Y, Li M, Xu X, Zhu H, Sun Q. Frequent Power-Up-and-Down-Induced Degradation of Device and Bandgap Voltage Reference in 14-nm FinFET Technology. Electronics. 2024; 13(17):3506. https://doi.org/10.3390/electronics13173506

Chicago/Turabian StyleShi, Yiqun, Yunpeng Li, Meng Li, Xin Xu, Hao Zhu, and Qingqing Sun. 2024. "Frequent Power-Up-and-Down-Induced Degradation of Device and Bandgap Voltage Reference in 14-nm FinFET Technology" Electronics 13, no. 17: 3506. https://doi.org/10.3390/electronics13173506