Novel Power-Efficient Fast-Locking Phase-Locked Loop Based on Adaptive Time-to-Digital Converter-Aided Acceleration Compensation Technology

Abstract

:1. Introduction

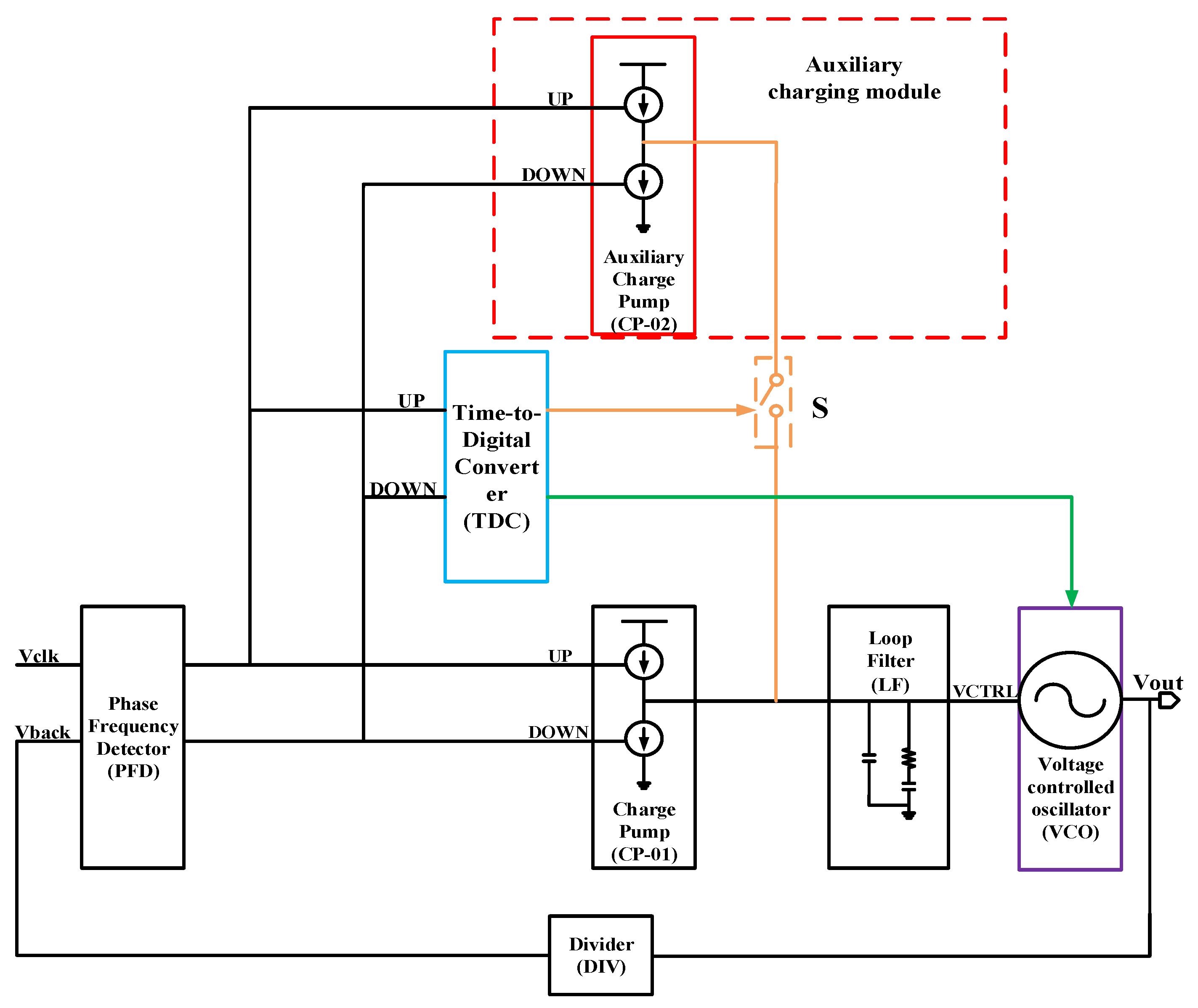

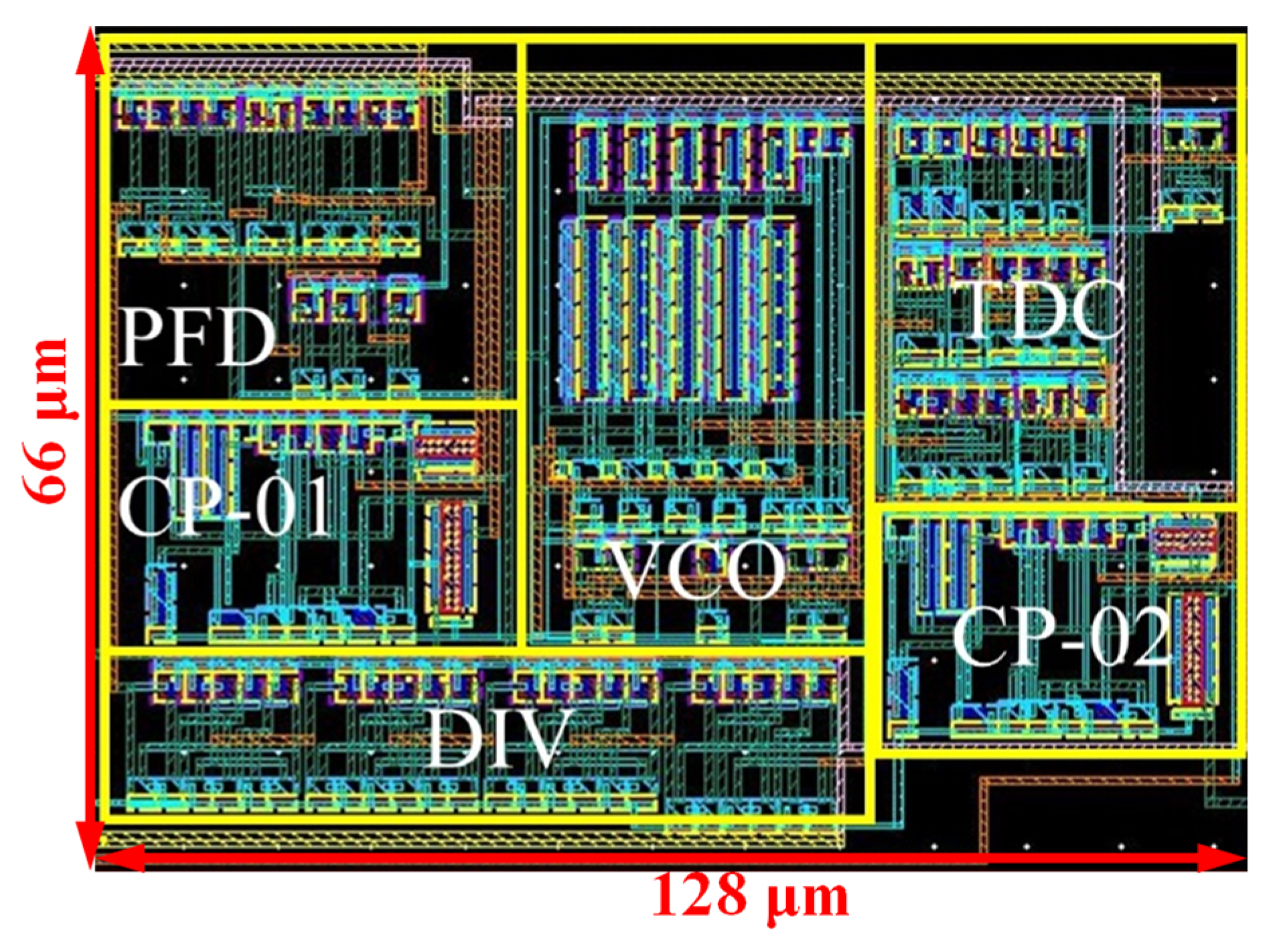

- An aided TDC circuit is implemented as the core adaptive control module in the PLL, and it can accurately convert the phase difference signal to switch the instructions to dynamically control the CP and VCO.

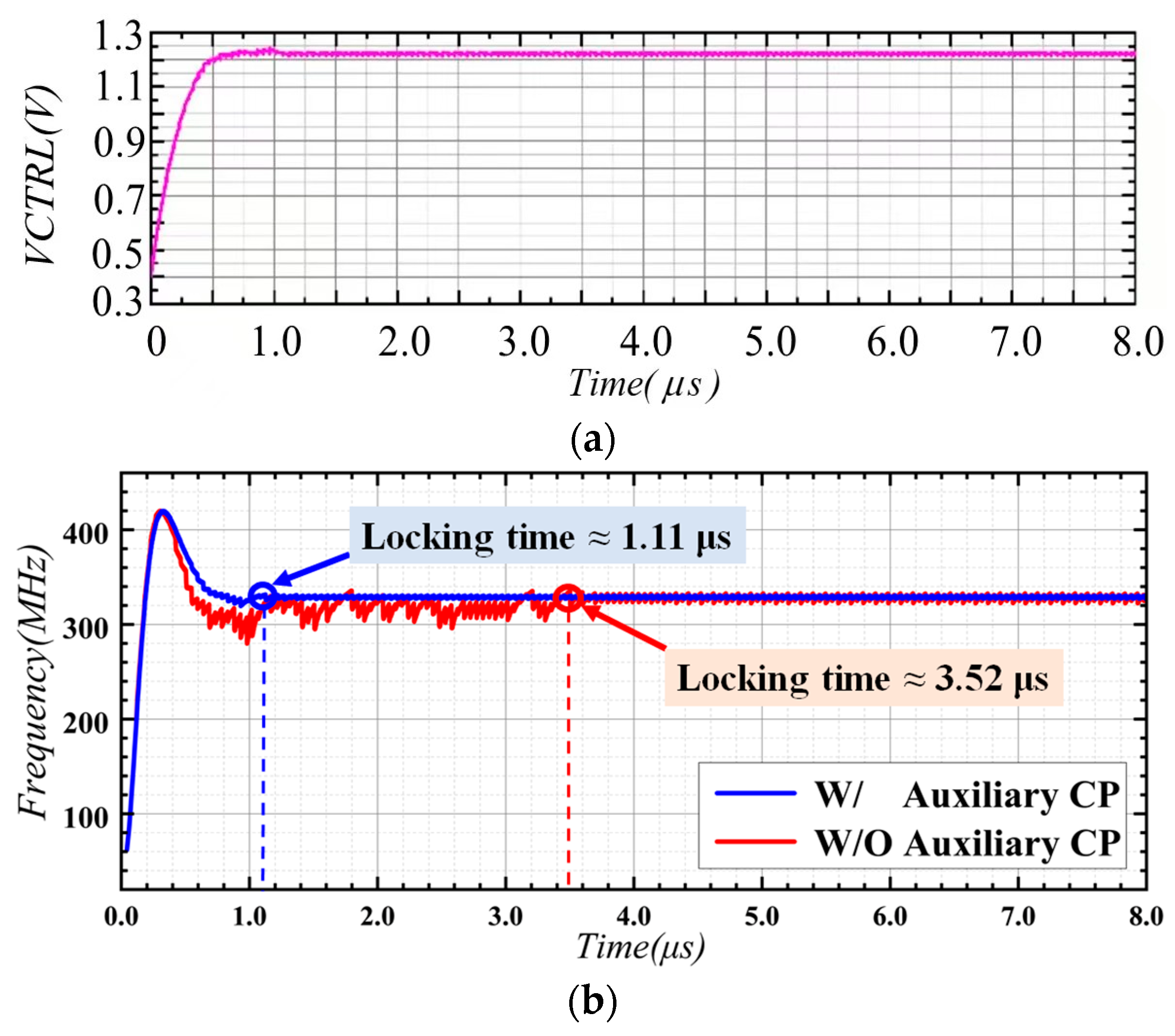

- An auxiliary secondary CP with a selectable switch is designed to construct a parallel output topology that forms paired CP modules, which can double the charging/discharging current to speed up the locking phase; otherwise, the CP operates in power-saving mode.

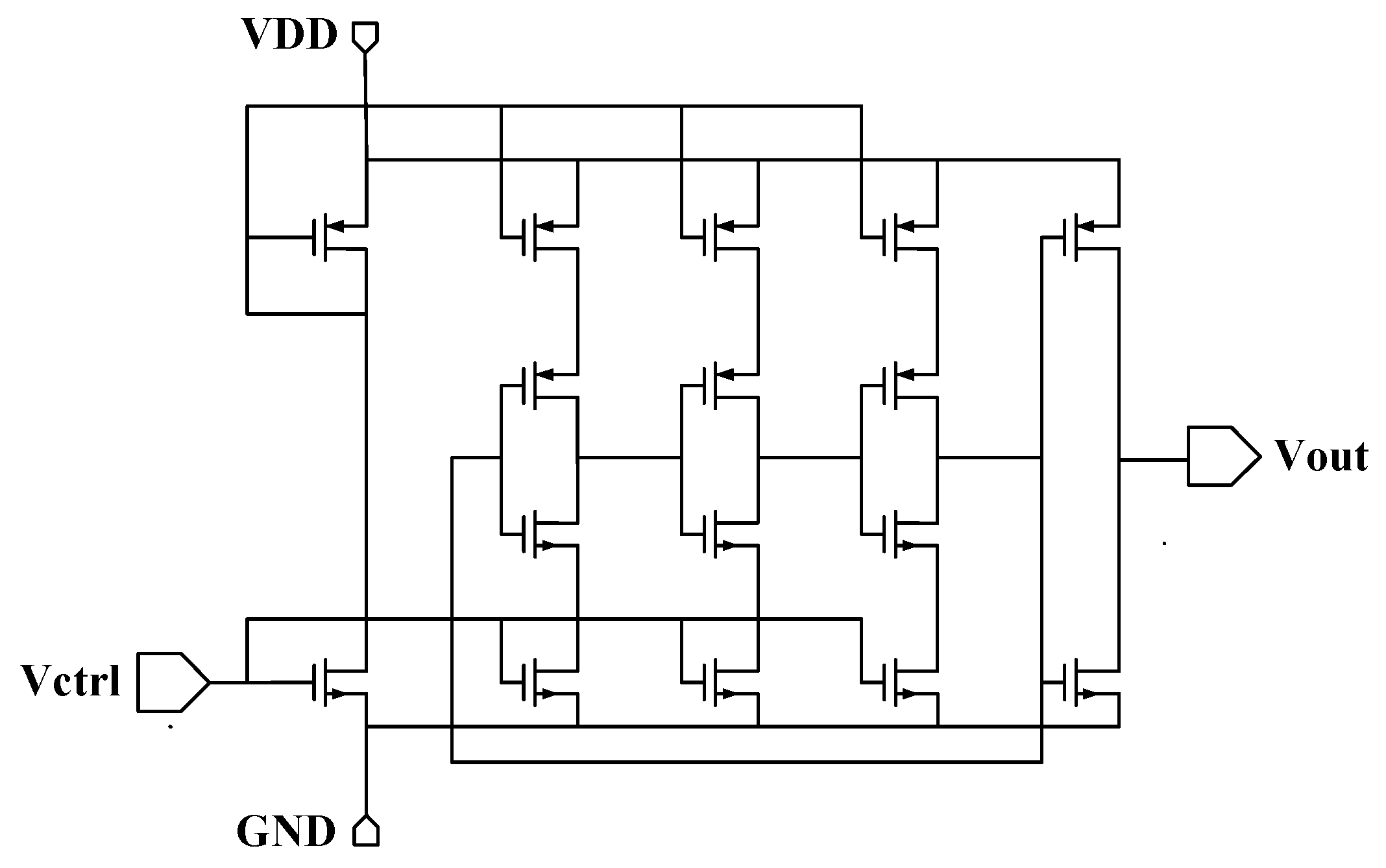

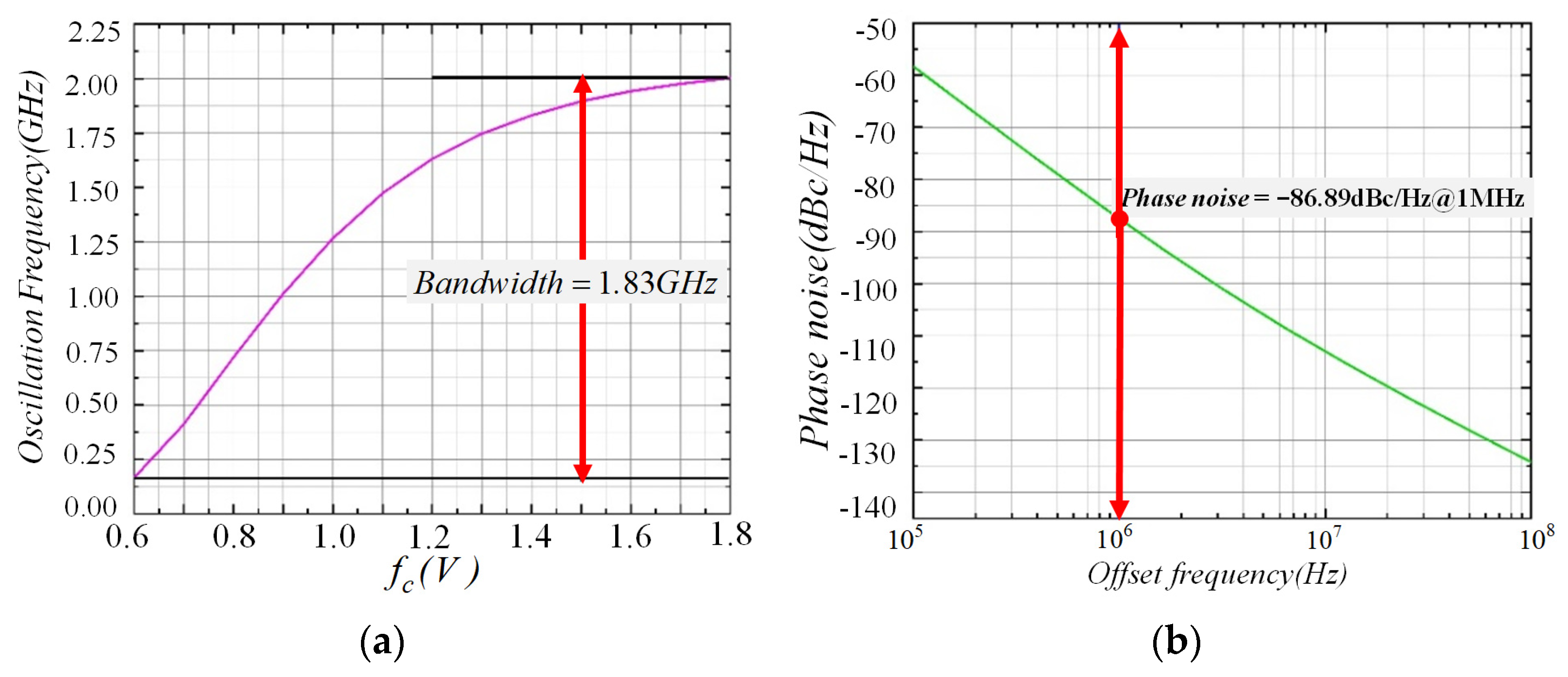

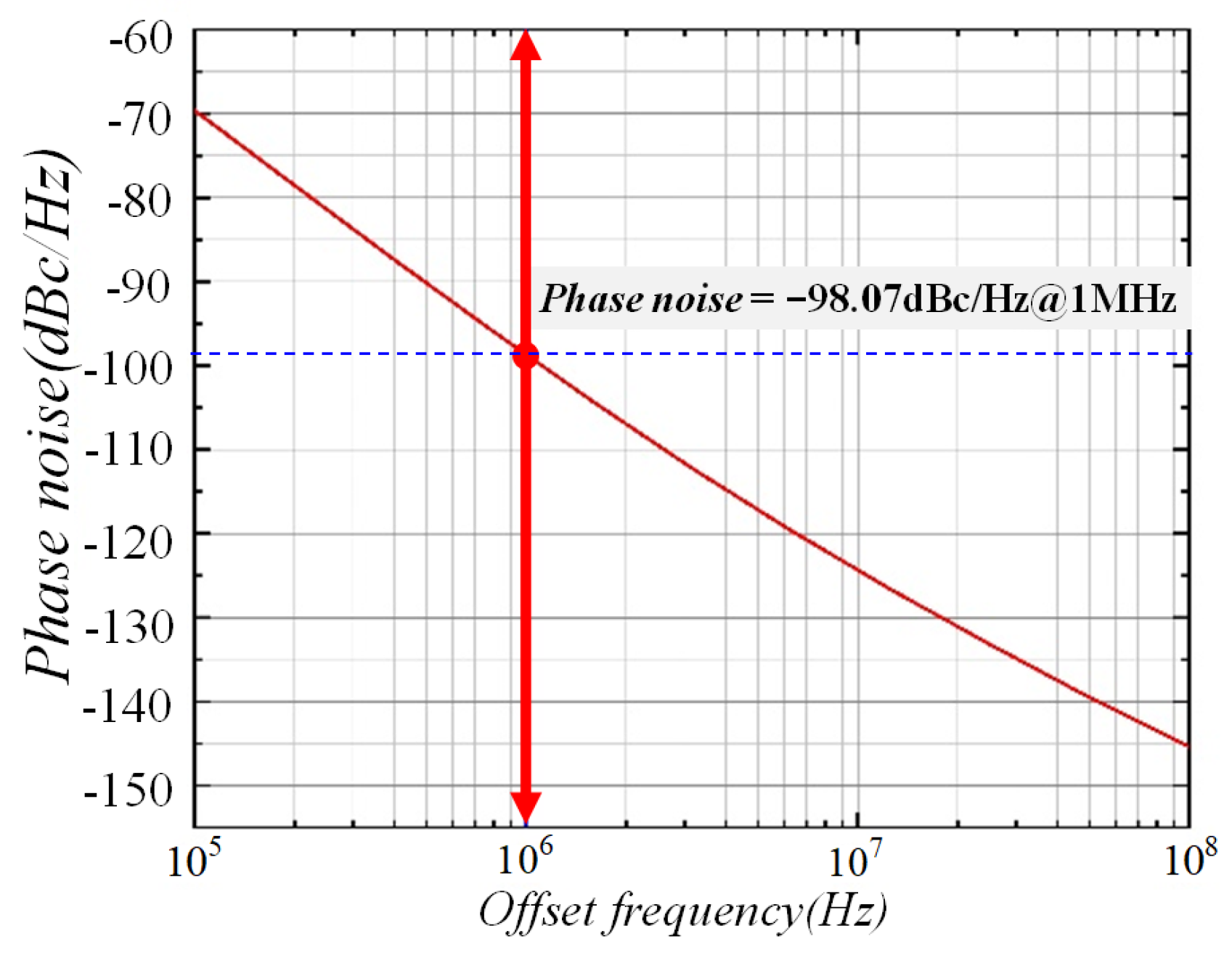

- A novel coarse- or fine-grained programmable frequency tunable ring voltage-controlled oscillator (VCO) is proposed, which can be adaptively tuned to the third or the fifth order by the TDC in order to dynamically optimize the phase noise and power consumption, leading to an optimal performance tradeoff.

2. PLL Design and Implementation

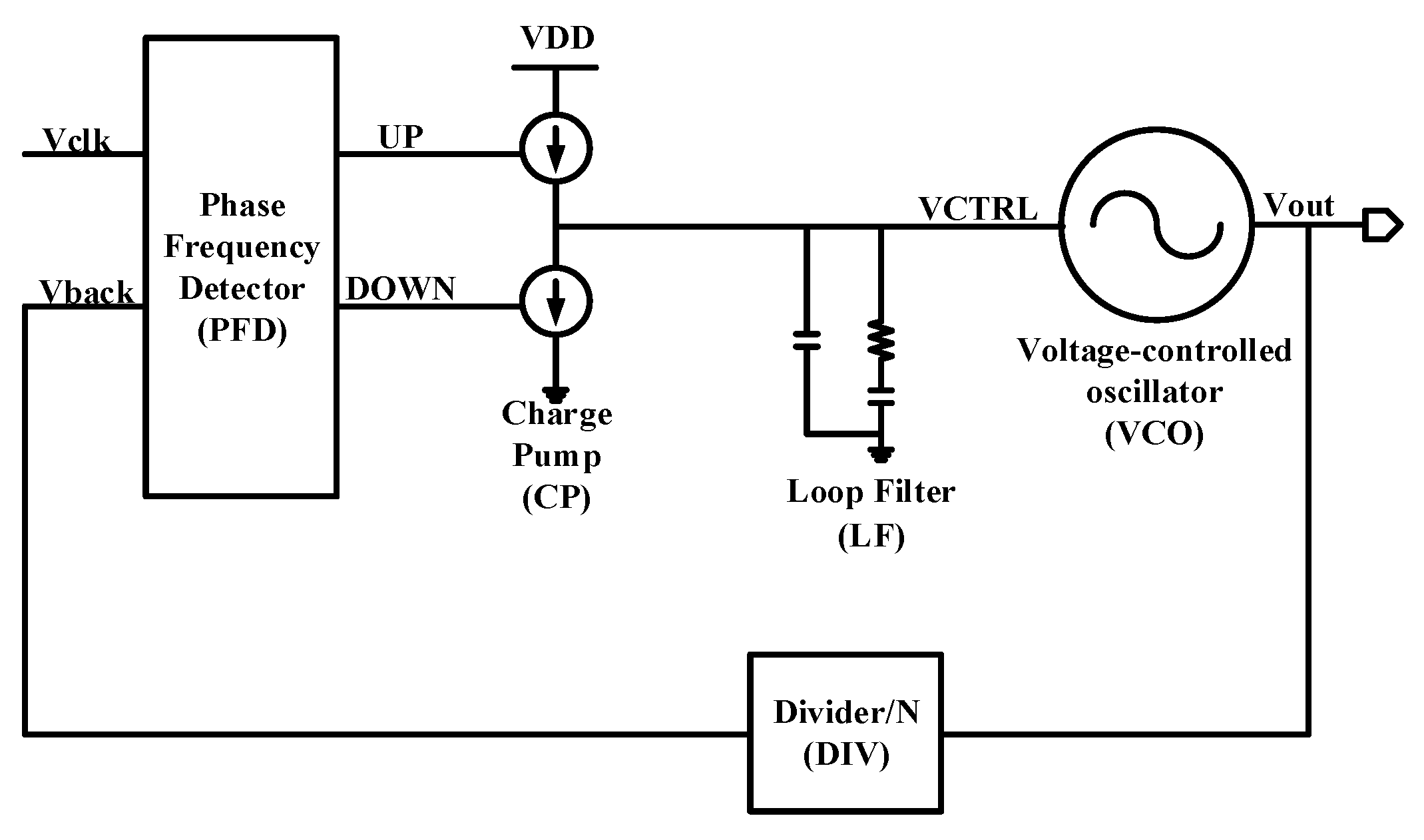

2.1. Previous Work

2.2. Proposed PLL Architecture

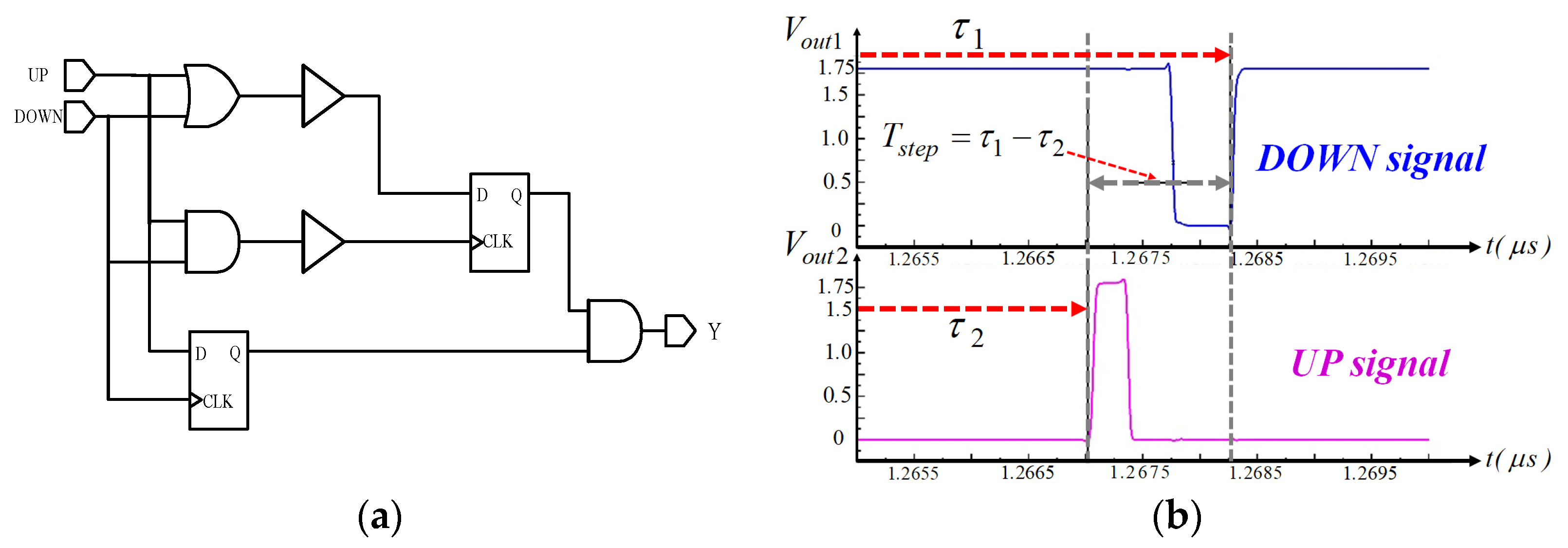

2.3. TDC-Aided Control

3. Design Tradeoff of Fast-Locking and Other Features

3.1. Theoretical Analysis of Phase Locking

3.2. Principle and Design of Ring-VCO

3.3. Feature Analysis of Individual Three-Stage and Five-Stage Ring Oscillators

3.4. Proposed TDC-Control-Based Adaptive Dual-Mode Switchable Ring-VCO

4. Performance Verification and Discussion

4.1. Simulation-Based Analysis

4.2. Comparison of Design Cases

5. Conclusions and Future Work

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Azadmousavi, T.; Azadbakht, M.; Aghdam, E.N.; Frounchi, J. A novel zero dead zone PFD and efficient CP for PLL applications. Analog. Integr. Circuit Signal Process. 2018, 95, 83–91. [Google Scholar] [CrossRef]

- Ding, Z.; Liu, H.; Li, Q. Phase-error cancellation technique for fast-lock phase-locked loop. IET Circuts Devices Syst. 2016, 10, 417–422. [Google Scholar] [CrossRef]

- Sahani, J.K.; Singh, A.; Agarwal, A. A Fast Locking and Low Jitter hybrid ADPLL Architecture with Bang Bang PFD and PVT calibrated Flash TDC. AEU Int. J. Electron. Commun. 2020, 124, 153344. [Google Scholar] [CrossRef]

- Biswas, D.; Bhattacharyya, T.K. Spur reduction architecture for multiphase fractional PLLs. IET Circuts Devices Syst. 2019, 13, 1169–1180. [Google Scholar] [CrossRef]

- Xia, L.; Wu, J.; Huang, C.; Zhang, M. Built-in self-test structure for fault detection of charge-pump phase-locked loop. IET Circuts Devices Syst. 2016, 10, 317–321. [Google Scholar] [CrossRef]

- Huang, P.-C.; Chang, W.-S.; Lee, T.-C. 21.2 A 2.3 GHz fractional-N divider less phase locked loop with −112dBc/Hz in-band phase noise. In Proceedings of the 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 9–13 February 2014; pp. 362–363. [Google Scholar]

- Liu, Y.H.; van Den Heuvel, J.; Kuramochi, T.; Busze, B.; Mateman, P.; Chillara, V.K.; Wang, B.; Staszewski, R.B.; Philips, K. An ultra-low power 1.7~2.7GHz fractional-N sub- sampling digital frequency synthesizer and modulator for IoT applications in 40nm CMOS. IEEE Trans. Circuits Syst. 2017, 64, 1094–1105. [Google Scholar] [CrossRef]

- Ali, M.K.M.; Hashemipour, O. Fast locking technique for phase locked loop based on phase error cancellation. AEU—Int. J. Electron. Commun. 2019, 109, 99–106. [Google Scholar]

- Dinesh, R.; Dinesh, R. A wide range high resolution digital controlled oscillator with high precision time to digital convertor for optimal sampling digital PLL. Microprocess. Microsyst. 2020, 74, 103013. [Google Scholar] [CrossRef]

- Deng, W.; Yang, D.S.; Ueno, T.; Siriburanon, T.; Kondo, S.; Okada, K.; Matsuzawa, A. A Fully Synthesizable All-Digital PLL With Interpolative Phase Coupled Oscillator, Current-Output DAC, and Fine-Resolution Digital Varactor Using Gated Edge Injection Technique. IEEE J. Solid-State Circuits 2015, 50, 68–80. [Google Scholar] [CrossRef]

- Su, R.; Lanzisera, S.; Pister, K.S.J. A 2.6ps rms-Period-Jitter 900MHz All-Digital Fractional-N PLL Built with Standard Cells. In Proceedings of the 2011 ESSCIRC, Helsinki, Finland, 12–16 September 2011; pp. 455–458. [Google Scholar]

- Aravinda, K.; Kuppushetty, R.T. Integer-N charge pump phase locked loop for 2.4 GHz application with a novel design of phase frequency detector. IET Circuts Devices Syst. 2020, 14, 60–65. [Google Scholar]

- Sofimowloodi, S.; Razaghian, F.; Gholami, M. Low-Power High-Frequency Phase Frequency Detector for Minimal Blind-Zone Phase-Locked Loops. Circuits Syst. Signal Process. 2019, 38, 498–511. [Google Scholar] [CrossRef]

- Lo, Y.-L.; Ho, W.-H. A Low-Voltage PLL Design Using a New Calibration Technique for Low-Power Implantable Biomedical Systems. Circuits Syst. Signal Process. 2017, 36, 4809–4828. [Google Scholar] [CrossRef]

- Li, X.; Zhang, J.; Zhang, Y.; Wang, W.; Liu, H.; Lu, C. A 5.7–6.0 GHz CMOS PLL with low phase noise and -68dBc reference spur. AEU-Int. J. Electron. Commun. 2018, 85, 23–31. [Google Scholar] [CrossRef]

- Arjun, R.P.; Liter, S. A TDC-less all-digital phase locked loop for medical implant applications. Microprocess. Microsyst. 2019, 6, 168–178. [Google Scholar]

- Albittar, I.F.; Dogan, H.; Ozgun, M.T. A novel biasing technique for low phase noise voltage controlled oscillators. Microelectron. J. 2018, 72, 120–125. [Google Scholar] [CrossRef]

- Jafari, B.; Sheikhaei, S. Low phase noise LC VCO with sinusoidal tail current shaping using cascode current source. AEU-Int. J. Electron. Commun. 2018, 83, 114–122. [Google Scholar] [CrossRef]

- Wei-Hao, C.; Yu-Hsiang, H.; Tsung-Hsien, L. A Dynamic Phase Error Compensation Technique for Fast-Locking Phase-Locked Loops. IEEE J. Solid State Circuits 2010, 45, 1137–1149. [Google Scholar]

- Erfani-Jazi, H.R.; Ghaderi, N. A divider-less, high speed and wide locking range phase locked loop. AEU-Int. J. Electron. Commun. 2015, 69, 722–729. [Google Scholar] [CrossRef]

- Hati, M.K.; Bhattacharyya, T.K. Phase noise analysis of proposed PFD and CP switching circuit and its advantages over various PFD/CP switching circuits in phase-locked loops. Integration 2018, 63, 115–129. [Google Scholar] [CrossRef]

- Wu, Y.; Shahmohammdi, M.; Chen, Y.; Lu, P.; Staszewski, R.B. A 3.5–6.8-GHz wide-bandwidth DTC-Assisted fractional-N all-digital PLL with a MASH $delta sigma $ -TDC for low in-band phase noise. IEEE J. Solid-State Circuits 2017, 52, 1885–1903. [Google Scholar] [CrossRef]

- Mazloum, J.; Sheikhaei, S. 1/f 3 (Close-in) Phase Noise Reduction by Tail Transistor Flicker Noise Suppression Technique. J. Circuits Syst. Comput. 2020, 29, 2050035. [Google Scholar] [CrossRef]

- Henzler, S. Time-to-Digital Converters; Springer: New York, NY, USA, 2010. [Google Scholar]

- Hati, M.K.; Bhattacharyya, T.K. A fast automatic frequency and amplitude control LC-VCO circuit with noise filtering technique for a fractional-N PLL frequency synthesizer. Microelectron. J. 2016, 52, 134–146. [Google Scholar] [CrossRef]

- Tsai, C.H.; Zong, Z.; Pepe, F.; Mangraviti, G.; Craninckx, J.; Wambacq, P. Analysis of a 28-nm CMOS Fast-Lock Bang-Bang Digital PLL With 220-fs RMS Jitter for Millimeter-Wave Communication. IEEE J. Solid-State Circuits 2020, 50, 1854–1863. [Google Scholar] [CrossRef]

- Yao, C.; Ni, R.; Lau, C.; Wu, W.; Godbole, K.; Zuo, Y.; Ko, S.; Kim, N.-S.; Han, S.; Jo, I.; et al. A 14-nm 0.14-psrms fractional-N digital PLL with a 0.2ps resolution ADC-assisted coarse/fine-conversion chopping TDC and TDC nonlinearity calibration. IEEE J. Solid-State Circuts 2017, 52, 3446–3457. [Google Scholar] [CrossRef]

- Qiu, Y.S.; Zhao, L.; Zhang, F. Design of 0.35-ps RMS Jitter 4.4–5.6-GHz Frequency Synthesizer with Adaptive Frequency Calibration Using 55-nm CMOS Technology. Circuits Syst. Signal Process. 2018, 17, 1489–1504. [Google Scholar] [CrossRef]

- Kashani, Z.G.; Avanji, S.A.I. Fully integrated fractional-N phase-locked loop for GNSS standards. IET Microw. Antennas Propag. 2019, 13, 2391–2395. [Google Scholar] [CrossRef]

- Amourah, M.; Whately, M. A Novel Switched Capacitor Filter Based Low-Area and Fast-Locking PLL. In Proceedings of the 2015 IEEE Custom Integrated Circuits Conference, San Jose, CA, USA, 28–30 September 2015; pp. 1–6. [Google Scholar]

| Performance Index | Pre-Opti. | Post-Opti. |

|---|---|---|

| Voltage [V] | 1.80 | 1.80 |

| Temperature [°C] | 25 | 25 |

| PN [dBc/Hz@1 MHz] | −78.13 | −98.07 |

| Power [μW] | 244.47 | 382.12 |

| FoM [dBc/Hz] | −150.41 | −157.06 |

| Process Corner | TT | SS | FF |

|---|---|---|---|

| Technology [nm] | 180 | 180 | 180 |

| Voltage [V] | 1.80 | 1.62 | 1.98 |

| Temperature [°C] | 25 | 120 | −40 |

| Lock Time [μs] | 1.11 | 0.82 | 0.57 |

| Power Diss. [mW] | 1.86 | 0.85 | 3.43 |

| Items | [1] | [2] | [14] | [15] | [26] | [27] | [28] | [29] | [30] | This Work |

|---|---|---|---|---|---|---|---|---|---|---|

| Technology [nm] | 180 | 130 | 180 | 130 | 28 | 14 | 55 | 180 | 65 | 180 |

| Supply voltage [V] | 1.80 | 1.20 | 0.70 | 1.50 | N/A | 0.80 | 1.20 | 1.80 | N/A | 1.80 |

| Phase noise [dBc/Hz @1 MHz] | −100 | N/A | −99.5 | −109 | −99.3 | −113.6 | −110 | −90 | N/A | −98.07 |

| Output freq. range [GHz] | 4.8–5.0 | 2.32–2.56 | N/A | 5.7–6.0 | 22.5–27.7 | N/A | 4.4–5.6 | 1.06–1.60 | 0.2–2.0 | 0.05–0.324 |

| Power dissipation [mW] | 11 | N/A | 0.43 | 12 | 25 | 13.4 | 20 | 11 | 9 | 1.86 |

| Locking time [μs] | 5 | 2.5 | 18 | N/A | 45 | 310 | 15 | 5 | 9.34 | 1.11 |

| Data type | Sim | Sim | Meas | Meas | Meas | Meas | Meas | Sim | Meas | Sim |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Sun, L.; Luo, Y.; Deng, Z.; Wang, J.; Liu, B. Novel Power-Efficient Fast-Locking Phase-Locked Loop Based on Adaptive Time-to-Digital Converter-Aided Acceleration Compensation Technology. Electronics 2024, 13, 3586. https://doi.org/10.3390/electronics13183586

Sun L, Luo Y, Deng Z, Wang J, Liu B. Novel Power-Efficient Fast-Locking Phase-Locked Loop Based on Adaptive Time-to-Digital Converter-Aided Acceleration Compensation Technology. Electronics. 2024; 13(18):3586. https://doi.org/10.3390/electronics13183586

Chicago/Turabian StyleSun, Ligong, Yixin Luo, Zhiyao Deng, Jinchan Wang, and Bo Liu. 2024. "Novel Power-Efficient Fast-Locking Phase-Locked Loop Based on Adaptive Time-to-Digital Converter-Aided Acceleration Compensation Technology" Electronics 13, no. 18: 3586. https://doi.org/10.3390/electronics13183586