Design of Stabilizing Network for Capacitive Power Transfer Transmitter Operating at Maximum Power Transfer Limiting the Voltage Gain in Resonant Capacitors

Abstract

1. Introduction

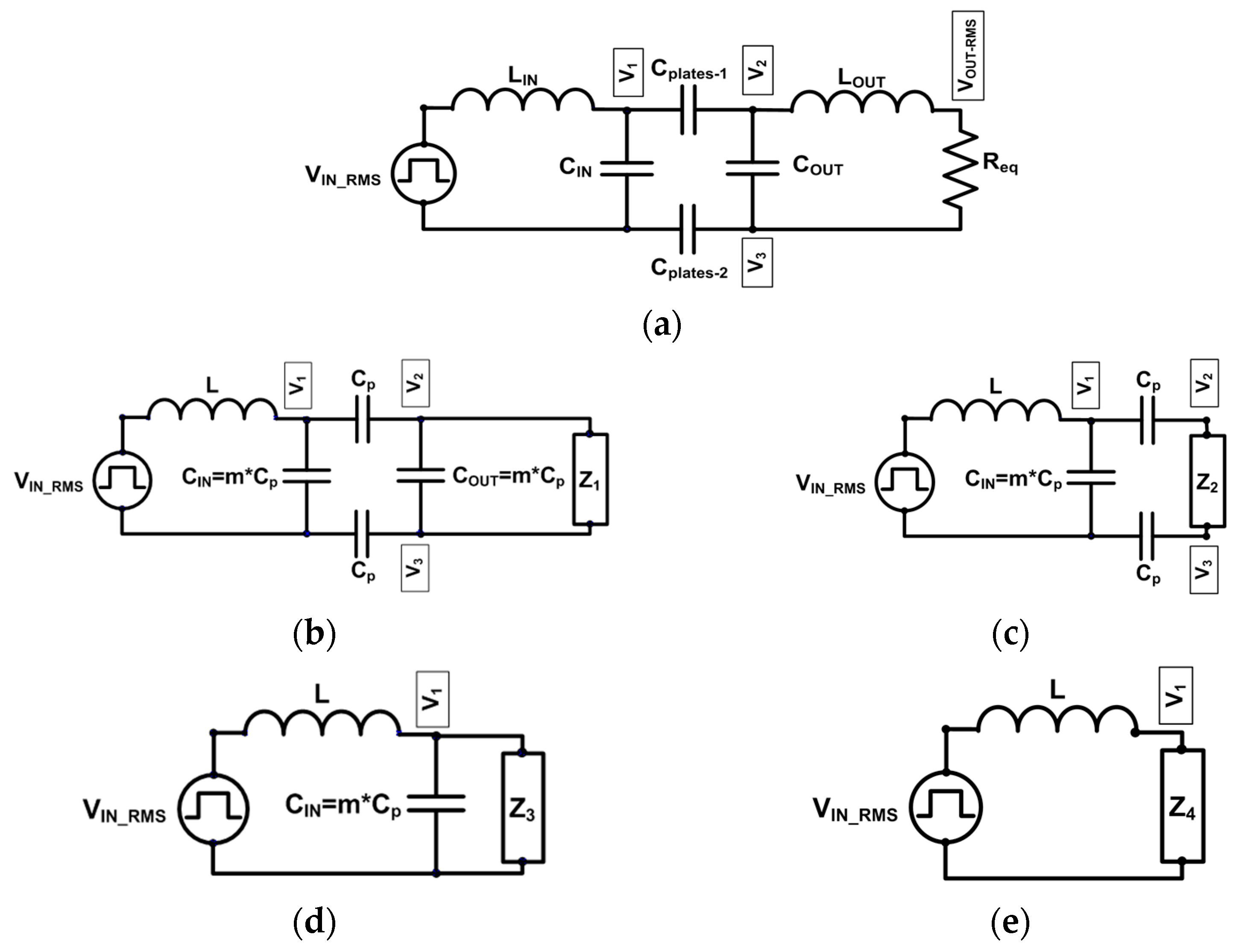

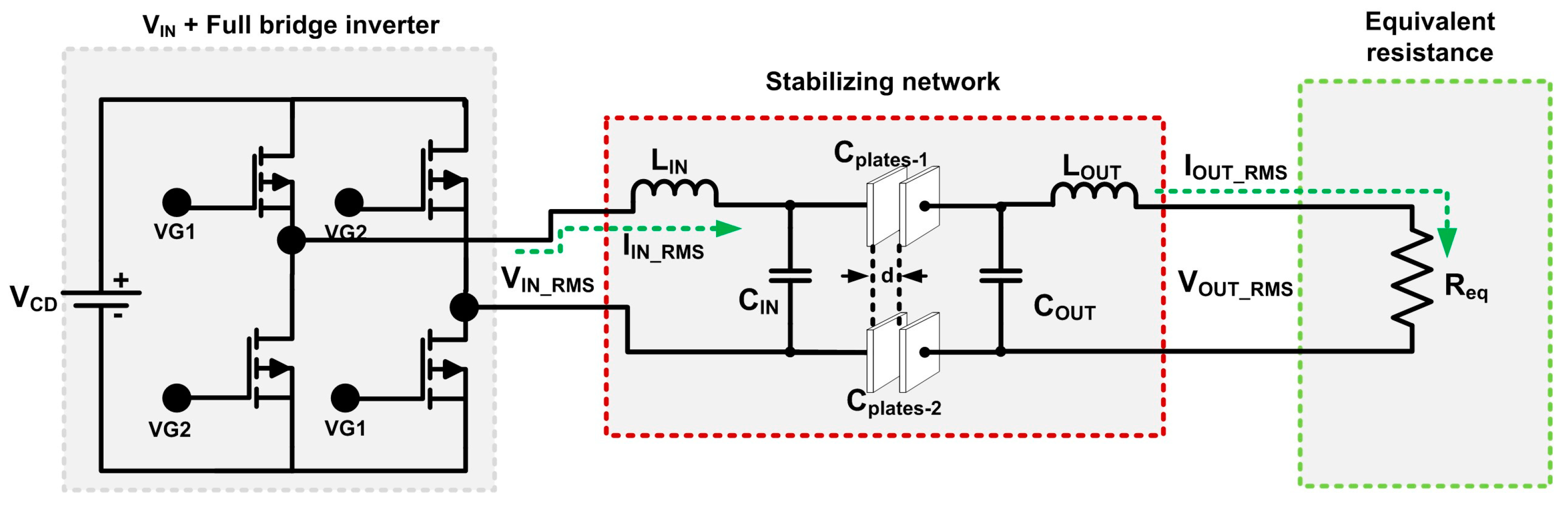

2. Design of Stabilizing Network

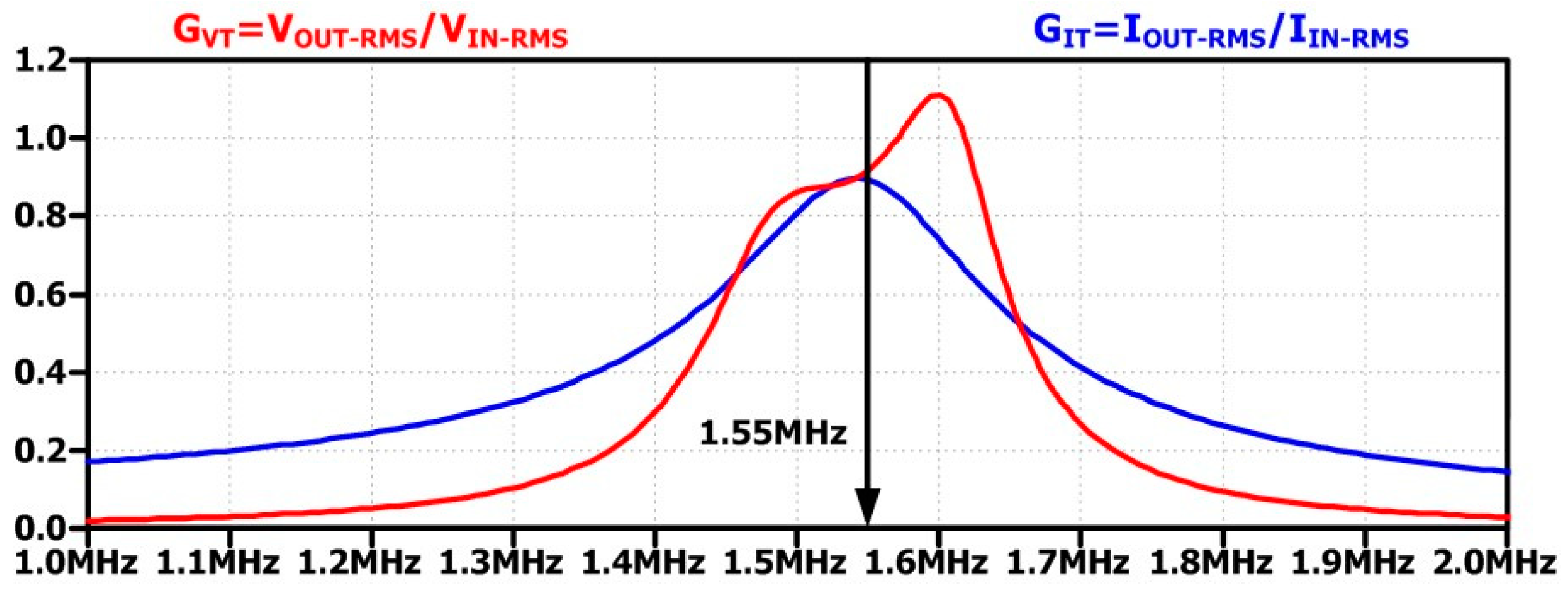

2.1. Stabilizing Network Analysis

2.2. Coupling Capacitances

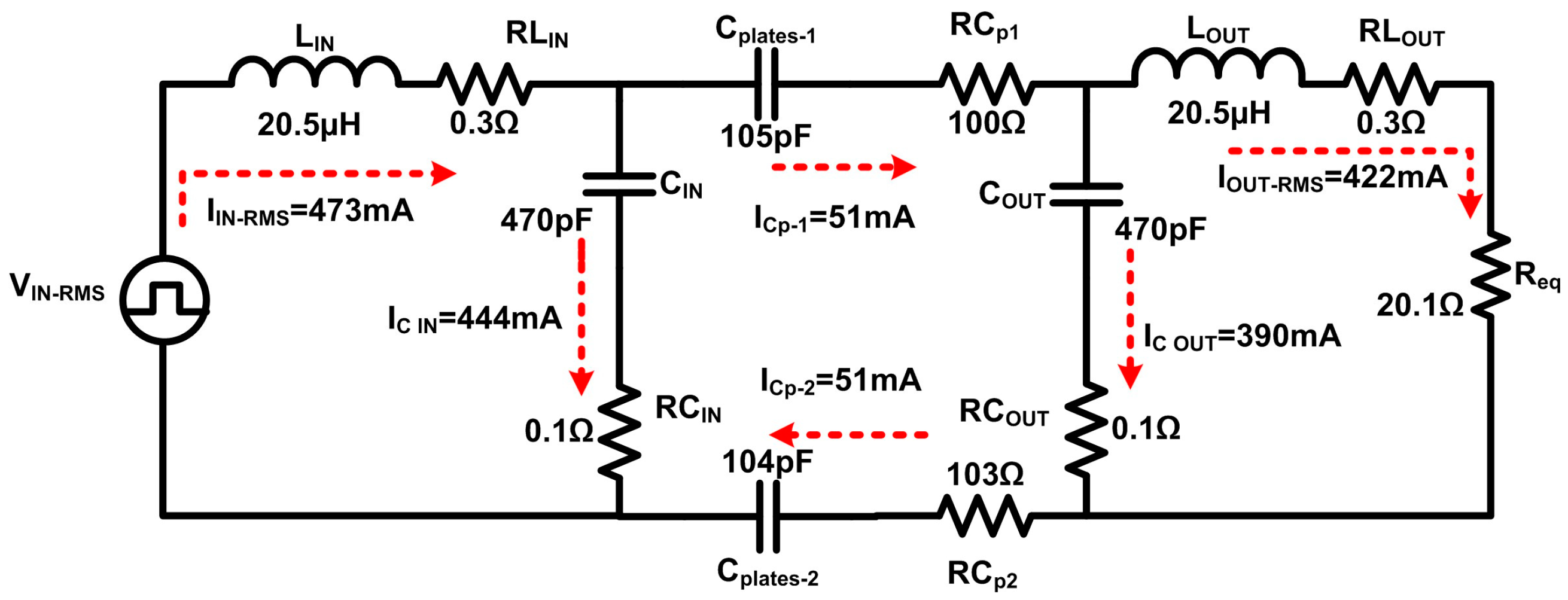

2.3. Proposed Calculation Methodology and Experimental Prototype Calculation

- The values of Cp, the inverter supply voltage (VCD), the operation frequency of the inverter, and the power at the output (PReq) are determined, and an initial value of is used.

- Req is obtained by (17) considering VOUT-RMS = VIN-RMS because the system operates at :

- The resonant capacitances (CIN = COUT = C) are calculated according to (15).

- The closest commercial value of C is selected, and the maximum voltage value at which it operates (VC-Max) is determined.

- The real value of is calculated with .

- Using Figure 2 and the VIN-RMS value, the voltages that will be generated in the CIN and COUT capacitors are estimated. These voltages must meet the following conditions to avoid component damage.

- The normalized resonance frequency () and are calculated with Equation (11).

- The inductors (LIN = LOUT = L) are obtained with (20) to operate in resonance.

3. Results

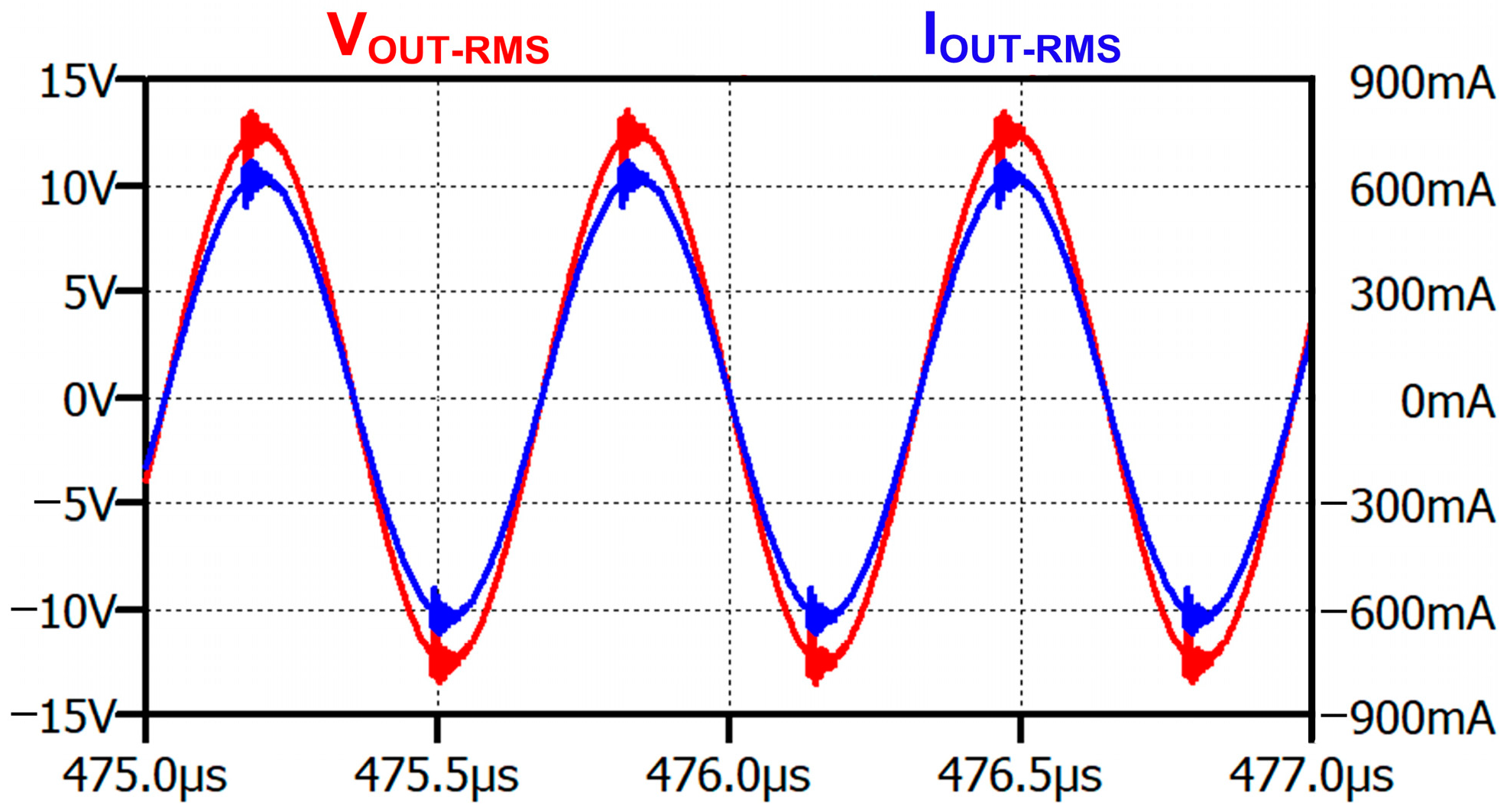

3.1. Simulation Verification

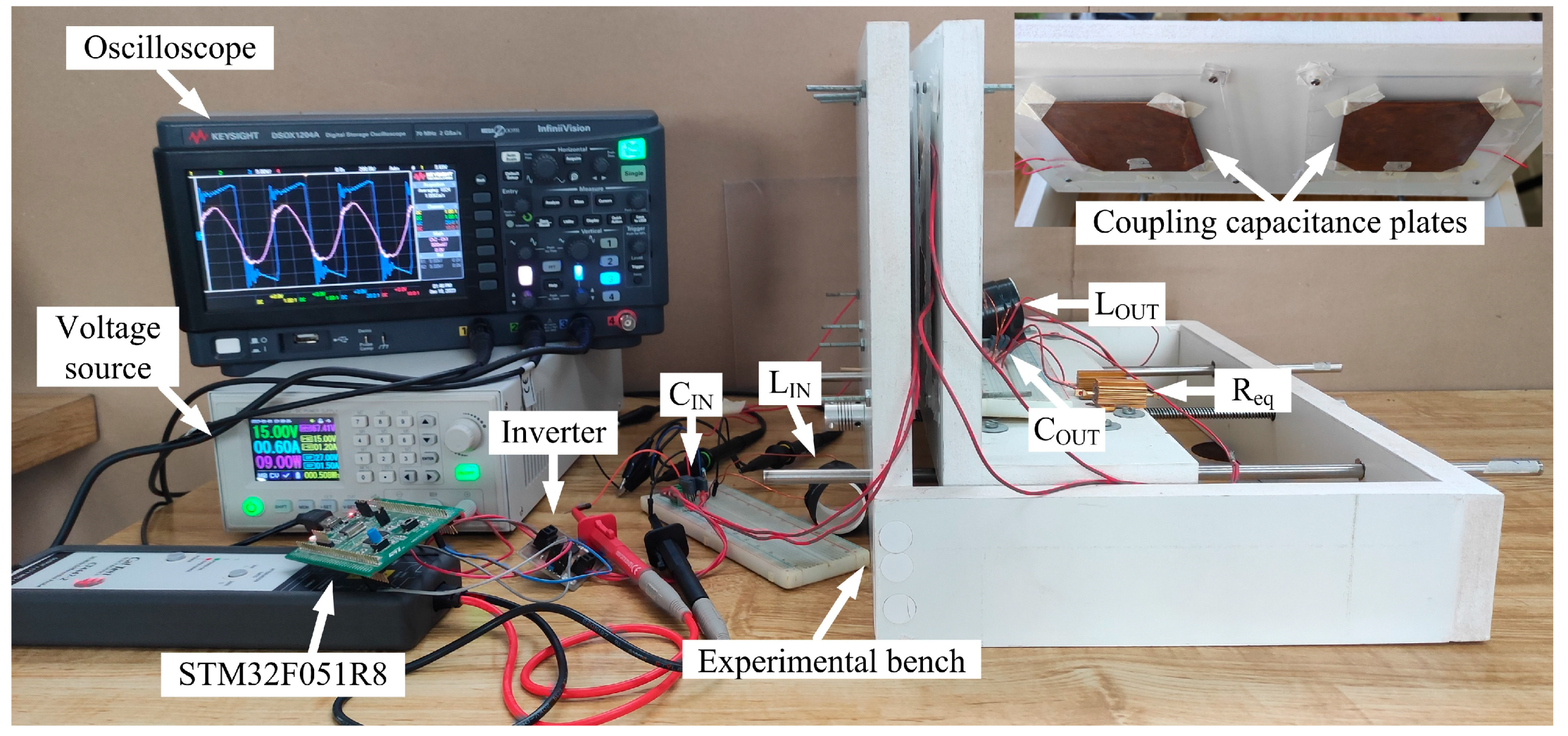

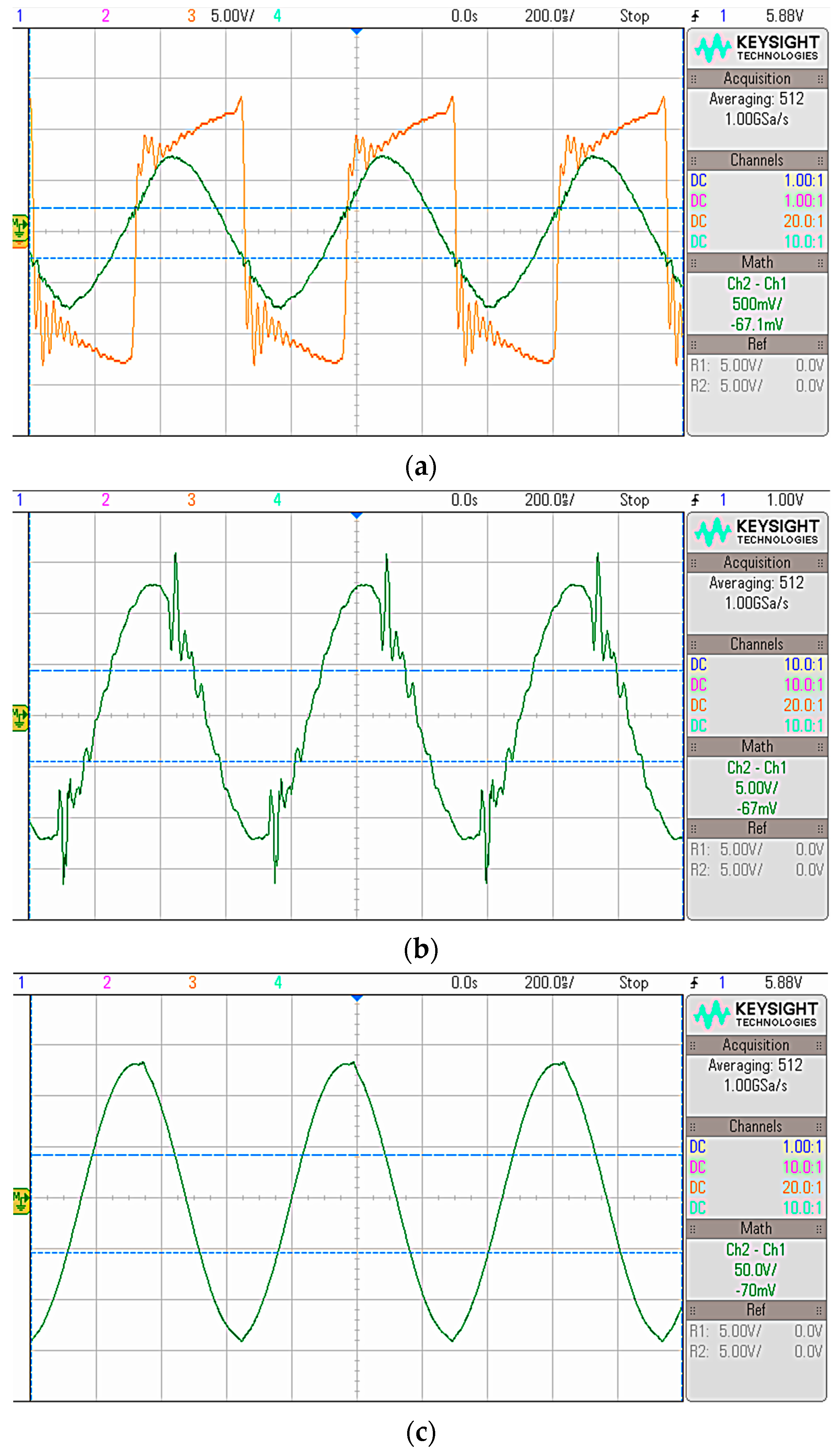

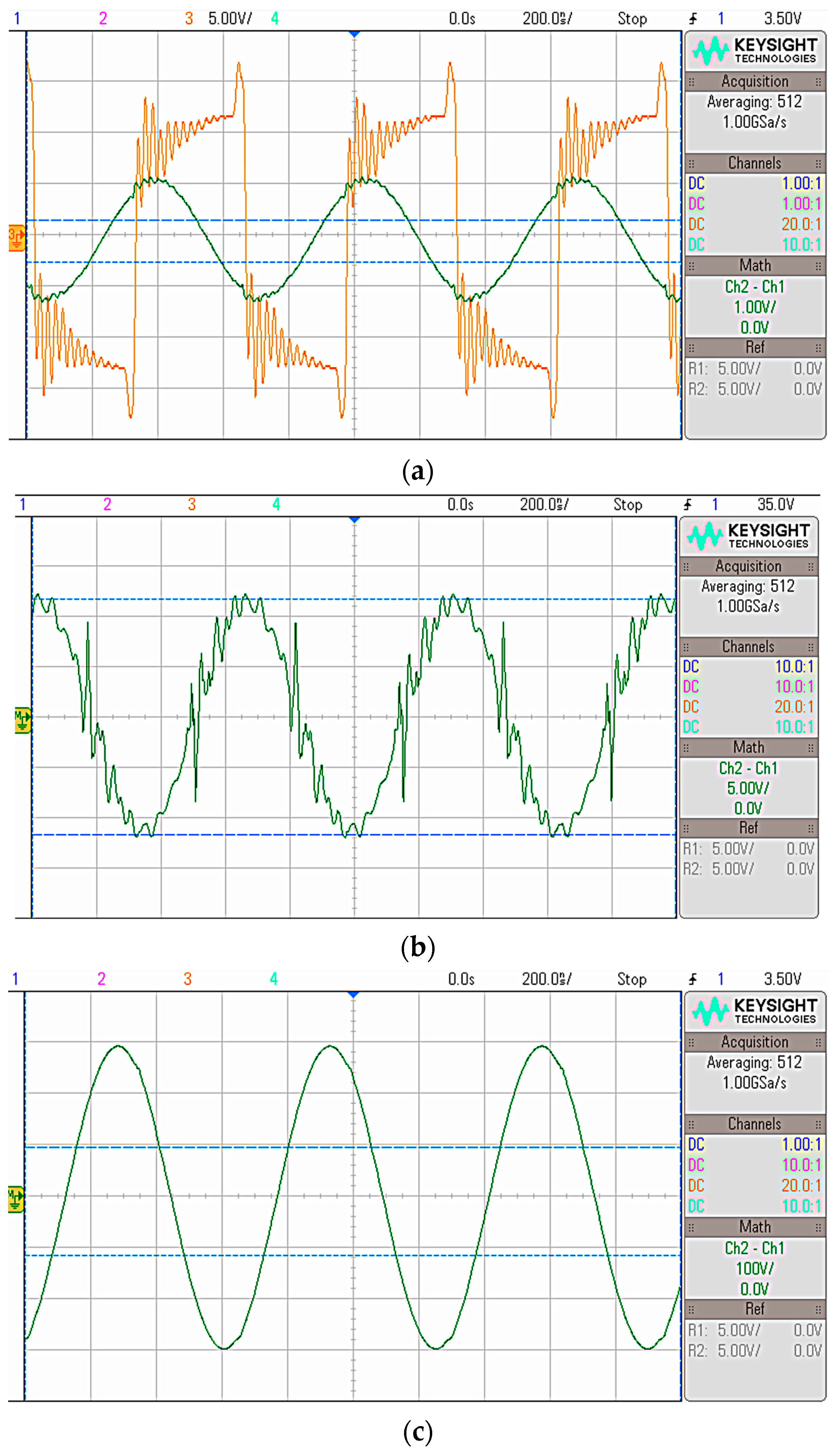

3.2. Experimental Verification

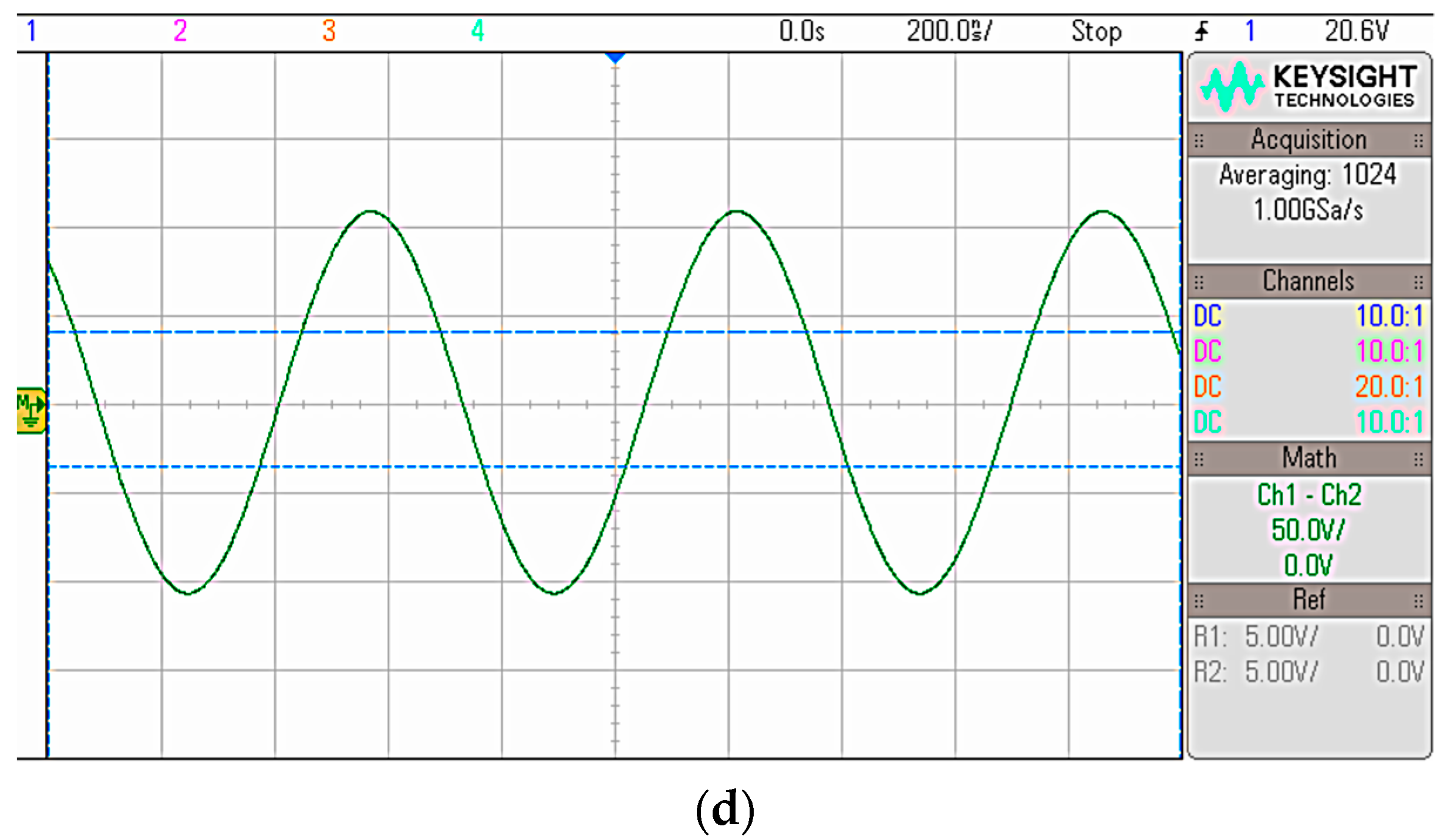

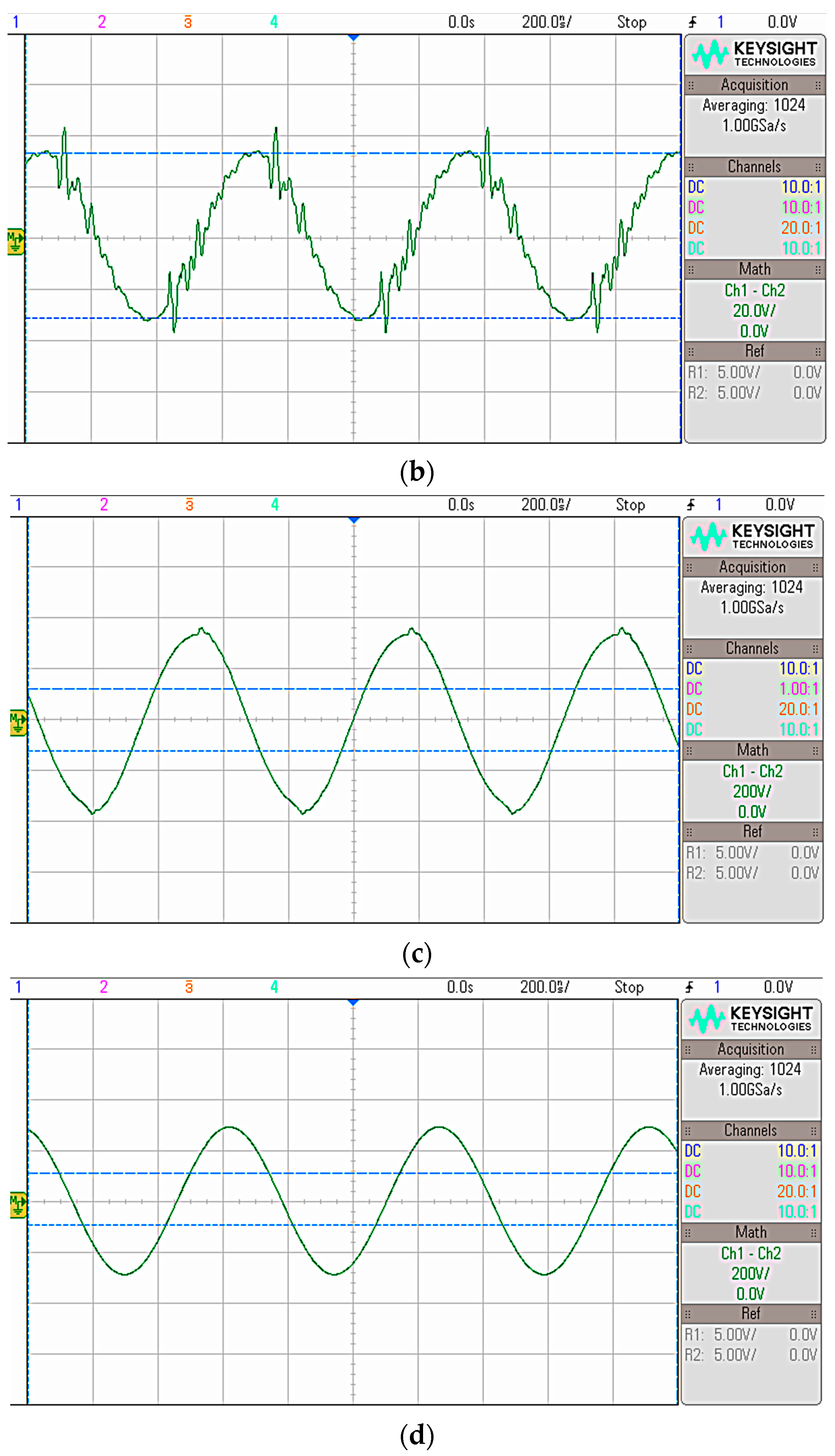

3.3. Power Increase

4. Discussion

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

Appendix A

References

- Stankiewicz, J.M. Analysis of the Wireless Power Transfer System Using a Finite Grid of Planar Circular Coils. Energies 2023, 16, 7651. [Google Scholar] [CrossRef]

- Lecluyse, C.; Minnaert, B.; Kleemann, M. A Review of the Current State of Technology of Capacitive Wireless Power Transfer. Energies 2021, 14, 5862. [Google Scholar] [CrossRef]

- Nguyen, M.T.; Nguyen, C.V.; Truong, L.H.; Le, A.M.; Quyen, T.V.; Masaracchia, A.; Teague, K.A. Electromagnetic Field Based WPT Technologies for UAVs: A Comprehensive Survey. Electronics 2020, 9, 461. [Google Scholar] [CrossRef]

- Triviño, A.; González-González, J.M.; Aguado, J.A. Wireless Power Transfer Technologies Applied to Electric Vehicles: A Review. Energies 2021, 14, 1547. [Google Scholar] [CrossRef]

- Agarwal, K.; Jegadeesan, R.; Guo, Y.-X.; Thakor, N.V. Wireless Power Transfer Strategies for Implantable Bioelectronics. IEEE Rev. Biomed. Eng. 2017, 10, 136–161. [Google Scholar] [CrossRef]

- Park, C.; Park, J.; Shin, Y.; Kim, J.; Huh, S.; Kim, D.; Park, S.; Ahn, S. Separated Circular Capacitive Coupler for Reducing Cross-Coupling Capacitance in Drone Wireless Power Transfer System. IEEE Trans. Microw. Theory Tech. 2020, 68, 3978–3985. [Google Scholar] [CrossRef]

- Mahdi, H.; Hoff, B.; Østrem, T. Optimal Solutions for Underwater Capacitive Power Transfer. Sensors 2021, 21, 8233. [Google Scholar] [CrossRef]

- Tamura, M.; Murai, K.; Matsumoto, M. Design of Conductive Coupler for Underwater Wireless Power and Data Transfer. IEEE Trans. Microw. Theory Tech. 2021, 69, 1161–1175. [Google Scholar] [CrossRef]

- Lu, F.; Zhang, H.; Mi, C. A Two-Plate Capacitive Wireless Power Transfer System for Electric Vehicle Charging Applications. IEEE Trans. Power Electron. 2018, 33, 964–969. [Google Scholar] [CrossRef]

- Yi, K. Capacitive Coupling Wireless Power Transfer with Quasi-LLC Resonant Converter Using Electric Vehicles’ Windows. Electronics 2020, 9, 676. [Google Scholar] [CrossRef]

- Erfani, R.; Marefat, F.; Mohseni, P. A Dual-Output Single-Stage Regulating Rectifier with PWM and Dual-Mode PFM Control for Wireless Powering of Biomedical Implants. IEEE Trans. Biomed. Circuits Syst. 2020, 14, 1195–1206. [Google Scholar] [CrossRef]

- Nag, S.; Koruprolu, A.; Saikh, S.M.; Erfani, R.; Mohseni, P. Auto-Resonant Tuning for Capacitive Power and Data Telemetry Using Flexible Patches. IEEE Trans. Circuits Syst. II Express Briefs 2020, 67, 1804–1808. [Google Scholar] [CrossRef]

- Ramos, I.; Afridi, K.; Estrada, J.A.; Popovic, Z. Near-field capacitive wireless power transfer array with external field cancellation. In Proceedings of the IEEE Wireless Power Transfer Conference (WPTC) 2016, Aveiro, Portugal, 5–6 May 2016; pp. 1–4. [Google Scholar]

- Regensburger, B.; Sinha, S.; Kumar, A.; Vance, J.; Popovic, Z.; Afridi, K.K. Kilowatt-scale large air-gap multi-modular capacitive wireless power transfer system for electric vehicle charging. In Proceedings of the IEEE Applied Power Electronics Conference and Exposition (APEC) 2018, San Antonio, TX, USA, 4–8 March 2018; pp. 666–671. [Google Scholar]

- Zou, L.J.; Hu, A.P. A Contactless Single-Wire CPT (Capacitive Power Transfer) Power Supply for Driving a Variable Message Sign. In Proceedings of the IEEE PELS Workshop on Emerging Technologies: Wireless Power Transfer 2018, Montréal, QC, Canada, 3–7 June 2018; pp. 1–5. [Google Scholar]

- Zhang, H.; Lu, F.; Hofmann, H.; Liu, W.; Mi, C. Six-Plate Capacitive Coupler to Reduce Electric Field Emission in Large AirGap Capacitive Power Transfer. IEEE Trans. Power Electron. 2018, 33, 665–675. [Google Scholar] [CrossRef]

- Lu, F.; Zhang, H.; Hofmann, H.; Mi, C. A Double-Sided LCLC Compensated Capacitive Power Transfer System for Electric Vehicle Charging. IEEE Trans. Power Electron. 2015, 30, 6011–6014. [Google Scholar] [CrossRef]

- Su, Y.-G.; Zhao, Y.-M.; Hu, A.P.; Wang, Z.-H.; Tang, C.-S.; Sun, Y. An F-Type Compensated Capacitive Power Transfer System Allowing for Sudden Change of Pickup. IEEE J. Emerg. Sel. Top. Power Electron. 2018, 7, 1084–1093. [Google Scholar] [CrossRef]

- Zhang, H.; Lu, F. An Improved Design Methodology of the Double-Sided LC-Compensated CPT System Considering the Inductance Detuning. IEEE Trans. Power Electron. 2019, 34, 11396–11406. [Google Scholar] [CrossRef]

- Mohamed, N.; Aymen, F.; Alqarni, M. Inductive Power Transmission System for Electric Car Charging Phase: Modeling plus Frequency Analysis. World Electr. Veh. J. 2021, 12, 267. [Google Scholar] [CrossRef]

- Mohamed, N.; Aymen, F.; Alqarni, M.; Turky, R.A.; Alamri, B.; Ali, Z.M.; Abdel Aleem, S.H.E. A new wireless charging system for electric vehicles using two receiver coils. Ain Shams Eng. J. 2022, 13, 101569. [Google Scholar] [CrossRef]

- Wu, X.-Y.; Su, Y.-G.; Hu, A.P.; Zou, L.J.; Liu, Z. A Sleeve-Type Capacitive Power Transfer System With Different Coupling Arrangements for Rotary Application. IEEE Access 2020, 8, 69148–69159. [Google Scholar] [CrossRef]

- Liu, Y.; Wu, T.; Fu, M. Interleaved Capacitive Coupler for Wireless Power Transfer. IEEE Trans. Power Electron. 2021, 36, 13526–13535. [Google Scholar] [CrossRef]

- Ahmad, S.; Muharam, A.; Hattori, R.; Uezu, A.; Mostafa, T.M. Shielded Capacitive Power Transfer (S-CPT) without Secondary Side Inductors. Energies 2021, 14, 4590. [Google Scholar] [CrossRef]

- Huh, S.; Ahn, D. Optimum Receiver-Side Tuning Capacitance for Capacitive Wireless Power Transfer. Electronics 2019, 8, 1543. [Google Scholar] [CrossRef]

- Xie, S.; Su, Y.; Zhou, W.; Zhao, Y.; Dai, X. An Electric-Field Coupled Power Transfer System with a Double-sided LC Network. J. Power Electron. 2018, 18, 289–299. [Google Scholar]

- Abramov, E.; Zeltser, I.; Peretz, M.M. A network-based approach for modeling resonant capacitive wireless power transfer systems. CPSS Trans. Power Electron. Appl. 2019, 4, 19–29. [Google Scholar] [CrossRef]

- Luo, B.; Hu, A.P.; Munir, H.; Zhu, Q.; Mai, R.; He, Z. Compensation Network Design of CPT Systems for Achieving Maximum Power Transfer Under Coupling Voltage Constraints. IEEE J. Emerg. Sel. Top. Power Electron. 2022, 10, 138–148. [Google Scholar] [CrossRef]

- Mostafa, T.M.; Bui, D.; Muharam, A.; Hu, A.P.; Hattori, R. Load Effect Analysis and Maximum Power Transfer Tracking of CPT System. IEEE Trans. Circuits Syst. I Regul. Pap. 2020, 67, 2836–2848. [Google Scholar] [CrossRef]

- Abramov, E.; Peretz, M.M. Adaptive Self-Tuned Controller IC for Resonant-Based Wireless Power Transfer Transmitters. IEEE Trans. Power Electron. 2021, 36, 12413–12431. [Google Scholar] [CrossRef]

- Truong, C.-T.; Choi, S.-J. Single-Stage Duty-Controlled Half-Bridge Inverter for Compact Capacitive Power Transfer System. IEEE Access 2021, 9, 119250–119261. [Google Scholar] [CrossRef]

- Sinha, S.; Kumar, A.; Afridi, K.K. Active variable reactance rectifier—A new approach to compensating for coupling variations in wireless power transfer systems. In Proceedings of the 2017 IEEE 18th Workshop on Control and Modeling for Power Electronics (COMPEL), Stanford, CA, USA, 9–12 July 2017; pp. 1–8. [Google Scholar]

- Liang, J.; Wu, D.; Yu, J. A Design Method of Compensation Circuit for High-Power Dynamic Capacitive Power Transfer System Considering Coupler Voltage Distribution for Railway Applications. Electronics 2021, 10, 153. [Google Scholar] [CrossRef]

- Dai, J.; Hagen, S.S.; Ludois, D.C. High-Efficiency Multiphase Capacitive Power Transfer in Sliding Carriages With Closed-Loop Burst-Mode Current Control. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 7, 1388–1398. [Google Scholar] [CrossRef]

- Mai, R.; Luo, B.; Chen, Y.; He, Z. Double-sided CL compensation topology-based component voltage stress optimization method for capacitive power transfer charging system. IET Power Electron. 2018, 11, 1153–1160. [Google Scholar] [CrossRef]

- Han, Y.; Perreault, D.J. Analysis and Design of High Efficiency Matching Networks. IEEE Trans. Power Electron. 2006, 21, 1484–1491. [Google Scholar] [CrossRef]

- Lu, F.; Zhang, H.; Hofmann, H.; Mi, C.C. A Double-Sided LC Compensation Circuit for Loosely Coupled Capacitive Power Transfer. IEEE Trans. Power Electron. 2018, 33, 1633–1643. [Google Scholar] [CrossRef]

- Erickson, R.W.; Maksimović, D. Resonant Conversion. In Fundamentals of Power Electronics, 2nd ed.; Kluwer Academic Publishers: Norwell, MA, USA, 2001; pp. 710–711. [Google Scholar]

- Lian, J.; Qu, X. Design of a Double-Sided LC Compensated Capacitive Power Transfer System with Capacitor Voltage Stress Optimization. IEEE Trans. Circuits Syst. II Express Briefs 2020, 67, 715–719. [Google Scholar] [CrossRef]

- Qing, X.-D.; Wang, Z.-H.; Su, Y.-G.; Zhao, Y.-M.; Wu, X.-Y. Parameter Design Method With Constant Output Voltage Characteristic for Bilateral LC-Compensated CPT System. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 8, 2707–2715. [Google Scholar] [CrossRef]

- Wu, Y.; Chen, Q.; Ren, X.; Zhang, Z. Efficiency Optimization Based Parameter Design Method for the Capacitive Power Transfer System. IEEE Trans. Power Electron. 2021, 36, 8774–8785. [Google Scholar] [CrossRef]

- Xiong, Q.; Shao, Y.; Sun, P.; Sun, J.; Rong, E.; Liang, Y. Constant output characteristics and design methodology of double side LC compensated capacitive power transfer. Sci. Rep. 2022, 12, 2663. [Google Scholar] [CrossRef]

| Length of the Plate | Capacitance Obtained |

|---|---|

| 5 cm × 5 cm | 25.17 pF |

| 10 cm × 10 cm | 94.88 pF |

| 20 cm × 20 cm | 365.7 pF |

| 30 cm × 30 cm | 818.6 pF |

| 40 cm × 40 cm | 1.44 nF |

| 50 cm × 50 cm | 2.25 nF |

| Parameter | Expected Value | Simulation | Experimental |

|---|---|---|---|

| 9 V | 9 V | 8.6 V | |

| 450 mA | 473 mA | 517 mA | |

| 9 V | 8.5 V | 8.6 V | |

| 450 mA | 422 mA | 427 mA | |

| 4 W | 3.6 W | 3.6 W | |

| 94 V | 96.8 V | 95 V | |

| 85 V | 83.6 V | 76 V | |

| 1 | 0.94 | 1 | |

| 1 | 0.9 | 0.82 | |

| <100% | 84.6% | 82.6% |

| 100 pF/4.6 | 8.6 V | 517 mA | 8.6 V | 427 mA | 1 | 0.82 | 95 V | 76 V | 19° | 82.6% |

| 90 pF/5.1 | 8.5 V | 567 mA | 8.8 V | 437 mA | 1.03 | 0.77 | 106 V | 77 V | 20.6° | 80% |

| 80 pF/5.75 | 8.6 V | 592 mA | 9.1 V | 452 mA | 1.05 | 0.76 | 119 V | 80 V | 19.5° | 80% |

| 70 pF/6.6 | 8.7 V | 657 mA | 9.3 V | 462 mA | 1.06 | 0.7 | 135 V | 80 V | 28.5° | 75% |

| 60 pF/7.6 | 8.8 V | 757 mA | 9 V | 447 mA | 1.02 | 0.59 | 155 V | 74 V | 35° | 60% |

| 50 pF/9.2 | 9.12 V | 857 mA | 8.8 V | 437 mA | 0.96 | 0.51 | 183 V | 64 V | 46° | 49% |

| 40 pF/11.5 | 9.37 V | 842 mA | 8.1 V | 402 mA | 0.86 | 0.47 | 210 V | 48 V | 56° | 41% |

| Parameter | Expected Value | Simulation | Experimental |

|---|---|---|---|

| 22.5 V | 22.4 V | 21.7 V | |

| 1.12 A | 1.17 A | 1.28 A | |

| 22.5 V | 21 V | 21.8 V | |

| 1.12 A | 1.05 A | 1.08 A | |

| 25 W | 22 W | 23.6 W | |

| 234 V | 243 V | 245 V | |

| 212 V | 210 V | 205 V | |

| 1 | 0.937 | 1 | |

| 1 | 0.9 | 0.84 | |

| <100% | 84.7% | 84.7% |

| Design of a Double-Sided LC Compensated… [39] | Parameter Design Method with Constant Output Voltage… [40] | Efficiency Optimization Based Parameter Design Method… [41] | Constant Output Characteristics and Design Methodology… [42] | Proposed Methodology | |

|---|---|---|---|---|---|

| Voltage supply | 24 V | 48 V | 128.68 V | 58.71 V (COV Mode)/58.82 V (COC Mode) | 25 V |

| Frequency | 200 kHz | 600 kHz | 1 MHz | 300 kHz | 1.55 MHz |

| Output power | Not mentioned | 64.8 W | 100 W | 209.56 W (COV Mode)/156.68 W (COC Mode) | 23.6 W |

| η | Not mentioned | 87.9% | 93.02% | 81.23% (COV Mode)/88.46% (COC Mode) | 84.7% |

| Voltage stress in capacitors (CIN/COUT) | 760 V/730 V (Max.) | Not mentioned | 772 V/799 V (RMS value) | Not mentioned | 245 V/205 V (RMS value) |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Estevez-Encarnacion, E.S.; Hernandez-Gonzalez, L.; Ramirez-Hernandez, J.; Juarez-Sandoval, O.U.; Guevara-Lopez, P.; Avalos Arzate, G. Design of Stabilizing Network for Capacitive Power Transfer Transmitter Operating at Maximum Power Transfer Limiting the Voltage Gain in Resonant Capacitors. Electronics 2024, 13, 3859. https://doi.org/10.3390/electronics13193859

Estevez-Encarnacion ES, Hernandez-Gonzalez L, Ramirez-Hernandez J, Juarez-Sandoval OU, Guevara-Lopez P, Avalos Arzate G. Design of Stabilizing Network for Capacitive Power Transfer Transmitter Operating at Maximum Power Transfer Limiting the Voltage Gain in Resonant Capacitors. Electronics. 2024; 13(19):3859. https://doi.org/10.3390/electronics13193859

Chicago/Turabian StyleEstevez-Encarnacion, Eduardo Salvador, Leobardo Hernandez-Gonzalez, Jazmin Ramirez-Hernandez, Oswaldo Ulises Juarez-Sandoval, Pedro Guevara-Lopez, and Guillermo Avalos Arzate. 2024. "Design of Stabilizing Network for Capacitive Power Transfer Transmitter Operating at Maximum Power Transfer Limiting the Voltage Gain in Resonant Capacitors" Electronics 13, no. 19: 3859. https://doi.org/10.3390/electronics13193859

APA StyleEstevez-Encarnacion, E. S., Hernandez-Gonzalez, L., Ramirez-Hernandez, J., Juarez-Sandoval, O. U., Guevara-Lopez, P., & Avalos Arzate, G. (2024). Design of Stabilizing Network for Capacitive Power Transfer Transmitter Operating at Maximum Power Transfer Limiting the Voltage Gain in Resonant Capacitors. Electronics, 13(19), 3859. https://doi.org/10.3390/electronics13193859