Simple Voltage Balancing Control of Four-Level Inverter

Abstract

:1. Introduction

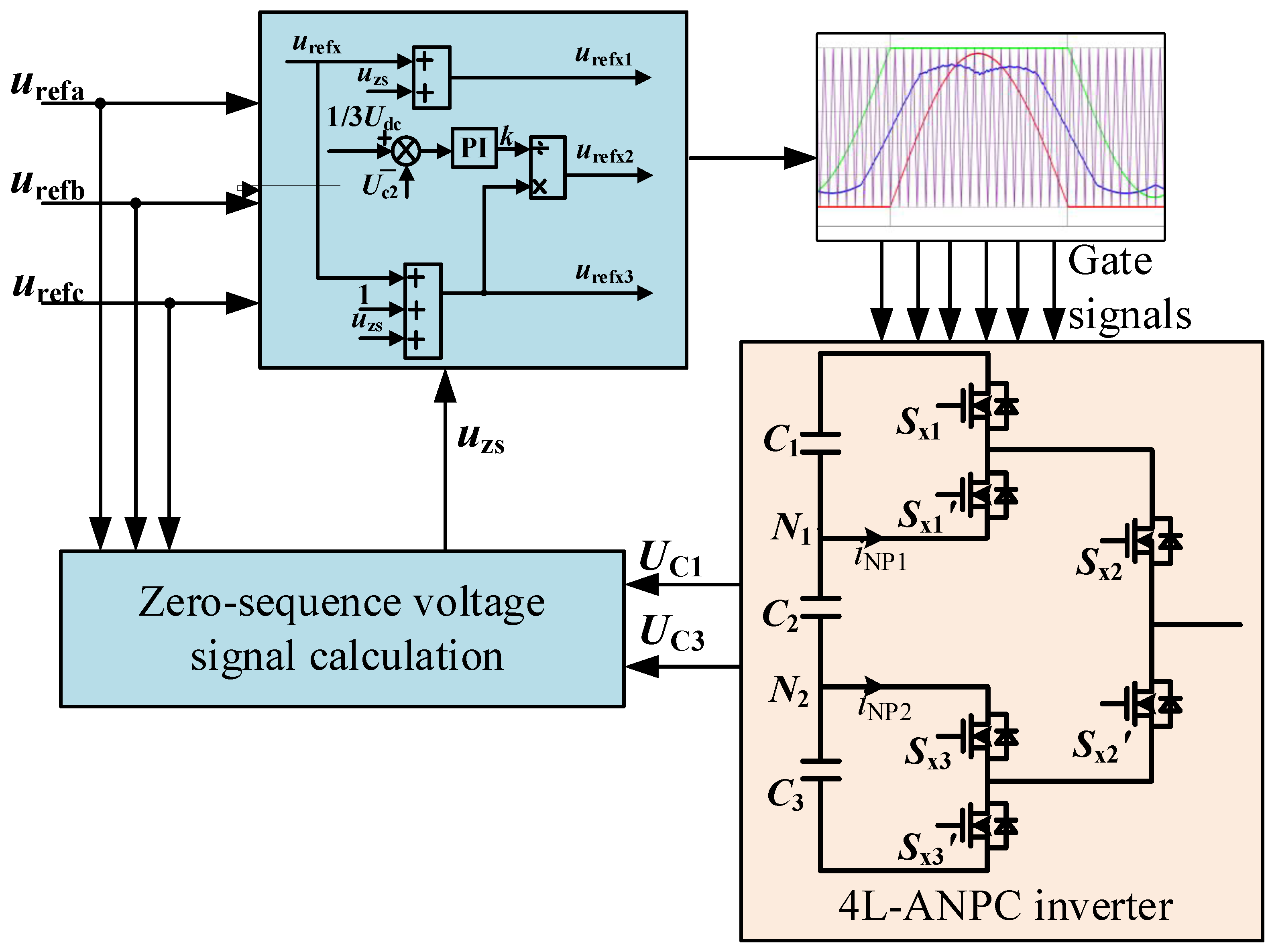

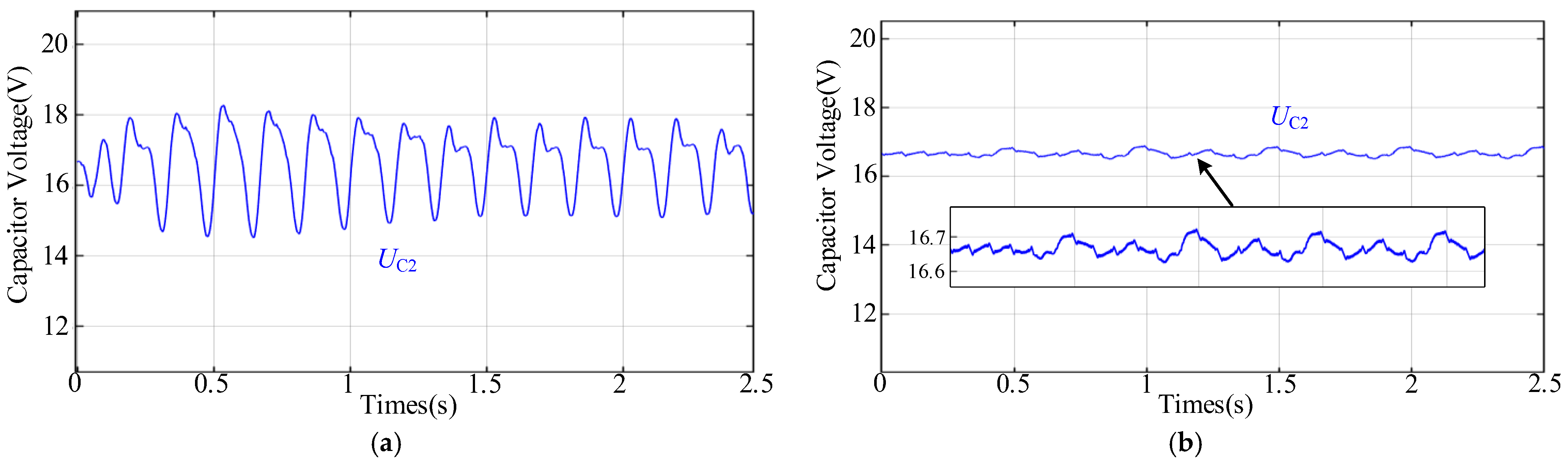

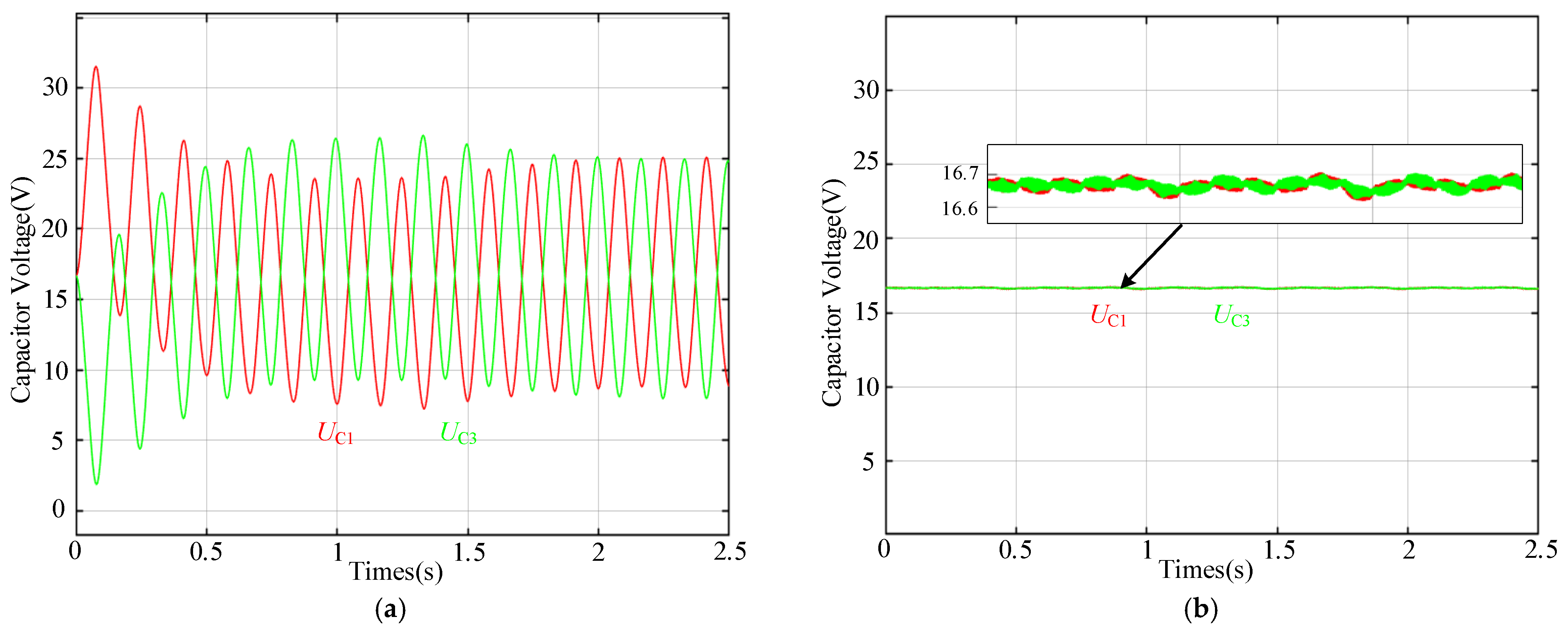

2. Proposed Voltage Balancing Control

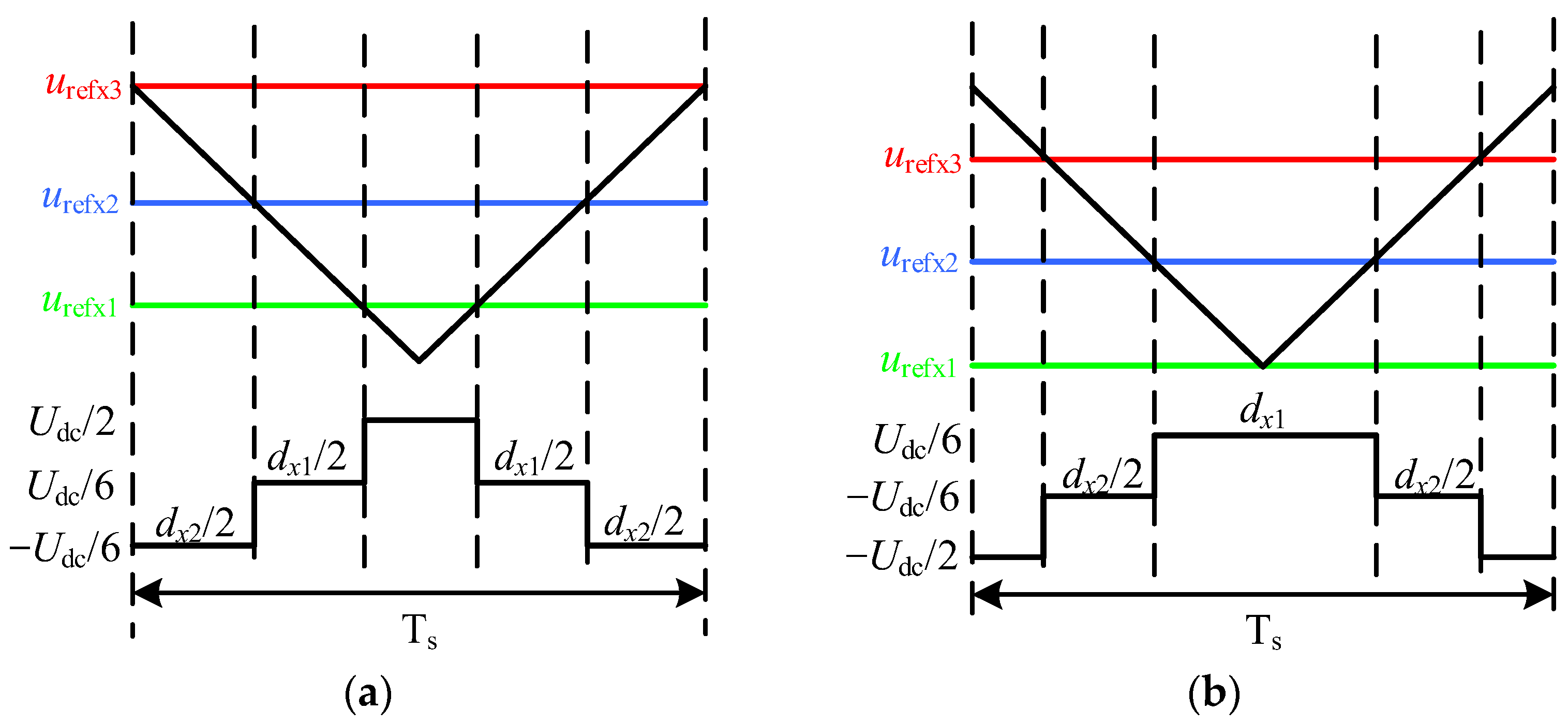

2.1. Variable Reference Voltage Method

2.2. Zero-Sequence Voltage Injection Method

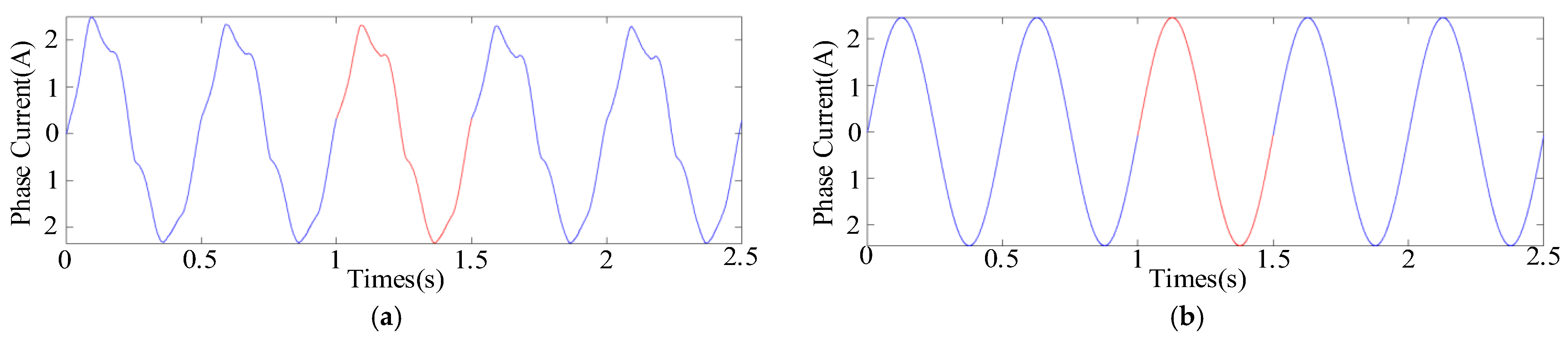

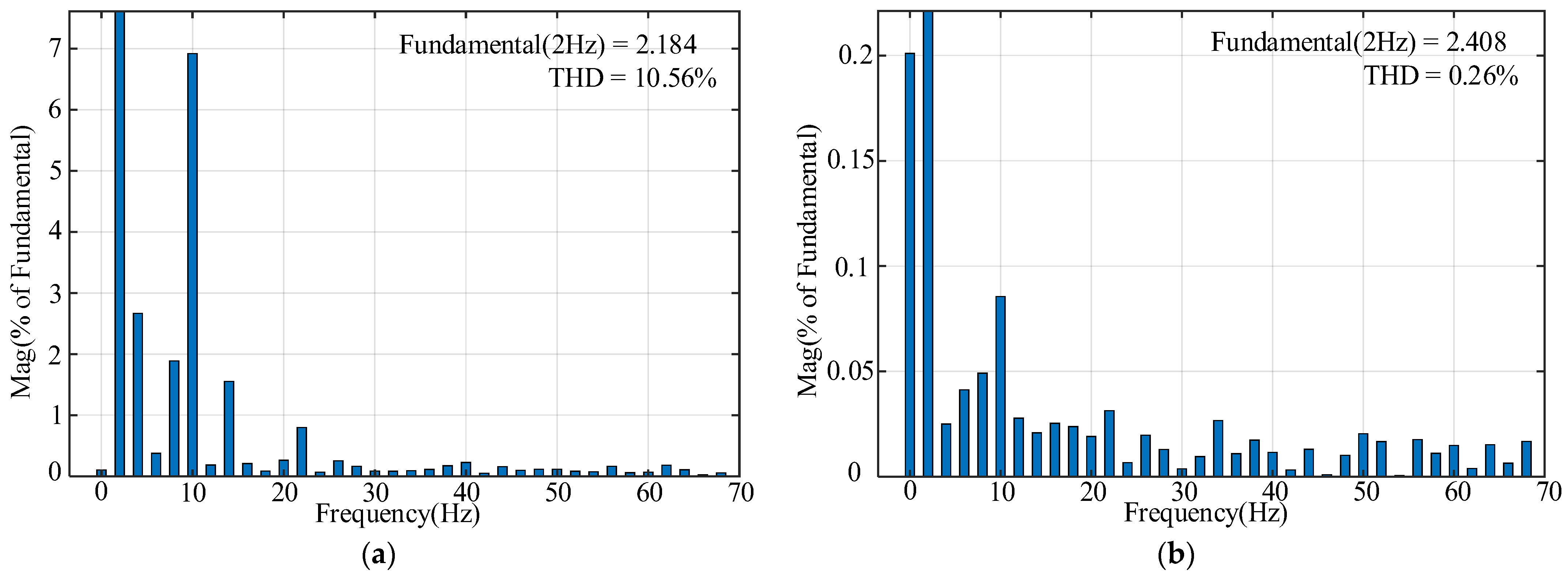

3. Analysis of Simulation Results

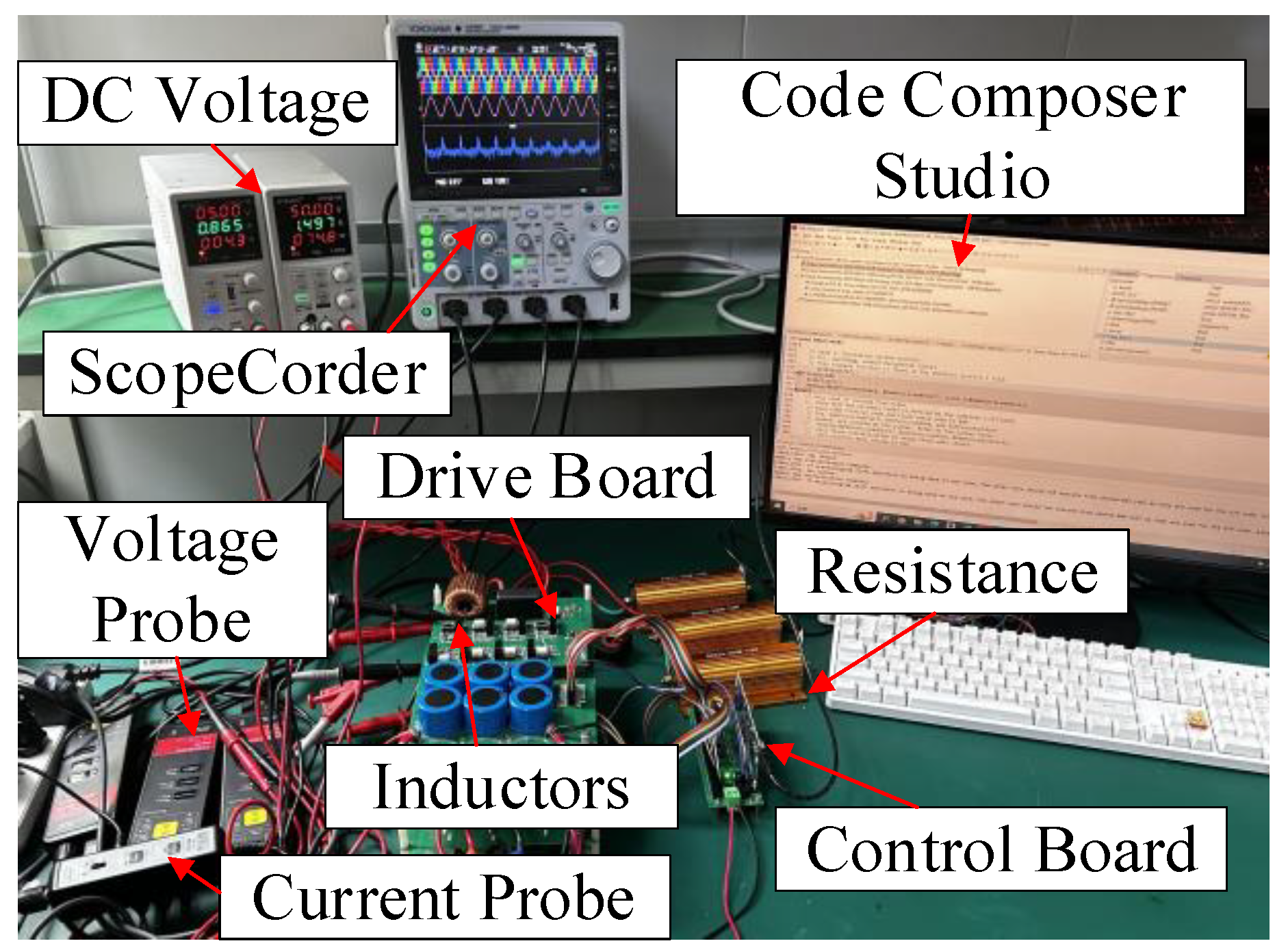

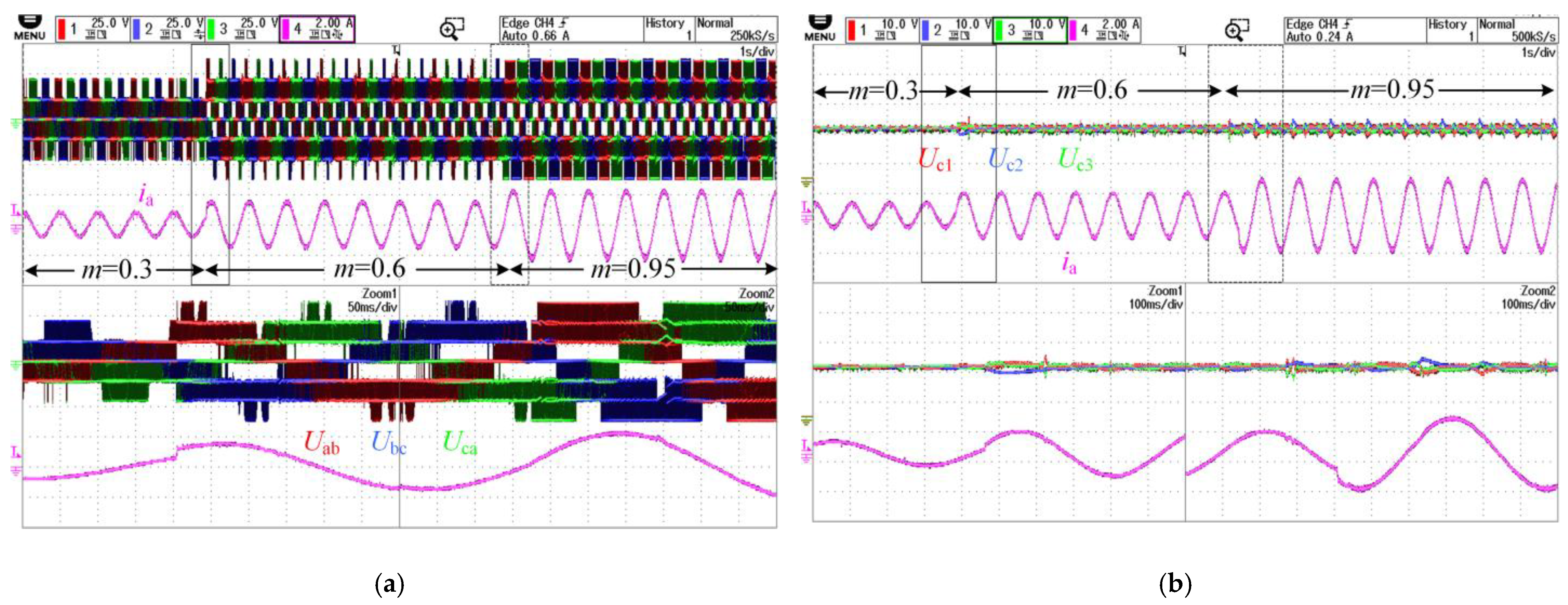

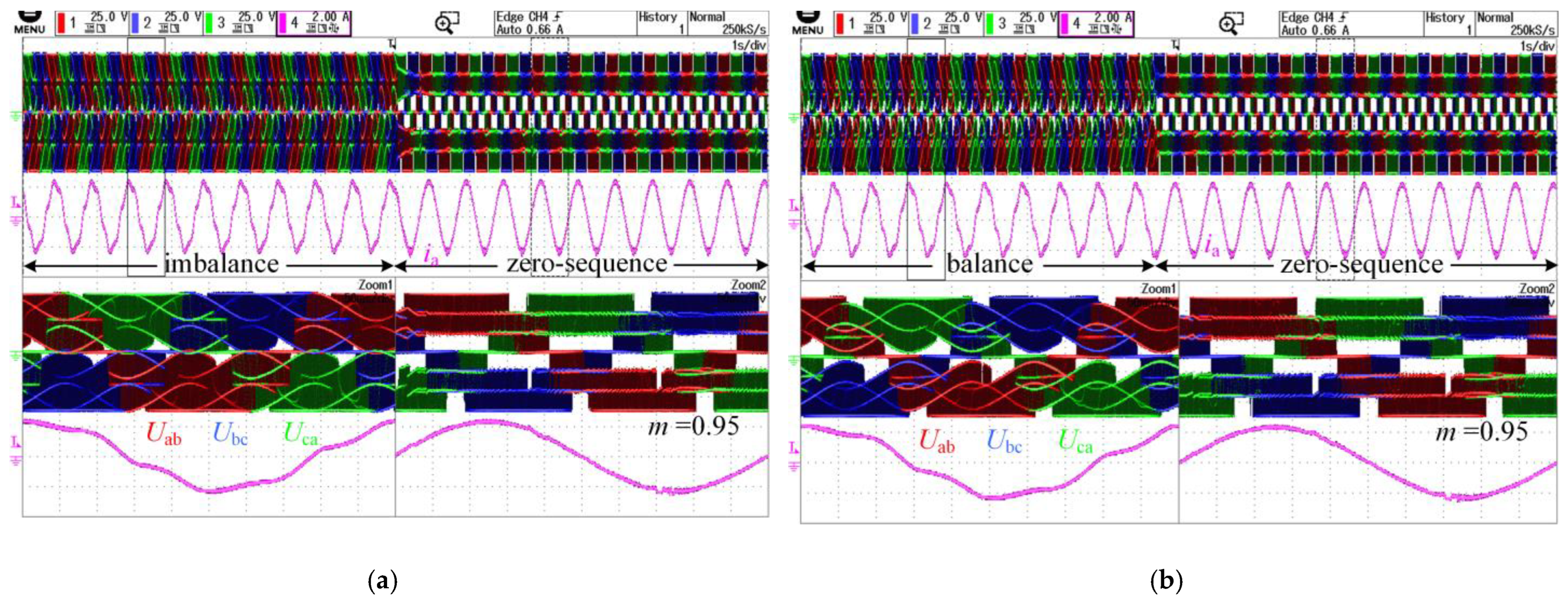

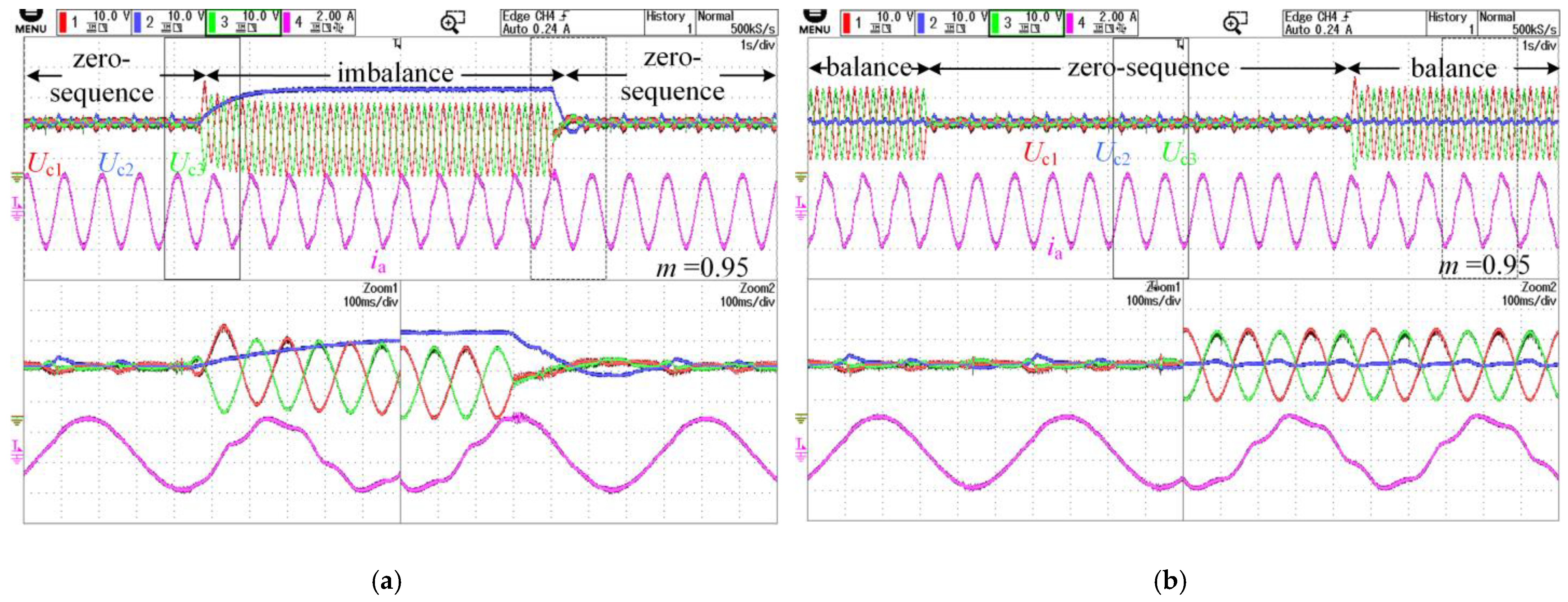

4. Verification of Experimental Results

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Wang, J.; Yang, B.; Zhao, J.; Deng, Y.; He, X.; Zhixin, X. Development of a compact 750KVA three-phase NPC three-level universal inverter module with specifically designed busbar. In Proceedings of the 2010 Twenty-Fifth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Palm Springs, CA, USA, 21–25 February 2010; pp. 1266–1271. [Google Scholar]

- Hosoda, H.; Peak, S. Multi-level converters for large capacity motor drive. In Proceedings of the 2010 International Power Electronics Conference-ECCE ASIA-, Sapporo, Japan, 21–24 June 2010; pp. 516–522. [Google Scholar]

- Zhang, D.; He, J.; Pan, D. A megawatt-scale medium-voltage high-efficiency high power density “SiC + Si” hybrid three-level ANPC inverter for aircraft hybrid-electric propulsion systems. IEEE Trans. Ind. Appl. 2019, 55, 5971–5980. [Google Scholar] [CrossRef]

- Jiao, Y.; Lee, F.C. New modulation scheme for three-level active neutral-point-clamped converter with loss and stress reduction. IEEE Trans. Ind. Electron. 2015, 62, 5468–5479. [Google Scholar] [CrossRef]

- Li, C.; Lu, R.; Li, C. Space vector modulation for SiC and Si hybrid ANPC converter in medium-voltage high-speed drive system. IEEE Trans. Power Electron. 2019, 35, 3390–3401. [Google Scholar] [CrossRef]

- Wang, B. Four-level neutral point clamped converter with reduced switch count. In Proceedings of the 2008 IEEE Power Electronics Specialists Conference, Rhodes, Greece, 15–19 June 2008; pp. 2626–2632. [Google Scholar]

- Pribadi, J.; Lee, D.-C. Open-Switch Fault Diagnosis in Four-Level Active Neutral-Point-Clamped Inverters. In Proceedings of the 2021 IEEE Energy Conversion Congress and Exposition (ECCE), Vancouver, BC, Canada, 10–14 October 2021; pp. 2576–2581. [Google Scholar]

- Wang, K.; Zheng, Z.; Li, Y. Topology and control of a four-level ANPC inverter. IEEE Trans. Power Electron. 2022, 35, 2342–2352. [Google Scholar] [CrossRef]

- Chen, H.; He, Y.; Liu, J. A novel hybrid SVPWM modulation algorithm for five level active neutral-point-clamped converter. In Proceedings of the 2019 IEEE Applied Power Electronics Conference and Exposition (APEC), Anaheim, CA, USA, 17–21 March 2019; pp. 2494–2498. [Google Scholar]

- Wang, K.; Zheng, Z.; Li, Y. Neutral-point potential balancing of a five-level active neutral-point-clamped inverter. IEEE Trans. Ind. Electron. 2012, 60, 1907–1918. [Google Scholar] [CrossRef]

- Oikonomou, N.; Gutscher, C.; Karamanakos, P. Model predictive pulse pattern control for the five-level active neutral-point-clamped inverter. IEEE Trans. Ind. Appl. 2013, 49, 2583–2592. [Google Scholar] [CrossRef]

- Hachlowski, J.; Stala, R. DC-link voltage balancing converter with resonant switched-capacitor circuit for four-level and six-level NPC inverter. In Proceedings of the 2019 21st European Conference on Power Electronics and Applications (EPE’19 ECCE Europe), Genova, Italy, 3–5 September 2019; pp. 1–10. [Google Scholar]

- Busquets-Monge, S.; Bordonau, J.; Rocabert, J. A virtual-vector pulse width modulation for the four-level diode-clamped DC–AC converter. IEEE Trans. Power Electron. 2008, 23, 1964–1972. [Google Scholar] [CrossRef]

- Pham, K.D.; Phan, Q.D.; Nguyen, N.V. Novel virtual vector SVPWM method to mitigate low-frequency common mode voltage for four-level NPC inverters. IEEE Access 2024, 12, 22403–22419. [Google Scholar] [CrossRef]

- Yang, Y.; Pan, J.; Wen, H. An optimized model predictive control for three-phase four-level hybrid-clamped converters. IEEE Trans. Power Electron. 2019, 35, 6470–6481. [Google Scholar] [CrossRef]

- Monfared, K.K.; Iman-Eini, H.; Neyshabouri, Y. Model predictive control with reduced common-mode voltage based on optimal switching sequences for nested neutral point clamped inverter. IEEE Trans. Ind. Electron. 2023, 71, 27–38. [Google Scholar] [CrossRef]

- Wang, K.; Xu, L.; Zheng, Z. Capacitor voltage balancing of a five-level ANPC converter using phase-shifted PWM. IEEE Trans. Power Electron. 2014, 30, 1147–1156. [Google Scholar] [CrossRef]

- Wang, K.; Zheng, Z.; Xu, L. An optimized carrier-based PWM method and voltage balancing control for five-level ANPC converters. IEEE Trans. Ind. Electron. 2019, 67, 9120–9132. [Google Scholar] [CrossRef]

- Chen, J.; Wang, C. Dual T-type four-level converter. IEEE Trans. Power Electron. 2019, 35, 5594–5600. [Google Scholar] [CrossRef]

- Chen, J.; Zhong, Y.; Wang, C. Four-level hybrid neutral point clamped converters. IEEE J. Emer. Sel. Top. Power. Electron. 2021, 9, 4786–4801. [Google Scholar] [CrossRef]

- Li, C.; Chen, J. Simplified SVPWM capacitor voltage balancing control method for four-level neutral point clamped inverters. In Proceedings of the 2023 IEEE 14th International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Shanghai, China, 9–12 June 2023; pp. 127–132. [Google Scholar]

- Wang, Y.; Chen, J. Voltage balancing control and implementation of detroit rectifier. IEEE Trans. Ind. Electron. 2024. [Google Scholar] [CrossRef]

- Wang, K.; Zheng, Z.; Li, Y. A novel carrier-overlapped PWM method for four-level neutral-point clamped converters. IEEE Trans. Power Electron. 2018, 34, 7–12. [Google Scholar] [CrossRef]

- Wang, K.; Zheng, Z.; Xu, L. A composite voltage-balancing method for four-level NPC inverters. IEEE J. Emer. Sel. Top. Power. Electron. 2020, 9, 3394–3406. [Google Scholar] [CrossRef]

- Wang, K.; Xu, L.; Zheng, Z. Multi-objective optimization control of a four-level hybrid-clamped inverter. In Proceedings of the 2015 IEEE Energy Conversion Congress and Exposition (ECCE), Montreal, QC, Canada, 20–24 September 2015; pp. 1611–1616. [Google Scholar]

- Qin, J.; Saeedifard, M. A zero-sequence voltage injection-based control strategy for a parallel hybrid modular multilevel HVDC converter system. IEEE Trans. Power Deliv. 2014, 30, 728–736. [Google Scholar] [CrossRef]

- Wang, K.; Xu, L.; Zheng, Z. Voltage balancing control of a four-level hybrid-clamped converter based on zero-sequence voltage injection using phase-shifted PWM. IEEE Trans. Power Electron. 2015, 31, 5389–5399. [Google Scholar] [CrossRef]

- Pou, J.; Zaragoza, J.; Rodríguez, P. Fast-processing modulation strategy for the neutral-point-clamped converter with total elimination of low-frequency voltage oscillations in the neutral point. IEEE Trans. Ind. Electron. 2007, 54, 2288–2294. [Google Scholar] [CrossRef]

- Chen, J. A new insight on four-level neutral point clamped converters: Four-level = two-level + three-level. IEEE Trans. Power Electron. 2024, 39, 5166–5177. [Google Scholar] [CrossRef]

| Parameter | Value |

|---|---|

| DC-link voltage Udc | 50 V |

| DC-link capacitors | 1.32 mF |

| Switching frequency fs | 10 kHz |

| LR Load | 5 mH, 10 Ω |

| Fundamental current | 2 Hz |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Su, S.; Xie, Q.; Wang, M.; Wang, Y.; Chen, J.; Hu, Z. Simple Voltage Balancing Control of Four-Level Inverter. Electronics 2024, 13, 3878. https://doi.org/10.3390/electronics13193878

Su S, Xie Q, Wang M, Wang Y, Chen J, Hu Z. Simple Voltage Balancing Control of Four-Level Inverter. Electronics. 2024; 13(19):3878. https://doi.org/10.3390/electronics13193878

Chicago/Turabian StyleSu, Shi, Qingyang Xie, Mengyuan Wang, Yu Wang, Jianfei Chen, and Zhikun Hu. 2024. "Simple Voltage Balancing Control of Four-Level Inverter" Electronics 13, no. 19: 3878. https://doi.org/10.3390/electronics13193878