A Capacitive-Feedback Amplifier with 0.1% THD and 1.18 μVrms Noise for ECG Recording

Abstract

1. Introduction

2. System Structure

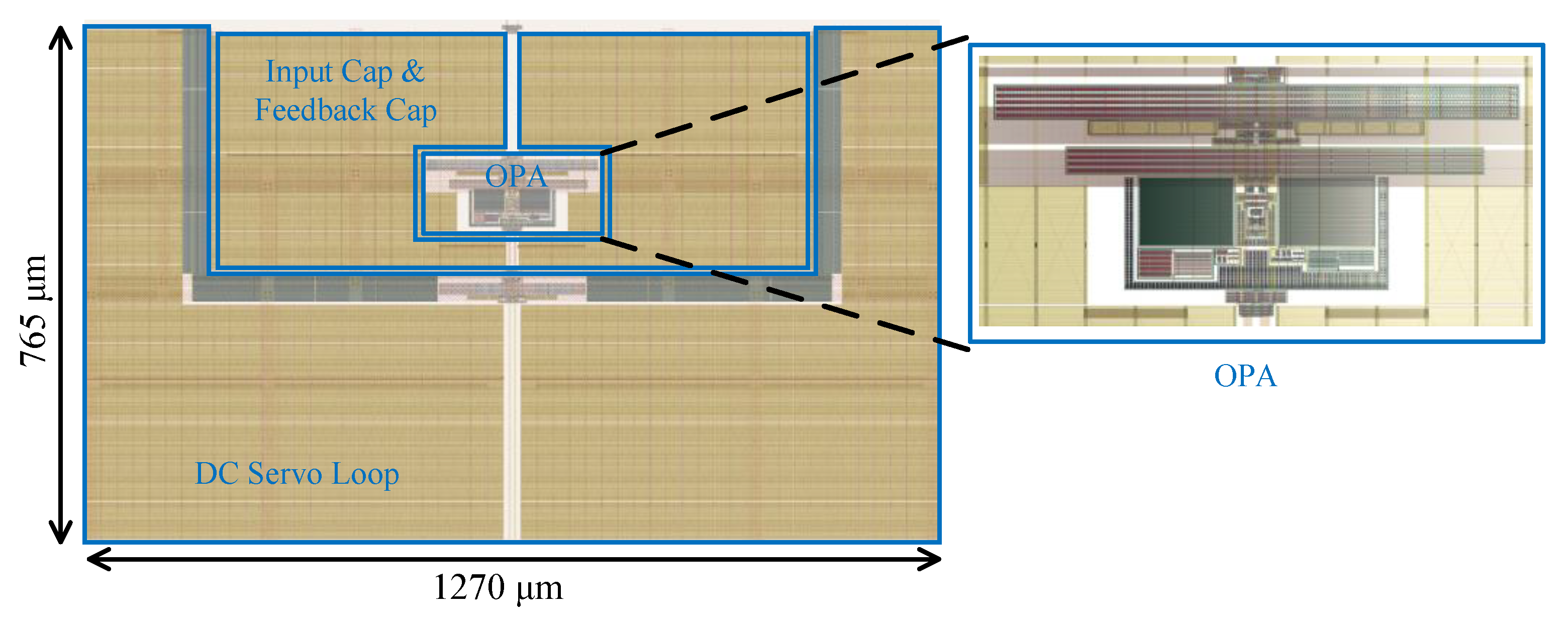

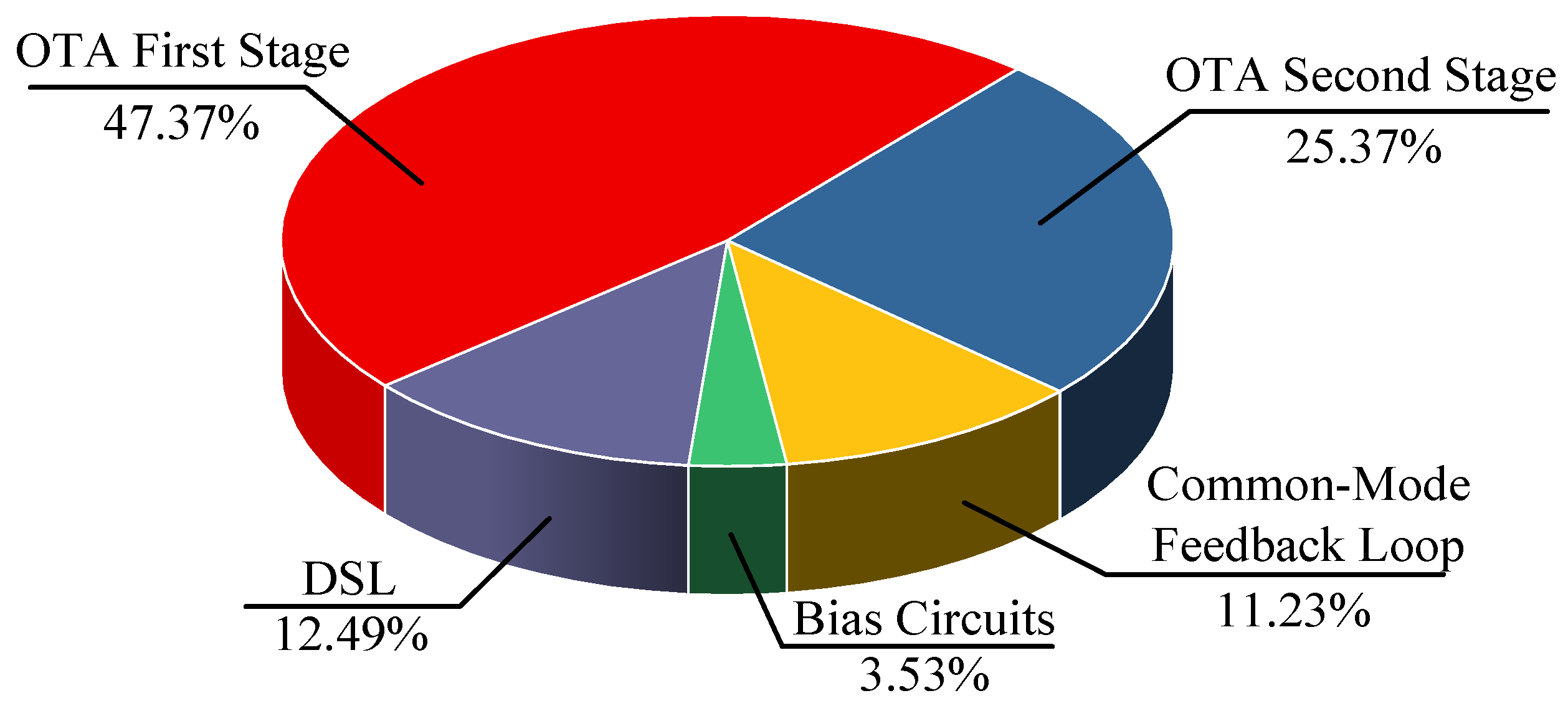

3. Circuit Design

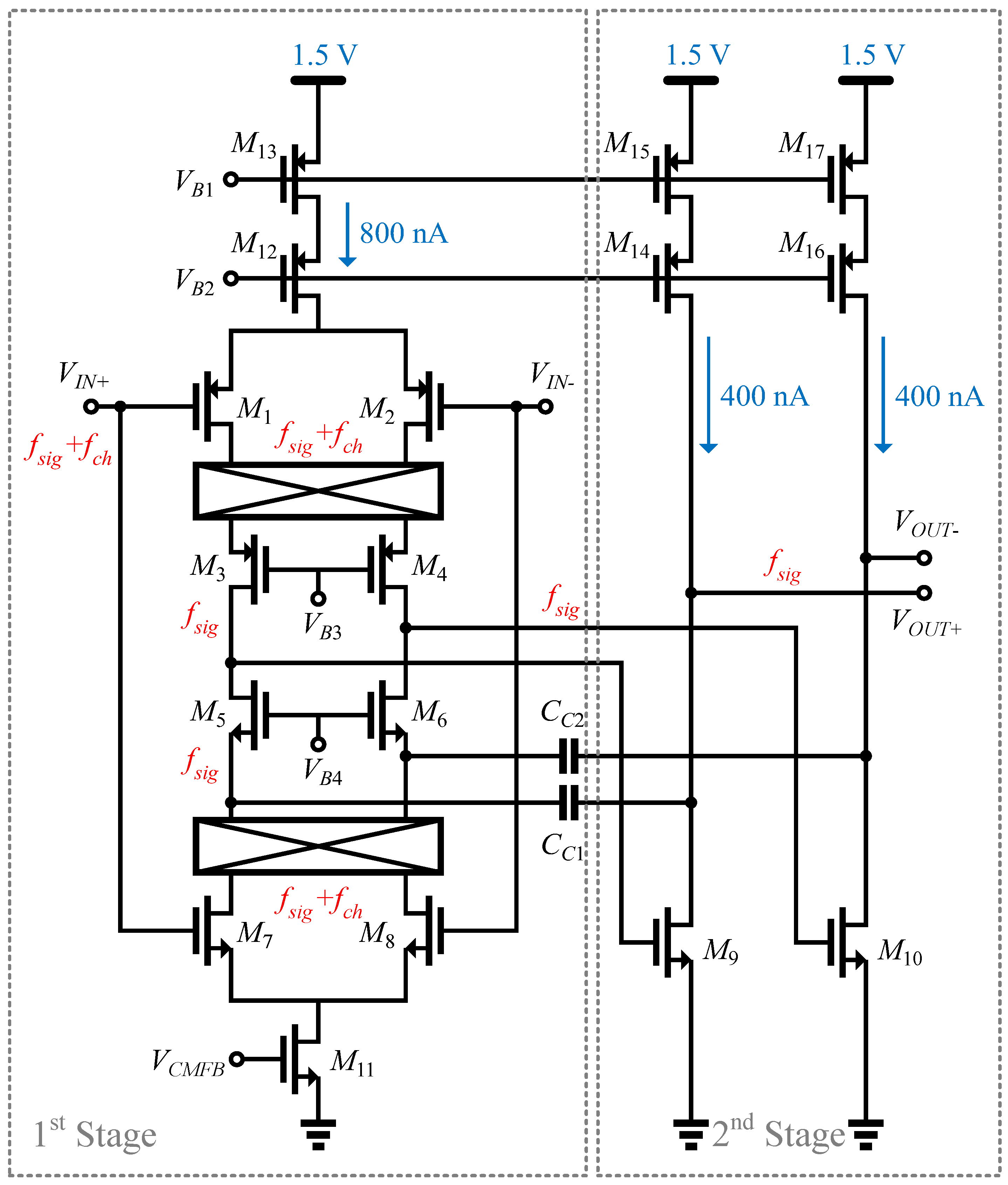

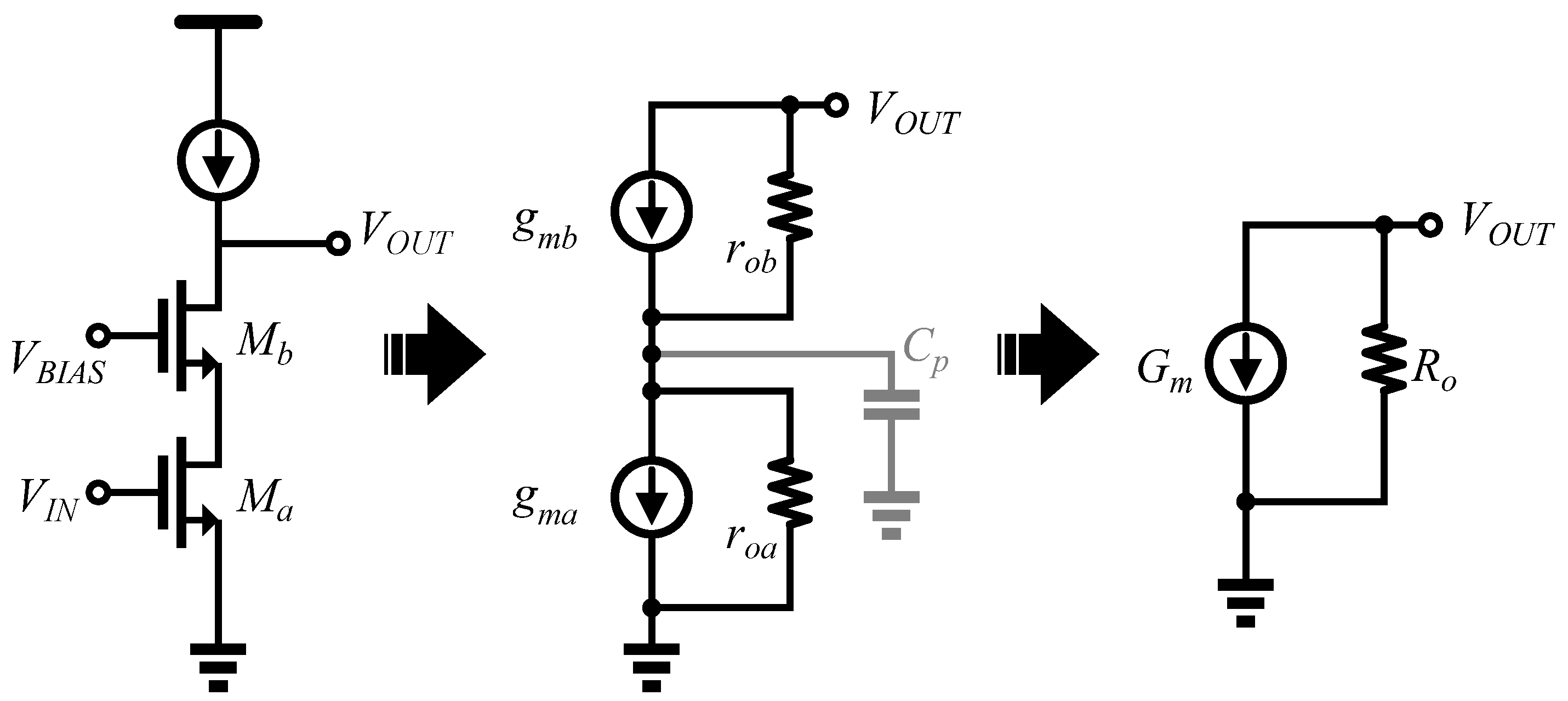

3.1. Architecture of OTA

3.2. Analysis of Output Swing

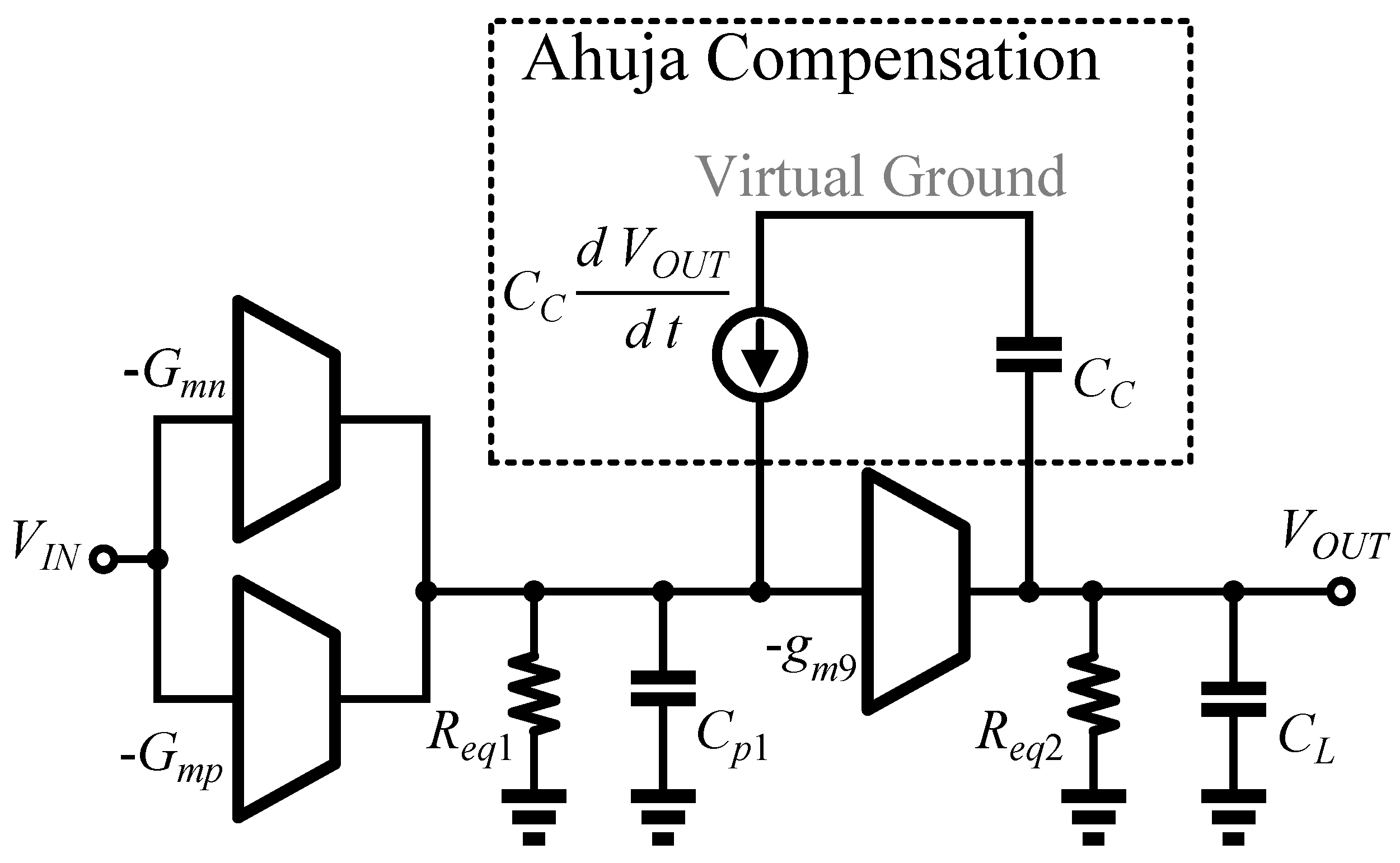

3.3. Analysis of Transfer Function

3.4. Analysis of Noise

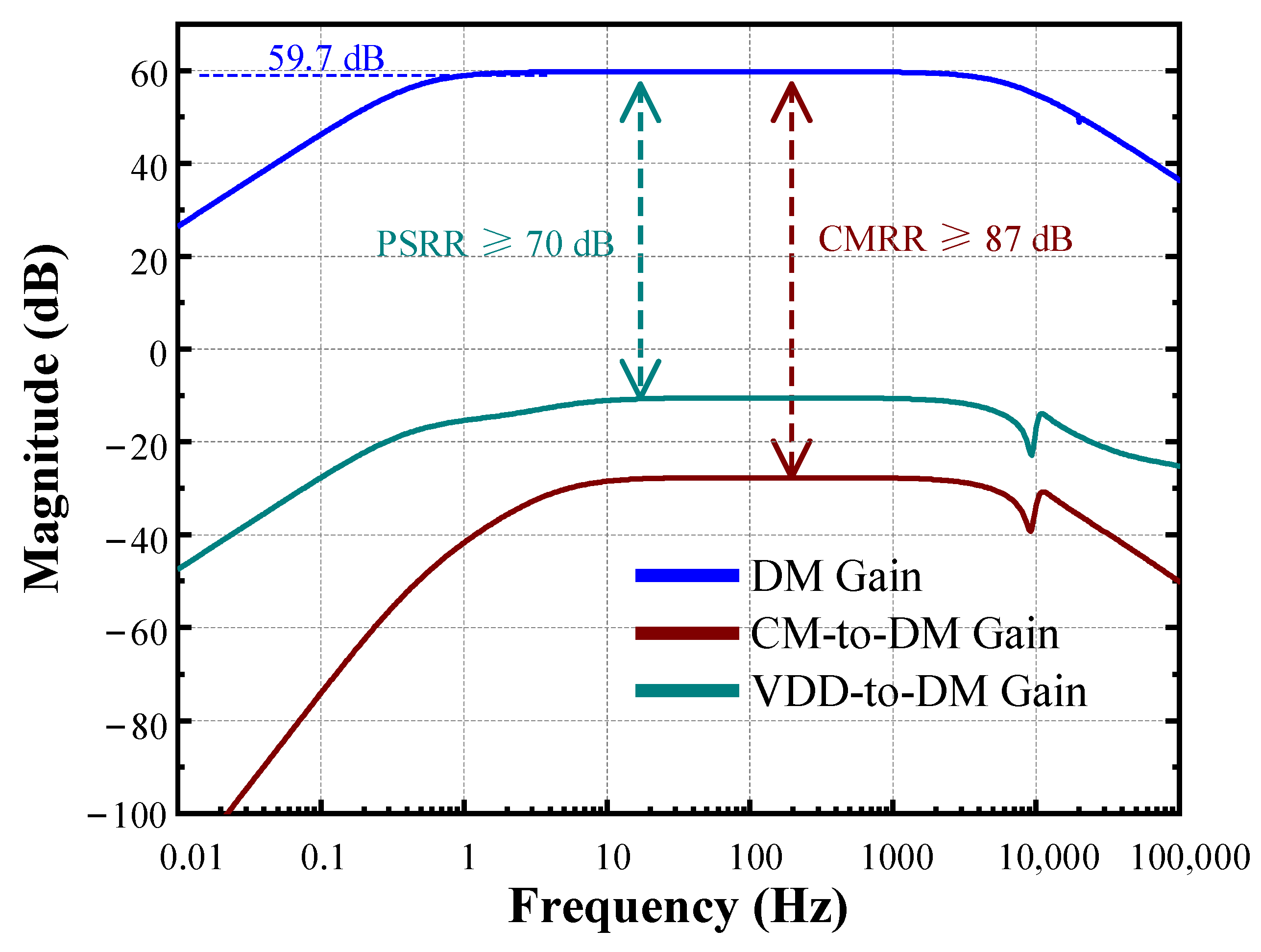

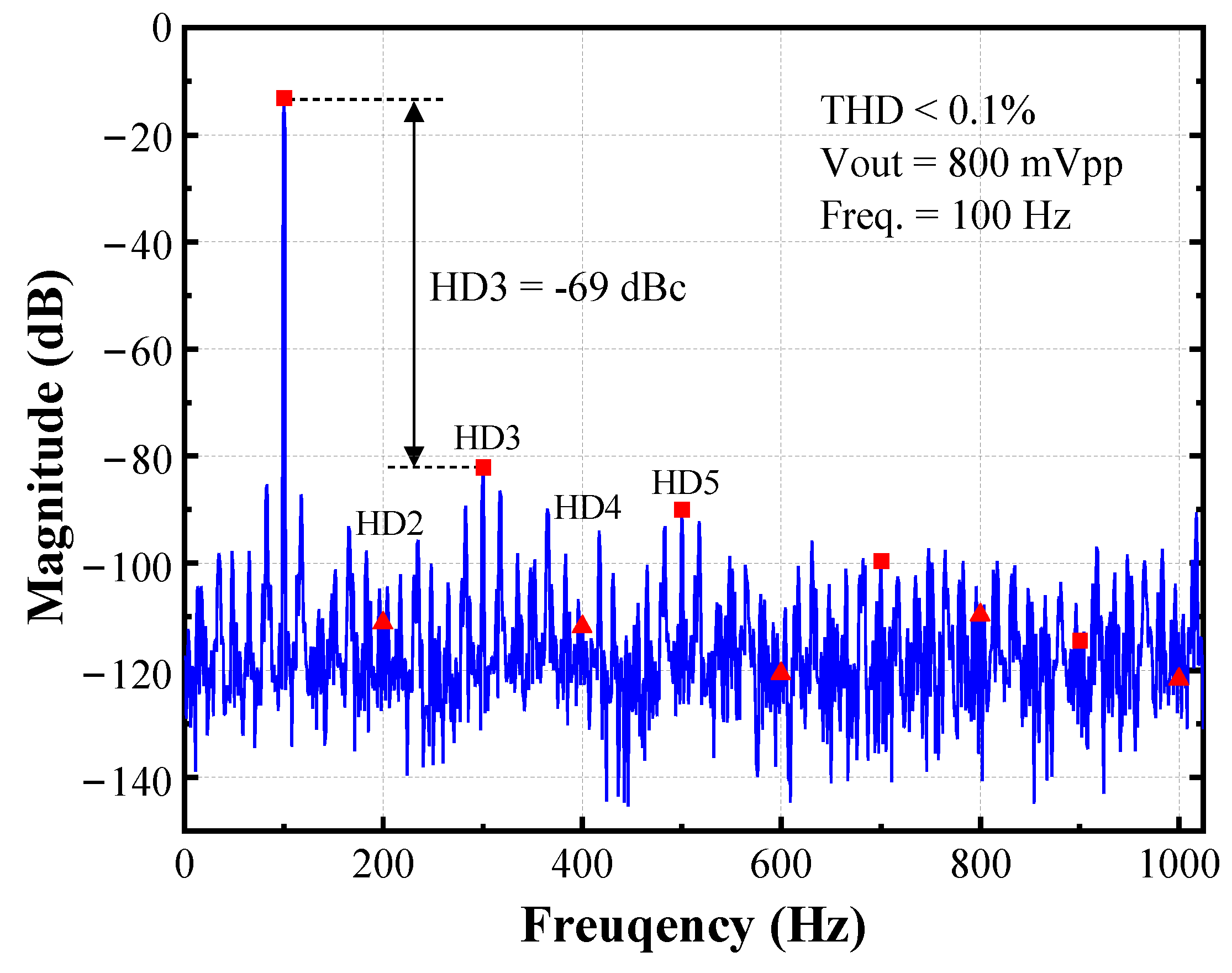

4. Results

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Lu, S.; Yang, J.; Yang, B.; Yin, Z.; Liu, M.; Yin, L.; Zheng, W. Analysis and Design of Surgical Instrument Localization Algorithm. CMES-Comput. Model. Eng. Sci. 2023, 137, 669–685. [Google Scholar] [CrossRef]

- Tang, T.; Goh, W.L.; Yao, L.; Cheong, J.H.; Gao, Y. An integrated multi-channel biopotential recording analog front-end IC with area-efficient driven-right-leg circuit. IEEE Trans. Biomed. Circuits Syst. 2019, 14, 297–304. [Google Scholar] [CrossRef]

- Wang, W.; Qi, F.; Wipf, D.; Cai, C.; Yu, T.; Li, Y.; Yu, Z.; Wu, W. Sparse bayesian learning for end-to-end EEG decoding. IEEE Trans. Pattern Anal. Mach. Intell. 2023, 45, 15632–15649. [Google Scholar] [CrossRef]

- Wang, C.; Zhang, X.; Liu, Y.; Li, J.; Zhu, L.; Lu, Y.; Guo, X.; Chen, D. An enzyme-particle hybrid ink for one step screen-printing and long-term metabolism monitoring. Anal. Chim. Acta 2022, 1221, 340168. [Google Scholar] [CrossRef]

- Bing, P.; Liu, Y.; Liu, W.; Zhou, J.; Zhu, L. Electrocardiogram classification using TSST-based spectrogram and ConViT. Front. Cardiovasc. Med. 2022, 9, 983543. [Google Scholar] [CrossRef] [PubMed]

- Tian, Y.; Qin, Z.; Yu, Y.; Gao, D.; Liao, X.; Liu, L. A Low-Noise and Low-Power Multi-Channel ECG AFE Based on Orthogonal Current-Reuse Amplifier. IEEE Trans. Circuits Syst. I Regul. Pap. 2023, 70, 3167–3177. [Google Scholar] [CrossRef]

- Dang, W.; Xiang, L.; Liu, S.; Yang, B.; Liu, M.; Yin, Z.; Yin, L.; Zheng, W. A Feature Matching Method based on the Convolutional Neural Network. J. Imaging Sci. Technol. 2023, 67. [Google Scholar] [CrossRef]

- Johnson, B.; Molnar, A. An orthogonal current-reuse amplifier for multi-channel sensing. IEEE J. Solid-State Circuits 2013, 48, 1487–1496. [Google Scholar] [CrossRef]

- Winter, B.B.; Webster, J.G. Driven-right-leg circuit design. IEEE Trans. Biomed. Eng. 1983, BME-30, 62–66. [Google Scholar] [CrossRef]

- Hu, H.; Lin, C.C.; Gupta, S. A 197.1-μW Wireless Sensor SoC with an Energy-Efficient Analog Front-End and a Harmonic Injection-Locked OOK TX. IEEE Trans. Circuits Syst. I Regul. Pap. 2021, 68, 2444–2456. [Google Scholar] [CrossRef]

- Zhang, J.; Zhang, H.; Sun, Q.; Zhang, R. A low-noise, low-power amplifier with current-reused OTA for ECG recordings. IEEE Trans. Biomed. Circuits Syst. 2018, 12, 700–708. [Google Scholar] [CrossRef] [PubMed]

- Mondal, S.; Hall, D.A. A 13.9-nA ECG amplifier achieving 0.86/0.99 NEF/PEF using AC-coupled OTA-stacking. IEEE J. Solid-State Circuits 2019, 55, 414–425. [Google Scholar] [CrossRef]

- Li, Q.; Wang, X.; Liu, Y. A 60 nV/√Hz <0.01%-THD ±200 mV-DC-Rejection Bio-Sensing Chopper Amplifier With Noise-Nonlinearity-Cancelling Loop. IEEE Trans. Circuits Syst. II Express Briefs 2019, 67, 215–219. [Google Scholar]

- Song, S.; Rooijakkers, M.; Harpe, P.; Rabotti, C.; Mischi, M.; van Roermund, A.H.; Cantatore, E. A low-voltage chopper-stabilized amplifier for fetal ECG monitoring with a 1.41 power efficiency factor. IEEE Trans. Biomed. Circuits Syst. 2015, 9, 237–247. [Google Scholar] [CrossRef] [PubMed]

- Wang, T.Y.; Lai, M.R.; Twigg, C.M.; Peng, S.Y. A fully reconfigurable low-noise biopotential sensing amplifier with 1.96 noise efficiency factor. IEEE Trans. Biomed. Circuits Syst. 2013, 8, 411–422. [Google Scholar] [CrossRef] [PubMed]

- Tang, T.; Goh, W.L.; Yao, L.; Gao, Y. A TDM-based 16-channel AFE ASIC with enhanced system-level CMRR for wearable EEG recording with dry electrodes. IEEE Trans. Biomed. Circuits Syst. 2020, 14, 516–524. [Google Scholar] [CrossRef]

- Huang, X.; Ballini, M.; Wang, S.; Miccoli, B.; Van Hoof, C.; Gielen, G.; Craninckx, J.; Van Helleputte, N.; Lopez, C.M. A compact, low-power analog front-end with event-driven input biasing for high-density neural recording in 22-nm FDSOI. IEEE Trans. Circuits Syst. II Express Briefs 2021, 69, 804–808. [Google Scholar] [CrossRef]

- Ha, U.; Lee, J.; Kim, M.; Roh, T.; Choi, S.; Yoo, H.J. An EEG-NIRS multimodal SoC for accurate anesthesia depth monitoring. IEEE J. Solid-State Circuits 2018, 53, 1830–1843. [Google Scholar] [CrossRef]

- Zhang, T.; Li, Y.; Su, C.; Zhang, X.; Yang, Y. A 1V 3.5 μW Bio-AFE with Chopper-Capacitor-Chopper Integrator-Based DSL and Low Power GM-C Filter. IEEE Trans. Circuits Syst. II Express Briefs 2021, 69, 5–9. [Google Scholar]

- Samiei, A.; Hashemi, H. A chopper stabilized, current feedback, neural recording amplifier. IEEE Solid-State Circuits Letters 2019, 2, 17–20. [Google Scholar] [CrossRef]

- Lee, C.J.; Song, J.I. A chopper-stabilized amplifier with a tunable bandwidth for EEG acquisition applications. IEEE Access 2019, 7, 73165–73171. [Google Scholar] [CrossRef]

- Martins, R.; Selberherr, S.; Vaz, F.A. A CMOS IC for portable EEG acquisition systems. IEEE Trans. Instrum. Meas. 1998, 47, 1191–1196. [Google Scholar] [CrossRef]

- Hoseini, Z.; Nazari, M.; Lee, K.S.; Chung, H. Current feedback instrumentation amplifier with built-in differential electrode offset cancellation loop for ECG/EEG sensing frontend. IEEE Trans. Instrum. Meas. 2020, 70, 1–11. [Google Scholar] [CrossRef]

- Miaofen, L.; Youmin, L.; Tianyang, W.; Fulei, C.; Zhike, P. Adaptive synchronous demodulation transform with application to analyzing multicomponent signals for machinery fault diagnostics. Mech. Syst. Signal Process. 2023, 191, 110208. [Google Scholar] [CrossRef]

- Ng, K.A.; Xu, Y.P. A low-power, high CMRR neural amplifier system employing CMOS inverter-based OTAs with CMFB through supply rails. IEEE J. Solid-State Circuits 2016, 51, 724–737. [Google Scholar]

- Wang, Y.; Chen, P.; Yong, J.; Xu, W.; Xu, S.; Liu, K. A comprehensive investigation on the selection of high-pass harmonic filters. IEEE Trans. Power Deliv. 2022, 37, 4212–4226. [Google Scholar] [CrossRef]

- Enz, C.C.; Vittoz, E.A.; Krummenacher, F. A CMOS chopper amplifier. IEEE J. Solid-State Circuits 1987, 22, 335–342. [Google Scholar] [CrossRef]

- Hu, J.; Wu, Y.; Li, T.; Ghosh, B.K. Consensus control of general linear multiagent systems with antagonistic interactions and communication noises. IEEE Trans. Autom. Control 2018, 64, 2122–2127. [Google Scholar] [CrossRef]

- Li, M.; Wang, T.; Chu, F.; Han, Q.; Qin, Z.; Zuo, M.J. Scaling-basis chirplet transform. IEEE Trans. Ind. Electron. 2020, 68, 8777–8788. [Google Scholar] [CrossRef]

- Enz, C.C.; Krummenacher, F.; Vittoz, E.A. An analytical MOS transistor model valid in all regions of operation and dedicated to low-voltage and low-current applications. Analog. Integr. Circuits Signal Process. 1995, 8, 83–114. [Google Scholar] [CrossRef]

- Chen, F.; Chandrakasan, A.P.; Stojanovic, V.M. Design and analysis of a hardware-efficient compressed sensing architecture for data compression in wireless sensors. IEEE J. Solid-State Circuits 2012, 47, 744–756. [Google Scholar] [CrossRef]

- Sawigun, C.; Thanapitak, S. A Compact Sub-μW CMOS ECG Amplifier With 57.5-MΩ Zin, 2.02 NEF, 8.16 PEF and 83.24-dB CMRR. IEEE Trans. Biomed. Circuits Syst. 2021, 15, 549–558. [Google Scholar] [CrossRef] [PubMed]

- Zhou, Z. A front-end amplifier with current compensation feedback input impedance booster for neural signal applications. IEEE Access 2020, 8, 178055–178062. [Google Scholar] [CrossRef]

- Pham, X.T.; Nguyen, N.T.; Nguyen, V.N.; Lee, J.W. Area and power-efficient capacitively-coupled chopper instrumentation amplifiers in 28 nm CMOS for multi-channel biosensing applications. IEEE Access 2021, 9, 86773–86785. [Google Scholar] [CrossRef]

| [11] TBCAS’18 | [13] TCS II’19 | [20] SSCL’19 a | [32] TBCAS’21 | [33] ACCESS’20 | [34] ACCESS’21 | This Work b | |

|---|---|---|---|---|---|---|---|

| Technology | 0.35 μm | 0.18 μm | 0.18 μm | 0.35 μm | 0.18 μm | 28 nm | 0.13 μm |

| Area (mm2) | 0.18 | 0.46 | 0.08 | 0.071 | 0.025 | 0.05 | 0.97 |

| Voltage (V) | 2 | 1.2 | 0.6, 1.2 | 2 | 1.8 | 1 | 1.5 |

| Current (A) | 160 n | 2 μ | N.A. | 0.336 μ | N.A. | 1 μ | 1.647 μ |

| Power (W) | 320 n | 2.4 μ | 2.6 μ | 0.672 μ | 7.6 μ | 1 μ | 2.471 μ |

| Gain (dB) | 39.8 | 40 | 41–59 | 40.6 | 14 | 39.5 | 59.7 |

| Bandwidth (Hz) | 0.2–200 | 0.5–500 | 200 | 7.84m-300 | 0.01–23 k | 1 k | 0.5-6.1 k |

| Input-Referred Noise (μVrms) | 2.05 (0.1–10 kHz) | 1.8 (0.5–500 Hz) | 3.2 | 1.54 (0.1–300 Hz) | N.A. | 2.74 (1–200 Hz) | 1.18 (0.5–500 Hz) |

| THD | <1% 20 Hz 15 mVpp Input | 0.01% 69 Hz 800 mVp Output | 1.7% 1 kHz 1 mVpp Input | 0.12% 100 Hz 5 mVp Input | −49 db 1 kHz 1 mVpp Input | −52.6 dB 100 Hz 1.5 mVp Input | <0.1% 100 Hz 800 mVpp Output |

| CMRR (dB) | >65 | >90 | 70 | 83.24 | 61 | 94 | ≥87 |

| PSRR (dB) | >70 | N.A. | N.A. | 84.2 | 57 | 79 | ≥70 |

| NEF | 2.26 | 4.4 | 3.2 | 2.02 | 4.7 c | 7.5 | 2.13 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chen, X.; Mo, T.; Wu, P.; Wu, B. A Capacitive-Feedback Amplifier with 0.1% THD and 1.18 μVrms Noise for ECG Recording. Electronics 2024, 13, 378. https://doi.org/10.3390/electronics13020378

Chen X, Mo T, Wu P, Wu B. A Capacitive-Feedback Amplifier with 0.1% THD and 1.18 μVrms Noise for ECG Recording. Electronics. 2024; 13(2):378. https://doi.org/10.3390/electronics13020378

Chicago/Turabian StyleChen, Xi, Taishan Mo, Peng Wu, and Bin Wu. 2024. "A Capacitive-Feedback Amplifier with 0.1% THD and 1.18 μVrms Noise for ECG Recording" Electronics 13, no. 2: 378. https://doi.org/10.3390/electronics13020378

APA StyleChen, X., Mo, T., Wu, P., & Wu, B. (2024). A Capacitive-Feedback Amplifier with 0.1% THD and 1.18 μVrms Noise for ECG Recording. Electronics, 13(2), 378. https://doi.org/10.3390/electronics13020378