Research on Parallel Reading and Drawing Techniques for Chemical Mechanical Polishing Simulation Data Based on Multi-Thread

Abstract

:1. Introduction

- The absolute value of dishing is greater than a certain value. The default value is 130 Å.

- The absolute value of the difference between the thickness of Cu and the average thickness of Cu is greater than a certain value, and the default value is 100 Å.

- The difference between the surface height and the average height is within a certain range. The default value is 130, which means that it is within ±130 Å.

2. Reading and Drawing Task Analysis

2.1. Reading Task Analysis

2.2. Reading Task Analysis

3. Optimization Scheme

3.1. Reading Optimization

3.1.1. Memory Mapping

- QFile::QFile(const Qstring &filename), used to create a file object.

- Bool QFile::open(OpenMode mode), used to open the file.

- Uchar *QfileDevice::map(qint64 offset,qint64 size, MemoryMapFlags flags = NoOptions), used to map the file. It is important to highlight that the “offset” parameter indicates the offset value of the data segment to be mapped in memory relative to the starting position of the file. The “size” parameter indicates the size of the data block to be mapped. File segmentation mapping can be achieved by setting different values for both the “offset” and “size” parameters.

- Bool QfileDevice::unmap (uchar *address), used to unmap the file.

- Void QfileDevice::close( ), used to close the file.

3.1.2. Multi-Threaded Reading

- Utilize Mmap to pre-read the CMP simulation result file, counting the number of newline characters (“\n”) and recording the position of each newline character (“\n”) in the file.

- Find the number of key characters “begin” or “end” to get the number of layout layers, so as to get the total number of grids in the file. Extract the total number of grid rows by reading the first column of grid data, and then calculate the total number of grid columns.

- According to the configured number of threads and the total number of grid columns, the grid data is allocated to each thread with the column as the smallest unit. Then, each thread calculates the starting position of the segment file based on the counted number of grids and the recorded newline characters positions. The end position of the previous file segment is the starting position of the next file segment.

3.1.3. String Conversion Performance Optimization

- Build a lookup table. Based on the data characteristics of the CMP simulation result file, we established a lookup table consisting of 10 rows and 7 columns denoted as , where r represents the row and c represents the column. The lookup table is shown in Table 1.

- Scan the floating-point number string. By scanning the floating-point number string, denoted as S, we can identify the positive/negative sign, integer part, and decimal part. In this representation, S = ‘sdndn-1…d1.x1x2…xm’, where the positive/negative sign ‘s’ can be empty or a minus sign, ‘d1d2…dn’ represents the integer part, ‘x1x2…xm’ represents the decimal part, and the decimal point separates the integer and decimal parts.

- According to the positive/negative sign, integer part and decimal part of the floating-point string, combined with the lookup table, add it for the calculation to obtain the calculated value of the floating-point values. When the positive/negative sign ‘s’ is empty or positive, let ; when the positive/negative sign ‘s’ is a negative sign, let . Combined with reading the value of each element M in the comparison table, the integer part and decimal part of the floating-point string are added by the lookup table.

3.2. Drawing Optimization

3.2.1. Uniform Hierarchical Downsampling Method

- Determine the initial downsampling level. Start by calculating the number of pixels N in the graphic display area based on the screen resolution. This will serve as the dividing criterion to create different intervals: [0, N], [N, 4N], [4N, 9N], …, [(n − 1)2N, n2N]. Each interval corresponds to a downsampling level, which we label as L1, L2, L3, …, Ln. For each grid data segment at level Ln, begin from the bottom left corner of the topographic data and replace the n × n grid data with its central grid data. Repeat this process until all grids have been reduced.

- Adjust the downsampling level according to the zoom level. Firstly, determine the maximum and minimum values of the zoom level. Then, divide the range of the scaling level into n consecutive intervals, with each interval corresponding to a specific scaling level (S1, S2, S3, …, Sn). For the initial downsampling level Ln, no changes are made when the zoom level is S1. However, as the user zooms in, the downsampling level will decrease by one level for each increment in the zoom level, as depicted in Figure 8.

- Obtain the segmented data by downsampling. Start by determining the number of grids after downsampling at each level, from initial level Ln to L1. Pre-allocate memory of the appropriate size for each level and obtain the segmented grid data using the corresponding relationships from Ln to L1.

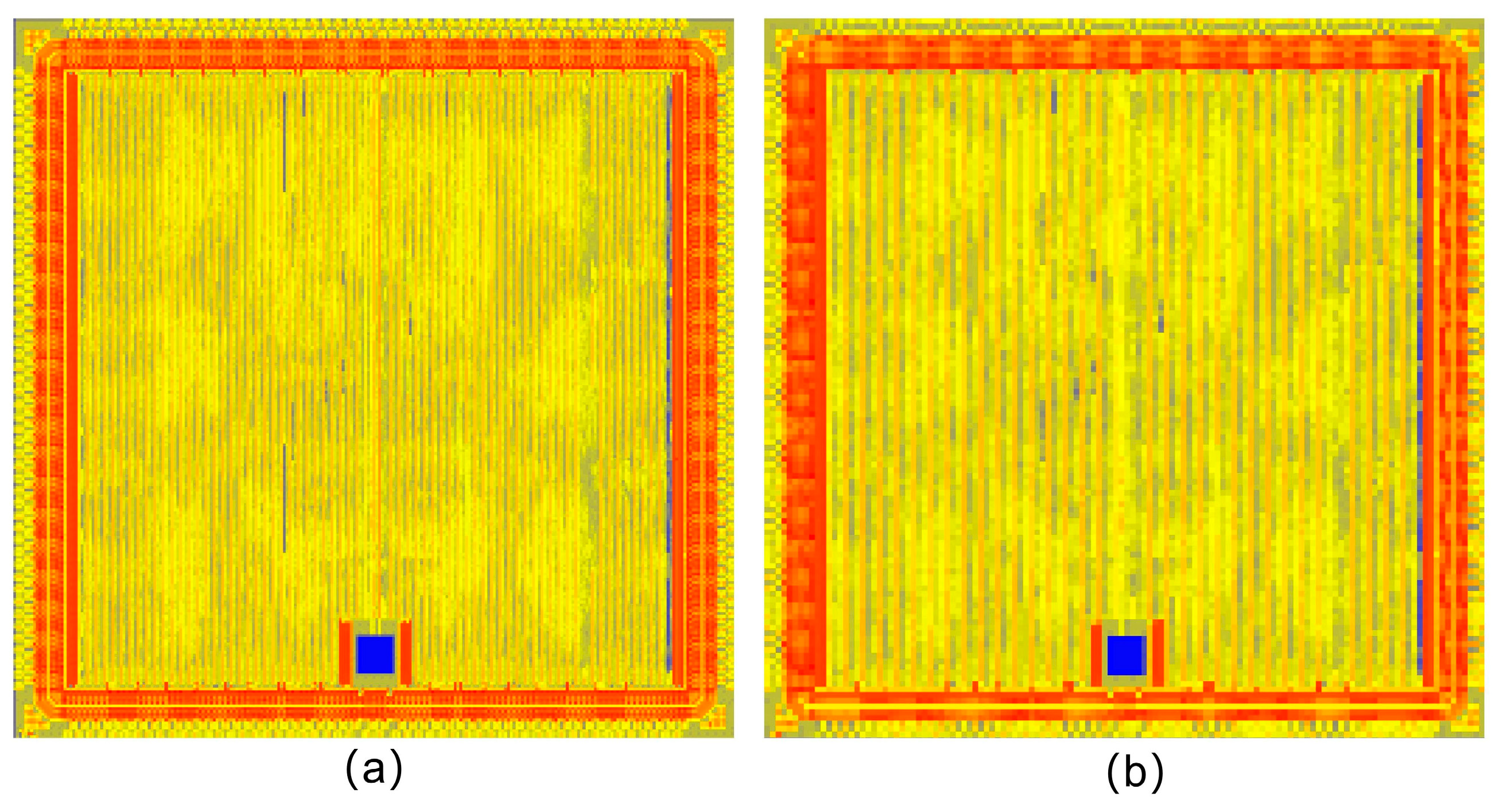

3.2.2. Multi-Threaded Drawing

- Parallelization of Drawing Threads. Each block of a complete morphology graph corresponds to a drawing thread. Each drawing thread primarily performs parallel operations, including data processing, g coordinate mapping, and drawing. When all threads finish drawing their block, the graphical composition thread combines them to form a complete image, marking the completion of a one-time drawing. This process is repeated until all graphical appearances are rendered.

- Output of the graphics. When the drawing working thread completes the drawing process on the QImage drawing memory, it transfers the QImage memory block to the GUI thread. Then, it converts the QImage object into a QPixmap object. Finally, it utilizes the API function of the QT drawing engine to output the graphics. The process of graphics output occurs in two stages. Firstly, to enhance the efficiency of the initial display, the graphics of the surface height of the first layer of layout under the maximum downsampling level are first drawn during the memory drawing process. After the drawing is complete, the graphics are then transmitted to the GUI thread for output display. Secondly, when all the layout morphology graphics of different layers and morphology information under all downsampling levels are drawn, they are bundled together and delivered to the GUI thread. This approach enables quicker switching between different display contents or zooming by retrieving the corresponding QImage image and converting it to QPixmap format for display output. Notably, the conversion time is shorter than the time required for graphics drawing, resulting in a significant improvement in the smoothness of human–computer interaction. It should be noted that there is a time difference in the output of these two graphics. When the user switches to display graphics before the second graphics output, it can cause display failure or display errors. Therefore, we used the signal and slot mechanism to take the GUI thread receiving the drawn graphics set as the signal and clicking the switch display button as the slot to avoid this display error.

3.3. Overall Design

4. Discussion

4.1. Simulation Environment

4.2. The Optimal Number of Threads

4.3. Comparison of Reading Efficiency

4.4. Comparison of Drawing Efficiency

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Tsujimura, M. The way to zeros: The future of semiconductor device and chemical mechanical polishing technologies. Jpn. J. Appl. Phys. 2016, 55, 6S3. [Google Scholar] [CrossRef]

- Ghulghazaryan, R.; Wilson, J.; Abouzeid, A. FEOL CMP modeling: Progress and challenges. In Proceedings of the 2015 International Conference on Planarization/CMP Technology, Chandler, AZ, USA, 30 September–2 October 2015; pp. 1–4. [Google Scholar]

- Zhang, J.H.; Huang, H.; Greene, A.M.; Xie, R.; Seo, S.C.; Montanini, P.; Tseng, T.W.; Tsai, S.; Malley, M.; Fang, Q.; et al. CMP challenges for advanced technology nodes. MRS Adv. 2017, 2, 2361–2372. [Google Scholar] [CrossRef]

- Xie, X. Physical Understanding and Modeling of Chemical Mechanical Planarization in Dielectric Materials. Ph.D. Thesis, Massachusetts Institute of Technology, Cambridge, MA, USA, 2007. [Google Scholar]

- Ma, T.; Chen, L.; Fang, J. Study of Optimal Dummy Fill Modes in Chemical–Mechanical Polishing Process. IEEE Trans. Compon. Packag. Manuf. Technol. 2012, 2, 1043–1047. [Google Scholar] [CrossRef]

- Tugbawa, T.E.; Park, T.H.; Boning, D.S. Integrated chip-scale simulation of pattern dependencies in copper electroplating and copper chemical mechanical polishing processes. In Proceedings of the IEEE 2002 International Interconnect Technology Conference (Cat. No.02EX519), Burlingame, CA, USA, 3–5 June 2002. [Google Scholar]

- Ruan, W.; Chen, L.; Ma, T.; Fang, J.; Zhang, H.; Ye, T. Optimization of a Cu CMP process modeling parameters of nanometer integrated circuits. J. Semicond. 2012, 33, 086001. [Google Scholar] [CrossRef]

- Bao, H.; Chen, L.; Ren, B. A Study on the Pattern Effects of Chemical Mechanical Planarization with CNN-Based Models. Electronics 2020, 9, 1158. [Google Scholar] [CrossRef]

- Chen, X.; Wang, Y.; Yang, H. Parallel Circuit Simulation on Multi/Many-core Systems. In Proceedings of the 2012 IEEE 26th International Parallel and Distributed Processing Symposium Workshops & PhD Forum, Shanghai, China, 21–25 May 2012; pp. 2530–2533. [Google Scholar]

- Ye, X.; Dong, W.; Li, P.; Nassif, S. Maps: Multi-algorithm parallel circuit simulation. In Proceedings of the 2008 IEEE/ACM International Conference on Computer-Aided Design, San Jose, CA, USA, 10–13 November 2008; pp. 73–78. [Google Scholar]

- Berger, E.D.; Yang, T.; Liu, T.; Novark, G. Grace: Safe multithreaded programming for C/C++. In Proceedings of the 24th ACM SIGPLAN Conference on Object Oriented Programming Systems Languages and Applications, New York, NY, USA, 25–29 October 2009; pp. 81–96. [Google Scholar]

- Sharif, K.H.; Zeebaree, S.R.M.; Haji, L.M.; Zebari, R.R. Performance measurement of processes and threads controlling, tracking and monitoring based on shared-memory parallel processing approach. In Proceedings of the 2020 3rd International Conference on Engineering Technology and its Applications (IICETA), Najaf, Iraq, 6–7 September 2020; pp. 62–67. [Google Scholar]

- Gepner, P.; Kowalik, M.F. Multi-core processors: New way to achieve high system performance. In Proceedings of the International Symposium on Parallel Computing in Electrical Engineering (PARELEC’06), Bialystok, Poland, 13–17 September 2006; pp. 9–13. [Google Scholar]

- Bucker, H.M.; Lang, B.; Rasch, A.; Bischof, C.H.; Mey, D. Explicit loop scheduling in OpenMP for parallel automatic differentiation. In Proceedings of the 16th Annual International Symposium on High Performance Computing Systems and Applications, Moncton, NB, Canada, 16–19 June 2002; pp. 121–126. [Google Scholar]

- Li, J.; Shu, J.; Chen, Y.; Wang, D. Analysis of factors affecting execution performance of openMP programs. Tsinghua Sci. Technol. 2005, 10, 304–308. [Google Scholar] [CrossRef]

- Lin, Z.; Kahng, M.; Sabrin, K.M.; Chau, D.H.P.; Lee, H.; Kang, U. Mmap: Fast billion-scale graph computation on a pc via memory mapping. In Proceedings of the 2014 IEEE International Conference on Big Data (Big Data), Washington, DC, USA, 27–30 October 2014; pp. 159–164. [Google Scholar]

- Van Essen, B.; Hsieh, H.; Ames, S.; Pearce, R.; Gokhale, M. DI-MMAP—A scalable memory-map runtime for out-of-core data-intensive applications. Cluster Comput. 2015, 18, 15–28. [Google Scholar] [CrossRef]

- Choi, J.; Kim, J.; Han, H. Efficient Memory Mapped File {I/O} for {In-Memory} File Systems. In Proceedings of the 9th USENIX Workshop on Hot Topics in Storage and File Systems (HotStorage’17), Santa Clara, CA, USA, 12–17 July 2017; p. 5. [Google Scholar]

- Song, N.Y.; Yu, Y.J.; Shin, W.; Eom, H.; Yeom, H.Y. Low-latency memory-mapped i/o for data-intensive applications on fast storage devices. In Proceedings of the 2012 SC Companion: High Performance Computing, Networking Storage and Analysis, Salt Lake City, UT, USA, 10–16 November 2012; pp. 766–770. [Google Scholar]

- Lu, H.; Cai, X.; Zhang, Y.; Fei, X. Visualize traffic data using double buffer graphics. In Proceedings of the 2012 2nd International Conference on Remote Sensing, Environment and Transportation Engineering, Nanjing, China, 1–3 June 2012; pp. 1–4. [Google Scholar]

- Sheeparamatti, R.B.; Sheeparamatti, B.G.; Bharamagoudar, M.; Ambali, N. Simulink model for double buffering. In Proceedings of the 32nd Annual Conference on IEEE Industrial Electronics (IECON 2006), Paris, France, 6–10 November 2006; pp. 4593–4597. [Google Scholar]

- Seng, D.; Wang, H. Realistic real-time rendering of 3D terrain scenes based on OpenGL. In Proceedings of the 2009 First International Conference on Information Science and Engineering, Nanjing, China, 26–28 December; pp. 2121–2124.

- Rajgarhia, A.; Gehani, A. Performance and extension of user space file systems. In Proceedings of the 2010 ACM Symposium on Applied Computing, New York, NY, USA, 16–22 March 2010; pp. 206–213. [Google Scholar]

- Katajainen, J.; Simonsen, B. Adaptable component frameworks: Using vector from the C++ standard library as an example. In Proceedings of the 2009 ACM SIGPLAN Workshop on Generic Programming, Edinburgh, UK, 31 August–2 September 2009; pp. 13–24. [Google Scholar]

- Li, S.; Marsaglia, N.; Garth, C.; Woodring, J.; Clyne, J.; Childs, H. Data reduction techniques for simulation, visualization and data analysis. Comput. Graph. Forum 2018, 37, 422–447. [Google Scholar] [CrossRef]

- Heok, T.K.; Daman, D. A Review on Level of Detail. In Proceedings of the International Conference on Computer Graphics, Imaging and Visualization (CGIV 2004), Penang, Malaysia, 26–29 July 2004; pp. 70–75. [Google Scholar]

- Agrawal, R.; Kadadi, A.; Dai, X.; Andres, F. Challenges and opportunities with big data visualization. In Proceedings of the 7th International Conference on Management of computational and collective intElligence in Digital EcoSystems, New York, NY, USA, 25–29 October 2015; pp. 169–173. [Google Scholar]

- Ma, K.L.; Parker, S. Massively parallel software rendering for visualizing large-scale data sets. IEEE Comput Graph Appl. 2001, 21, 72–83. [Google Scholar] [CrossRef]

- Yu, H.; Ma, K.L.; Welling, J. A parallel visualization pipeline for terascale earthquake simulations. In Proceedings of the 2004 ACM/IEEE Conference on Supercomputing (SC’04), Pittsburgh, PA, USA, 6–12 November 2004; p. 49. [Google Scholar]

- Lindstrom, P.; Pascucci, V. Visualization of large terrains made easy. In Proceedings of the Visualization, San Diego, CA, USA, 21–26 October 2001; pp. 363–574. [Google Scholar]

- Ahrens, J.; Brislawn, K.; Martin, K.; Geveci, B.; Law, C.C.; Papka, M. Large-scale data visualization using parallel data streaming. IEEE Comput Graph Appl. 2001, 21, 34–41. [Google Scholar] [CrossRef]

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | |

|---|---|---|---|---|---|---|---|

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 2 | 1 | 10 | 1 × 102 | 1 × 103 | 1 × 104 | 1 × 105 | 1 × 106 |

| 3 | 2 | 20 | 2 × 102 | 2 × 103 | 2 × 104 | 2 × 105 | 2 × 106 |

| 4 | 3 | 30 | 3 × 102 | 3 × 103 | 3 × 104 | 3 × 105 | 3 × 106 |

| 5 | 4 | 40 | 4 × 102 | 4 × 103 | 4 × 104 | 4 × 105 | 4 × 106 |

| 6 | 5 | 50 | 5 × 102 | 5 × 103 | 5 × 104 | 5 × 105 | 5 × 106 |

| 7 | 6 | 60 | 6 × 102 | 6 × 103 | 6 × 104 | 6 × 105 | 6 × 106 |

| 8 | 7 | 70 | 7 × 102 | 7 × 103 | 7 × 104 | 7 × 105 | 7 × 106 |

| 9 | 8 | 80 | 8 × 102 | 8 × 103 | 8 × 104 | 8 × 105 | 8 × 106 |

| 10 | 9 | 90 | 9 × 102 | 9 × 103 | 9 × 104 | 9 × 105 | 9 × 106 |

| File Size | Grid Size/μm2 | Number of Horizontal and Vertical Grids | Grid Number |

|---|---|---|---|

| 160.3 MB | 20 × 20 | 1503 × 1524 | 2,290,572 |

| 423.7 MB | 10 × 10 | 2404 × 2496 | 6,000,384 |

| 867.7 MB | 2 × 2 | 5751 × 2221 | 12,772,971 |

| 3.4 GB | 1 × 1 | 5775 × 8653 | 49,971,075 |

| File Size | Reading Time/s * | |||

|---|---|---|---|---|

| Single Thread | Single Thread + Mmap | Single Thread + Mmap + Optimize | Multi-Thread + Mmap + Optimize | |

| 160.3 MB | 6.36 | 4.89 | 1.61 | 0.68 |

| 423.7 MB | 16.72 | 12.01 | 4.23 | 1.82 |

| 867.7 MB | 33.52 | 21.79 | 9.51 | 4.50 |

| 3.4 GB | 133.09 | 80.12 | 38.95 | 17.04 |

| File Size | Drawing Time/s * | ||

|---|---|---|---|

| Single Thread | Single Thread + Downsample | Multi-Thread + Downsample | |

| 160.3 MB | 2.77 | 0.76 | 0.23 |

| 423.7 MB | 7.34 | 1.03 | 0.67 |

| 867.6 MB | 16.32 | 1.66 | 0.96 |

| 3.4 GB | 56.89 | 1.97 | 1.08 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ji, Z.; Chen, L.; Sun, Y.; Cai, H. Research on Parallel Reading and Drawing Techniques for Chemical Mechanical Polishing Simulation Data Based on Multi-Thread. Electronics 2024, 13, 706. https://doi.org/10.3390/electronics13040706

Ji Z, Chen L, Sun Y, Cai H. Research on Parallel Reading and Drawing Techniques for Chemical Mechanical Polishing Simulation Data Based on Multi-Thread. Electronics. 2024; 13(4):706. https://doi.org/10.3390/electronics13040706

Chicago/Turabian StyleJi, Zhenyu, Lan Chen, Yan Sun, and Hong Cai. 2024. "Research on Parallel Reading and Drawing Techniques for Chemical Mechanical Polishing Simulation Data Based on Multi-Thread" Electronics 13, no. 4: 706. https://doi.org/10.3390/electronics13040706