Comprehensive Investigation of Promising Techniques to Enhance the Voltage Sharing among SiC MOSFET Strings, Supported by Experimental and Simulation Validations

Abstract

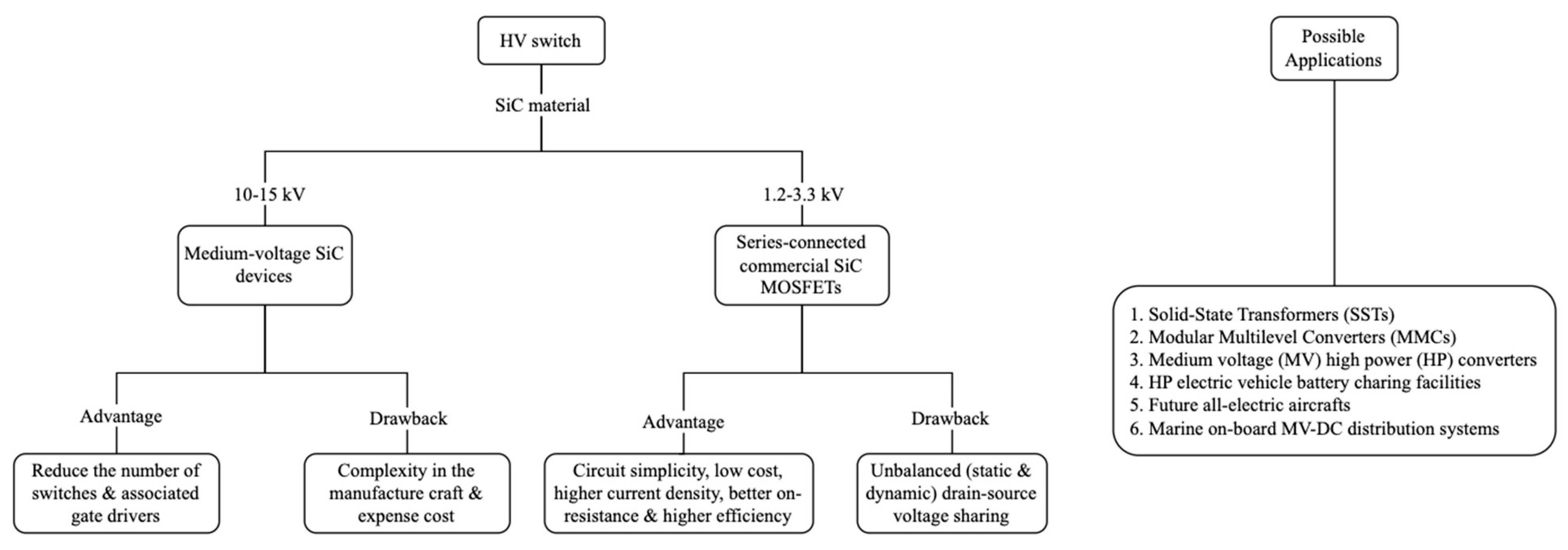

1. Introduction

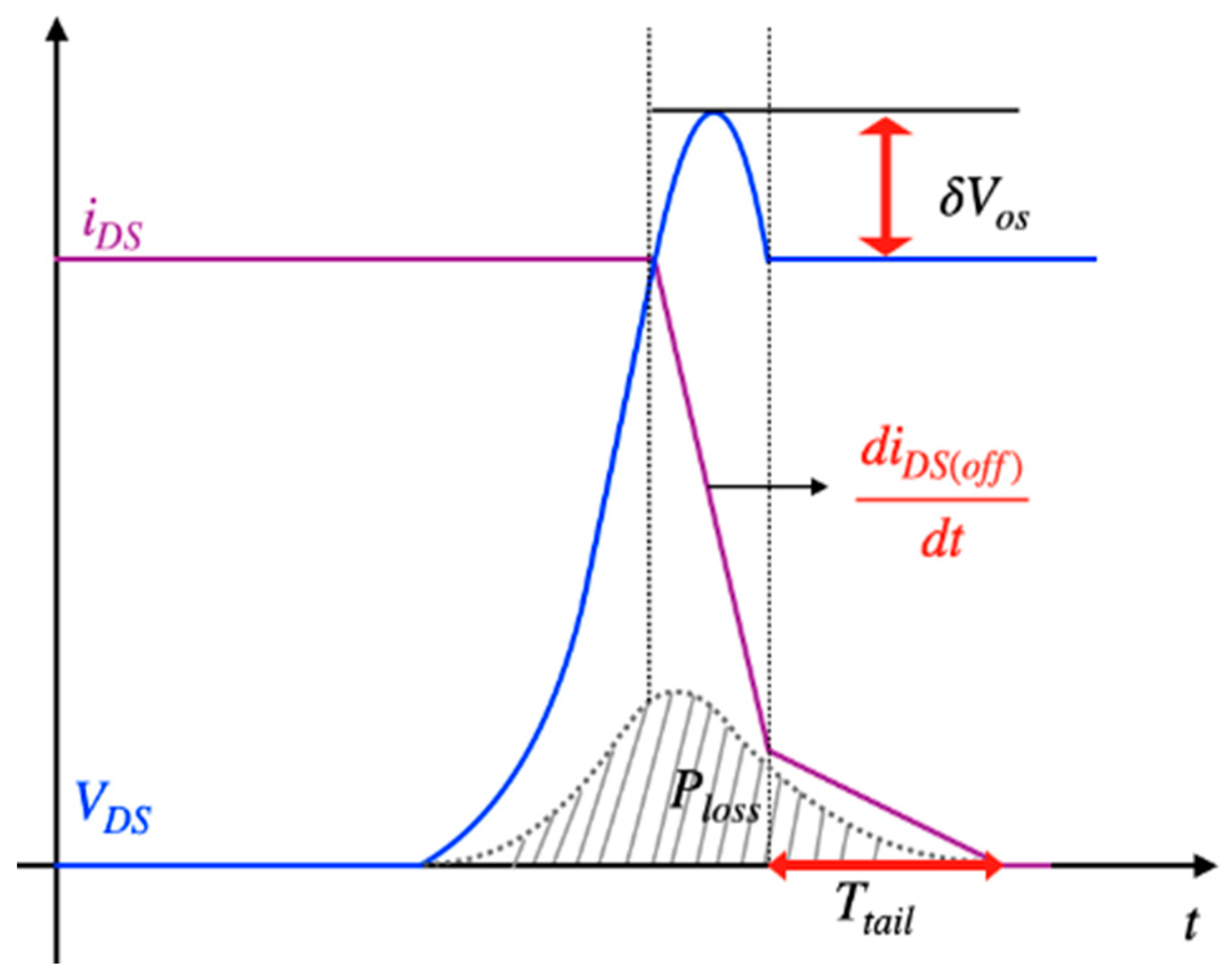

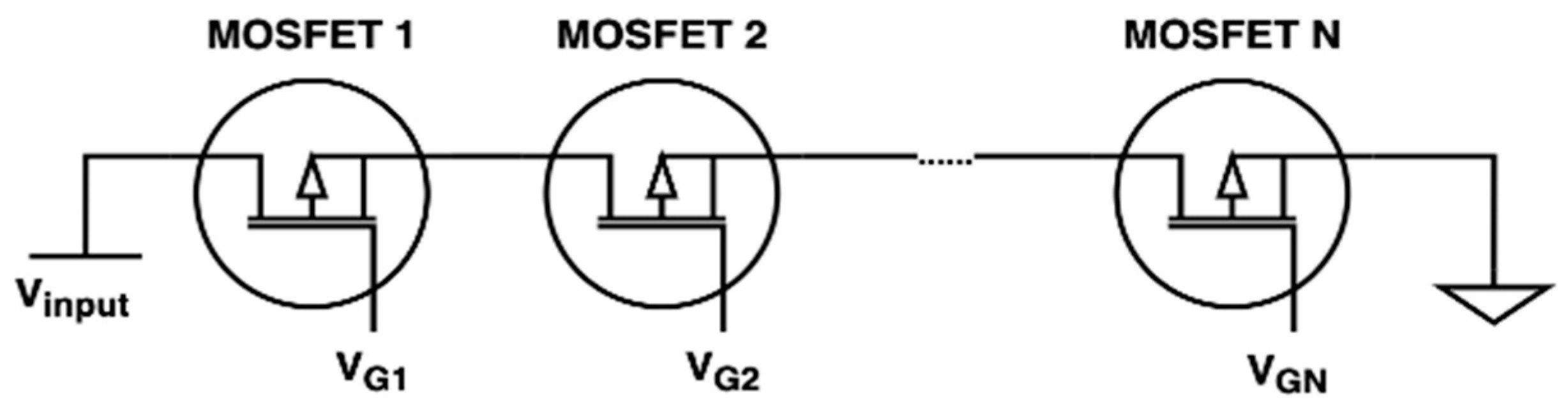

1.1. Factors Influencing the Drain-Source Voltage Distribution

1.2. State-of-the-Art Solutions

1.3. Outline

2. Static Voltage-Balancing Method

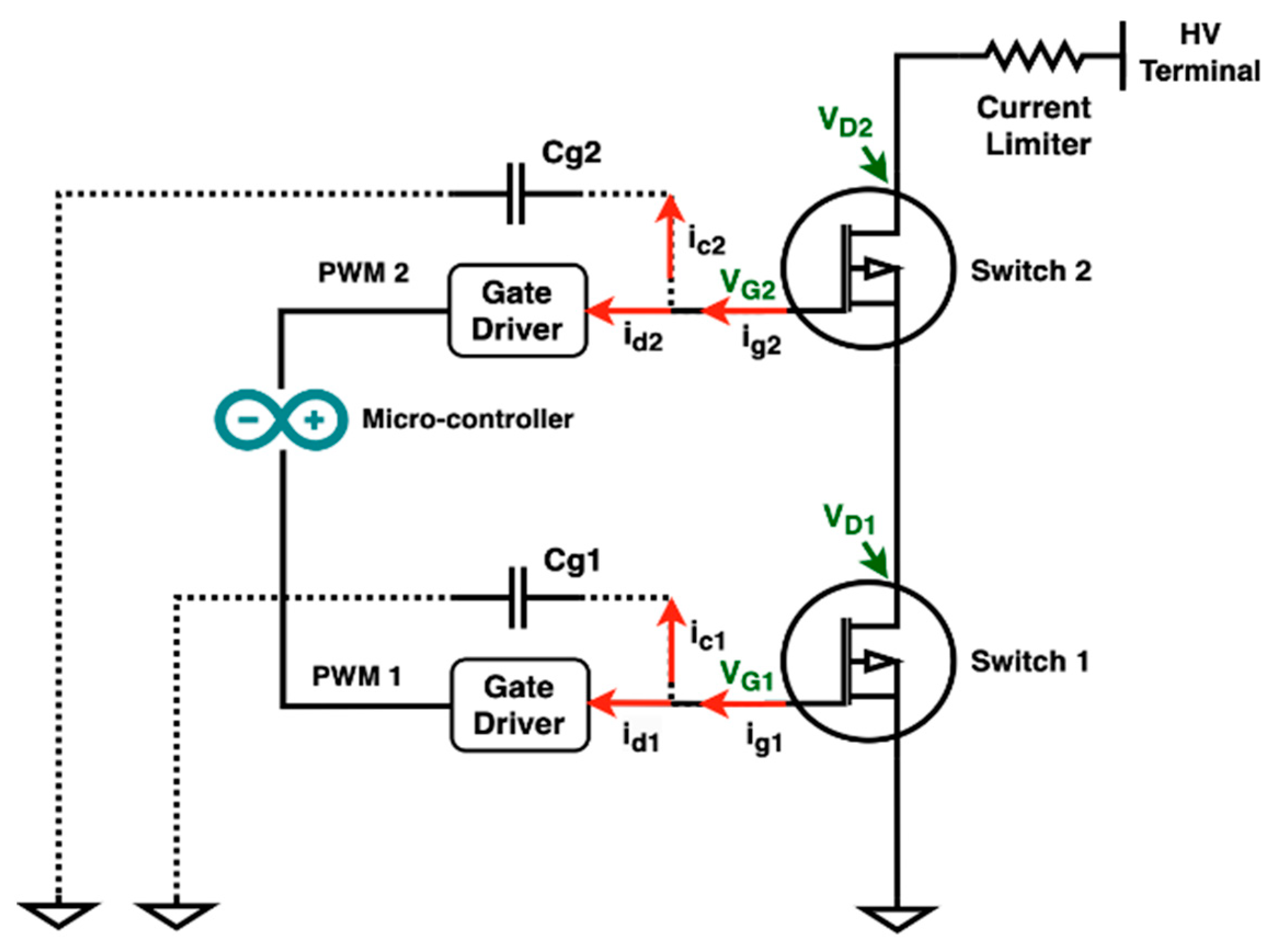

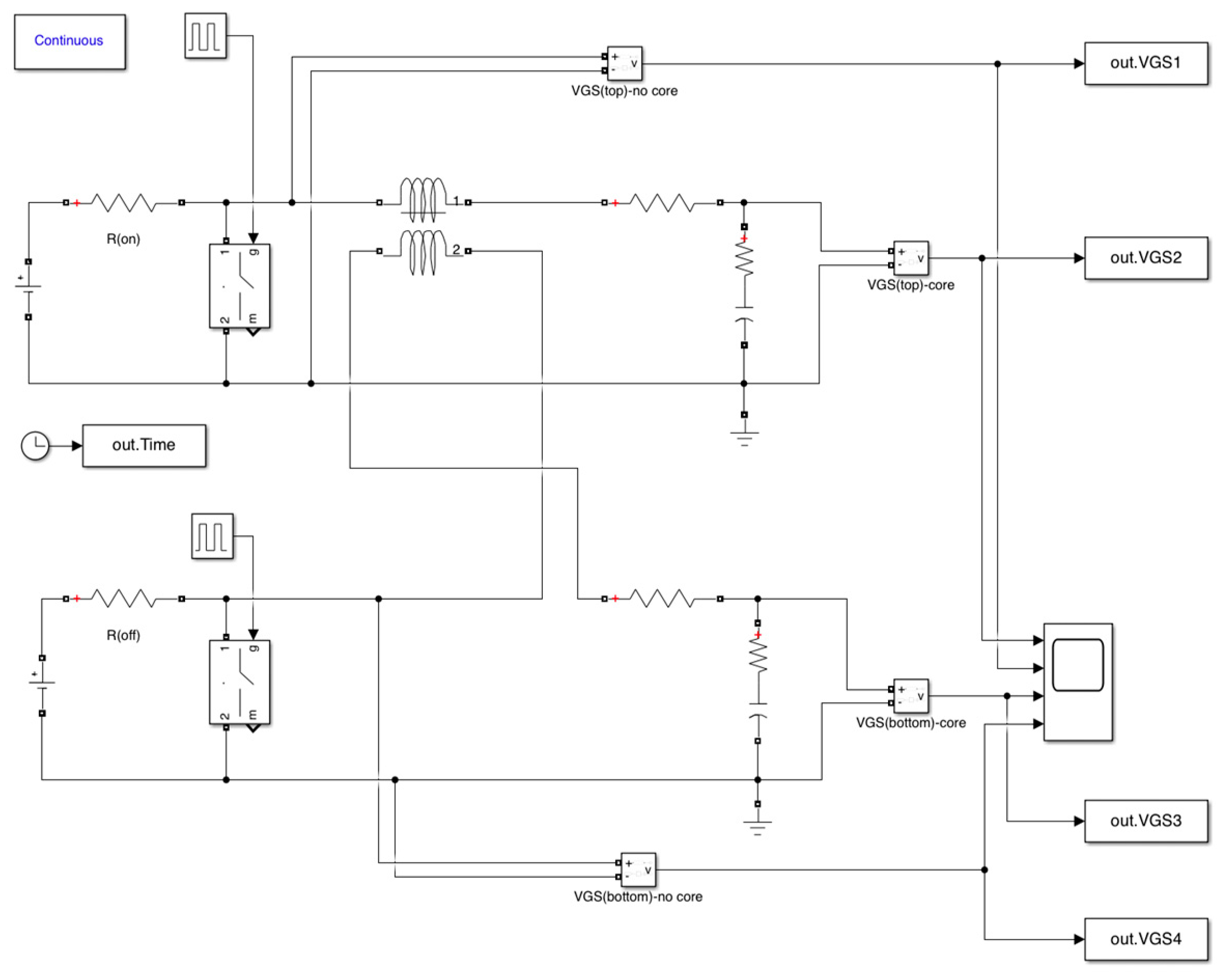

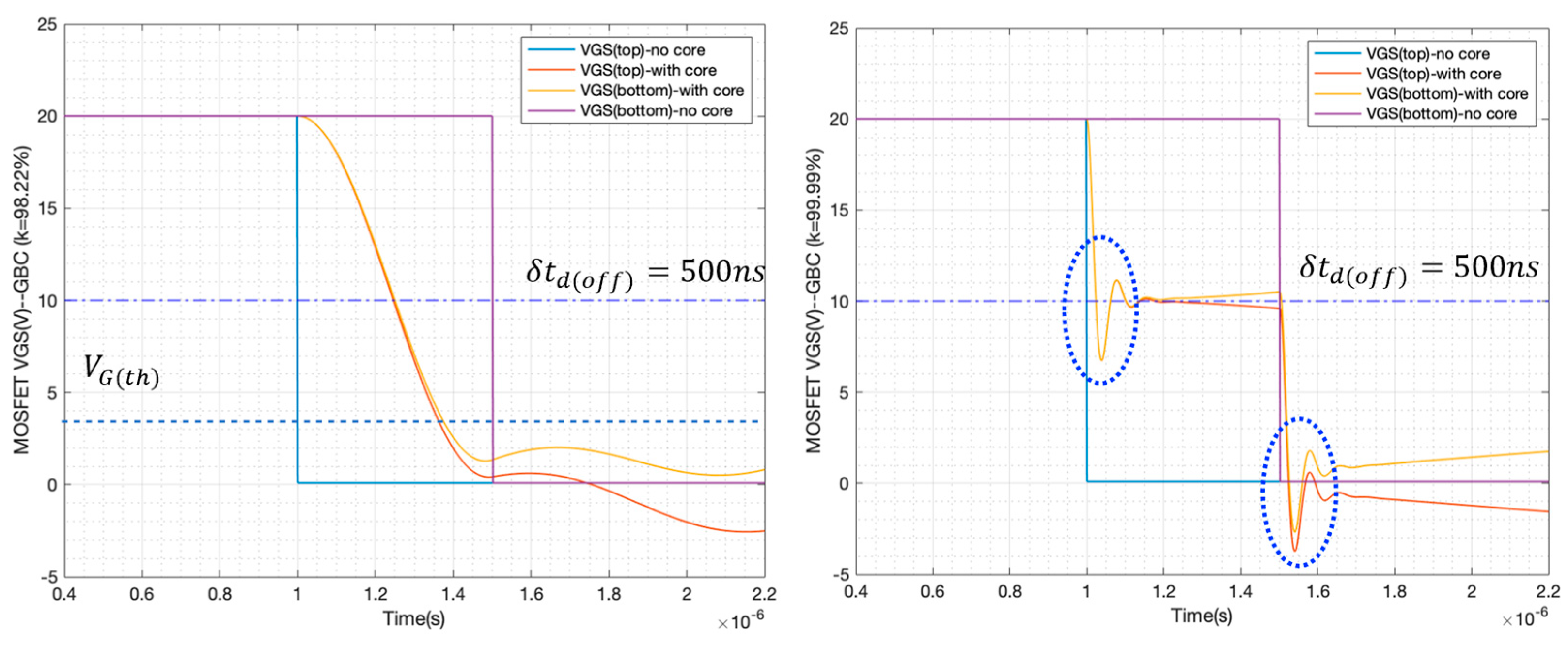

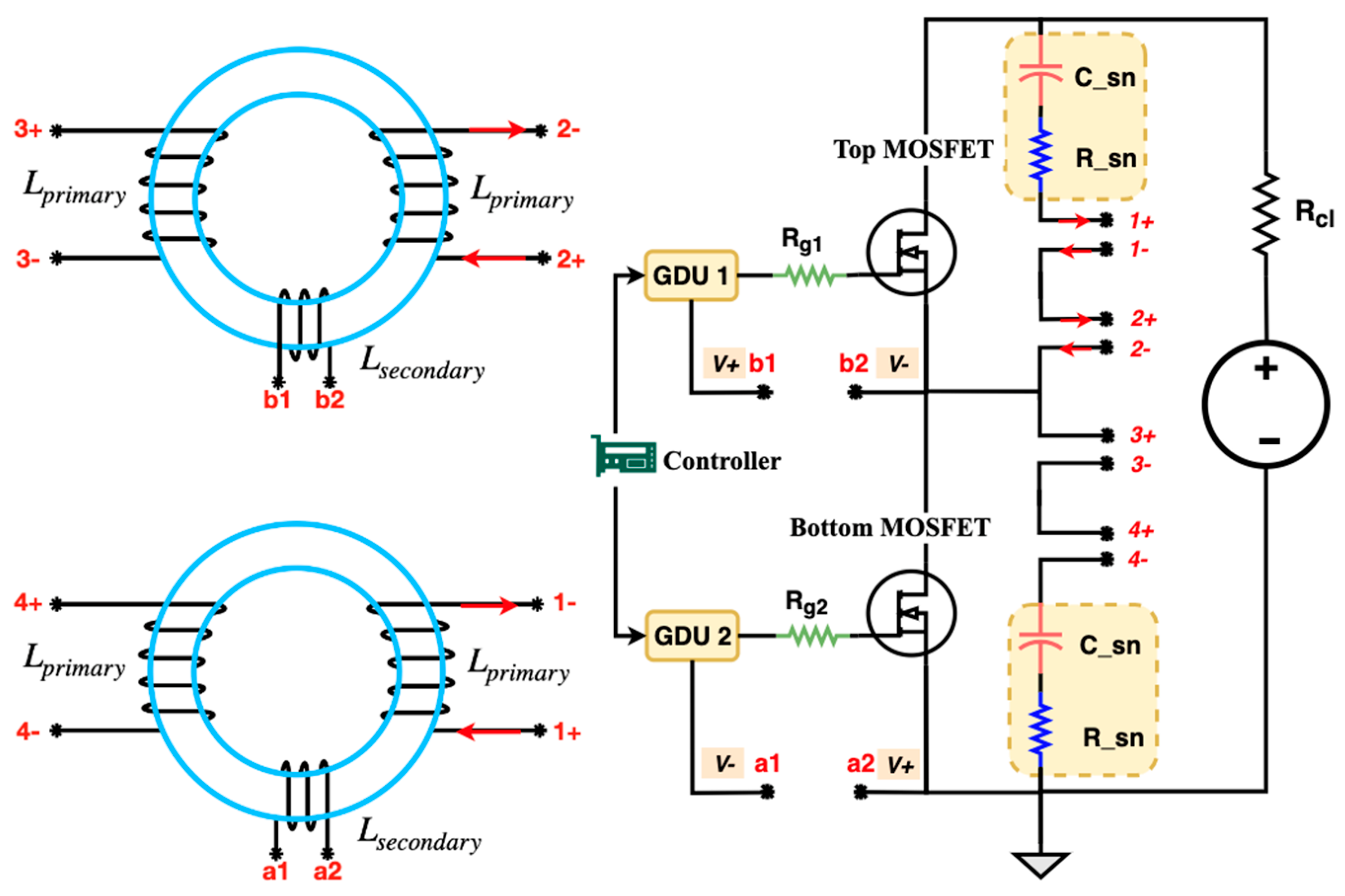

3. Gate-Balancing Core (GBC) Method

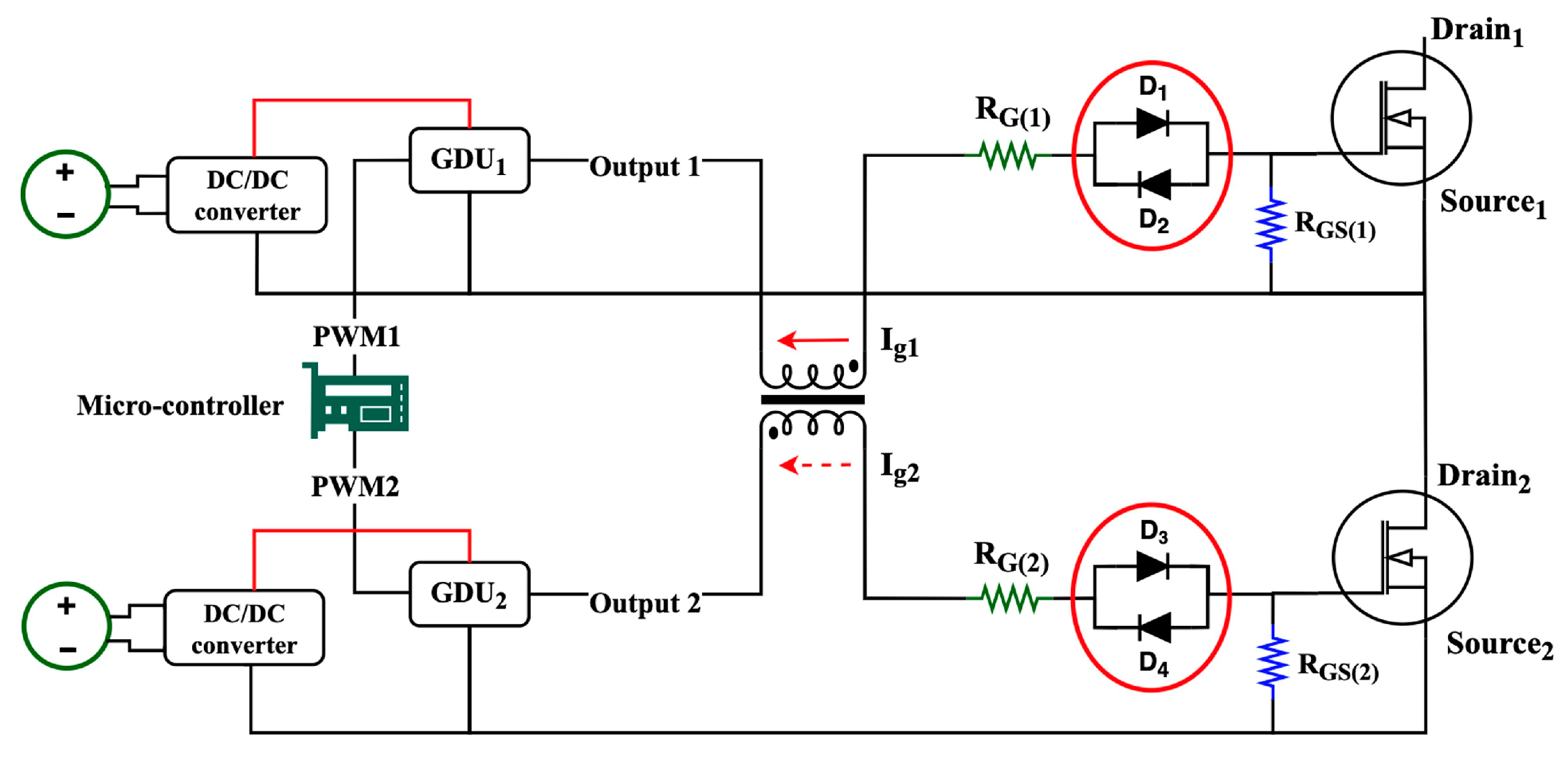

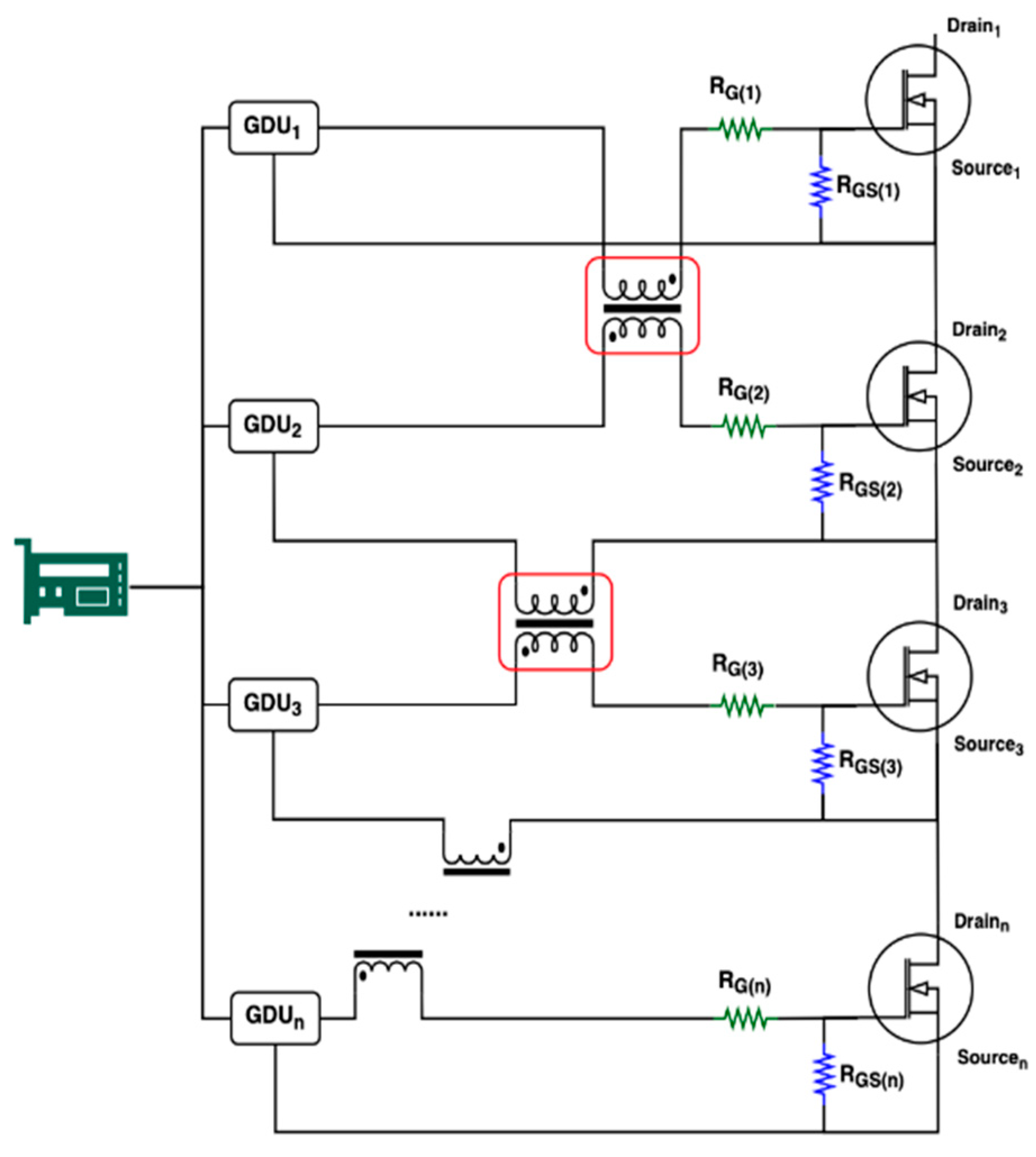

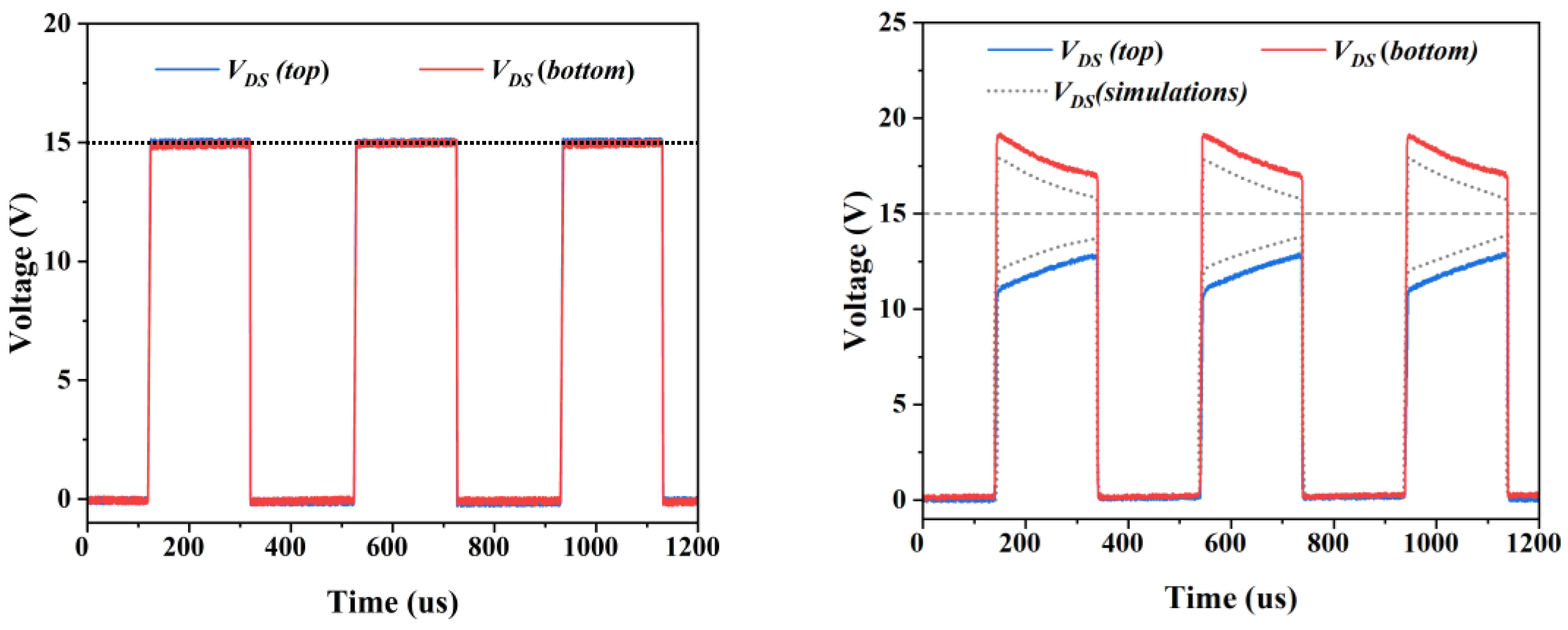

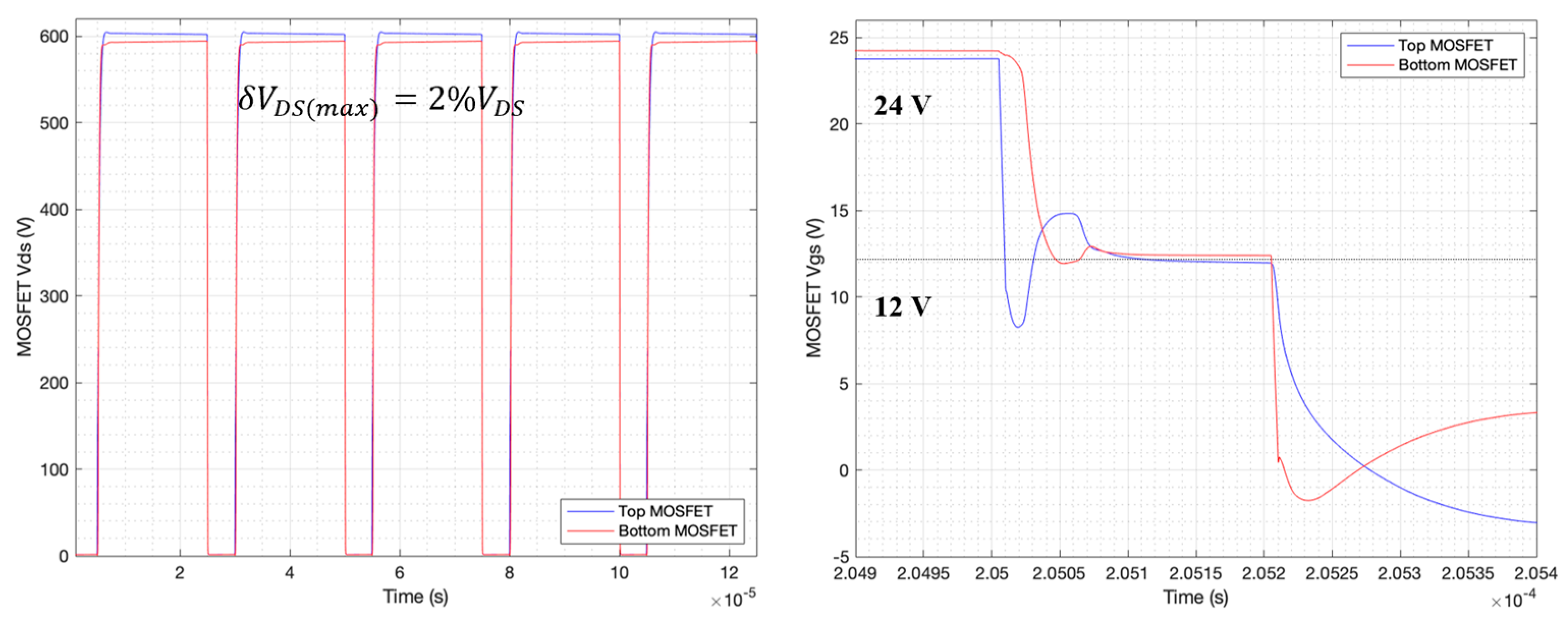

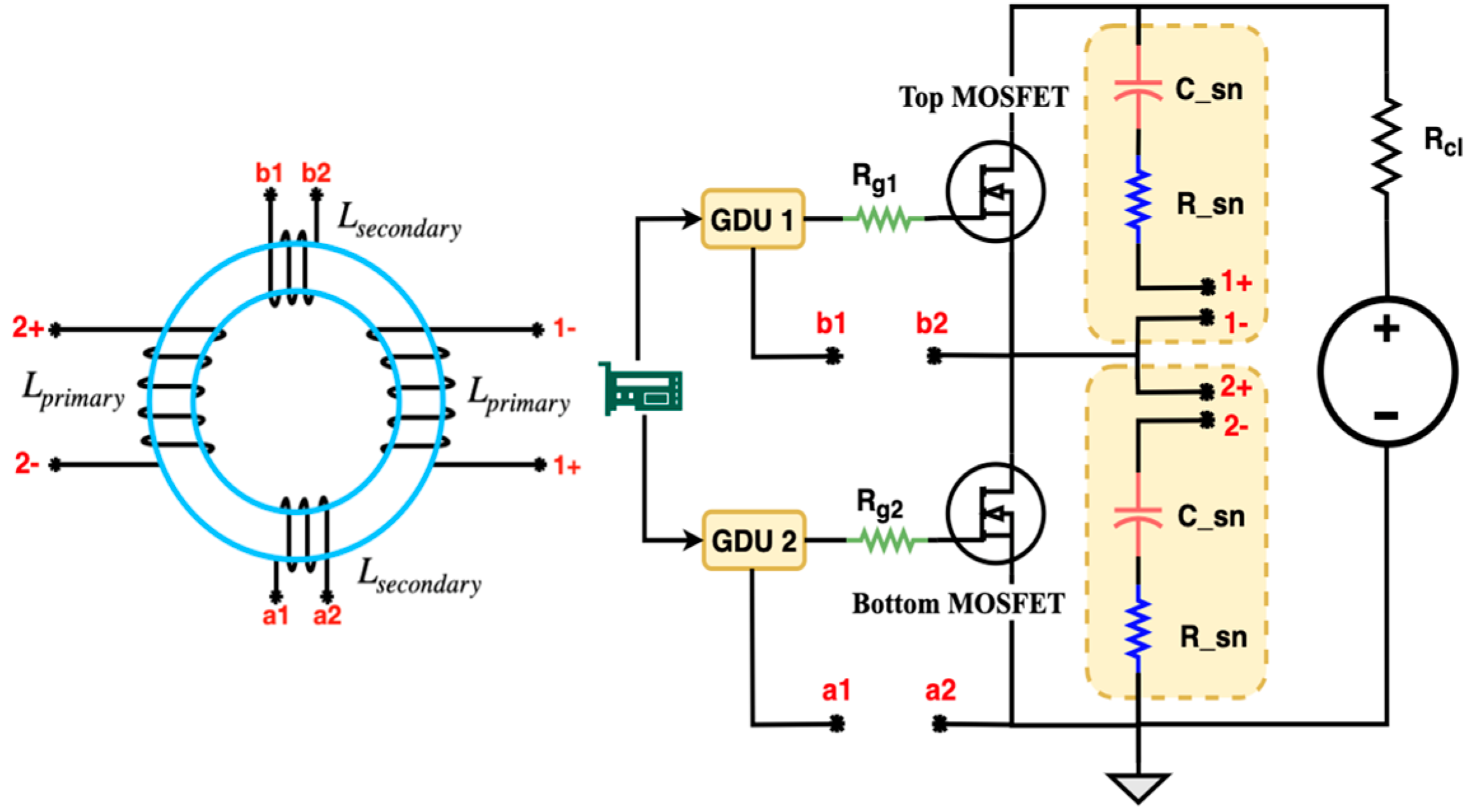

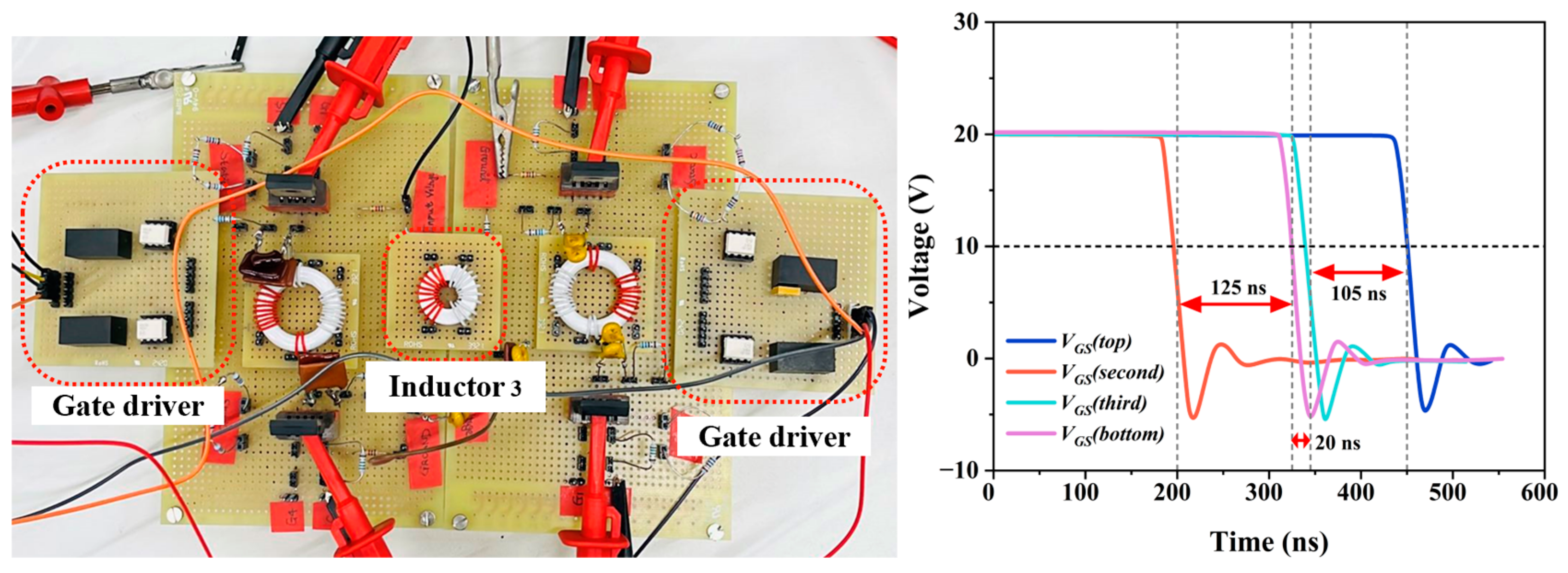

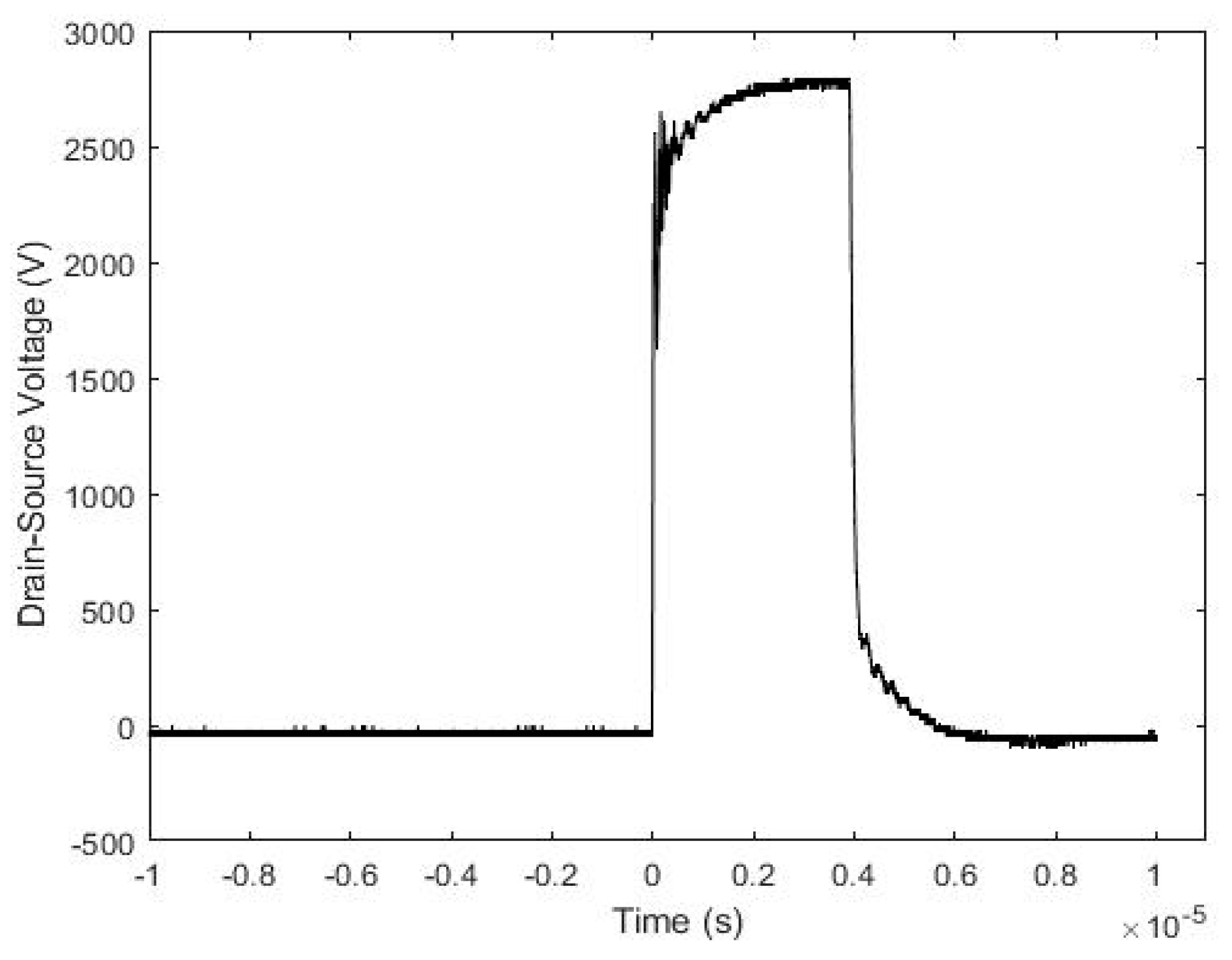

3.1. Experiments with Two Series-Connected MOSFETs Using the GBC Method

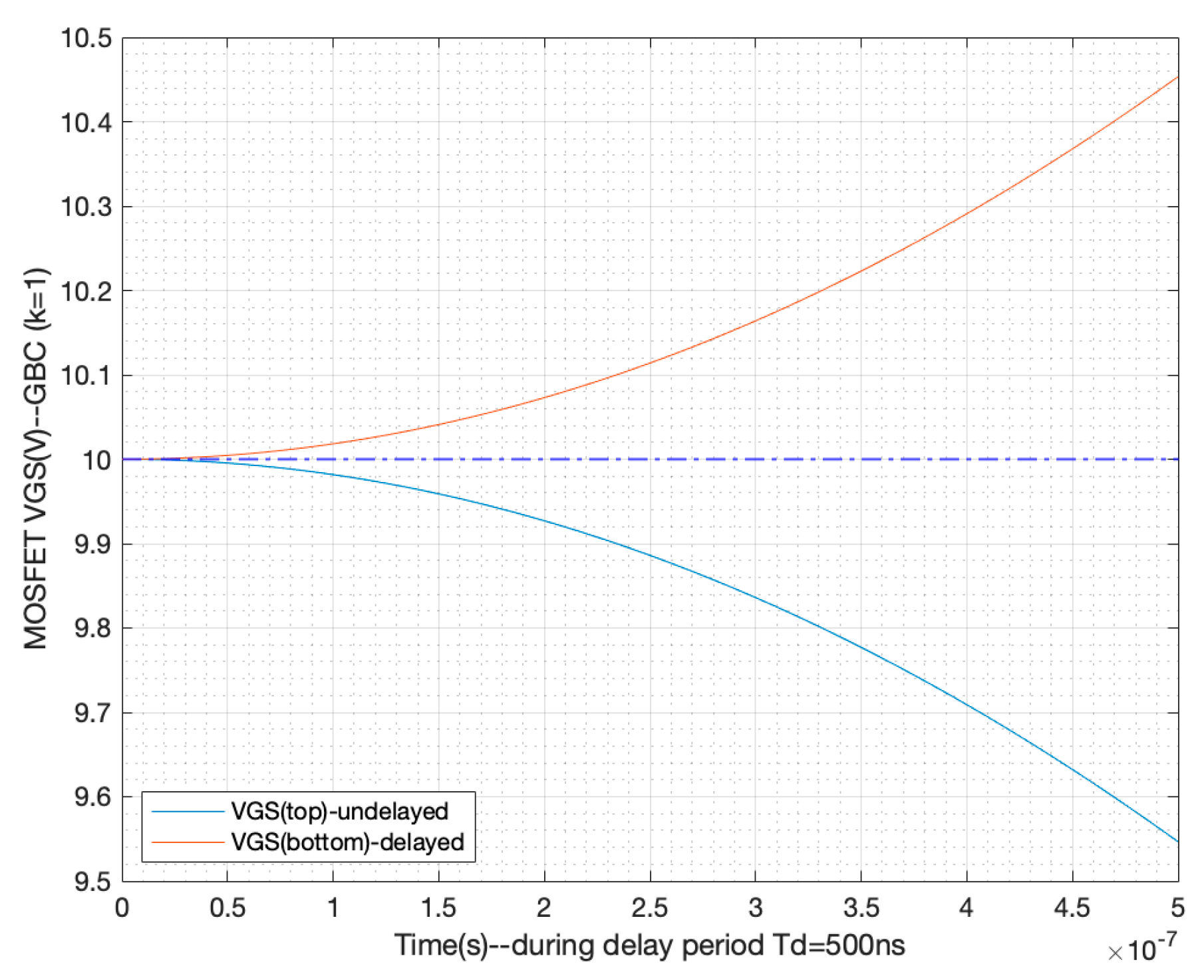

3.2. Analytical Analysis of Dynamic Voltage Sharing Using the GBC Method

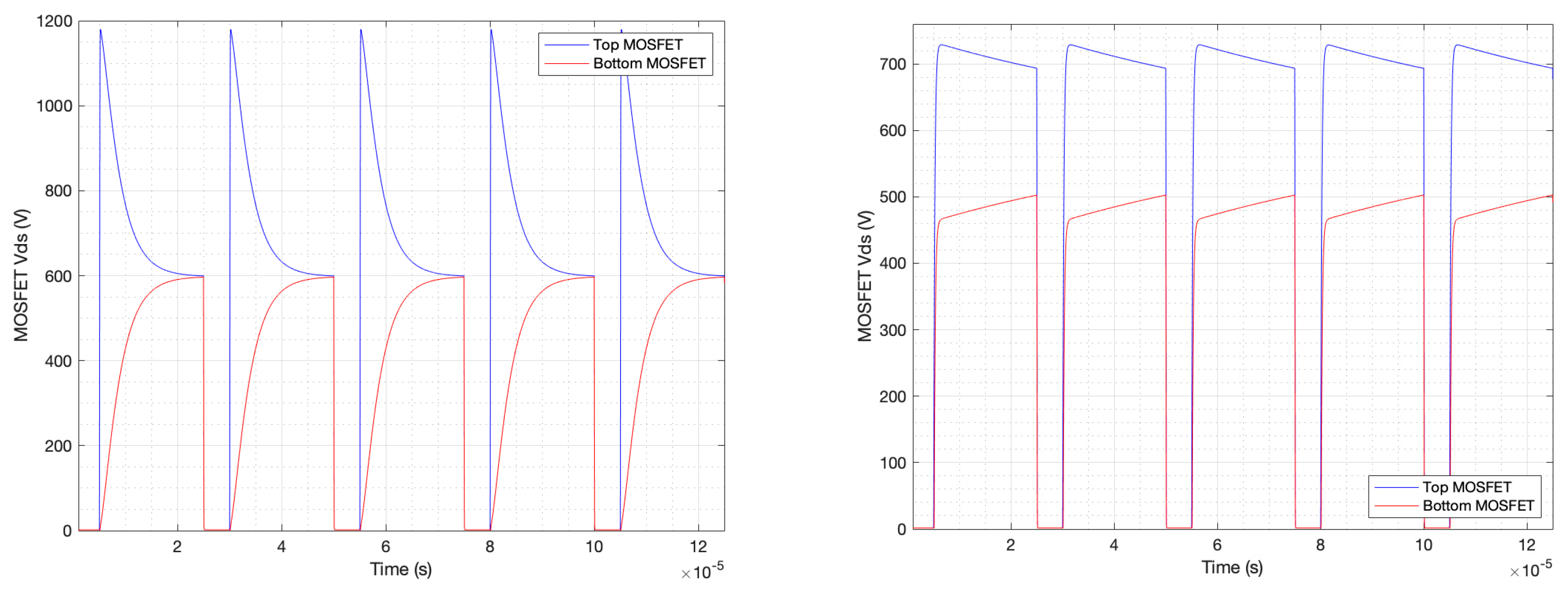

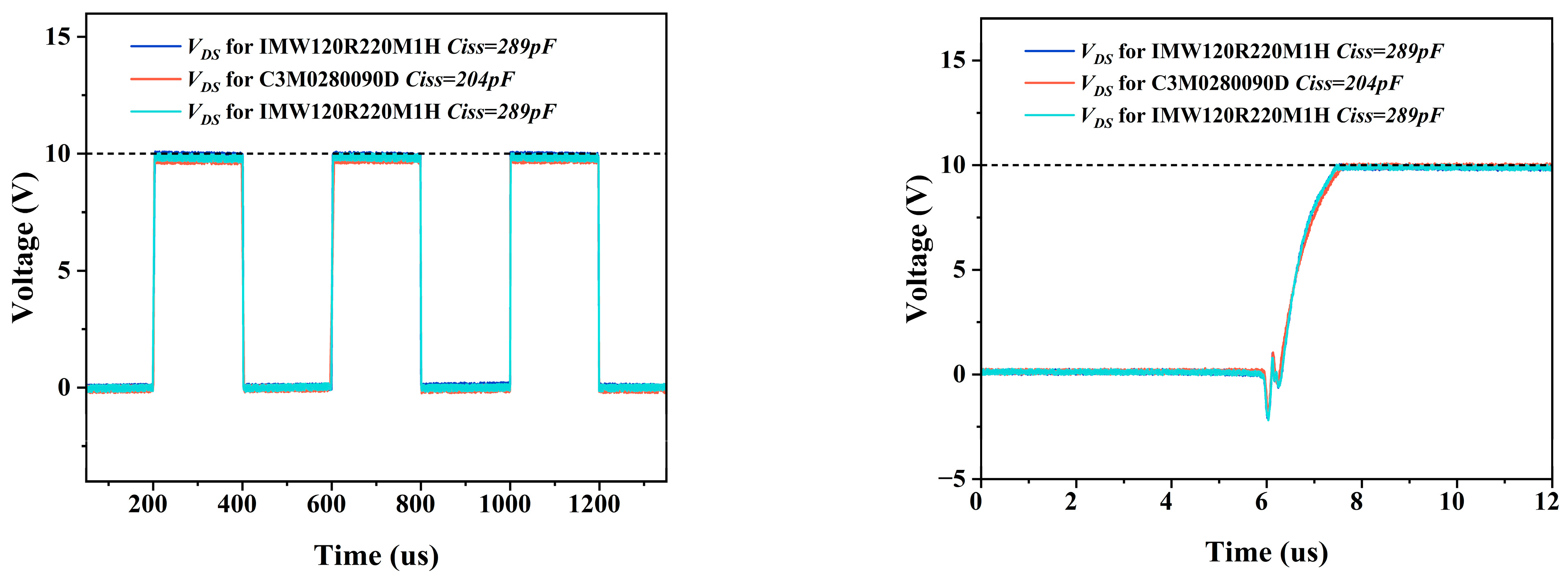

3.3. Simulation Verification of Dynamic Voltage Sharing Using the GBC Method

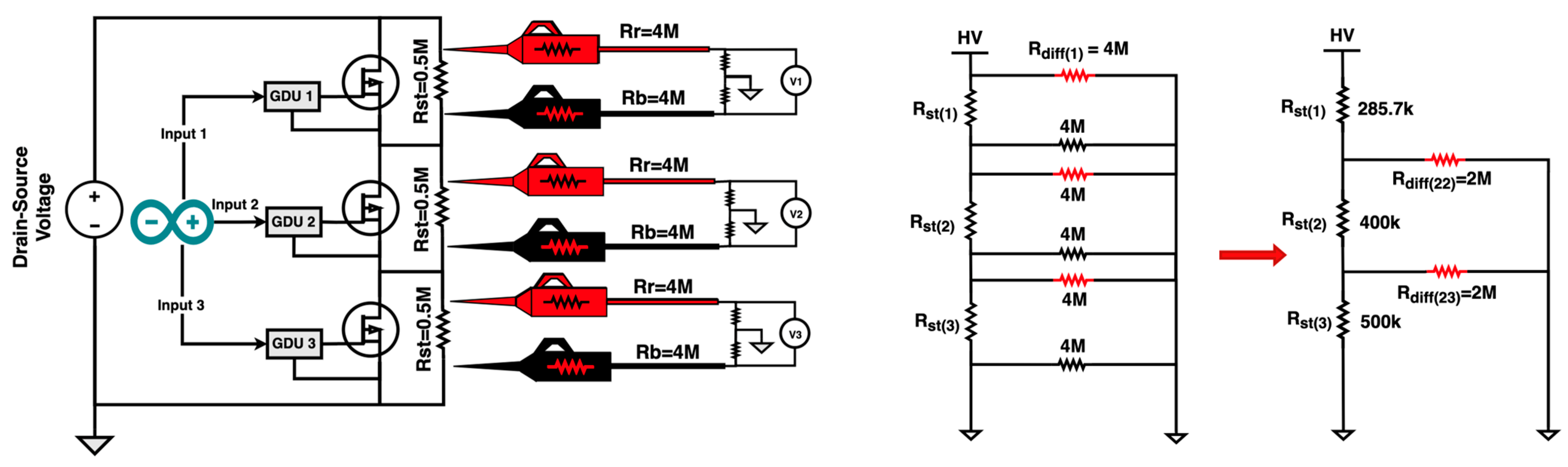

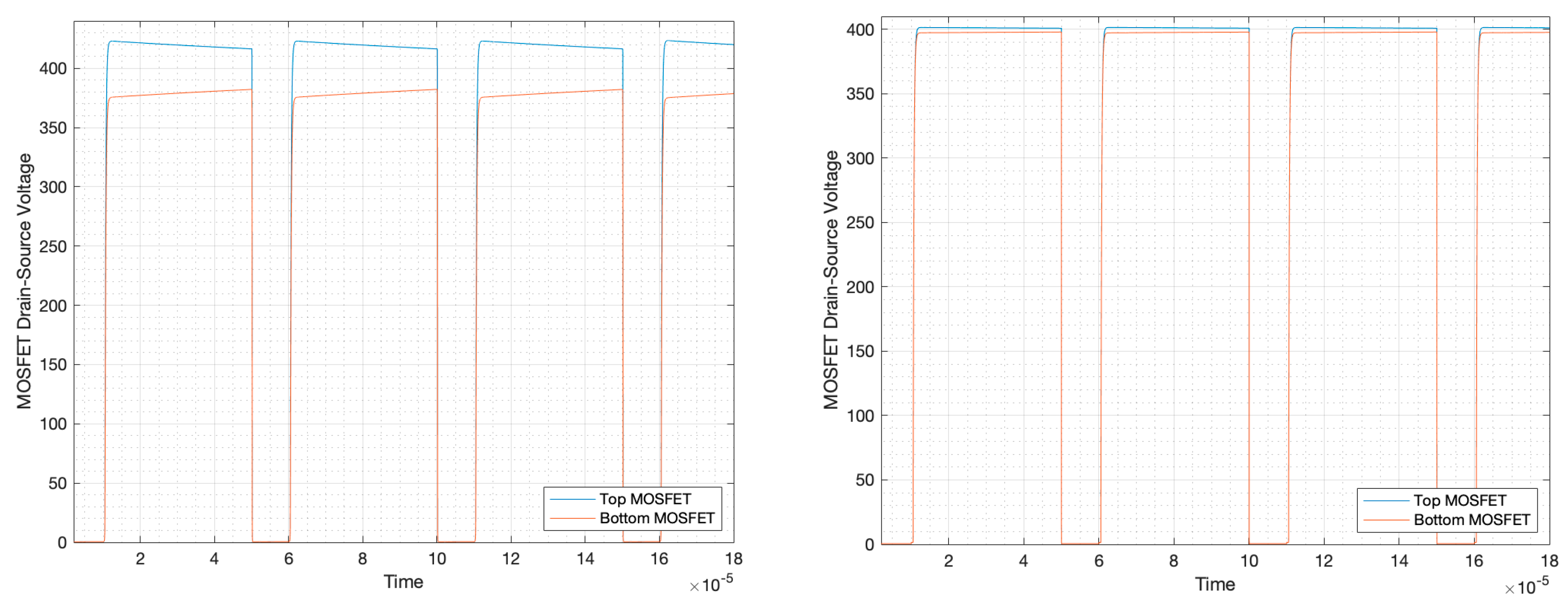

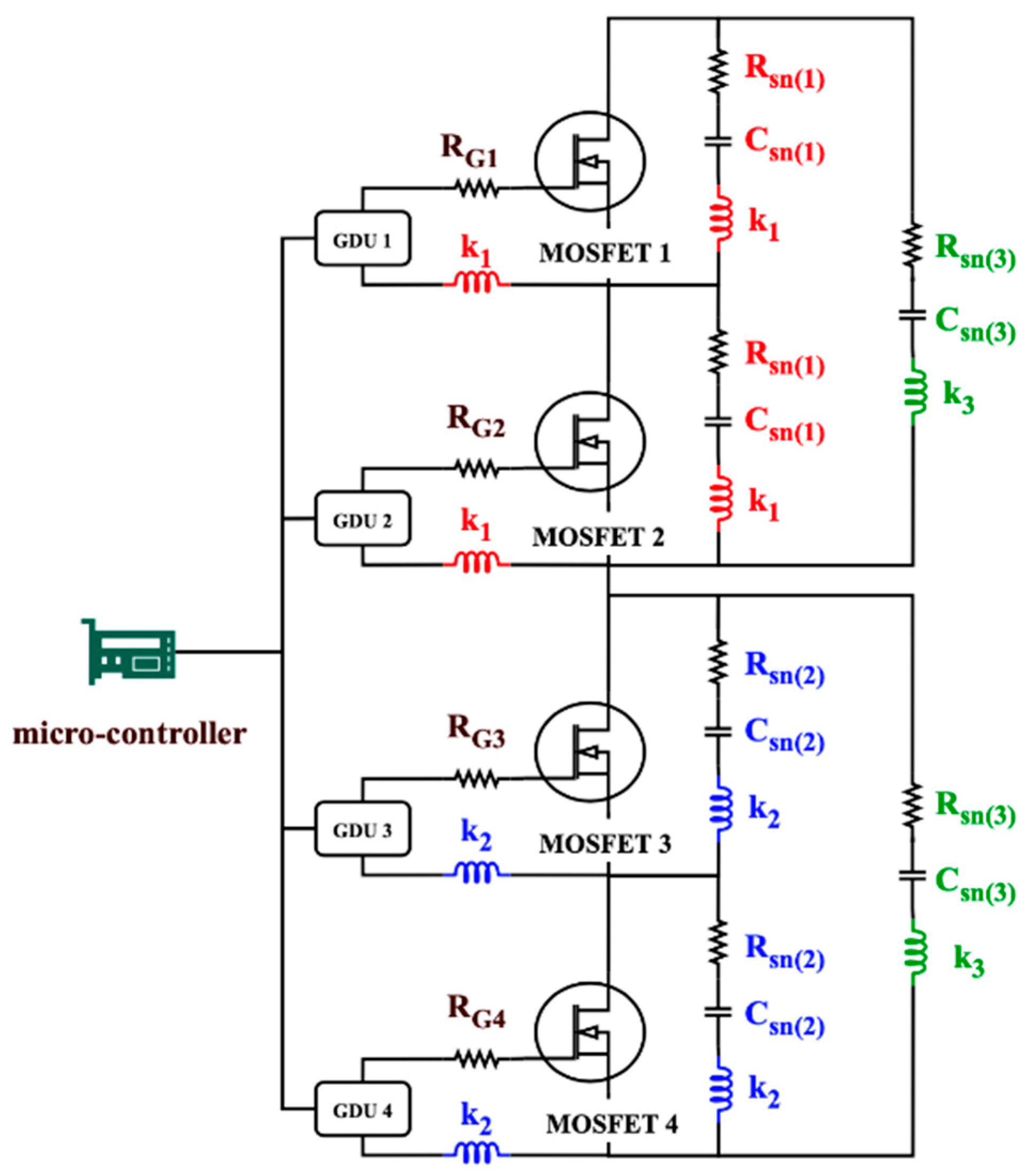

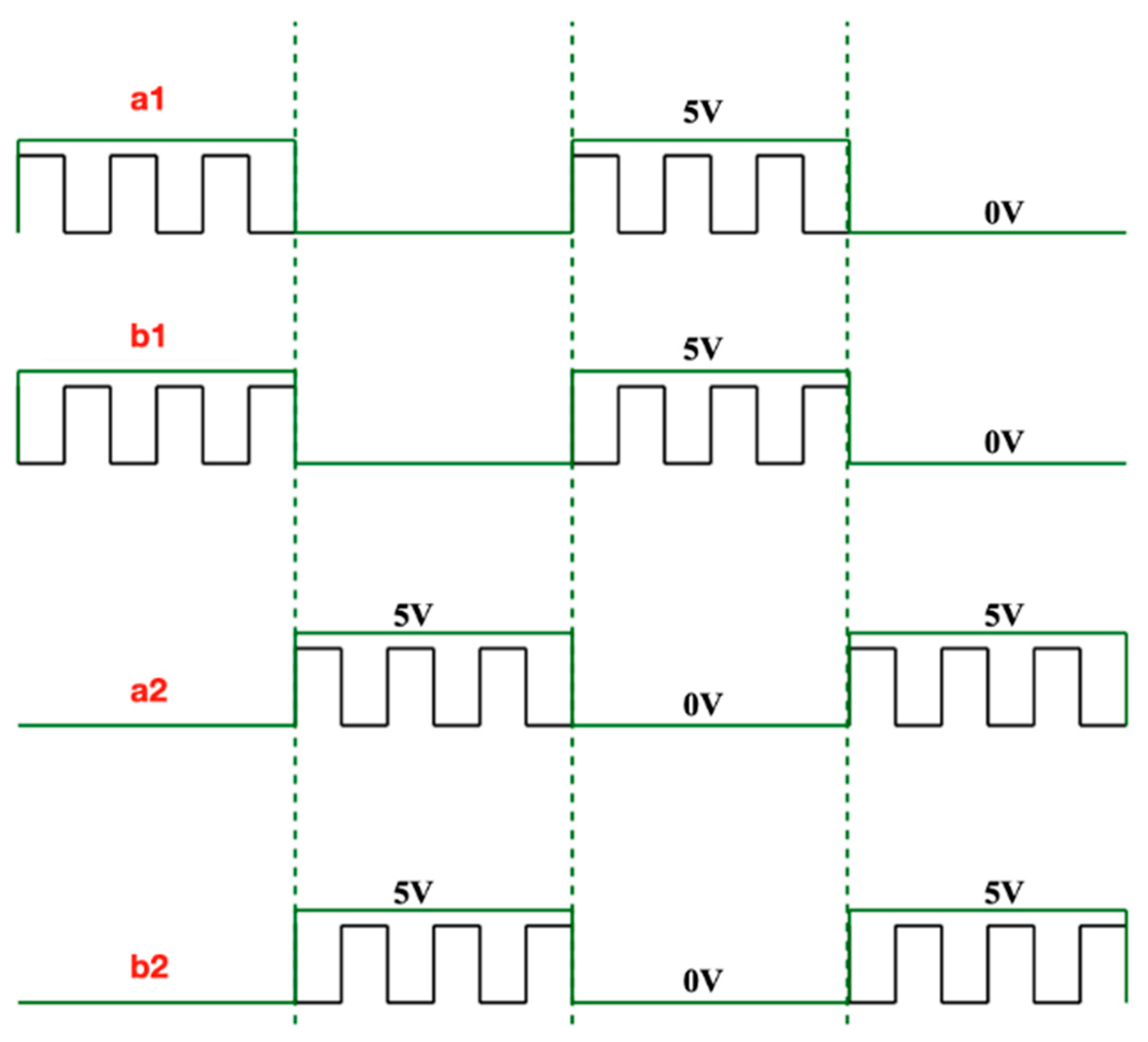

4. Hybrid Gate Signal Delay Adjustment Method—Improved RC Snubber Method

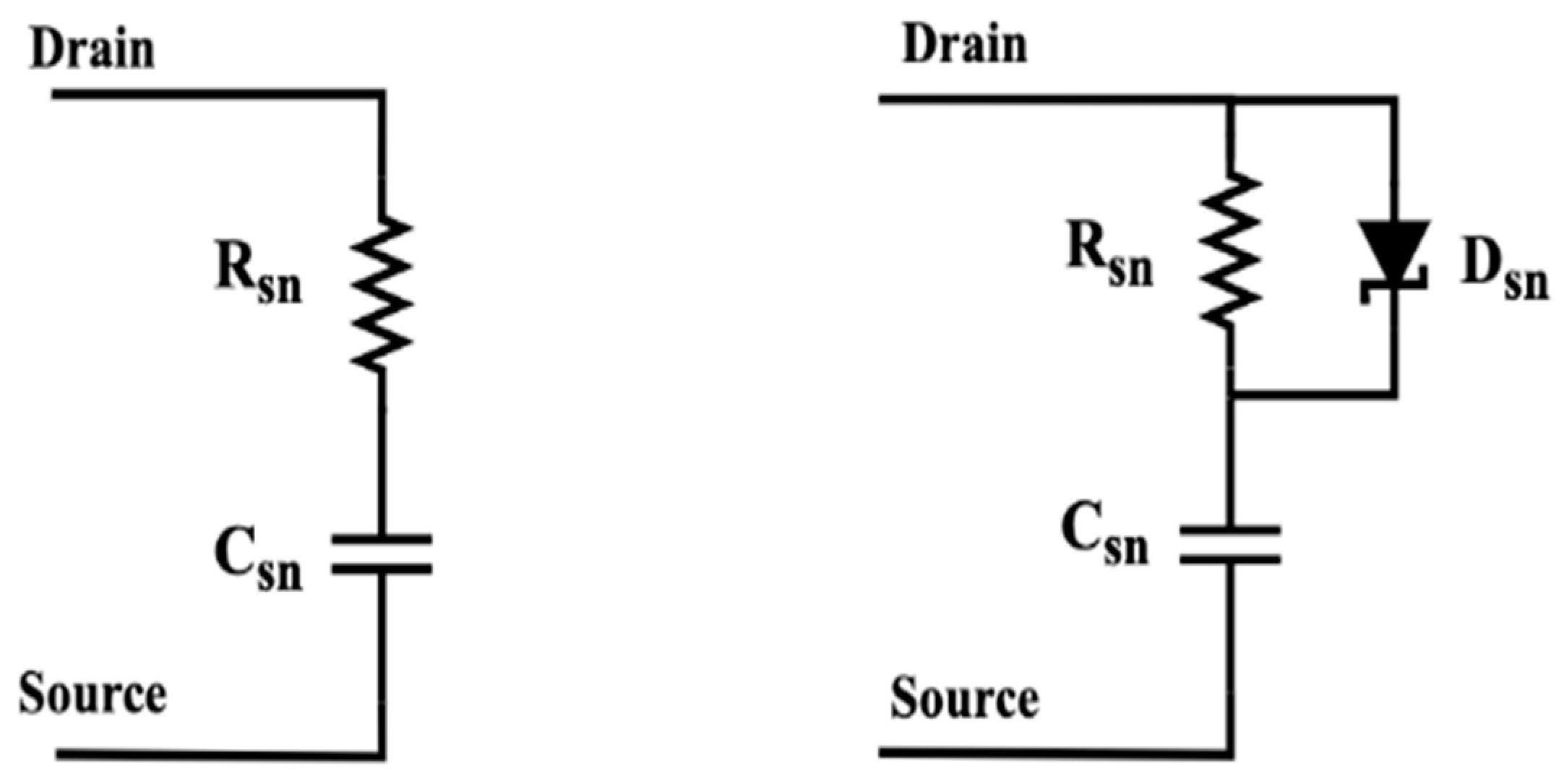

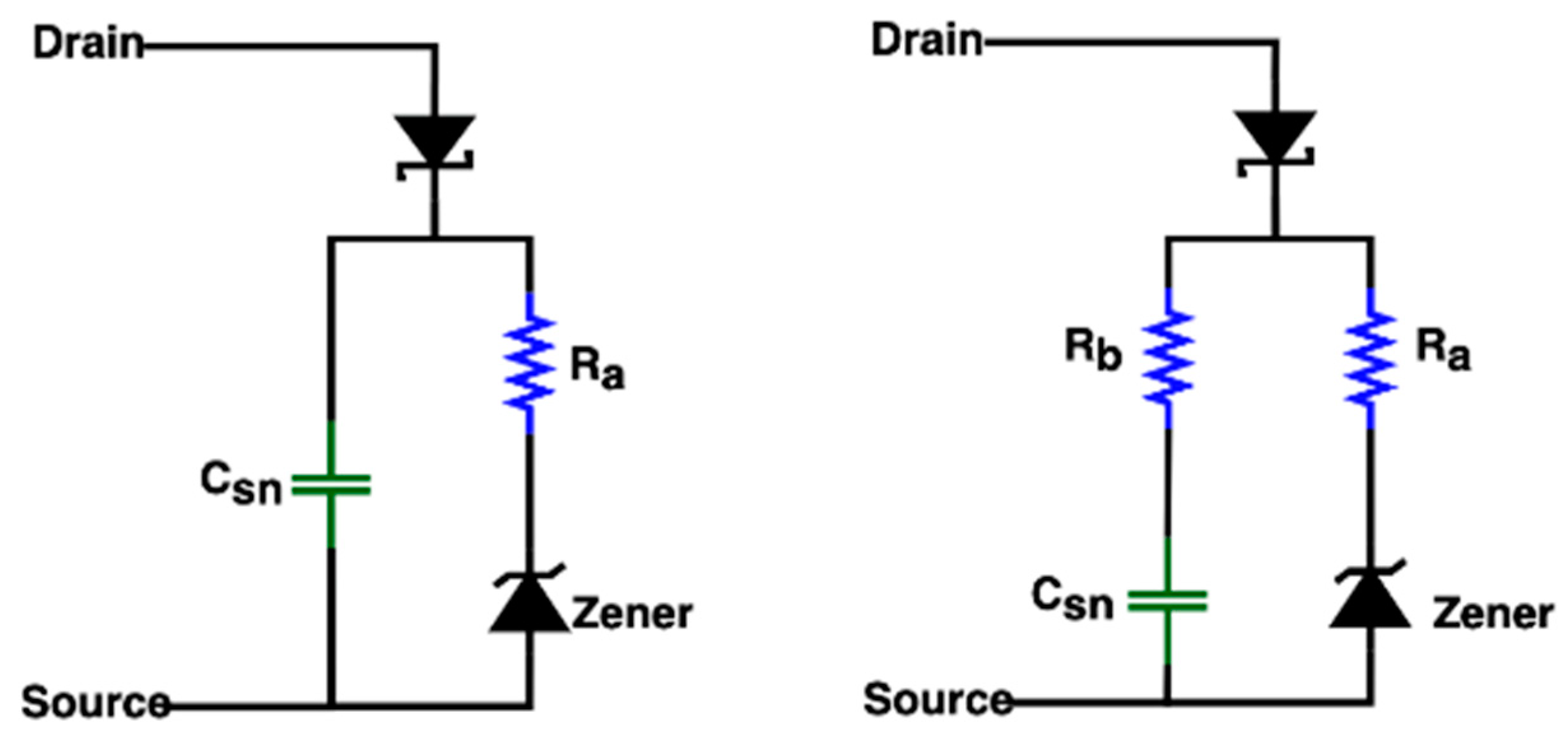

4.1. Passive Snubber Circuits

4.2. Improved RC Snubber Method (a)

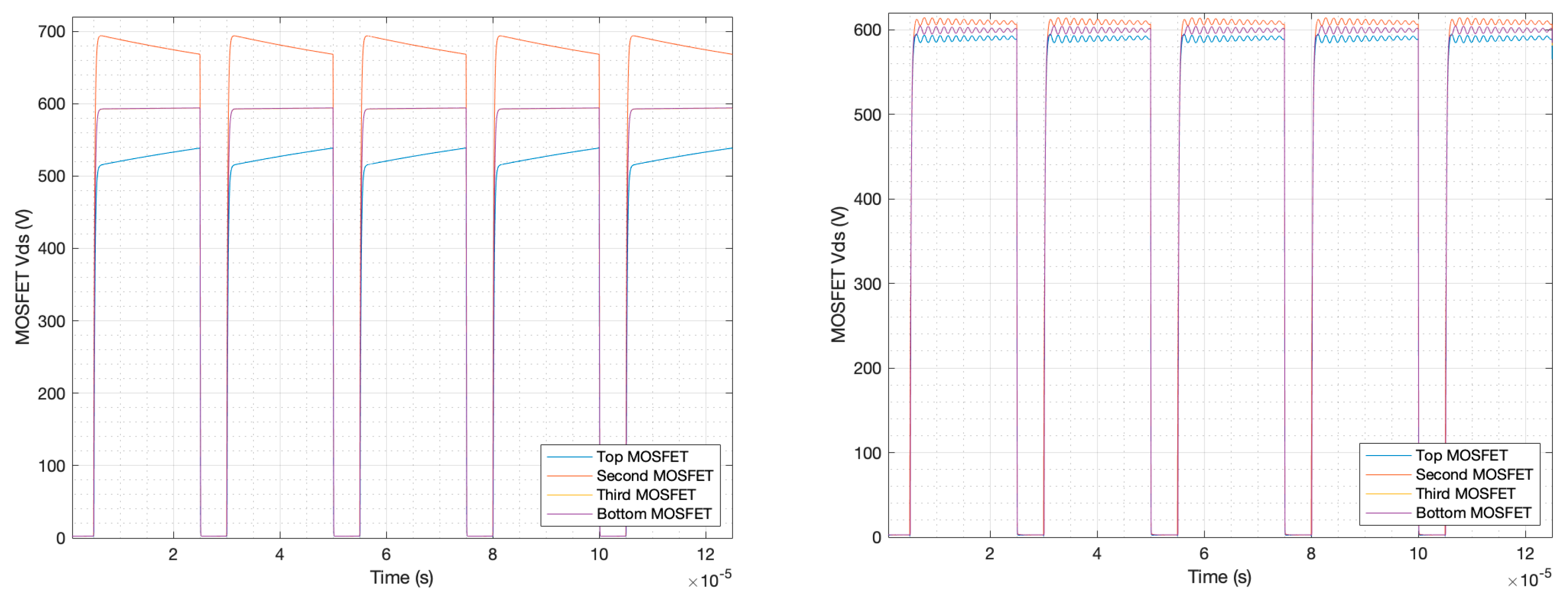

4.3. Improved RC Snubber Method (b)

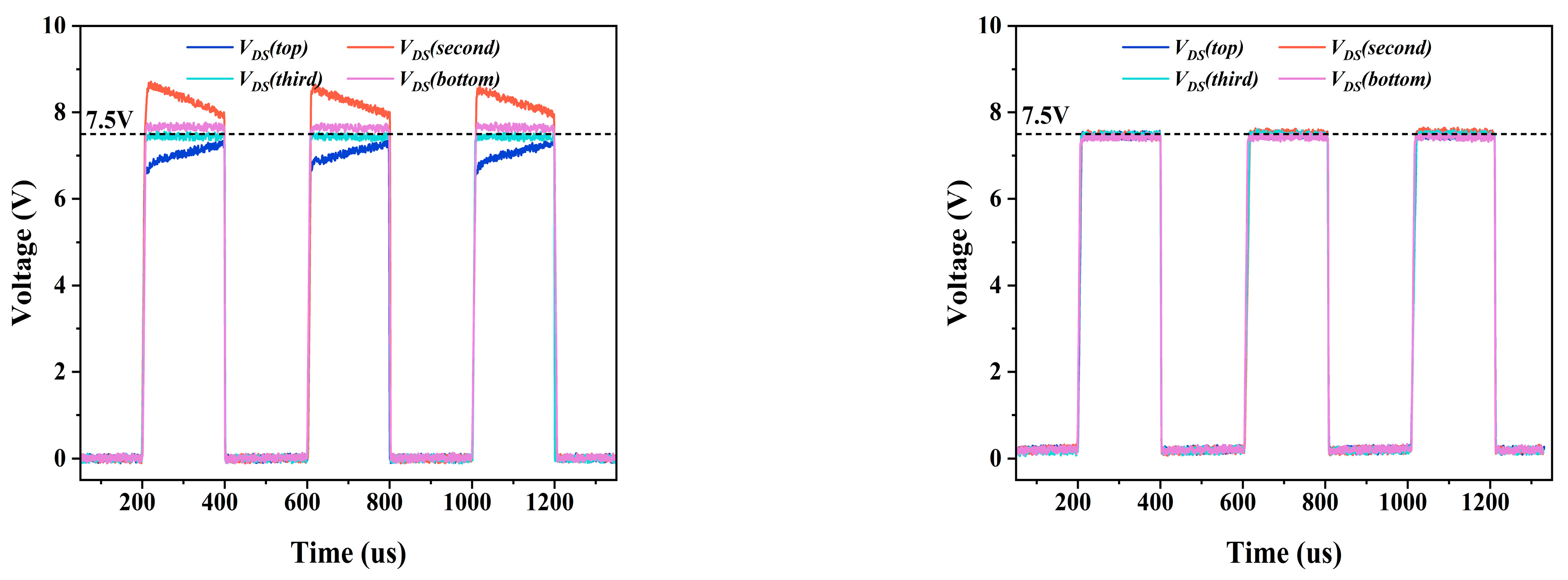

4.4. Experiments Using Improved RC Snubber Method (b) on Four Series-Connected SiC MOSFETs

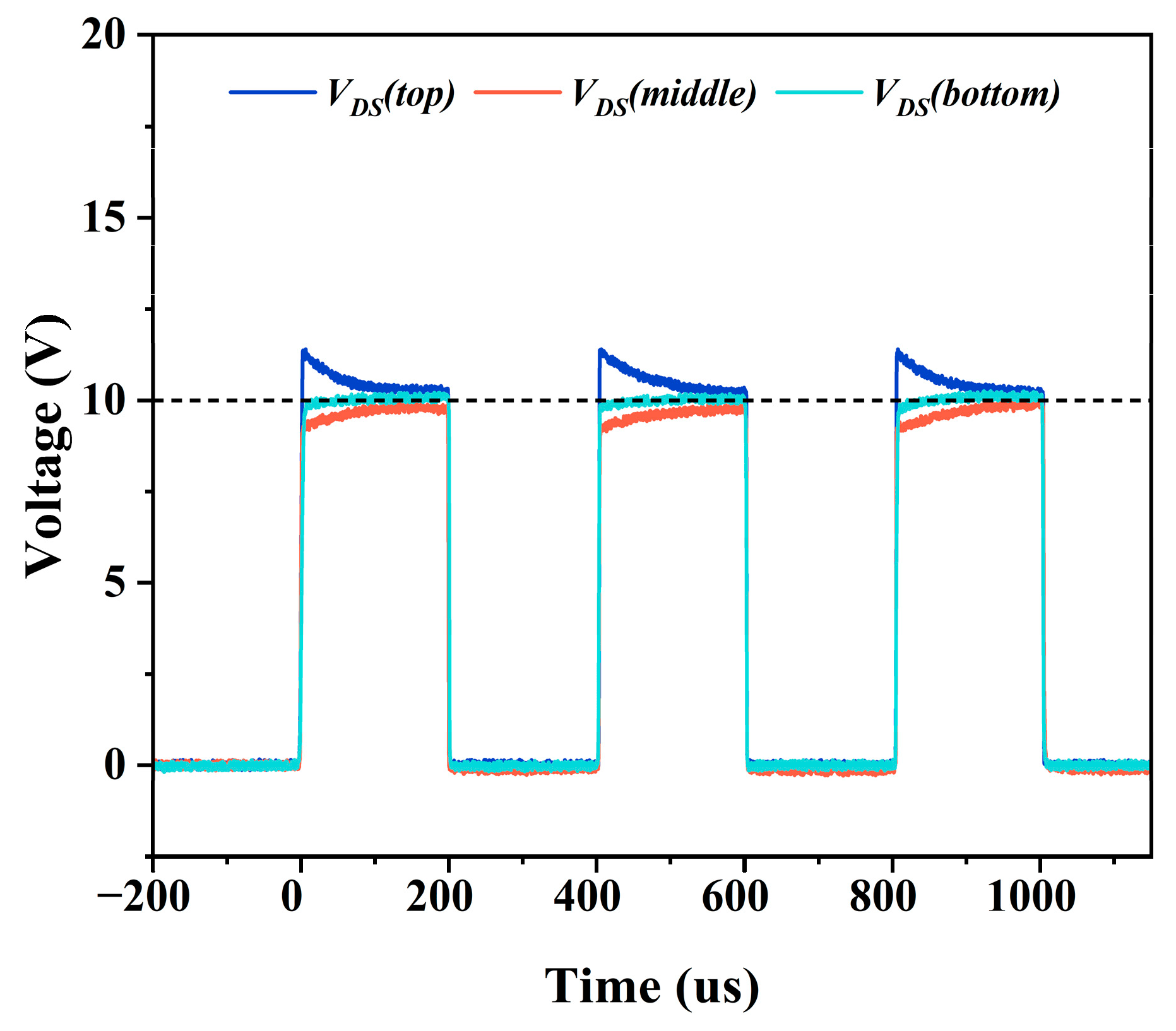

5. Gate-Drain Zener Clamping Circuits

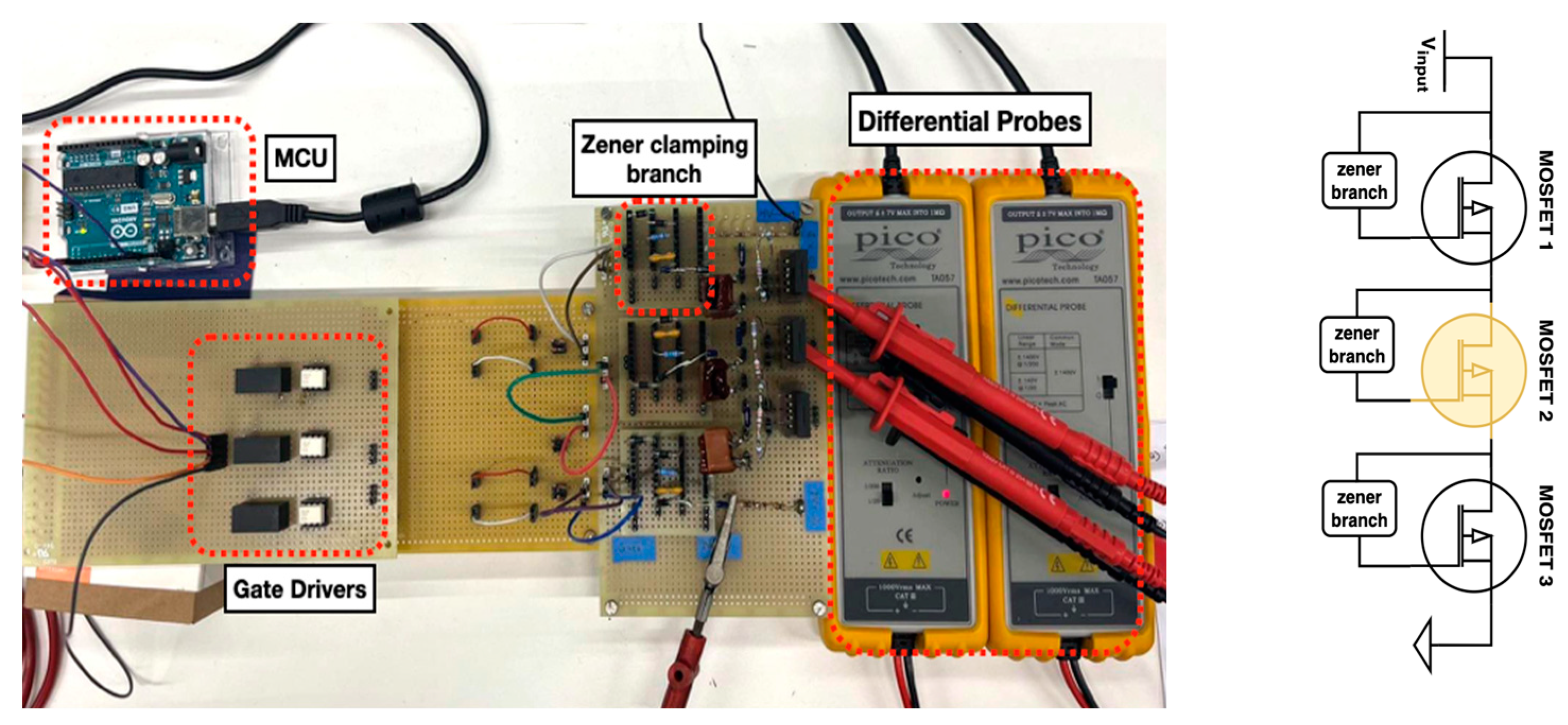

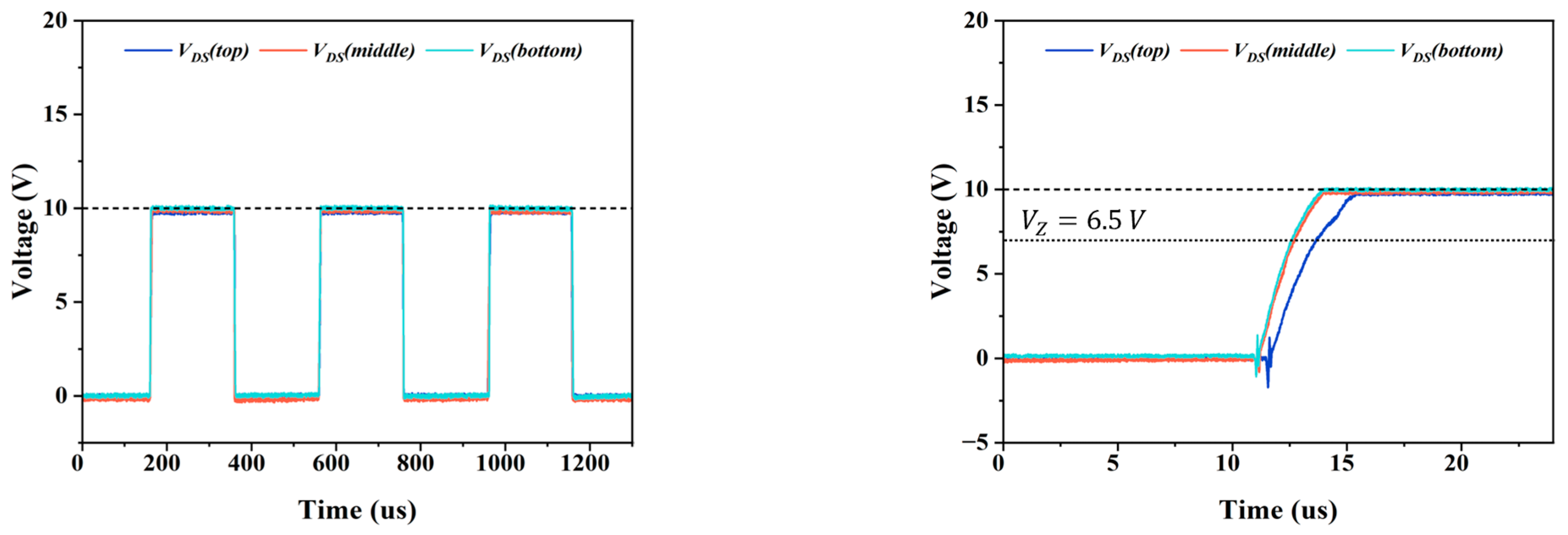

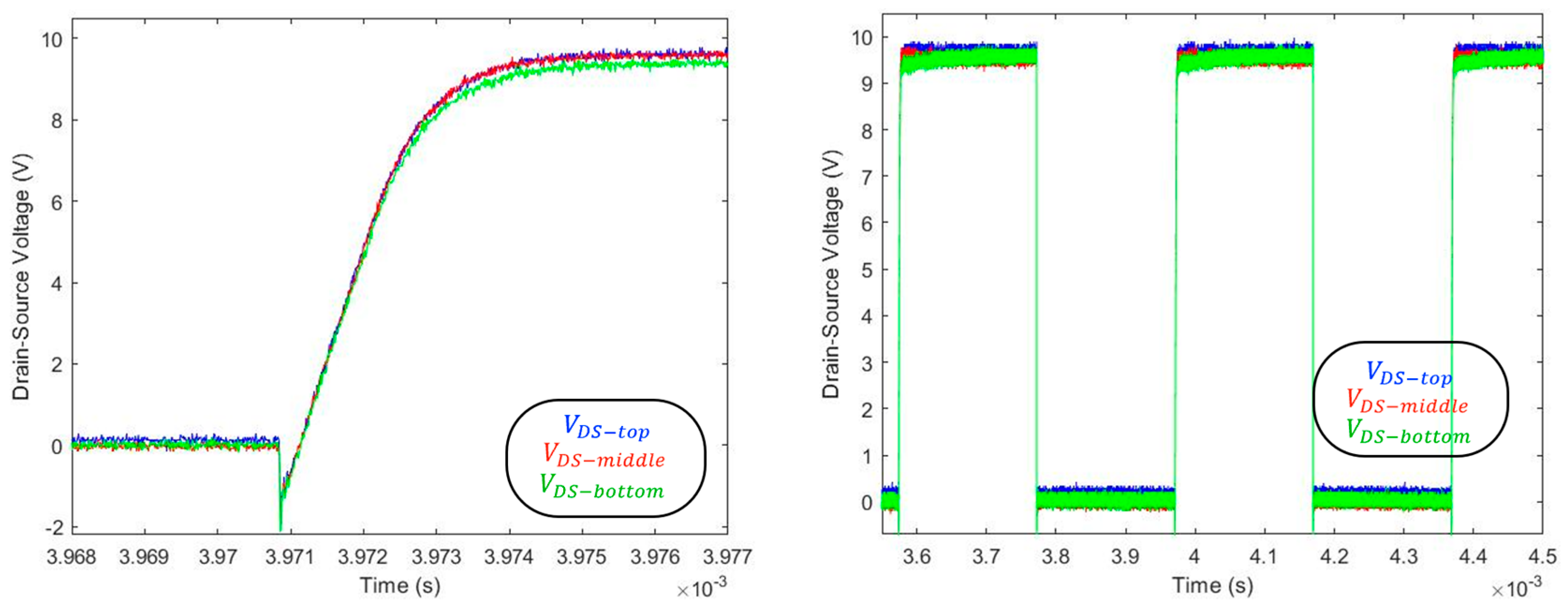

Experiments with the Optimized Zener Clamping Method and Three Series-Connected MOSFETs

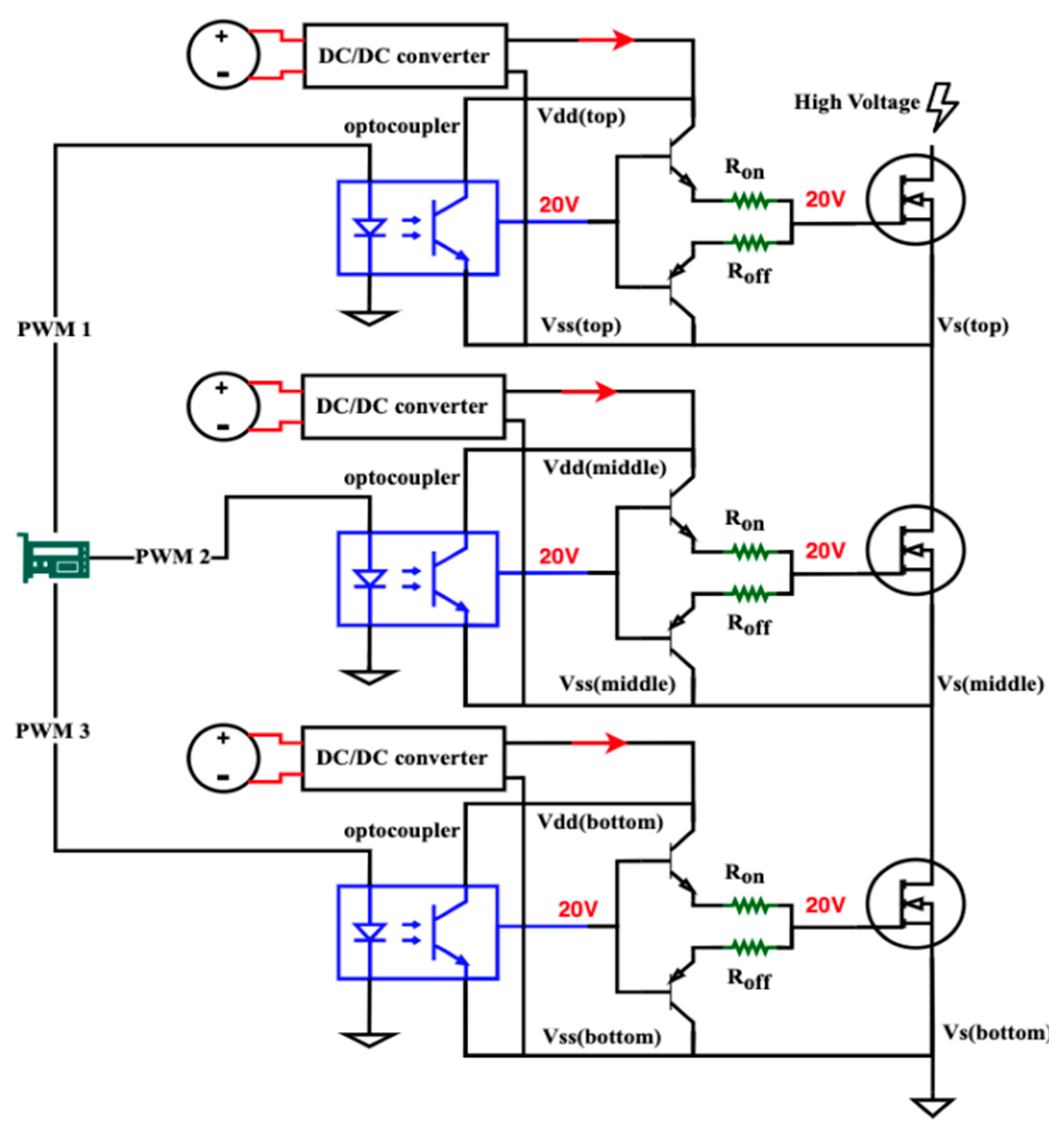

6. Design of Isolated HV Gate Drivers

7. A Magnetically Isolated HV Gate Driver

LTspice Simulations of the Magnetically Isolated HV Gate Driver

8. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Abbreviations

| GBC | Gate-balancing core |

| HF | High frequency |

| HV | High voltage |

| IC | Integrated circuit |

| IGBT | Insulated-gate bipolar transistor |

| MMC | Modular multilevel converter |

| MOSFET | Metal–oxide–semiconductor field-effect transistor |

| MV | Medium voltage |

| PE | Power electronic |

| PWM | Pulse-width modulation |

| Si | Silicon |

| SiC | Silicon carbide |

| SST | Solid-state transformer |

References

- Ganeshpure, D.A.; Soundararajan, A.P.; Soeiro, T.B.; Niasar, M.G.; Vaessen, P.; Bauer, P. Comparison of Pulse Current Capability of Different Switches for Modular Multilevel Converter-based Arbitrary Wave shape Generator used for Dielectric Testing of High Voltage Grid Assets. In Proceedings of the 2022 24th European Conference on Power Electronics and Applications (EPE’22 ECCE Europe), Hanover, Germany, 5–9 September 2022; pp. 1–11. [Google Scholar]

- Ganeshpure, D.A.; Soeiro, T.B.; Niasar, M.G.; Vaessen, P.; Bauer, P. Modular Multilevel Converter-based Arbitrary Wave shape Generator used for High Voltage Testing. In Proceedings of the 2021 IEEE 19th International Power Electronics and Motion Control Conference (PEMC), Gliwice, Poland, 25–29 April 2021; pp. 124–131. [Google Scholar]

- Rothmund, D.; Guillod, T.; Bortis, D.; Kolar, J.W. 99.1% Efficient 10 kV SiC-Based Medium-Voltage ZVS Bidirectional Single-Phase PFC AC/DC Stage. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 7, 779–797. [Google Scholar] [CrossRef]

- Rothmund, D.; Guillod, T.; Bortis, D.; Kolar, J.W. 99% Efficient 10 kV SiC-Based 7 kV/400 V DC Transformer for Future Data Centers. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 7, 753–767. [Google Scholar]

- Callanan, R.J.; Agarwal, A.; Burk, A.; Das, M.; Hull, B.; Husna, F.; Powell, A.; Richmond, J.; Ryu, S.H.; Zhang, Q. Recent progress in SiC DMOSFETs and JBS diodes at Cree. In Proceedings of the 2008 34th Annual Conference of IEEE Industrial Electronics, Orlando, FL, USA, 10–13 November 2008; pp. 2885–2890. [Google Scholar]

- Fukuda, K.; Okamoto, D.; Okamoto, M.; Deguchi, T.; Mizushima, T.; Takenaka, K.; Fujisawa, H.; Harada, S.; Tanaka, Y.; Yonezawa, Y.; et al. Development of Ultrahigh-Voltage SiC Devices. IEEE Trans. Electron Devices 2015, 62, 396–404. [Google Scholar] [CrossRef]

- Koseki, K.; Yonezawa, Y.; Mizushima, T.; Matsunaga, S.; Iizuka, Y.; Yamaguchi, H. Dynamic Behavior of a Medium-Voltage N-Channel SiC-IGBT with Ultrafast Switching Performance of 300 kV/μs. IEEE Trans. Ind. Appl. 2018, 54, 3558–3565. [Google Scholar] [CrossRef]

- Berning, D.W.; Duong, T.H.; Ortiz-Rodriguez, J.M.; Rivera-Lopez, A.; Hefner, A.R., Jr. High-Voltage Isolated Gate Drive Circuit for 10 kV, 100 A SiC MOSFET/JBS Power Modules. In Proceedings of the 2008 IEEE Industry Applications Society Annual Meeting, Edmonton, AB, Canada, 5–9 October 2008; pp. 1–7. [Google Scholar]

- Schuderer, J.; Vemulapati, U.; Traub, F. Packaging SiC power semiconductors—Challenges, technologies and strategies. In Proceedings of the 2014 IEEE Workshop on Wide Bandgap Power Devices and Applications, Knoxville, TN, USA, 13–15 October 2014; pp. 18–23. [Google Scholar]

- Casady, J.B.; Pala, V.; Lichtenwalner, D.J.; Van Brunt, E.; Hull, B.; Wang, G.Y.; Richmond, J.; Allen, S.T.; Grider, D.; Palmour, J.W. New Generation 10 kV SiC Power MOSFET and Diodes for Industrial Applications. In Proceedings of the PCIM Europe 2015; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremberg, Germany, 19–21 May 2015; pp. 1–8. [Google Scholar]

- Lemmon, A.N.; Graves, R. Gate drive development and empirical analysis of 10 kV SiC MOSFET modules. In Proceedings of the 2015 IEEE 3rd Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Blacksburg, VA, USA, 2–4 November 2015; pp. 108–112. [Google Scholar]

- Srdic, S.; Liang, X.; Zhang, C.; Yu, W.; Lukic, S. A SiC-based high-performance medium-voltage fast charger for plug-in electric vehicles. In Proceedings of the 2016 IEEE Energy Conversion Congress and Exposition (ECCE), Milwaukee, WI, USA, 18–22 September 2016; pp. 1–6. [Google Scholar]

- Sarlioglu, B.; Morris, C.T. More Electric Aircraft: Review, Challenges, and Opportunities for Commercial Transport Aircraft. IEEE Trans. Transp. Electrif. 2015, 1, 54–64. [Google Scholar] [CrossRef]

- Cano, T.C.; Castro, I.; Rodriguez, A.; Lamar, D.G.; Khalil, Y.F.; Albiol-Tendillo, L.; Kshirsagar, P. Future of Electrical Aircraft Energy Power Systems: An Architecture Review. IEEE Trans. Transp. Electrif. 2021, 7, 1915–1929. [Google Scholar] [CrossRef]

- Ghassemi, M.; Barzkar, A.; Saghafi, M. All-Electric NASA N3-X Aircraft Electric Power Systems. IEEE Trans. Transp. Electrif. 2022, 8, 4091–4104. [Google Scholar] [CrossRef]

- Schefer, H.; Fauth, L.; Kopp, T.H.; Mallwitz, R.; Friebe, J.; Kurrat, M. Discussion on Electric Power Supply Systems for All Electric Aircraft. IEEE Access 2020, 8, 84188–84216. [Google Scholar] [CrossRef]

- Buticchi, G.; Bozhko, S.; Liserre, M.; Wheeler, P.; Al-Haddad, K. On-Board Microgrids for the More Electric Aircraft—Technology Review. IEEE Trans. Ind. Electron. 2018, 66, 5588–5599. [Google Scholar] [CrossRef]

- Tessarolo, A.; Castellan, S.; Menis, R.; Sulligoi, G. Electric generation technologies for all-electric ships with Medium-Voltage DC power distribution systems. In Proceedings of the IEEE Electric Ship Technologies Symposium, Arlington, VA, USA, 22–24 April 2013; pp. 275–281. [Google Scholar]

- Yang, C.; Pei, Y.; Xu, Y.; Zhang, F.; Wang, L.; Zhu, M.; Yu, L. A Gate Drive Circuit and Dynamic Voltage Balancing Control Method Suitable for Series-Connected SiC MOSFETs. IEEE Trans. Power Electron. 2019, 35, 6625–6635. [Google Scholar] [CrossRef]

- Pala, V.; Brunt, E.V.; Cheng, L.; O’Loughlin, M.; Richmond, J.; Burk, A.; Allen, S.T.; Grider, D.; Palmour, J.W.; Scozzie, C.J. 10 kV and 15 kV silicon carbide power MOSFETs for next-generation energy conversion and transmission systems. In Proceedings of the IEEE Energy Conversion Congress and Exposition (ECCE), Pittsburgh, PA, USA, 14–18 September 2014; pp. 449–454. [Google Scholar] [CrossRef]

- Tripathi, A.; Mainali, K.; Madhusoodhanan, S.; Yadav, A.; Vechalapu, K.; Bhattacharya, S. A MV intelligent gate driver for 15 kV SiC IGBT and 10 kV SiC MOSFET. In Proceedings of the 2016 IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 20–24 March 2016; pp. 2076–2082. [Google Scholar]

- GeneSiC Semiconductor, G2R1000MT33J, Silicon Carbide MOSFET N-Channel Enhancement Mode, Jun. 2021. Available online: https://genesicsemi.com/sic-mosfet/G2R1000MT33J/G2R1000MT33J.pdf (accessed on 15 November 2023).

- Zhang, F.; Yang, X.; Chen, W.; Wang, L. Voltage Balancing Control of Series-Connected MOSFETs by Using Energy Recovery Snubber Circuits. IEEE Trans. Power Electron. 2020, 35, 10200–10212. [Google Scholar] [CrossRef]

- Barkhordarian, V. Power MOSFET Basics. Powerconvers. Intell. Motion-Engl. Ed. 1997, 22, 2–8. [Google Scholar]

- STMicroelectronics, STGAP2SICSN, Galvanically Isolated 4 A Single Gate Driver for SiC MOSFETs, Sep. 2022. Available online: https://www.st.com/en/power-management/stgap2sics.html (accessed on 15 November 2023).

- Littelfuse, IXDD630MCI, 30-Ampere Low-Side Ultrafast MOSFET Drivers, May 2017. Available online: https://www.littelfuse.com/media?resourcetype=datasheets&itemid=9a089c7d-2853-4c70-bbb7-8823051f821a&filename=ixd-630 (accessed on 15 November 2023).

- ON Semiconductor. Fod3182, 3A Output Current, High Speed MOSFET Gate Driver Optocoupler; Onsemi: Phoenix, AZ, USA, 2020. [Google Scholar]

- Marzoughi, A.; Burgos, R.; Boroyevich, D. Active Gate-Driver with dv/dt Controller for Dynamic Voltage Balancing in Series-Connected SiC MOSFETs. IEEE Trans. Ind. Electron. 2018, 66, 2488–2498. [Google Scholar] [CrossRef]

- Yue, L.; Lee, I.; Yao, X. A Review of Voltage Sharing Control Methods for Series-connected IGBTs for Applications in Pulsed Power Generation. In Proceedings of the 2018 IEEE International Power Modulator and High Voltage Conference (IPMHVC), Jackson, WY, USA, 3–7 June 2018; pp. 397–402. [Google Scholar]

- Zorngiebel, V.; Spahn, E.; Buderer, G.; Welleman, A.; Fleischmann, W. Compact High Voltage IGBT Switch for Pulsed Power Applications. IEEE Trans. Magn. 2009, 45, 531–535. [Google Scholar] [CrossRef]

- Pawaskar, V.U.; Gohil, G.; Balsara, P.T. Study of Voltage Balancing Techniques for Series-Connected Insulated Gate Power Devices. IEEE J. Emerg. Sel. Top. Power Electron. 2021, 10, 2380–2394. [Google Scholar] [CrossRef]

- Sasagawa, K.; Abe, Y.; Matsuse, K. Voltage balancing method for IGBTs connected in series. In Proceedings of the 2002 IEEE Industry Applications Conference. 37th IAS Annual Meeting, Pittsburgh, PA, USA, 13–18 October 2002; Volume 4, pp. 2597–2602. [Google Scholar] [CrossRef]

- Chen, S.; Li, C.; Lu, Z.; Luo, H.; Li, W.; He, X. A Coupled Inductor Based Circuit for Voltage Balancing among Series Connected SiC MOSFETs. In Proceedings of the 2020 IEEE Applied Power Electronics Conference and Exposition (APEC), New Orleans, LA, USA, 15–19 March 2020; pp. 2588–2593. [Google Scholar]

- Withanage, R.; Shammas, N. Series Connection of Insulated Gate Bipolar Transistors (IGBTs). IEEE Trans. Power Electron. 2012, 27, 2204–2212. [Google Scholar] [CrossRef]

- Sasagawa, K.; Abe, Y.; Matsuse, K. Voltage-balancing method for IGBTs connected in series. IEEE Trans. Ind. Appl. 2004, 40, 1025–1030. [Google Scholar] [CrossRef]

- Yu, G.; Niasar, M.G.; Ganeshpure, D.; Soeiro, T.B.; Bauer, P. A Transformer Isolated Driving Method for SiC MOSFETs with a Constant Negative Off Voltage. In Proceedings of the 2021 IEEE 19th International Power Electronics and Motion Control Conference (PEMC), Gliwice, Poland, 25–29 April 2021; pp. 39–45. [Google Scholar]

- Baraia, I.; Barrena, J.A.; Abad, G.; Segade, J.M.C.; Iraola, U. An Experimentally Verified Active Gate Control Method for the Series Connection of IGBT/Diodes. IEEE Trans. Power Electron. 2011, 27, 1025–1038. [Google Scholar] [CrossRef]

- Zhang, F.; Yang, X.; Ren, Y.; Feng, L.; Chen, W.; Pei, Y. A Hybrid Active Gate Drive for Switching Loss Reduction and Voltage Balancing of Series-Connected IGBTs. IEEE Trans. Power Electron. 2016, 32, 7469–7481. [Google Scholar] [CrossRef]

- Li, C.; Chen, S.; Luo, H.; Li, C.; Li, W.G.; He, X. A Modified RC Snubber with Coupled Inductor for Active Voltage Balancing of Series-Connected SiC MOSFETs. IEEE Trans. Power Electron. 2021, 36, 11208–11220. [Google Scholar] [CrossRef]

- Bruckmann, M.; Sommer, R.; Fasching, M.; Sigg, J. Series connection of high voltage IGBT modules. In Proceedings of the 1998 IEEE Industry Applications Conference. Thirty-Third IAS Annual Meeting, St. Loius, MO, USA, 12–15 October 1998; Volume 2, pp. 1067–1072. [Google Scholar]

- Withanage, R.; Crookes, W.; Shammas, N. Novel voltage balancing technique for series connection of IGBTs. In Proceedings of the 2007 European Conference on Power Electronics and Applications, Aalborg, Denmark, 2–5 September 2007; pp. 1–10. [Google Scholar]

- Infineon, IMW120R220M1H, CoolSiCTM 1200V SiC Trench MOSFET Silicon Carbide MOSFET, Dec. 2020. Available online: https://www.infineon.com/dgdl/Infineon-IMW120R220M1H-DataSheet-v02_00-EN.pdf?fileId=5546d46269e1c019016a92fe078366a0 (accessed on 9 February 2024).

- CREE, C3M0280090D, Silicon Carbide Power MOSFET, C3MTM MOSFET Technology, Jan. 2024. Available online: https://assets.wolfspeed.com/uploads/2024/01/Wolfspeed_C3M0280090D_data_sheet.pdf (accessed on 9 February 2024).

- Saiz, J.; Mermet, M.; Frey, D.; Jeannin, P.; Schanen, J.; Muszicki, P. Optimisation and integration of an active clamping circuit for IGBT series association. In Proceedings of the 2001 IEEE Industry Applications Society 36th Annual Meeting-IAS’01, Chicago, IL, USA, 30 September–4 October 2001. [Google Scholar]

- Bai, H.; Zhao, Z.; Eltawil, M.; Yuan, L. Optimization Design of High-Voltage-Balancing Circuit Based on the Functional Model of IGCT. IEEE Trans. Ind. Electron. 2007, 54, 3012–3021. [Google Scholar] [CrossRef]

- Yu, G.; Niasar, M.G. Design and Prototyping of Auxiliary Power Supply for MMC Based High Voltage Generator. Master’s Thesis, Delft University of Technology, Delft, The Netherlands, August 2020. [Google Scholar]

- Ghafoor, S.; Kulkarni, M.; Mirzdarani, R.; Vaessen, P.T.M.; Niasar, M.G. A Scalable Isolated Gate Driver with Programmable Duty Cycle for Series-Connected SiC MOSFETs. IEEE Open J. Power Electron, under review.

- Anthony, P.; McNeill, N.; Holliday, D.; Grant, D.; Hearn, G. A magnetically isolated gate driver for high-speed voltage sharing in series-connected MOSFETs. In Proceedings of the 2011 14th European Conference on Power Electronics and Applications, Birmingham, UK, 30 August–1 September 2022; pp. 1–10. [Google Scholar]

- Xu, W.; Huang, A.Q. 15 kV/50 A SiC AC Switch Based On Series Connection of 1.7 kV MOSFETs. In Proceedings of the 2022 IEEE Energy Conversion Congress and Exposition (ECCE), Detroit, MI, USA, 9–13 October 2022; pp. 1–6. [Google Scholar]

| SiC MOSFET | Datasheet | Measurement | ||||

|---|---|---|---|---|---|---|

| IMW120R220M1H | 5.0 ns | 10.0 ns | 6.8 ns | ±2.0 ns | 12.8 ns | ±2.4 ns |

| C3M0280090D | 5.3 ns | 8.5 ns | 7.7 ns | ±2.3 ns | 11.6 ns | ±1.6 ns |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhao, W.; Ghafoor, S.; Lagerweij, G.W.; Rietveld, G.; Vaessen, P.; Niasar, M.G. Comprehensive Investigation of Promising Techniques to Enhance the Voltage Sharing among SiC MOSFET Strings, Supported by Experimental and Simulation Validations. Electronics 2024, 13, 1481. https://doi.org/10.3390/electronics13081481

Zhao W, Ghafoor S, Lagerweij GW, Rietveld G, Vaessen P, Niasar MG. Comprehensive Investigation of Promising Techniques to Enhance the Voltage Sharing among SiC MOSFET Strings, Supported by Experimental and Simulation Validations. Electronics. 2024; 13(8):1481. https://doi.org/10.3390/electronics13081481

Chicago/Turabian StyleZhao, Weichuan, Sohrab Ghafoor, Gijs Willem Lagerweij, Gert Rietveld, Peter Vaessen, and Mohamad Ghaffarian Niasar. 2024. "Comprehensive Investigation of Promising Techniques to Enhance the Voltage Sharing among SiC MOSFET Strings, Supported by Experimental and Simulation Validations" Electronics 13, no. 8: 1481. https://doi.org/10.3390/electronics13081481

APA StyleZhao, W., Ghafoor, S., Lagerweij, G. W., Rietveld, G., Vaessen, P., & Niasar, M. G. (2024). Comprehensive Investigation of Promising Techniques to Enhance the Voltage Sharing among SiC MOSFET Strings, Supported by Experimental and Simulation Validations. Electronics, 13(8), 1481. https://doi.org/10.3390/electronics13081481