Design Techniques for Wideband CMOS Power Amplifiers for Wireless Communications

Abstract

:1. Introduction

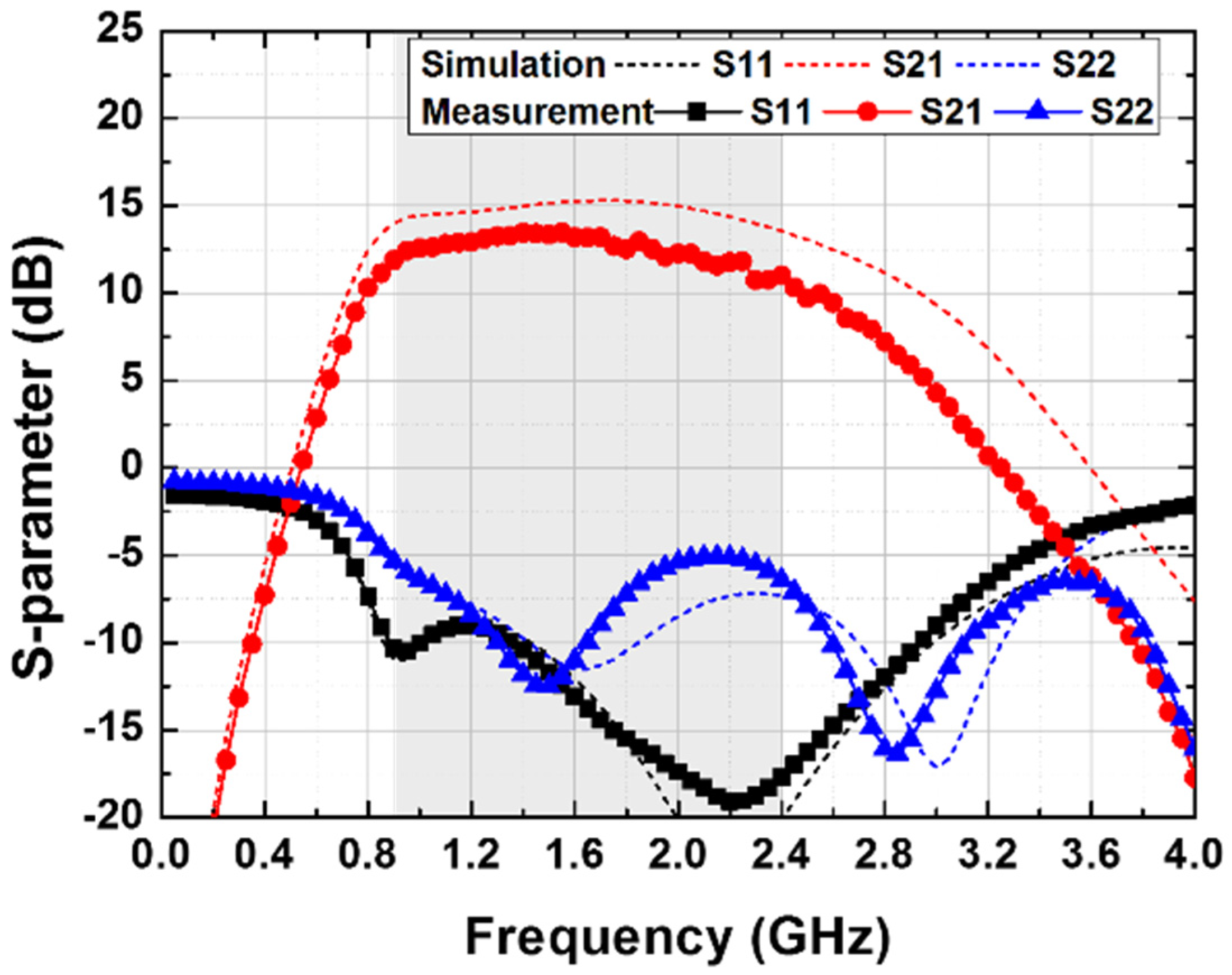

2. Design of the Wideband Input Matching Network

3. Design of the Wideband Output Matching Network

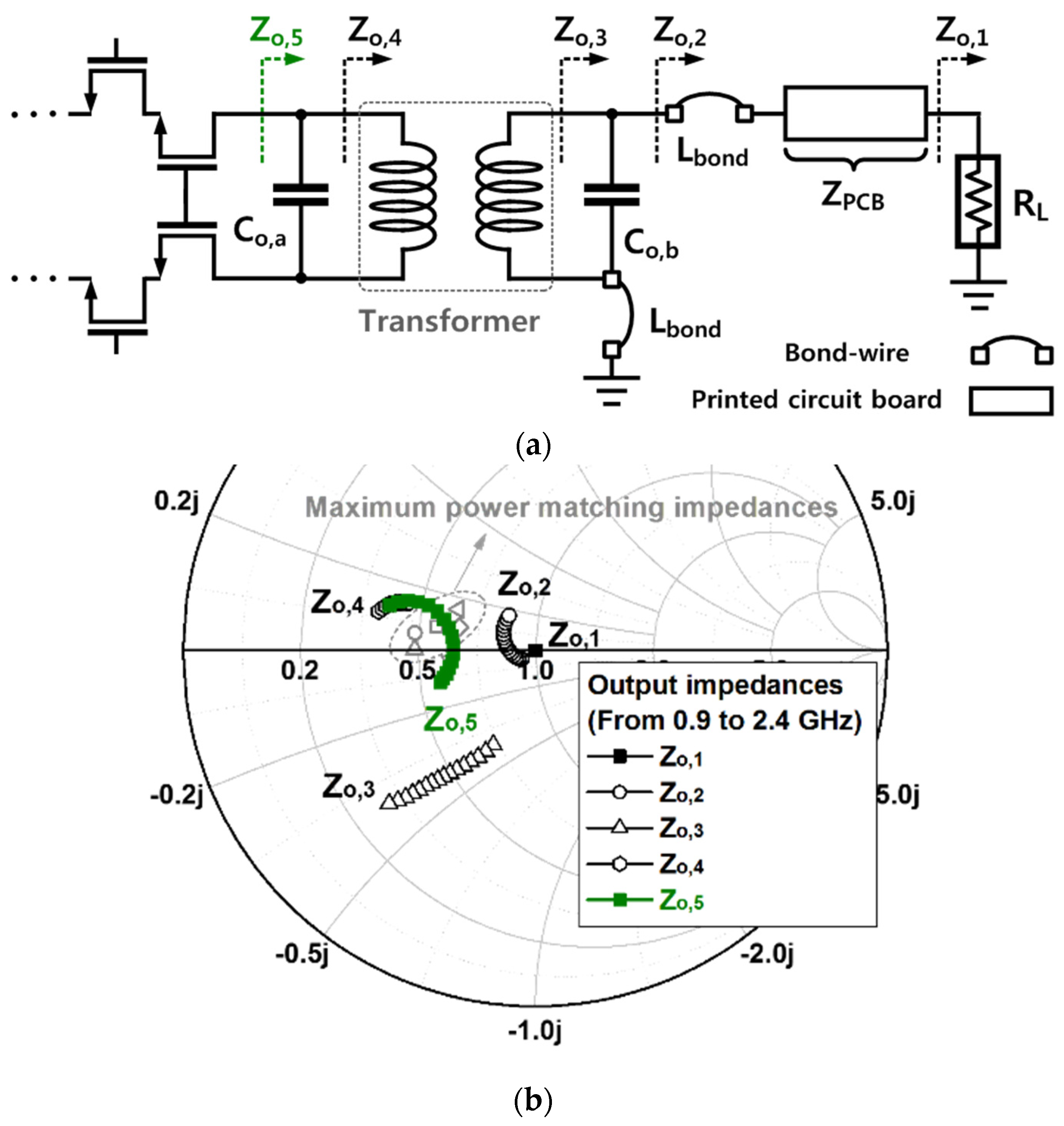

3.1. Design of the Wideband Power Matching Network

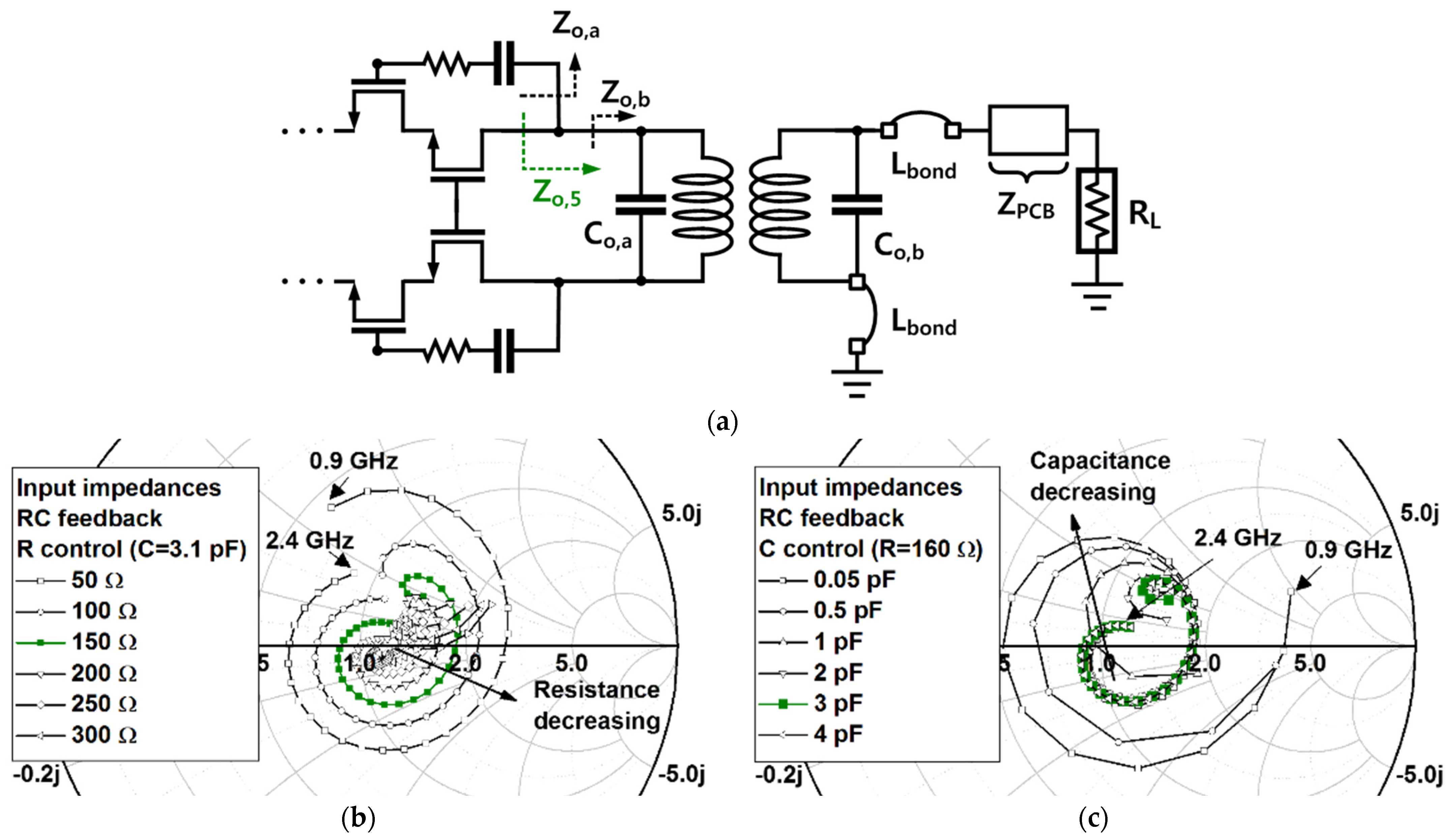

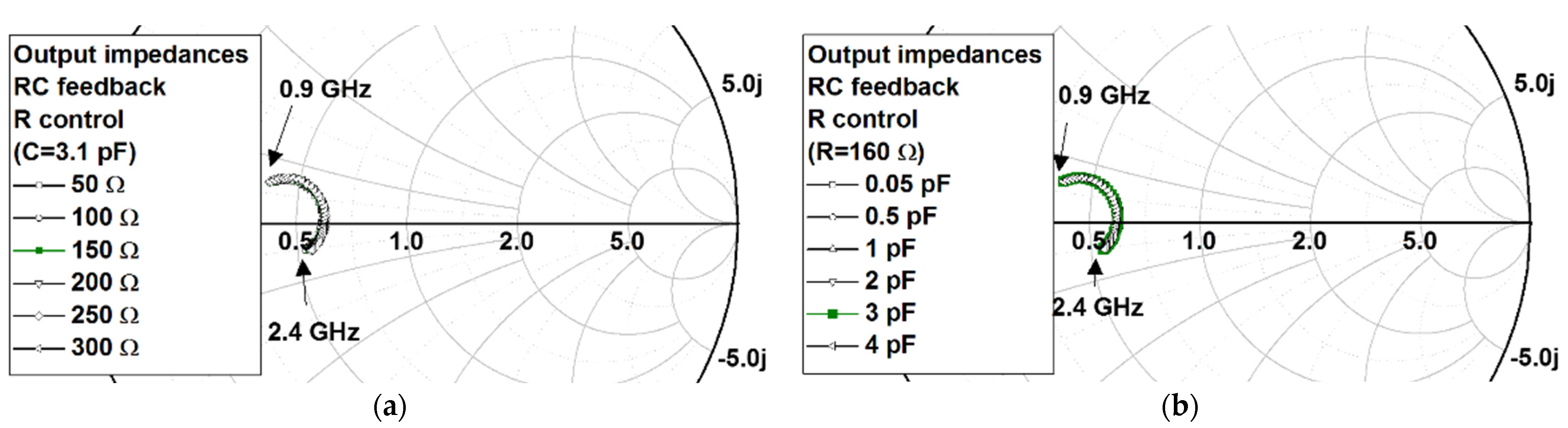

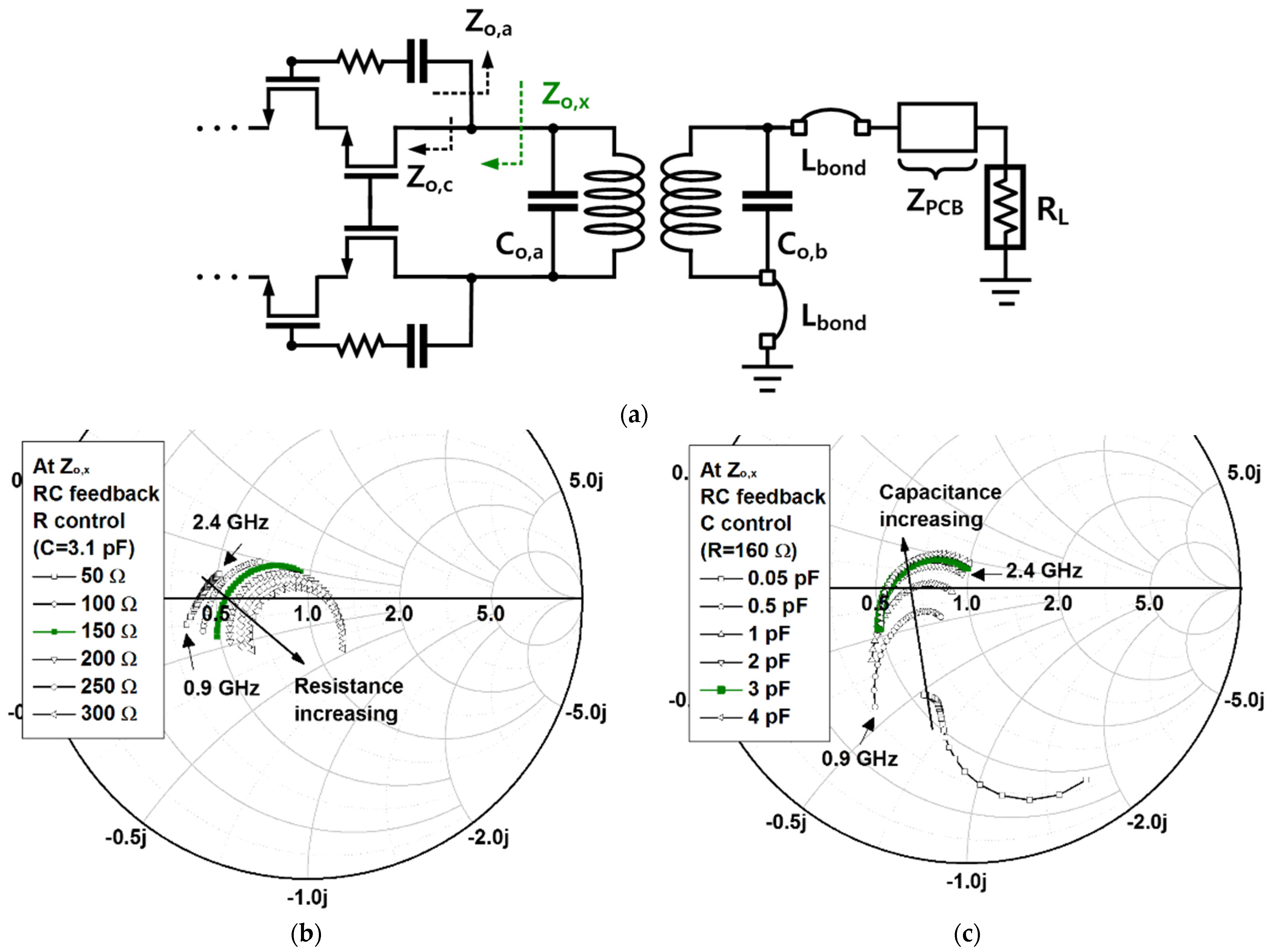

3.2. Design of the Wideband Conjugate Matching Network

4. Design Results of the Proposed CMOS Power Amplifier

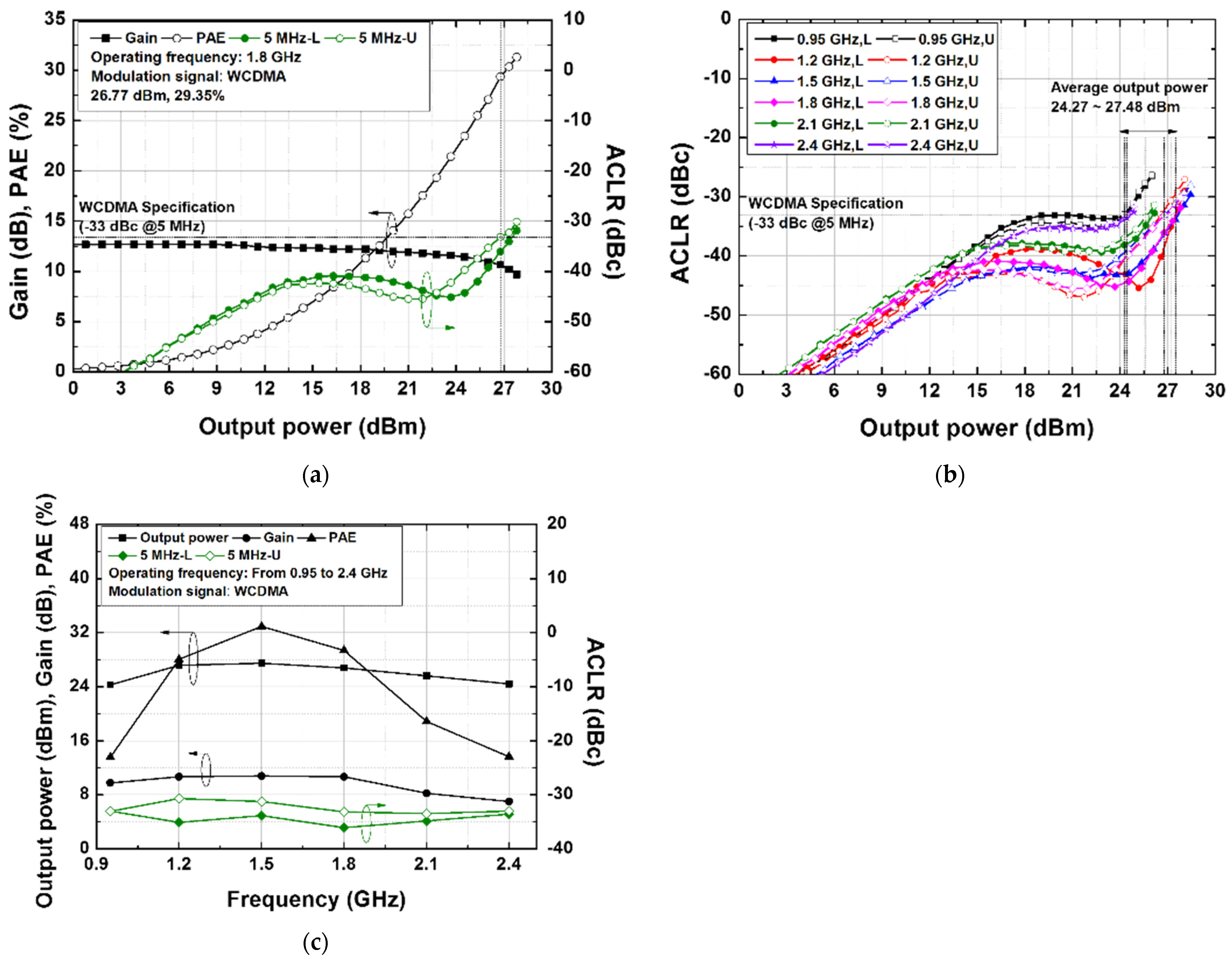

4.1. Measurement Results with WCDMA Modulated Signal

4.2. Measurement Results with LTE Modulated Signal

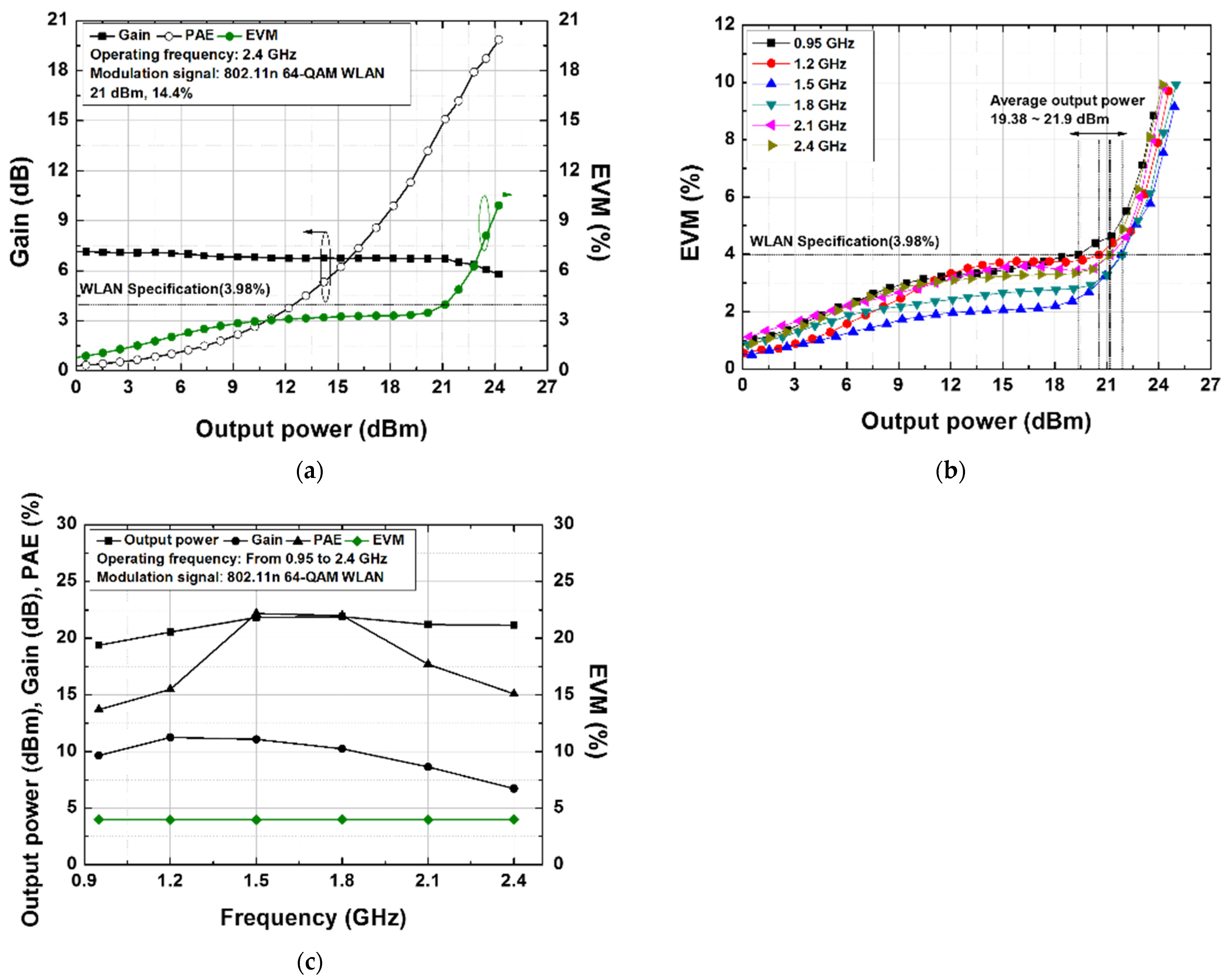

4.3. Measurement Results with a WLAN Modulated Signal

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Zhang, Y.; Mueller, J.H.; Mohr, B.; Liao, L.; Atac, A.; Wunderlich, R.; Heinen, S. A Multi-Frequency Multi-Standard Wideband Fractional-N PLL with Adaptive Phase-Noise Cancellation for Low-Power Short-Range Standards. IEEE Trans. Microw. Theory Tech. 2016, 64, 1133–1142. [Google Scholar] [CrossRef]

- Fehri, B.; Boumaiza, S.; Sich, E. Crest Factor Reduction of Inter-Band Multi-Standard Carrier Aggregated Signals. IEEE Trans. Microw. Theory Tech. 2014, 62, 3286–3297. [Google Scholar] [CrossRef]

- Jain, S.; Jang, S.-L.; Tchamov, N.T. Tuned LC-Resonator Dual-Band VCO. IEEE Microw. Wirel. Compon. Lett. 2016, 26, 204–206. [Google Scholar] [CrossRef]

- Xie, C.; Wu, P.; Tan, C.; Yuan, Y.; Zeng, J.; Yu, Z. An X/Ku Dual-Band Switchless Frequency Reconfigurable GaAs Power Amplifier. IEEE Microw. Wirel. Compon. Lett. 2022, 32, 539–542. [Google Scholar] [CrossRef]

- Lee, W.; Hong, S. Frequency-Reconfigurable SP4T Switch with Plaid Metal Transistors and Forward Body Biasing for Enhanced RON × COFF Characteristics. IEEE Trans. Circuits Syst. II Express Briefs 2022, 69, 399–403. [Google Scholar] [CrossRef]

- Kanchetla, V.K.; Kharalkar, A.; Jain, S.; Khyalia, S.K.; Joy, J.; Jose, S.; Zele, R. A Compact, Reconfigurable CMOS RF Receiver for NavIC/GPS/Galileo/BeiDou. IEEE Trans. Microw. Theory Tech. 2022, 70, 3361–3373. [Google Scholar] [CrossRef]

- Ko, B.; Lee, S.; Seo, W.; Sim, T.; Kim, S.; Kim, M.-S.; Kim, J. A 39/48 GHz Switchless Reconfigurable Low Noise Amplifier Using Common Gate and Coupled-Line-Based Diplexer. IEEE Trans. Circuits Syst. II Express Briefs 2023, 70, 4028–4032. [Google Scholar] [CrossRef]

- Wang, Z.; Wang, X.; Liu, Y. A Wideband Power Amplifier in 65 nm CMOS Covering 25.8 GHz–36.9 GHz by Staggering Tuned MCRs. Electronics 2023, 12, 3566. [Google Scholar] [CrossRef]

- Mauludin, M.F.; Lee, D.-H.; Kim, J. A Wideband Low-Power Balun-LNA with Feedback and Current Reuse Technique. Electronics 2022, 11, 1372. [Google Scholar] [CrossRef]

- Mahmood, H.U.; Utomo, D.R.; Han, S.-K.; Kim, J.; Lee, S.-G. A Ku-Band RF Front-End Employing Broadband Impedance Matching with 3.5 dB NF and 21 dB Conversion Gain in 45-nm CMOS Technology. Electronics 2020, 9, 539. [Google Scholar] [CrossRef]

- Lee, M.; Park, C. A Triple-Band CMOS Power Amplifier Using Multi-Band and Switchable Matching Network for Wireless Mobile. IEEE Trans. Microw. Theory Tech. 2019, 67, 4220–4231. [Google Scholar] [CrossRef]

- Kim, J. A Wideband Triple-Stacked CMOS Distributed Power Amplifier Using Double Inductive Peaking. IEEE Microw. Wirel. Compon. Lett. 2019, 29, 787–790. [Google Scholar] [CrossRef]

- Alizadeh, A.; Medi, A. Distributed Class-J Power Amplifiers. IEEE Trans. Microw. Theory Tech. 2017, 65, 513–521. [Google Scholar] [CrossRef]

- Chirala, M.K.; Guan, X.; Nguyen, C. Integrated Multilayered On-Chip Inductors for Compact CMOS RFICs and Their Use in a Miniature Distributed Low-Noise-Amplifier Design for Ultra-Wideband Applications. IEEE Trans. Microw. Theory Tech. 2008, 56, 1783–1789. [Google Scholar] [CrossRef]

- Kilinc, S.; Yarman, B.S.; Ozoguz, S. Broadband Power Amplifier Design via Fictitious Matching. IEEE Trans. Circuits Syst. II Express Briefs 2022, 69, 4844–4848. [Google Scholar] [CrossRef]

- Kim, M.-S.; Jhon, H. A Broadband Gain Amplifier Designed with the Models for Package and Diode Using 0.5 μm GaAs E-pHEMT Process. Electronics 2021, 10, 2678. [Google Scholar] [CrossRef]

- Zhai, C.; Liu, H.-Y.; Cheng, K.-K.M. Single-Chip CMOS Reconfigurable Dual-Band Tri-Mode High-Efficiency RF Amplifier Design. IEEE Trans. Circuits Syst. II Express Briefs 2021, 68, 868–872. [Google Scholar] [CrossRef]

- Kang, L.; Chen, W.; Wu, A. A Reconfigurable S-/X-Band GaN MMIC Power Amplifier. IEEE Microw. Wirel. Compon. Lett. 2022, 32, 547–550. [Google Scholar] [CrossRef]

- Aggrawal, E.; Rawat, K. Reconfigurable Chireix Outphasing Power Amplifier Over Multiple Frequency Bands. IEEE Trans. Circuits Syst. II Express Briefs 2020, 67, 1019–1023. [Google Scholar] [CrossRef]

- Su, G.; Sun, L.; Wen, J.; Wang, H.; Yu, Z.; Zhang, N. An estimable stability method applied to power amplifier design. In Proceedings of the 2011 IEEE Electrical Design of Advanced Packaging and Systems Symposium (EDAPS), Hanzhou, China, 12–14 December 2011; pp. 1–4. [Google Scholar] [CrossRef]

- Rasmi, A.; Marzuki, A.; Ismail, M.A.; Rahim, A.I.A.; Yahya, M.R.; Mat, A.F.A. 0.5 µm GaAs PHEMT medium power amplifier design using simple RC feedback amplifier for wireless LAN applications. In Proceedings of the 2008 Asia-Pacific Microwave Conference, Hong Kong, China, 16–20 December 2008; pp. 1–4. [Google Scholar] [CrossRef]

- Kim, B.; Lee, D.-H.; Hong, S.; Park, M. A multi-band CMOS power amplifier using reconfigurable adaptive power cell technique. IEEE Microw. Wirel. Compon. Lett. 2016, 26, 616–618. [Google Scholar] [CrossRef]

- Kim, K.; Ko, J.; Lee, S.; Nam, S. A two-stage broadband fully integrated CMOS linear power amplifier for LTE applications. IEEE Trans. Circuits Syst. II Express Briefs 2016, 63, 533–537. [Google Scholar] [CrossRef]

- Park, J.; Lee, C.; Park, C. A quad-band CMOS linear power amplifier for EDGE applications using an anti-phase method to enhance its linearity. IEEE Trans. Circuits Syst. I Regul. Pap. 2017, 64, 765–776. [Google Scholar] [CrossRef]

- Lee, M.-L.; Liou, C.-Y.; Tsai, W.-T.; Lou, C.-Y.; Hsu, H.-L.; Mao, S.-G. Fully monolithic BiCMOS reconfigurable power amplifier for multi-mode and multi-band applications. IEEE Trans. Microw. Theory Tech. 2015, 63, 614–624. [Google Scholar] [CrossRef]

| Device | Value | Device | Value | Device | Value |

|---|---|---|---|---|---|

| CP | 2.8 pF | Lbond | 0.5 nH | ZPCB | 44.2–45.9 Ω |

| Co,a | 6.5 pF | Rb | 2.0 kΩ | Common source TR | 180/8/16/30 (1) |

| Co,b | 2.0 pF | RF | 150 Ω | Common gate TR | 350/8/16/36 (1) |

| LA | 0.4 nH | CF | 3 pF | - | - |

| Ref. | Tech. (nm) | Freq. (GHz) | Plinear (dBm) | PAE (%) | Modulation Signal | Size (mm2) | Configuration |

|---|---|---|---|---|---|---|---|

| [22] | 40 | 0.65 | 18.2 | - | 802.11n 64 QAM, 20 MHz, 2% | 1.98 × 1.61 | Single PA |

| 0.88 | 18.4 | - | |||||

| [23] | 110 | 1.8–2.3 | 27.3 | 26.1–33 | LTE 16 QAM, 10 MHz, −30 dBc | 2.52 × 0.9 | Single PA |

| [24] | 110 | 0.9 | 26.2 | 19.4 | EDGE, −54 dBc@400 KHz | 3 × 3 (package) | Multiple PAs |

| 1.9 | 26.7 | 25.6 | |||||

| 26 | 25 | WCDMA, 3.84 MHz, −33 dBc | |||||

| [25] | 180 | 1.95 | 25.6 | - | WCDMA, 3.84 MHz, −33 dBc | 1 × 2.6 | Single PA |

| 2.45 | 20.2 | - | 802.11g 64 QAM, 20 MHz, 3% | ||||

| 2.35 | 24.7 | 19 | LTE 16 QAM, 20 MHz, −33 dBc | ||||

| This Work | 180 | 1.8 | 26.7 | 29.3 | WCDMA, 3.84 MHz, −33 dBc | 1.38 × 0.9 | Single PA |

| 1.8 | 25.0 | 27.7 | LTE 16 QAM, 10 MHz, −30 dBc | ||||

| 1.8 | 23.5 | 21.6 | LTE 16 QAM, 20 MHz, −30 dBc | ||||

| 2.4 | 21.0 | 14.4 | 802.11n 64 QAM, 20 MHz, 3.98% |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lee, M.; Yang, J.; Lee, J.; Park, C. Design Techniques for Wideband CMOS Power Amplifiers for Wireless Communications. Electronics 2024, 13, 1695. https://doi.org/10.3390/electronics13091695

Lee M, Yang J, Lee J, Park C. Design Techniques for Wideband CMOS Power Amplifiers for Wireless Communications. Electronics. 2024; 13(9):1695. https://doi.org/10.3390/electronics13091695

Chicago/Turabian StyleLee, Milim, Junhyuk Yang, Jaeyong Lee, and Changkun Park. 2024. "Design Techniques for Wideband CMOS Power Amplifiers for Wireless Communications" Electronics 13, no. 9: 1695. https://doi.org/10.3390/electronics13091695

APA StyleLee, M., Yang, J., Lee, J., & Park, C. (2024). Design Techniques for Wideband CMOS Power Amplifiers for Wireless Communications. Electronics, 13(9), 1695. https://doi.org/10.3390/electronics13091695