Research on Low-Insertion-Loss Packaging Materials for DC-6 GHz Attenuation Chips

Abstract

:1. Introduction

2. Methods

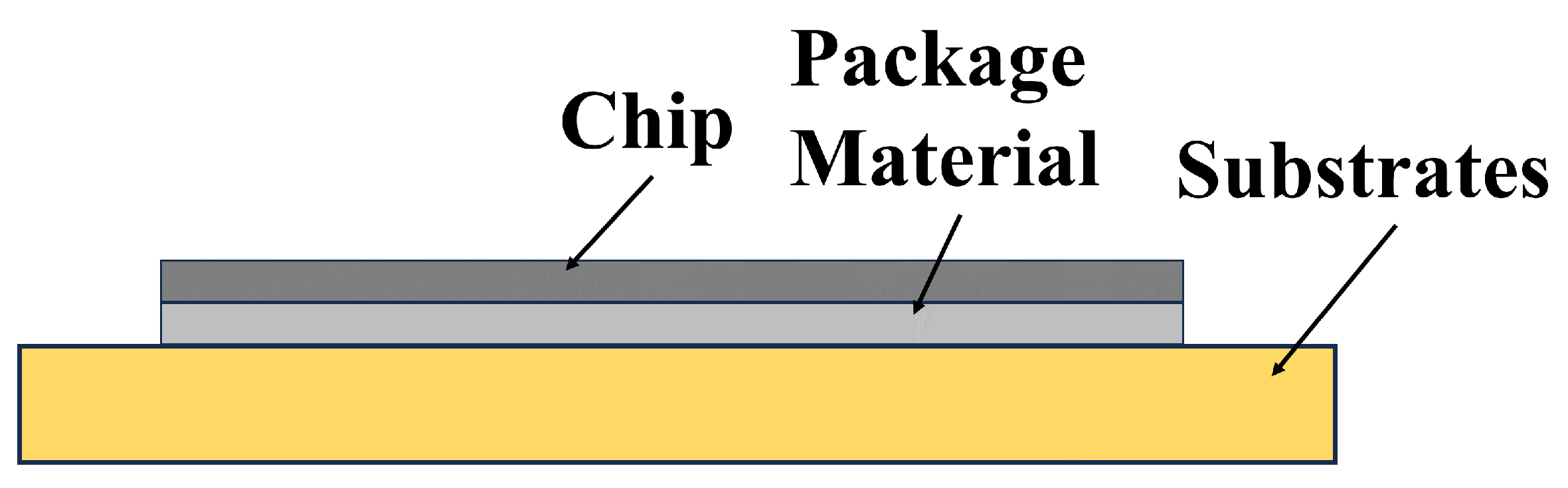

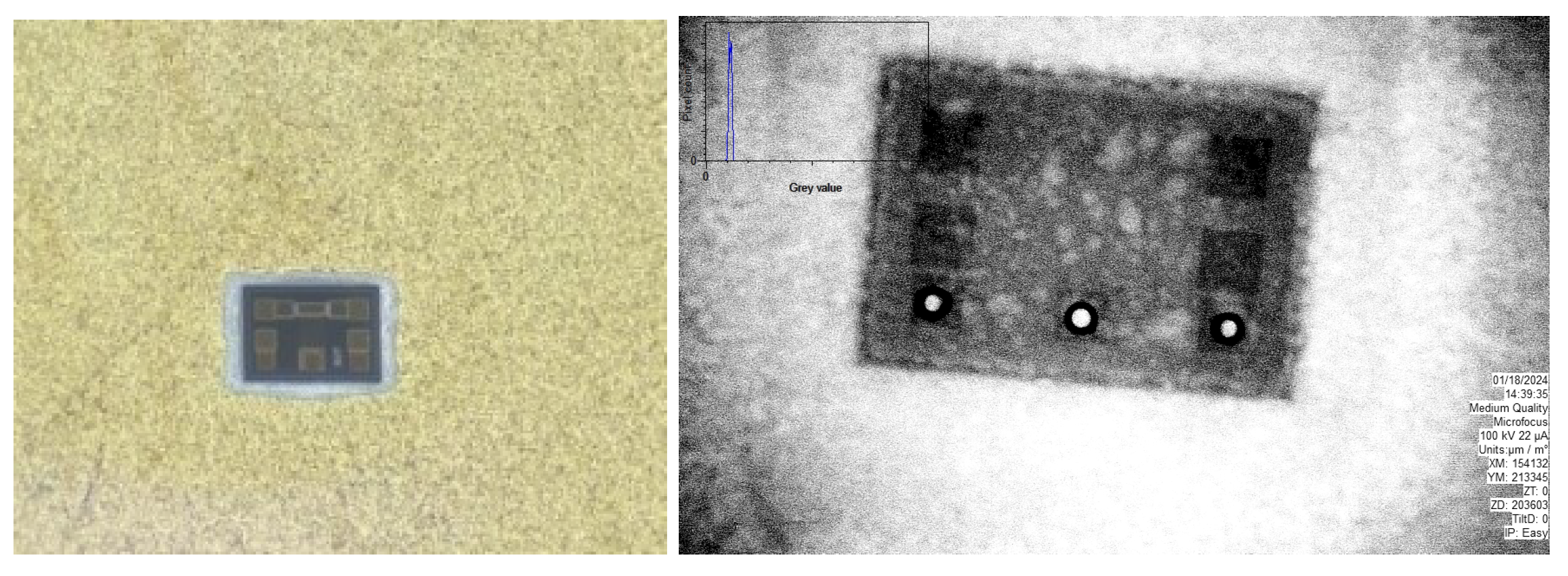

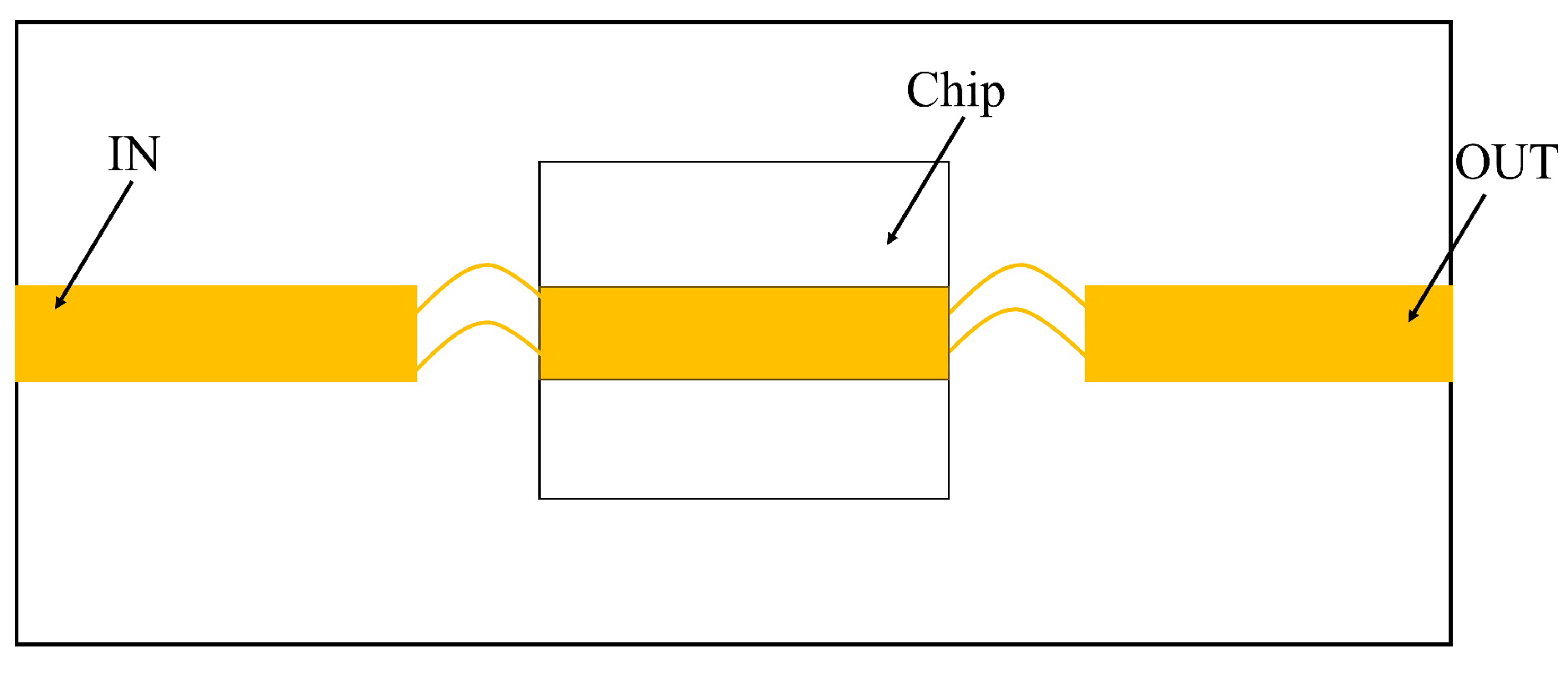

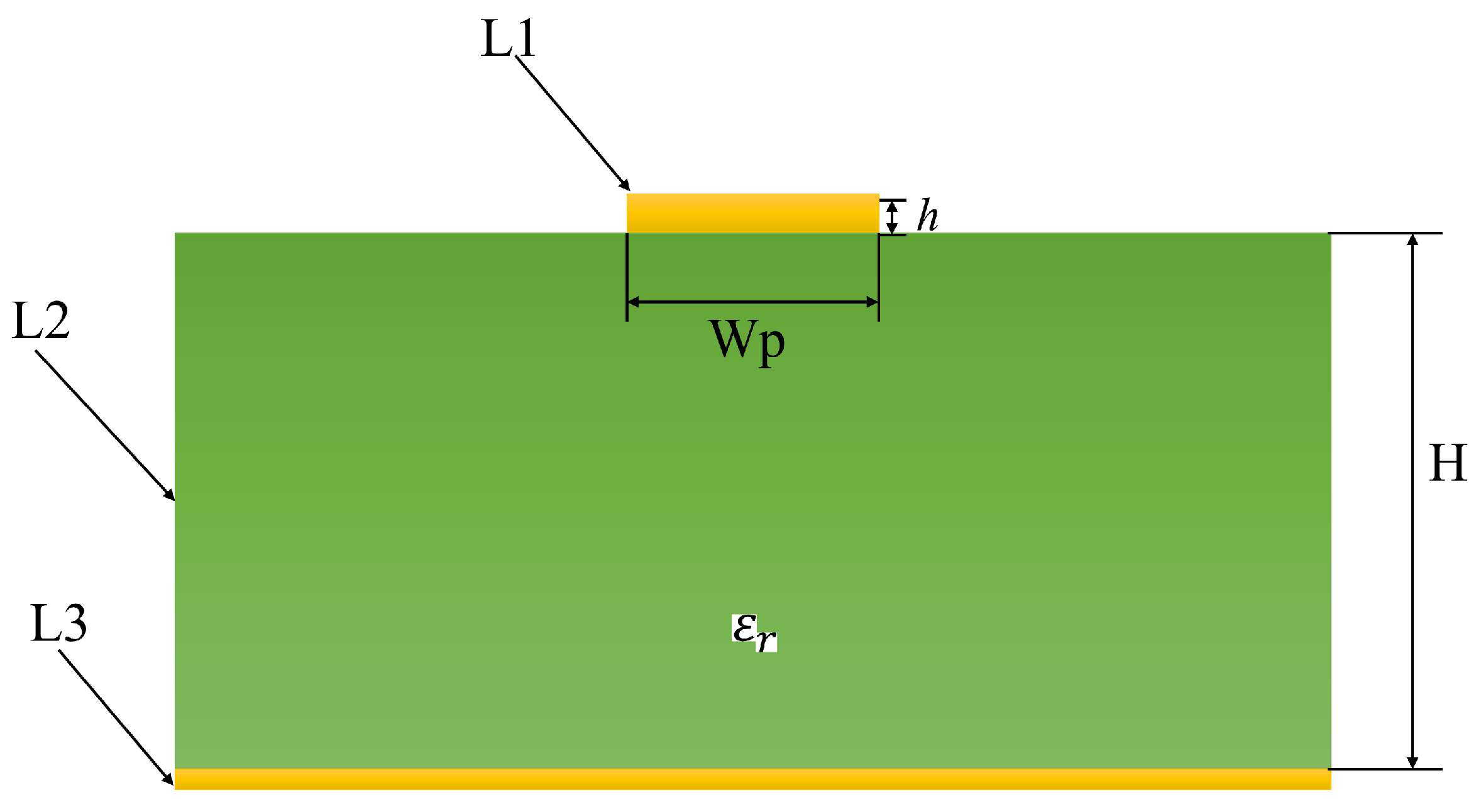

2.1. Experimental Model

2.2. Experimental Model

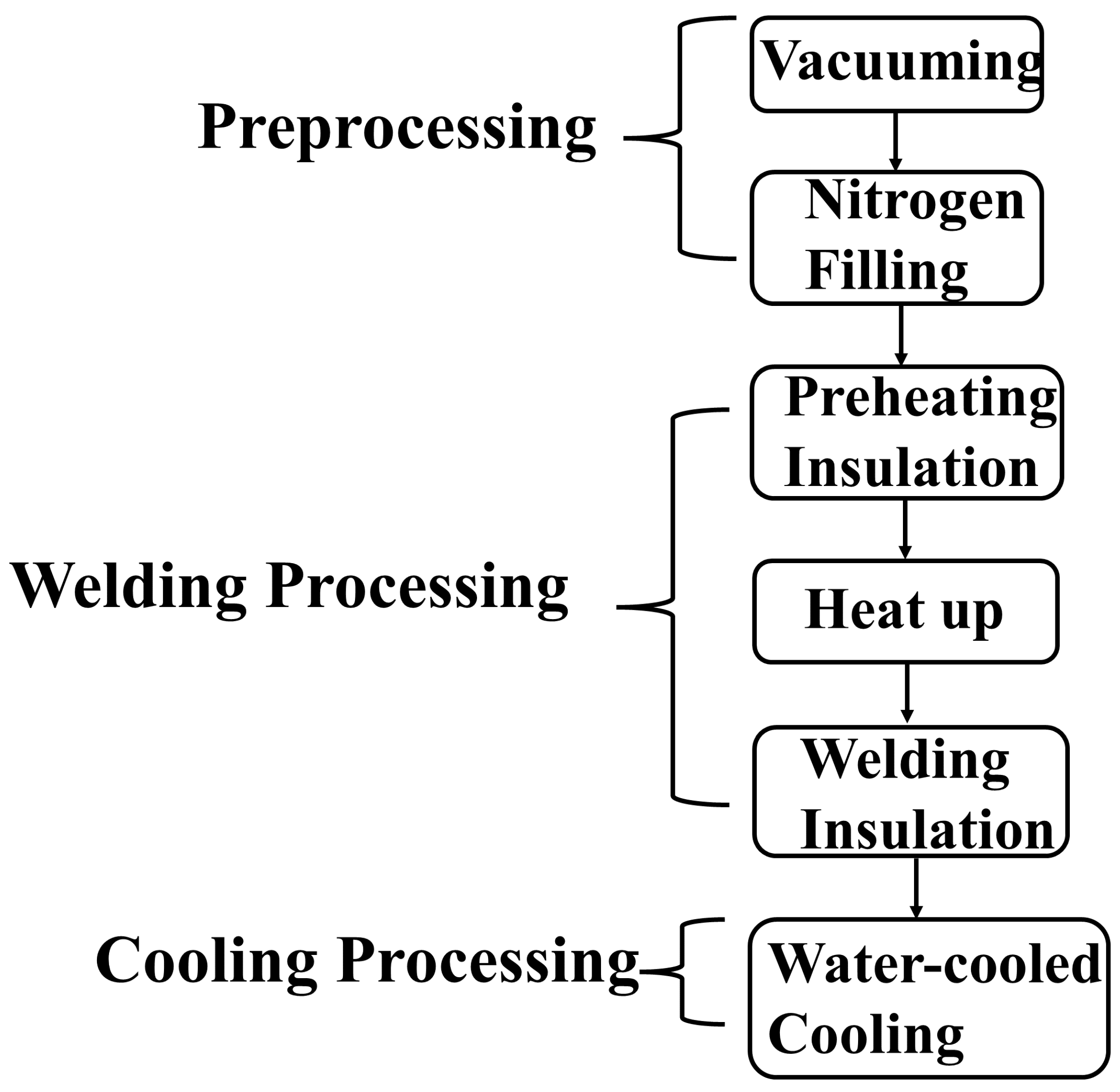

2.3. Nano-Silver Sintering Experiments

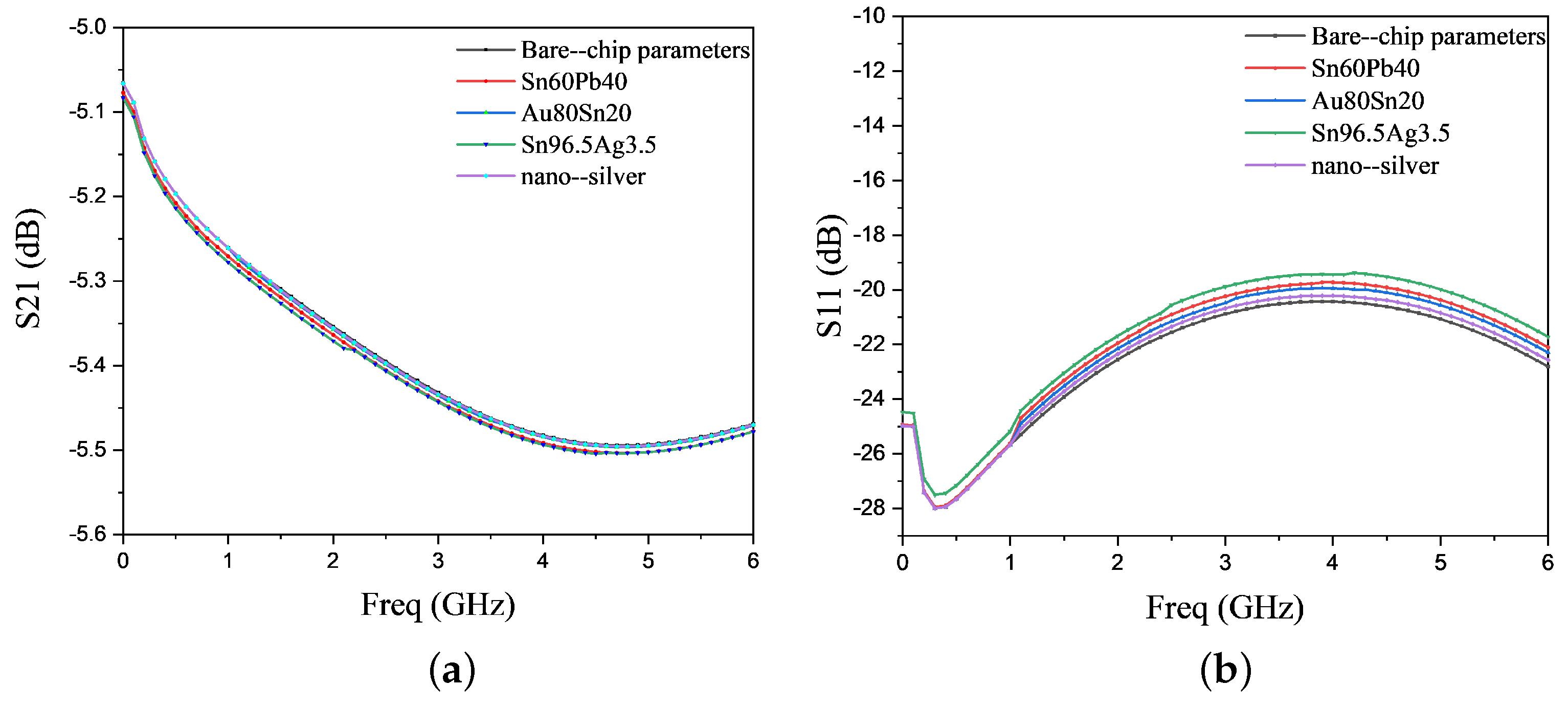

3. Performance Testing and Analysis

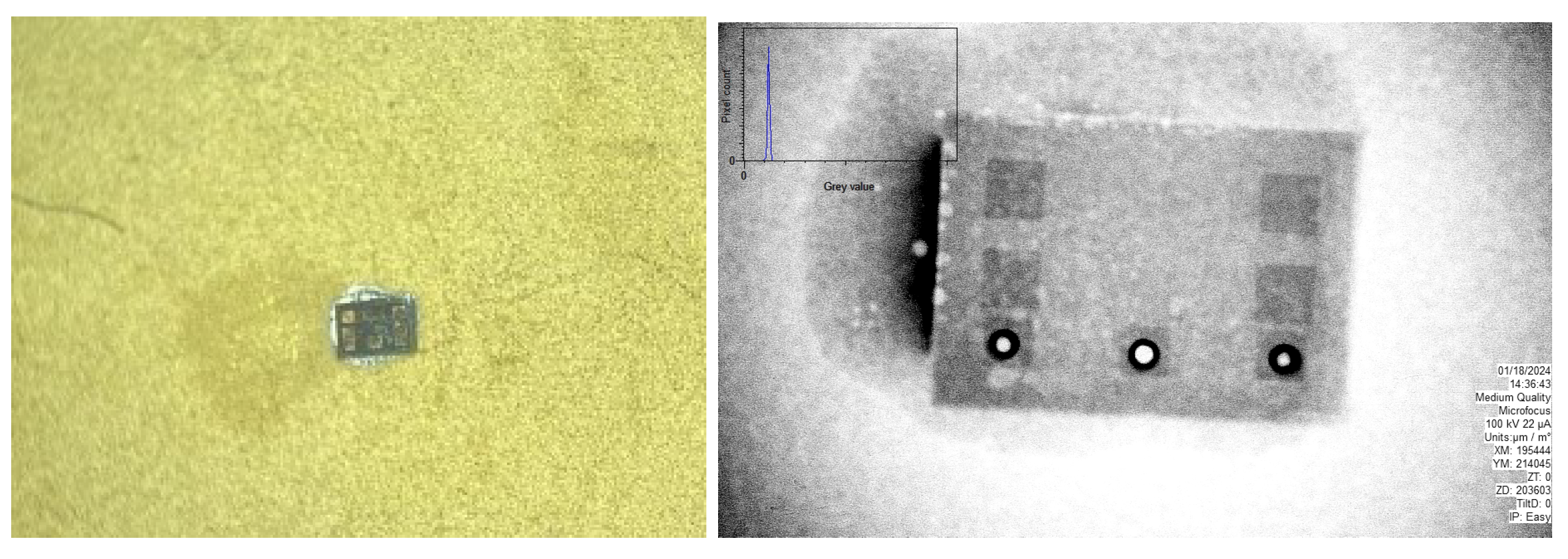

3.1. Performance Testing

3.2. Analysis of Results

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Jung, D.Y.; Jang, H.G.; Cho, D.; Park, K.S.; Lim, J.W.; Choi, Y.H.; Lee, Y. Multi-layer Ceramic Based Surface Mount Device Packaging for 1200 V and 1700 V SiC SBD Power Semiconductors. In Proceedings of the 2020 IEEE International Conference on Consumer Electronics, Las Vegas, NV, USA, 4–6 January 2020; pp. 65–68. [Google Scholar]

- Du, Y.; Qiao, Y.; Ren, X.; Lai, Y.; Zhao, N. Characterization of Sn-xIn Solders and Thermomigration-Induced Interfacial IMC Growth of Cu/Sn-xIn/Cu Micro Solder Joints. Electronics 2023, 12, 1899. [Google Scholar] [CrossRef]

- Luyang, Z. Brief analysis of micro-assembly technology of electronic products. Shandong Ind. Technol. 2015, 6, 191. [Google Scholar]

- Na, C.Y.; Jeon, B.M.; Kim, J.W.; Jung, W.S.; Jeong, J.S.; Cho, S.M.; Park, H.S. Fabrication of 30 µm Sn Microbumps by Electroplating and Investigation of IMC Characteristics on Shear Strength. Electronics 2022, 12, 144. [Google Scholar] [CrossRef]

- Chen, C.; Gong, W.; Qi, J. Research progress on chip assembly reliability and testing methods. Electron. Process. Technol. 2015, 36, 253–256. [Google Scholar]

- Zhou, B.; Lu, T.; You, J. Study on fatigue ductility coefficient and life prediction for mixed solder joints under thermal cycle loads. In Proceedings of the 2014 10th International Conference on Reliability, Maintainability and Safety (ICRMS), Guangzhou, China, 6–8 August 2014; pp. 686–690. [Google Scholar]

- Xiang, L.; Shao, L.; Yan, T. Research on low void welding of semiconductor power module chips. Equip. Manuf. Technol. 2017, 2, 82–85. [Google Scholar]

- Depiver, J.A.; Mallik, S.; Amalu, E.H. Characterizing Solder Materials from Random Vibration Response of Their Interconnects in BGA Packaging. J. Electron. Mater. 2023, 52, 4655–4671. [Google Scholar] [CrossRef]

- Lee, J.R.; Chong, M.X.; Abdul Aziz, M.S.; Khor, C.Y.; Mohd Salleh, M.A.; Mohd Arif Zainol, M.R.; Ani, F.C. Numerical Analysis of the Thermal and Mechanical Performance of Cu Pillar Bumps During Reflow: Effects of Height and Solder Material. J. Electron. Mater. 2024, 53, 1169–1182. [Google Scholar] [CrossRef]

- Craton, M.T.; Konstantinou, X.; Albrecht, J.D.; Chahal, P.; Papapolymerou, J. A Chip-First Microwave Package Using Multimaterial Aerosol Jet Printing. IEEE Trans. Microw. Theory Tech. 2020, 68, 3418–3427. [Google Scholar] [CrossRef]

- Hao, D.; Zhang, W.; Liu, X.; Liu, Y. A Wideband 6-Bit Digital Attenuator in a GaAs pHEMT MMIC. Electronics 2022, 11, 2166. [Google Scholar] [CrossRef]

- Yuan, H.; Yuan, Y.; Zhan, H. Effect and regulation of solder voids on the reliability of power devices. Electron. Packag. 2023, 23, 15–22. [Google Scholar]

- Zhou, Q.; Li, Q.; Zhou, Y. Reliability soldering study of small size Sn63Pb37 and Sn3.0Ag0.5Cu solder balls. Electron. Process. Technol. 2018, 39, 79–83+100. [Google Scholar]

- Jia, Q.; Zou, G.; Zhang, H. Progress of sintered connections with nanoparticle materials as intermediate layers and their encapsulation applications. J. Mech. Eng. 2022, 58, 2–16. [Google Scholar]

- Wang, D.Q. Research and Design of SIW Filter and Duplexer Based on Multimode Technology; Nanjing University of Posts and Telecommunications: Nanjing, China, 2022. [Google Scholar]

- Zuoyong, D. Research on Microwave Functional Module Micro-Assembly Application Technology. Master’s Thesis, Nanjing University of Science and Technology, Nanjing, China, 2014. [Google Scholar]

| Makings | Density (g/cm3) | Coefficient of Thermal Expansion (10−6/°C) | Thermal Conductivity (W/mk) | Young’s Modulus (GPa) | Poisson’s Ratio | Conductivity (1/ohm × m) | Resistivity (ohm × m) |

|---|---|---|---|---|---|---|---|

| GaAs | 5.32 | 5.9 | 46 | 80 | 0.29 | 2 × 10−6 | 10−8 |

| Sn60Pb40 | 8.5 | 25 | 51 | 34.5 | 0.4 | 6.1 × 10−7 | 22.4 × 10−8 |

| Au80Sn20 | 14.7 | 16 | 57 | 68 | 0.41 | 4.5 × 10−7 | 16.4 × 10−8 |

| Sn96.5Ag3.5 | 7.4 | 30 | 33 | 118.7 | 0.38 | 4.7 × 10−7 | 21.3 × 10−8 |

| nano-silver | - | 22 | 150 | 18 | - | 6.62 × 10−7 | 5 × 10−8 |

| Mo85Cu15 | 10 | 4.8 | 160 | 110 | 0.34 | 5.71 × 10−7 | 1.72 × 10−8 |

| Serial Number | T (°C) | CT (S) | V (Pa) | F (g) | N2 |

|---|---|---|---|---|---|

| 1 | 50 | 20 | 90,000 | 50 | 0 |

| 2 | 50 | 60 | 10 | 50 | 0 |

| 3 | 150 | 240 | 80,000 | 50 | 1 |

| 4 | 150 | 120 | 80,000 | 50 | 1 |

| 5 | 200 | 210 | 80,000 | 50 | 1 |

| 6 | 200 | 60 | 80,000 | 50 | 1 |

| 7 | 220 | 30 | 30 | 50 | 0 |

| 8 | 50 | 150 | 100,000 | 50 | 1 |

| Serial Number | T (°C) | CT (S) | V (Pa) | F (g) | N2 |

|---|---|---|---|---|---|

| 1 | 50 | 20 | 90,000 | 50 | 0 |

| 2 | 50 | 60 | 10 | 50 | 0 |

| 3 | 180 | 240 | 80,000 | 50 | 1 |

| 4 | 180 | 120 | 80,000 | 50 | 1 |

| 5 | 300 | 210 | 80,000 | 50 | 1 |

| 6 | 300 | 60 | 80,000 | 50 | 1 |

| 7 | 320 | 45 | 30 | 50 | 0 |

| 8 | 50 | 150 | 100,000 | 50 | 1 |

| Serial Number | T (°C) | CT (S) | V (Pa) | F (g) | N2 |

|---|---|---|---|---|---|

| 1 | 50 | 20 | 90,000 | 50 | 0 |

| 2 | 50 | 60 | 10 | 50 | 0 |

| 3 | 140 | 240 | 80,000 | 50 | 1 |

| 4 | 140 | 120 | 80,000 | 50 | 1 |

| 5 | 220 | 210 | 80,000 | 50 | 1 |

| 6 | 220 | 60 | 80,000 | 50 | 1 |

| 7 | 240 | 30 | 30 | 50 | 0 |

| 8 | 50 | 150 | 100,000 | 50 | 1 |

| Parameters | Material Properties | Sizes (mm) |

|---|---|---|

| L1 | Nickel-Plated Copper Plating | - |

| L2 | Core RO4003C | - |

| L3 | Core | - |

| Wp | - | 0.414 |

| H | - | 0.412 |

| h | - | 0.203 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wei, Z.; Yu, S.; Wei, P. Research on Low-Insertion-Loss Packaging Materials for DC-6 GHz Attenuation Chips. Electronics 2024, 13, 1785. https://doi.org/10.3390/electronics13091785

Wei Z, Yu S, Wei P. Research on Low-Insertion-Loss Packaging Materials for DC-6 GHz Attenuation Chips. Electronics. 2024; 13(9):1785. https://doi.org/10.3390/electronics13091785

Chicago/Turabian StyleWei, Zhijie, Shenglin Yu, and Pengcheng Wei. 2024. "Research on Low-Insertion-Loss Packaging Materials for DC-6 GHz Attenuation Chips" Electronics 13, no. 9: 1785. https://doi.org/10.3390/electronics13091785

APA StyleWei, Z., Yu, S., & Wei, P. (2024). Research on Low-Insertion-Loss Packaging Materials for DC-6 GHz Attenuation Chips. Electronics, 13(9), 1785. https://doi.org/10.3390/electronics13091785