Design Strategies for BCAT Structures: Enhancing DRAM Reliability and Mitigating Row Hammer Effect

Abstract

1. Introduction

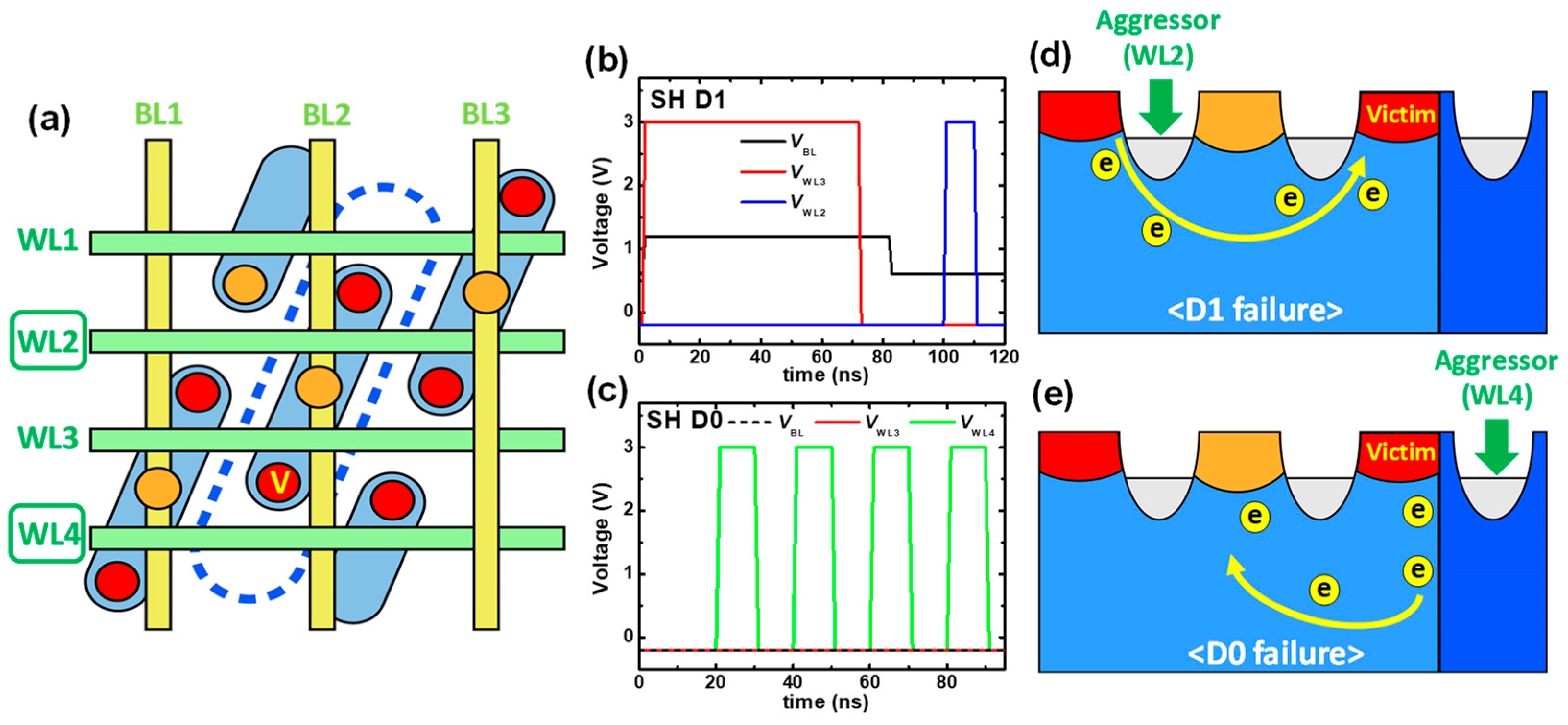

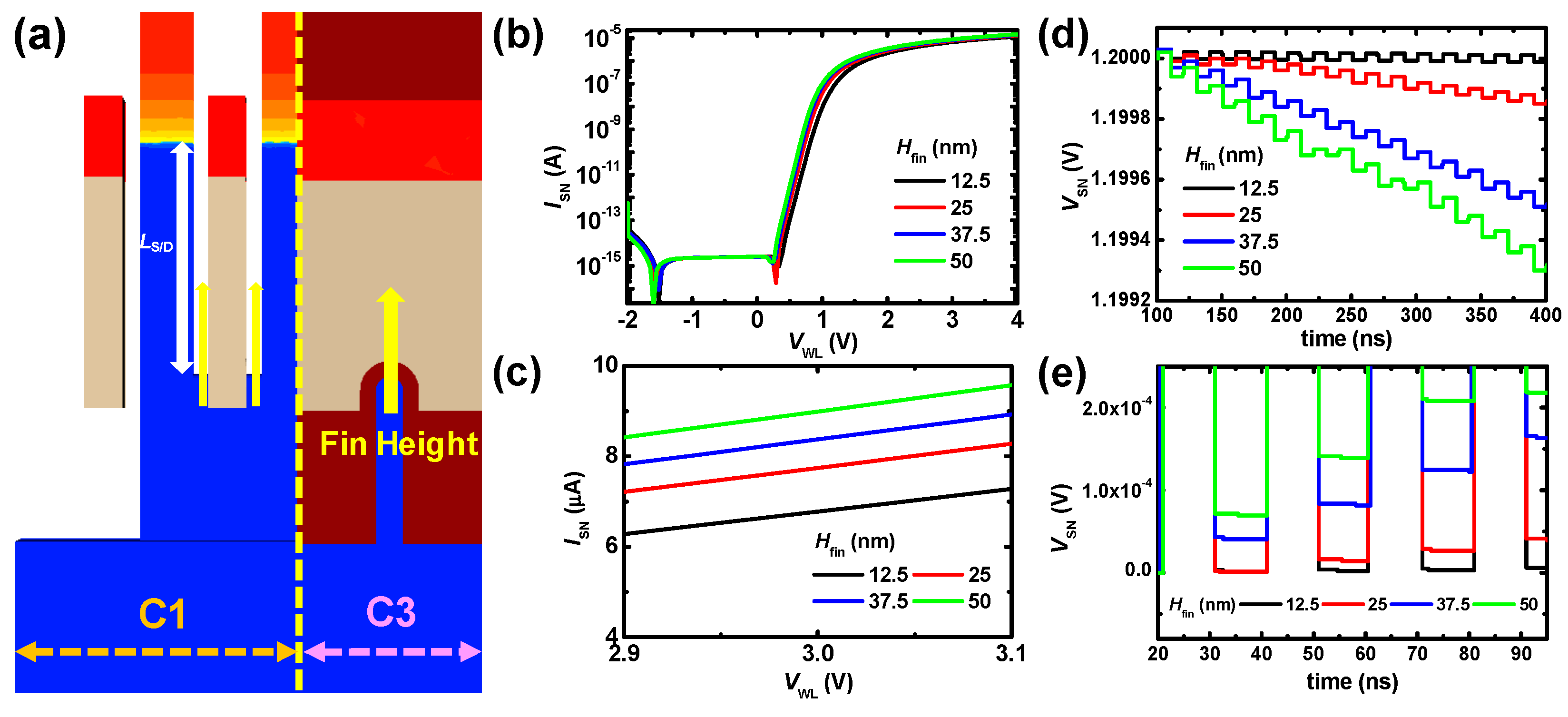

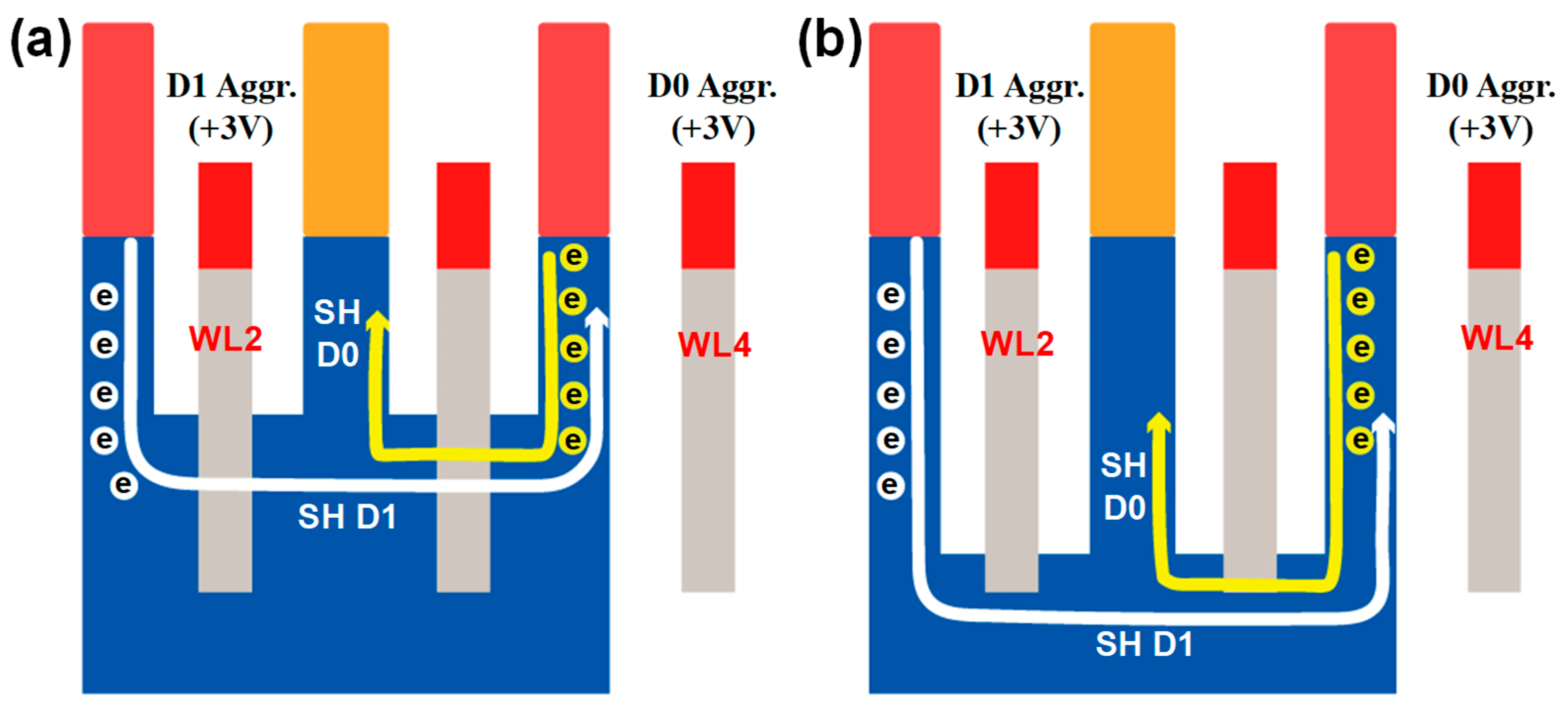

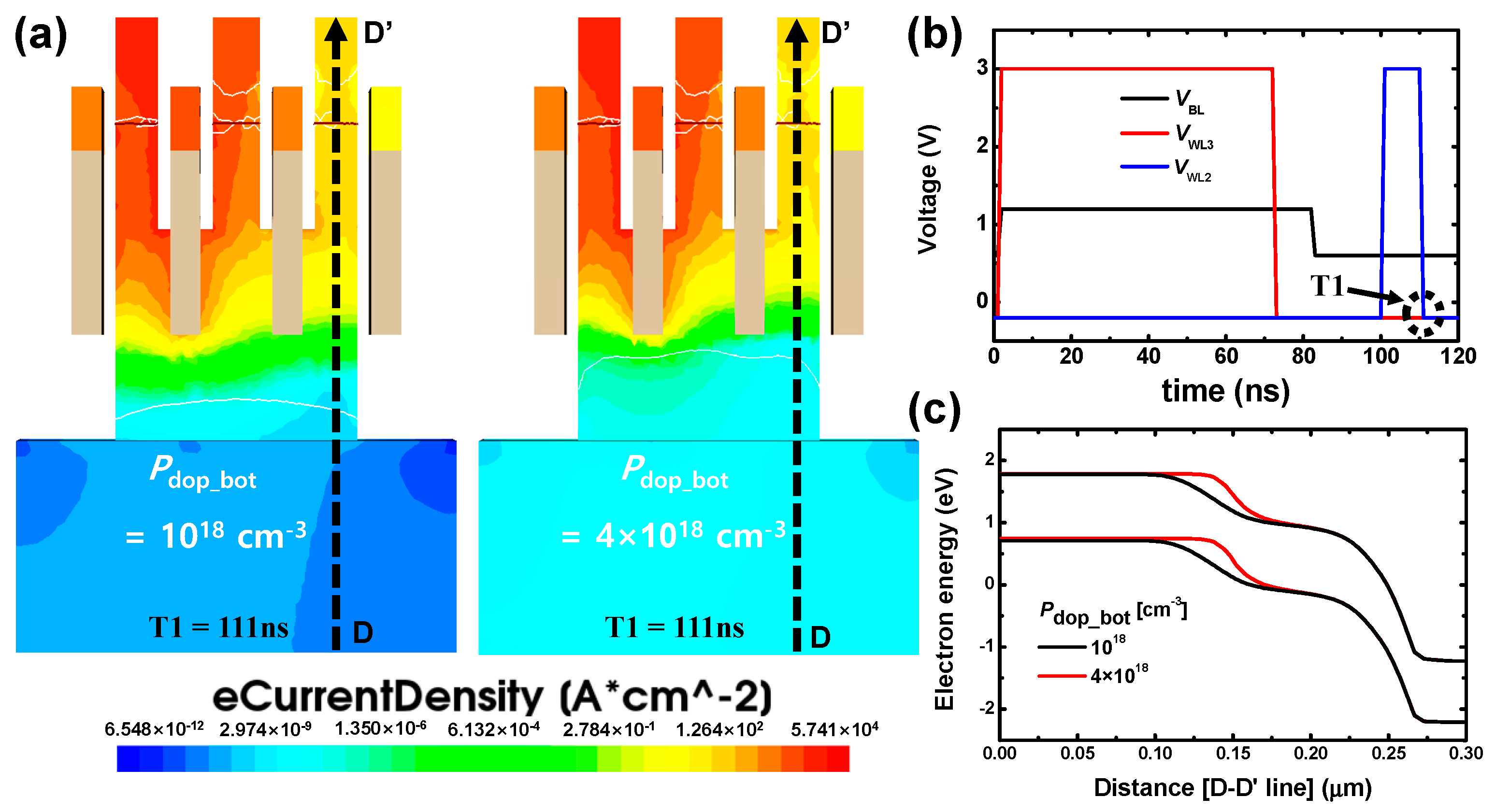

2. Device Structure and Mechanism

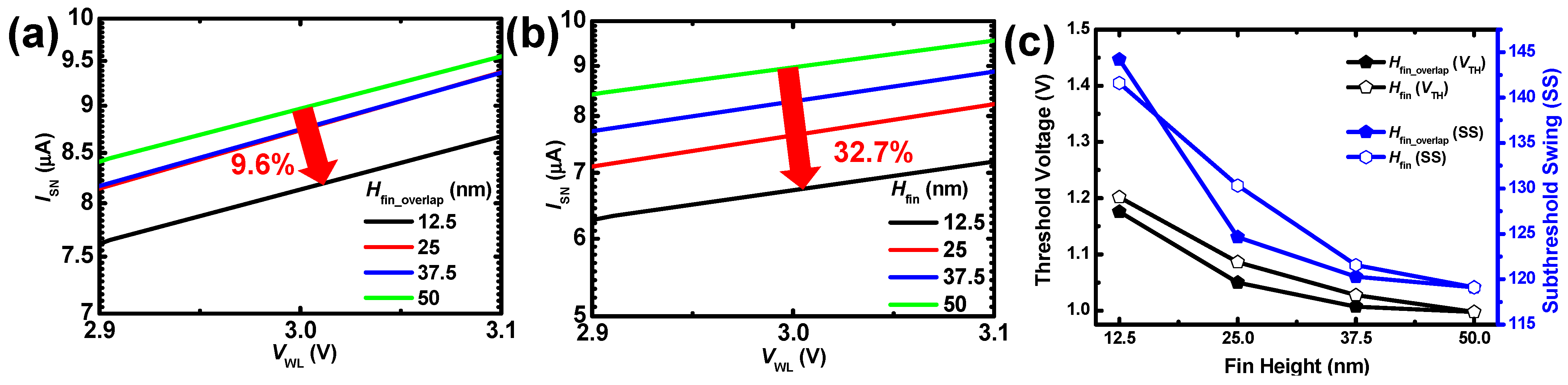

3. Analysis of Characteristics Through BCAT Structure Modifications

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Cha, S.; Seongil, O.; Shin, H.; Hwang, S.; Park, K.; Jang, S.J.; Choi, J.S.; Jin, G.Y.; Son, Y.H.; Cho, H.; et al. Defect Analysis and Cost-Effective Resilience Architecture for Future DRAM Devices. In Proceedings of the 2017 IEEE International Symposium on High Performance Computer Architecture (HPCA), Austin, TX, USA, 4–8 February 2017; pp. 61–72. [Google Scholar]

- Jeong, S.; Lee, J.-S.; Jang, J.; Kim, J.; Shin, H.; Kim, J.H.; Song, J.; Woo, D.; Oh, J.; Lee, J. Investigation of Sub-20nm 4th generation DRAM cell transistor’s parasitic resistance and scalable methodology for Sub-20nm era. In Proceedings of the 2023 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 26–30 March 2023; pp. 1–6. [Google Scholar]

- Seo, H.; Rim, T.; Lee, E.; Jang, S.; Chae, K.; Oh, J.; Ban, H.; Lee, J. Analysis of Intermittent Single-bit Failure on 10-nm Node Generation DRAM Devices. In Proceedings of the 2023 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 26–30 March 2023; pp. 1–6. [Google Scholar]

- Kim, J.S.; Patel, M.; Yağlıkçı, A.G.; Hassan, H.; Azizi, R.; Orosa, L.; Mutlu, O. Revisiting RowHammer: An Experimental Analysis of Modern DRAM Devices and Mitigation Techniques. In Proceedings of the 2020 ACM/IEEE 47th Annual International Symposium on Computer Architecture (ISCA), Virtual, 30 May–3 June 2020; pp. 638–651. [Google Scholar]

- Chae, K.; Rim, T.; Son, Y.; Choi, H.; Lee, J.; Jeong, S.; Lee, J.; Lee, D.; Lee, B.; Woo, D.; et al. Single Metal BCAT Breakthrough to Open a New Era of 12 nm DRAM and Beyond. In Proceedings of the 2024 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), Honolulu, HI, USA, 16–20 June 2024; pp. 1–2. [Google Scholar]

- Yang, T.; Lin, X.-W. Trap-Assisted DRAM Row Hammer Effect. IEEE Electron Device Lett. 2019, 40, 391–394. [Google Scholar] [CrossRef]

- Yang, C.-M.; Wei, C.-K.; Chang, Y.J.; Wu, T.-C.; Chen, H.-P.; Lai, C.-S. Suppression of Row Hammer Effect by Doping Profile Modification in Saddle-Fin Array Devices for Sub-30-nm DRAM Technology. IEEE Trans. Device Mater. Reliab. 2016, 16, 685–687. [Google Scholar] [CrossRef]

- Zhou, L.; Ye, S.; Wang, R.; Ji, Z. Unveiling RowPress in Sub-20 nm DRAM Through Comparative Analysis with Row Hammer: From Leakage Mechanisms to Key Features. IEEE Trans. Electron Devices 2024, 71, 4677–4684. [Google Scholar] [CrossRef]

- Cho, Y.; Kim, Y.-S.; Kwon, M.-W. Mitigating Pass Gate Effect in Buried Channel Array Transistors Through Buried Oxide Integration: Addressing Interference Phenomenon Between Word Lines. Appl. Sci. 2024, 14, 10348. [Google Scholar] [CrossRef]

- Park, J.H.; Kim, S.Y.; Kim, D.Y.; Kim, G.; Park, J.W.; Yoo, S.; Lee, Y.-W.; Lee, M.J. Row Hammer Reduction Using a Buried Insulator in a Buried Channel Array Transistor. IEEE Trans. Electron Devices 2022, 69, 6710–6716. [Google Scholar] [CrossRef]

- Kim, D.; Park, H.; Yeo, I.; Lee, Y.K.; Kim, Y.; Lee, H.-M.; Kwon, K.-W. Rowhammer Attacks in Dynamic Random-Access Memory and Defense Methods. Sensors 2024, 24, 592. [Google Scholar] [CrossRef] [PubMed]

- Kim, M.; Choi, J.; Kim, H.; Lee, H.-J. An Effective DRAM Address Remapping for Mitigating Rowhammer Errors. IEEE Trans. Comput. 2019, 68, 1428–1441. [Google Scholar] [CrossRef]

- Gruss, D.; Lipp, M.; Schwarz, M.; Genkin, D.; Juffinger, J.; O’Connell, S.; Schoechl, W.; Yarom, Y. Another Flip in the Wall of Rowhammer Defenses. In Proceedings of the 2018 IEEE Symposium on Security and Privacy (SP), San Francisco, CA, USA, 20–24 May 2018; pp. 245–261. [Google Scholar]

- Schaller, A.; Xiong, W.; Anagnostopoulos, N.A.; Saleem, M.U.; Gabmeyer, S.; Katzenbeisser, S.; Szefer, J. Intrinsic Rowhammer PUFs: Leveraging the Rowhammer Effect for Improved Security. In Proceedings of the 2017 IEEE International Symposium on Hardware Oriented Security and Trust (HOST), McLean, VA, USA, 1–5 May 2017; pp. 1–7. [Google Scholar]

- Hwang, Y.; Park, J.; Jin, G.-Y.; Chung, C. An Overview and Future Challenges of High Density DRAM for 20 nm and Beyond. In Proceedings of the Extended Abstracts of the 2012 International Conference on Solid State Devices and Materials, Kyoto, Japan, 4–7 September 2012; pp. 586–587. [Google Scholar]

- Jang, D.; Kim, D.; Lee, J.; Lee, I.; Ahn, S.B.; Hong, Y.; Kim, S.; Park, T.; Ban, H. Improvement of VRT Immunity Using Low 10-Boron Word Line in Recent DRAM. Microelectron. Reliab. 2024, 157, 115396. [Google Scholar] [CrossRef]

- Park, D.-S.; Im, D.-H.; Kim, Y.-J.; Lee, S.S.; Kang, B.-J.; Seo, J.-H.; Koo, T.; Choi, B. Novel Dual Work Function Buried Channel Array Transistor Process Design for Sub-17 nm DRAM. IEEE Access 2024, 12, 63049–63065. [Google Scholar] [CrossRef]

- Park, J.M.; Hwang, Y.S.; Kim, S.-W.; Han, S.Y.; Park, J.S.; Kim, J.; Seo, J.W.; Kim, B.S.; Shin, S.H.; Cho, C.H.; et al. 20nm DRAM: A New Beginning of Another Revolution. In Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; pp. 26.5.1–26.5.4. [Google Scholar]

- Suh, M.; Ryu, M.; Ha, J.; Bang, M.; Lee, D.; Kim, J. Design Guideline of Saddle-Fin-Based DRAM for Mitigating Rowhammer Effect. IEEE Trans. Electron Devices 2024, 71, 2417–2422. [Google Scholar] [CrossRef]

- Ramaswamy, N.; Ananthan, V.; Hwang, D.; Iyer, R.; Mouli, C.; Mcteer, A.; Tang, S.; Parekh, K.; Owens, T.; Kim, Y.P.; et al. Metal Gate Recessed Access Device (RAD) for DRAM Scaling. In Proceedings of the 2007 IEEE Workshop on Microelectronics and Electron Devices, Boise, ID, USA, 20 April 2007; pp. 42–44. [Google Scholar]

- Walker, A.J.; Lee, S.; Beery, D. On DRAM Rowhammer and the Physics of Insecurity. IEEE Trans. Electron Devices 2021, 68, 1400–1410. [Google Scholar] [CrossRef]

- Sun, Y.; Liu, X.; Wang, N.; Jeon, J.; Wu, B.; Cao, K. Trap-Assisted Passing Word Line Leakage and Variable Retention Time in DRAM. In Proceedings of the 2021 IEEE 4th International Conference on Electronics Technology (ICET), Chengdu, China, 7–10 May 2021; pp. 338–341. [Google Scholar]

| Structure Condition | Units | Structure Condition | Units |

|---|---|---|---|

| Total thickness (Ttotal) | 300 nm | Gate oxide thickness (Tox) | 6 nm |

| Storage node length (LSN) | 20 nm | Poly-Si gate thickness (Tpoly) | 30 nm |

| Bit line node length (LBL) | 22 nm | TiN gate thickness (TTiN) | 86 nm |

| Junction thickness (Tj) | 50 nm | Θangle | 0° |

| Bulk thickness (Tbulk) | 100 nm | Hfin_overlap | 50 nm |

| Top gate length (LTG) | 14 nm | Hfin | 50 nm |

| Bottom gate length (LBG) | 14 nm | Pdop_bot | 1018 cm−3 |

| Gate Angle [°] | Channel Length [nm] | Gate Area (C1-C1′ Line) [nm2] | Distance Between Adjacent Fins [nm] |

|---|---|---|---|

| 0 | 126 | 1624 | 22 |

| 1 | 123 | 1276 | 26 |

| 2 | 119 | 1032 | 29 |

| 3 | 116 | 777 | 33 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Im, J.; Kim, H.; Kim, H.; Woo, S.Y. Design Strategies for BCAT Structures: Enhancing DRAM Reliability and Mitigating Row Hammer Effect. Electronics 2025, 14, 499. https://doi.org/10.3390/electronics14030499

Im J, Kim H, Kim H, Woo SY. Design Strategies for BCAT Structures: Enhancing DRAM Reliability and Mitigating Row Hammer Effect. Electronics. 2025; 14(3):499. https://doi.org/10.3390/electronics14030499

Chicago/Turabian StyleIm, Jisung, Hansol Kim, Hyungjin Kim, and Sung Yun Woo. 2025. "Design Strategies for BCAT Structures: Enhancing DRAM Reliability and Mitigating Row Hammer Effect" Electronics 14, no. 3: 499. https://doi.org/10.3390/electronics14030499

APA StyleIm, J., Kim, H., Kim, H., & Woo, S. Y. (2025). Design Strategies for BCAT Structures: Enhancing DRAM Reliability and Mitigating Row Hammer Effect. Electronics, 14(3), 499. https://doi.org/10.3390/electronics14030499