A Wideband Analog Vector Modulator Phase Shifter Based on Non-Quadrature Vector Operation

Abstract

:1. Introduction

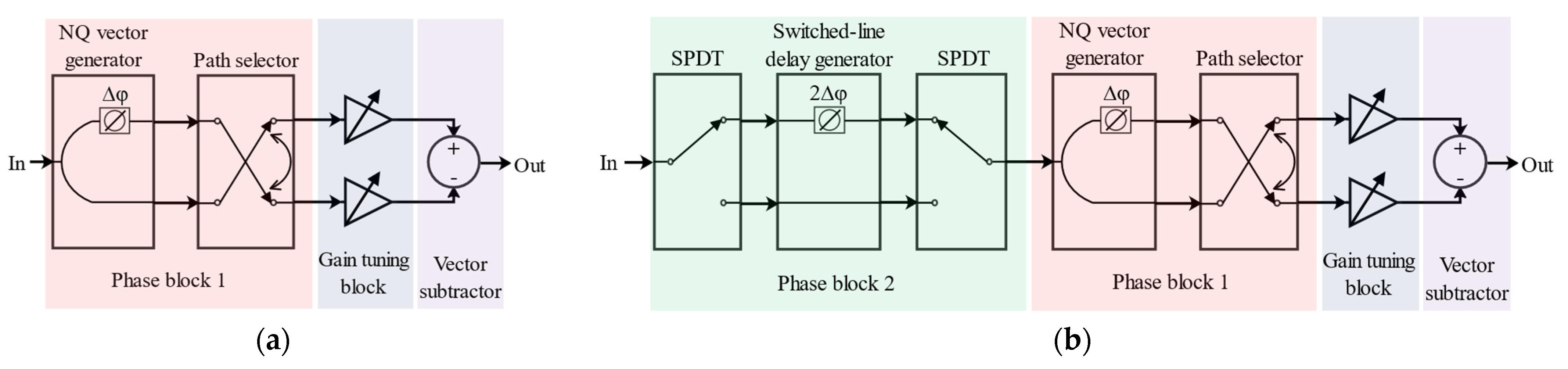

2. Conceptual Block Diagram of the Non-Quadrature Vector Modulator

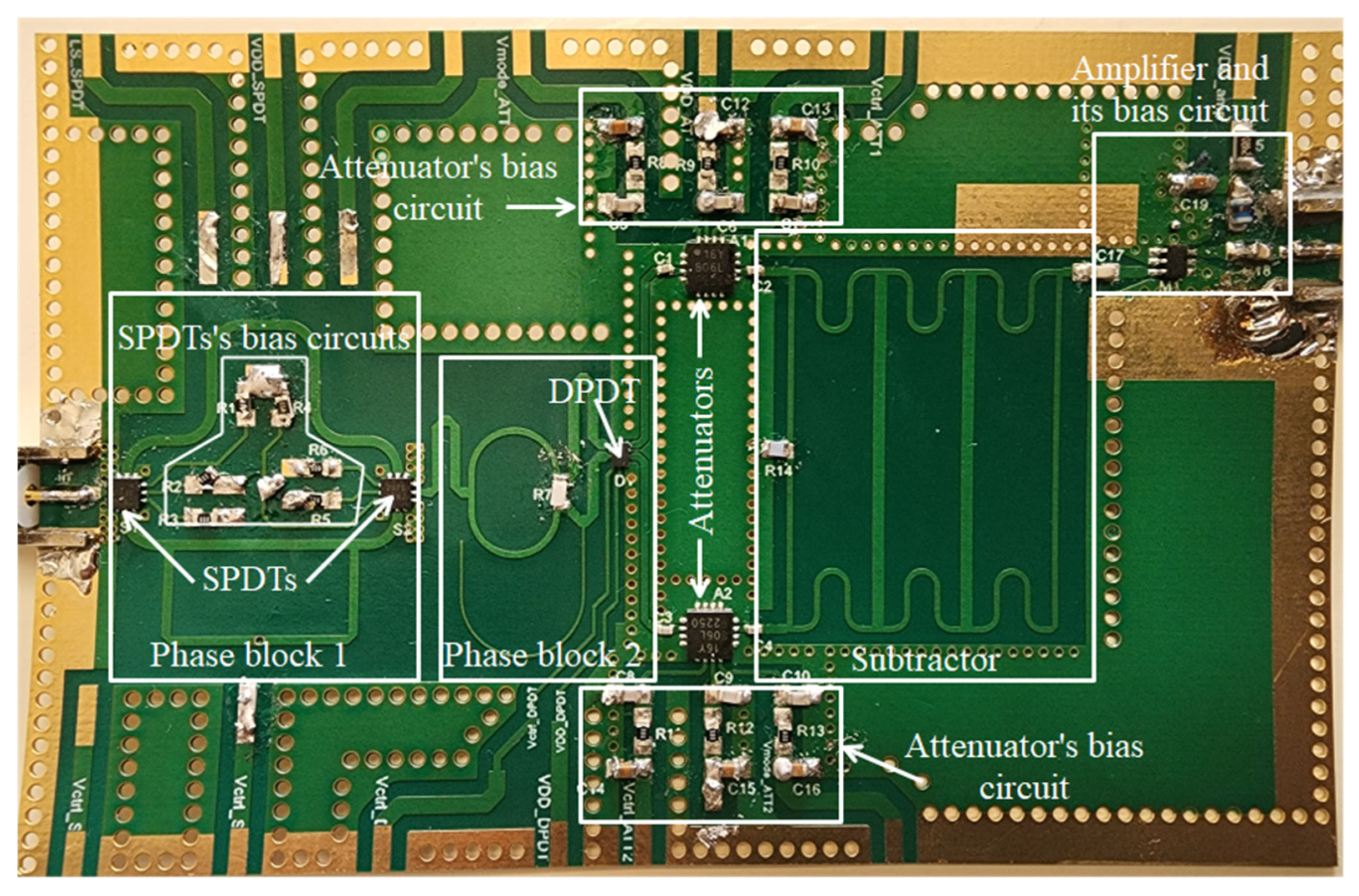

3. Implementation of the Proposed Phase Shifter

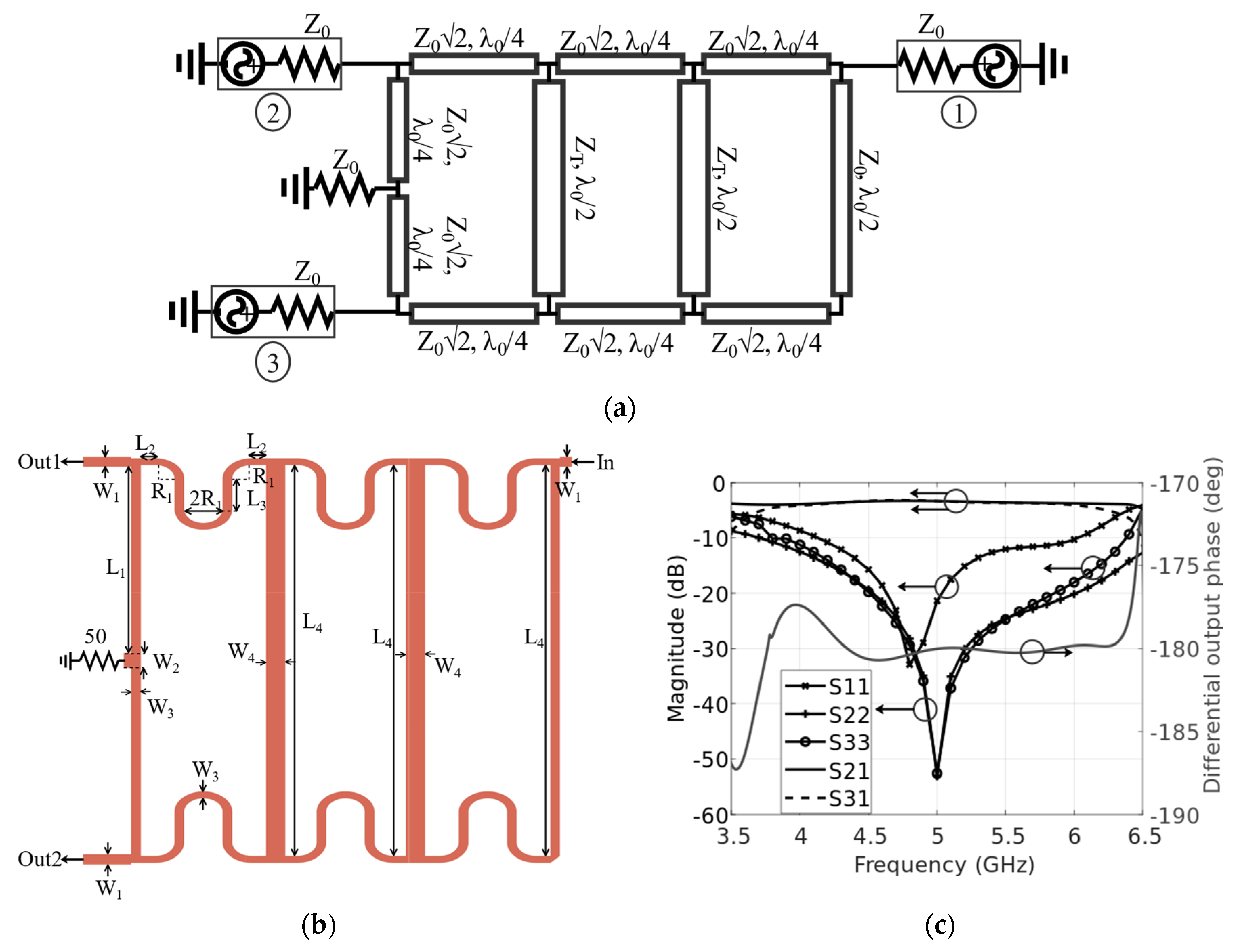

3.1. Phase Block 1

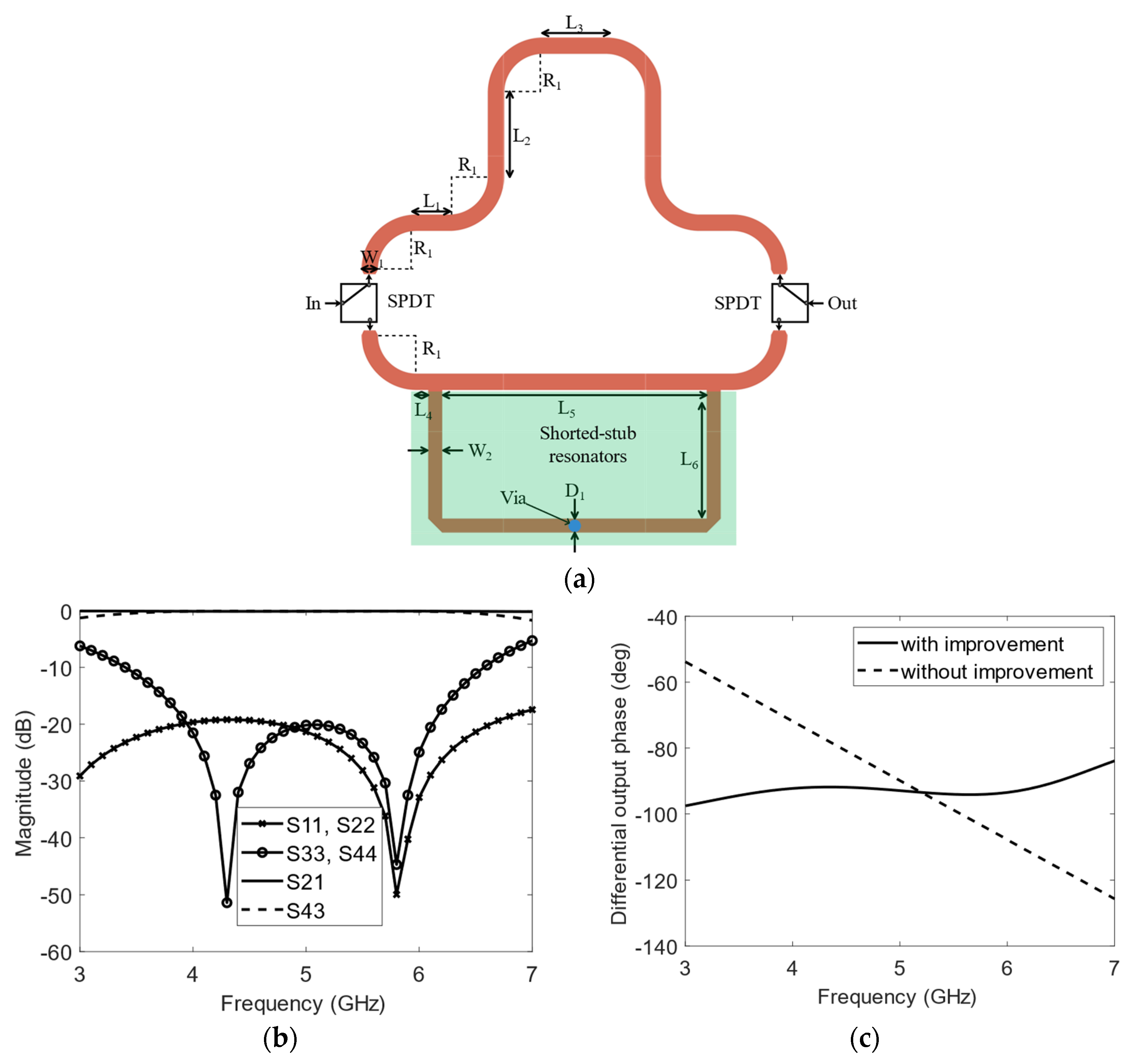

3.2. Phase Block 2

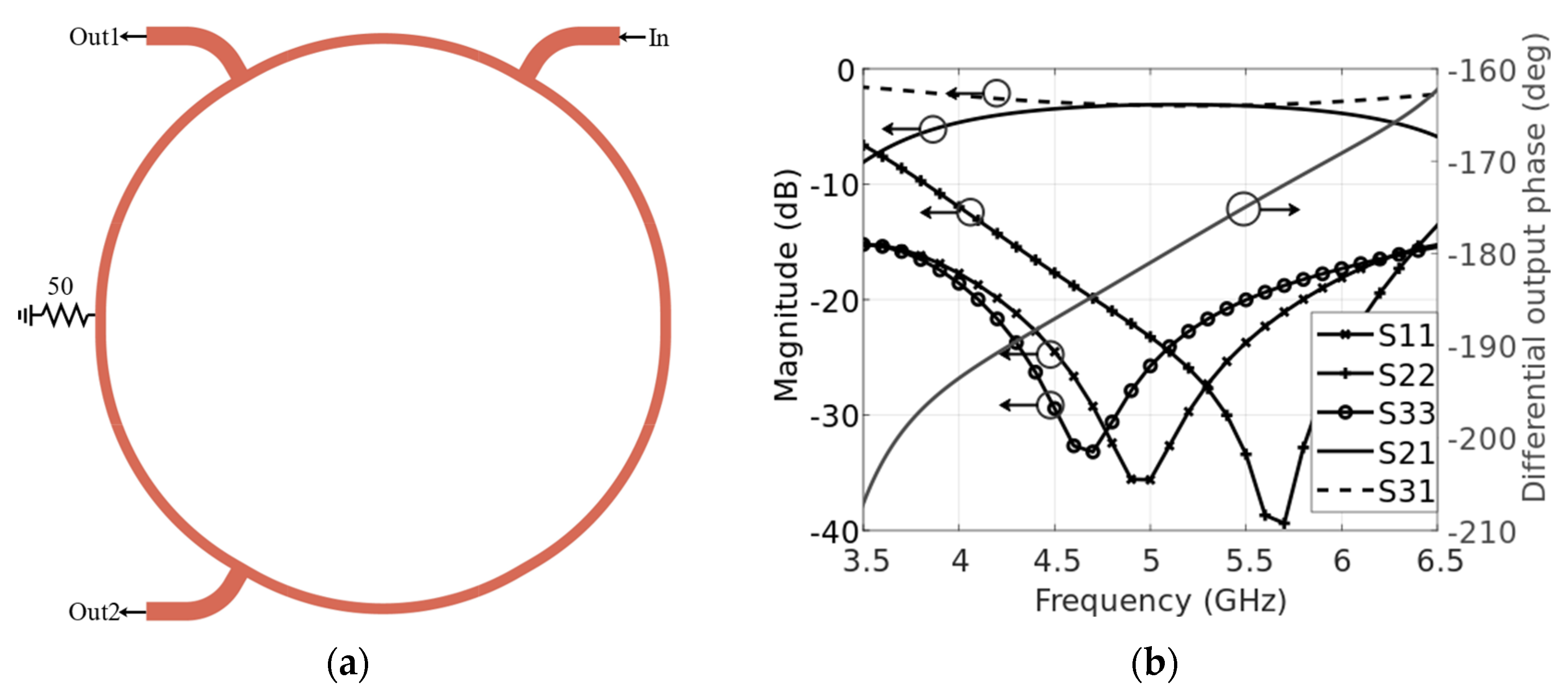

3.3. Vector Subtractor

3.4. Gain-Tuning Block and Output Amplification

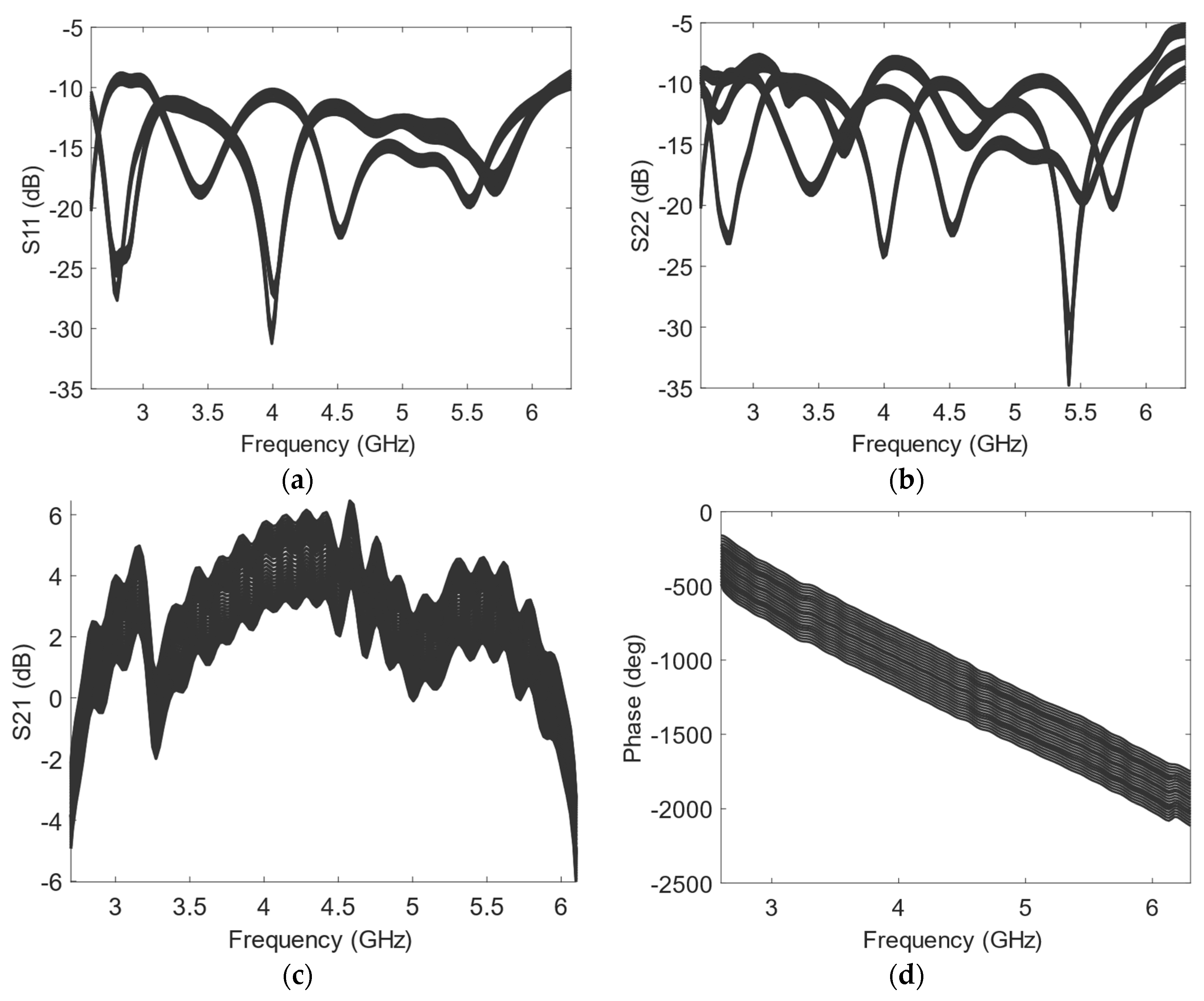

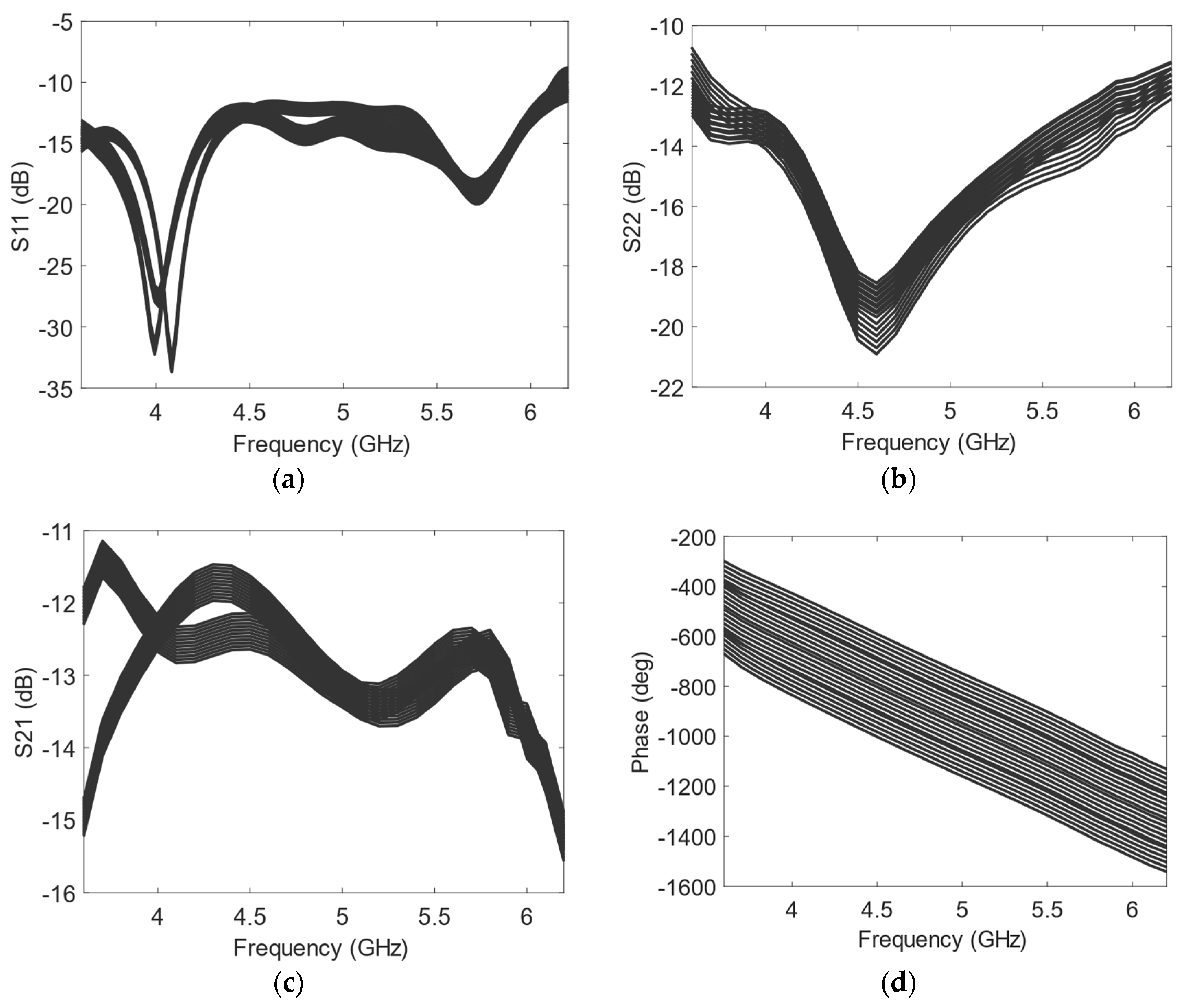

4. Measurement Results and Discussion

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Ojaroudi Parchin, N.; Jahanbakhsh Basherlou, H.; Abd-Alhameed, R.A. Design of Multi-Mode Antenna Array for Use in Next-Generation Mobile Handsets. Sensors 2020, 20, 2447. [Google Scholar] [CrossRef] [PubMed]

- Guan, Y.; Geng, F.; Saleh, J.H. Review of High Throughput Satellites: Market Disruptions, Affordability-Throughput Map, and the Cost Per Bit/Second Decision Tree. IEEE Aerosp. Electron. Syst. Mag. 2019, 34, 64–80. [Google Scholar] [CrossRef]

- Jeon, H.; Kobayashi, K.W. A High Linearity +44.5-dBm IP3 C-Band 6-bit Digital Phase Shifter Using SOI Technology for Phased Array Applications. IEEE Microw. Wireless Compon. Lett. 2019, 29, 733–736. [Google Scholar] [CrossRef]

- Kadam, M.; Kumar, A.; Aniruddhan, S. A 4-bit Bidirectional Phase Shifter for 3GHz S-Band Applications. In Proceedings of the 2021 IEEE International Midwest Symposium on Circuits and Systems (MWSCAS), Lansing, MI, USA, 10–13 August 2021; pp. 745–748. [Google Scholar]

- Abdullah, S.; Xiao, G.G.; Amaya, R.E. Design and Implementation of an 8-bit, 256-step Digitally-Controlled Phase Shifter at 2.1 GHz with Minimum 1.41° Phase Change for its LSB Step Size. In Proceedings of the 2021 IEEE Canadian Conference on Electrical and Computer Engineering, Virtual, 12–17 September 2021; pp. 1–4. [Google Scholar]

- An, B.; Chaudhary, G.; Jeong, Y. Wideband Tunable Phase Shifter with Low In-Band Phase Deviation Using Coupled Line. IEEE Microw. Wirel. Compon. Lett. 2018, 28, 678–680. [Google Scholar] [CrossRef]

- Liu, W.J.; Zheng, S.Y.; Pan, Y.M.; Li, Y.X.; Long, Y.L. A Wideband Tunable Reflection-Type Phase Shifter with Wide Relative Phase Shift. IEEE Trans. Circuits Syst. II Exp. Briefs 2017, 64, 1442–1446. [Google Scholar] [CrossRef]

- Burdin, F.; Iskandar, Z.; Podevin, F.; Ferrari, P. Design of Compact Reflection-Type Phase Shifters with High Figure-of-Merit. IEEE Trans. Microw. Theory Tech. 2015, 63, 1883–1893. [Google Scholar] [CrossRef]

- Cetindogan, B.; Ozeren, E.; Ustundag, B.; Kaynak, M.; Gurbuz, Y. A 6 Bit Vector-Sum Phase Shifter with a Decoder-Based Control Circuit for X-Band Phased Arrays. IEEE Microw. Wireless Compon. Lett. 2016, 26, 64–66. [Google Scholar] [CrossRef]

- Zhu, X.; Yang, T.; Chi, P.-L.; Xu, R. Novel Passive Vector-Sum Reconfigurable Filtering Phase Shifter with Continuous Phase-Control and Tunable Center Frequency. IEEE Trans. Microw. Theory Tech. 2022, 70, 1188–1197. [Google Scholar] [CrossRef]

- Mohsenpour, M.-M.; Saavedra, C.E. Variable 360° Vector-Sum Phase Shifter with Coarse and Fine Vector Scaling. IEEE Trans. Microw. Theory Tech. 2016, 64, 2113–2120. [Google Scholar] [CrossRef]

- Akbar, F.; Mortazawi, A. A Frequency Tunable 360° Analog CMOS Phase Shifter with an Adjustable Amplitude. IEEE Trans. Circuits Syst. II Express Briefs 2017, 64, 1427–1431. [Google Scholar] [CrossRef]

- Qiu, F.; Zhu, H.; Wu, L.; Che, W.; Xue, Q. A 15–38 GHz Vector-Summing Phase-Shifter with 360° Phase-Shifting Range Using Improved I/Q Generator. IEEE Trans. Circuits Syst. II Express Briefs 2021, 68, 3199–3203. [Google Scholar] [CrossRef]

- Sah, S.P.; Yu, X.; Heo, D. Design and Analysis of a Wideband 15–35-GHz Quadrature Phase Shifter with Inductive Loading. IEEE Trans. Microw. Theory Tech. 2013, 61, 3024–3033. [Google Scholar] [CrossRef]

- Kim, S.Y.; Kang, D.-W.; Koh, K.-J.; Rebeiz, G.M. An Improved Wideband All-Pass I/Q Network for Millimeter-Wave Phase Shifters. IEEE Trans. Microw. Theory Tech. 2012, 60, 3431–3439. [Google Scholar] [CrossRef]

- Zhou, J.; Qian, H.J.; Luo, X. High-Resolution Wideband Vector-Sum Digital Phase Shifter with On-Chip Phase Linearity Enhancement Technology. IEEE Trans. Circuits Syst. I Regul. Pap. 2021, 68, 2457–2469. [Google Scholar] [CrossRef]

- Ye, Y.; Li, L.-Y.; Tong, R.; Sun, X.-W. A Full-360° Vector-Sum Phase Shifter with Low RMS Phase and Gain Errors for 60 GHz 5-bit Application. In Proceedings of the 2014 9th European Microwave Integrated Circuit Conference, Rome, Italy, 6–7 October 2014; pp. 305–308. [Google Scholar]

- Thompson, D.; Yeary, M.; Fulton, C.; McGuire, B. Optimized Beam Steering Approach for Improved Sidelobes in Phased Array Radars Using a Minimal Number of Control Bits. IEEE Trans. Antennas Propag. 2015, 63, 106–112. [Google Scholar] [CrossRef]

- Kebe, M.; Abdullah, S.; Amaya, R.E.; Yagoub, M.C.E. Architecture and Design of a New Non-Quadrature Vector-Sum Microwave Phase Shifter at 10 GHz with Maximum Residual Phase Error of 1.80°. In Proceedings of the 2023 International Conference on Electrical, Computer and Communication Engineering (ECCE), Chittagong, Bangladesh, 23–25 February 2023; pp. 1–6. [Google Scholar]

- Kebe, M.; Mohammad, B.; Sanduleanu, M. Differential-to-Differential and Single-Ended-to-Differential Bandpass Filters for 5G Applications. AEU Int. J. Electron. Commun. 2021, 141, 153977. [Google Scholar] [CrossRef]

- Vishay. High Frequency (Up to 40 GHz) Resistor, Thin Film Surface Mount Chip, FC0603E1000BTBST1 Datasheet. Revised Mar. 2021. Available online: https://www.vishay.com/docs/60093/fcseries.pdf (accessed on 7 February 2025).

- Infineon. DPDT Cross Switch with GPIO Control Interface, BGSX22G6U10 Datasheet. Revised Oct. 2023. Available online: https://www.infineon.com/dgdl/Infineon-BGSX22G6U10-DataSheet-v02_01-EN.pdf?fileId=5546d4627a0b0c7b017a2d9e9ec16100 (accessed on 7 February 2025).

- Renesas. High Linearity Broadband SP2T 5MHz to 10GHz, F2976 Datasheet. Revised Apr. 2017. Available online: https://www.renesas.com/en/products/rf-products/rf-switches/f2976-high-linearity-broadband-sp2t-rf-switch?srsltid=AfmBOooWa3dXZJzfAuZe6PMdY4xSMphR-NsTExuMhCVkyehS3GPzhLWc#documents (accessed on 7 February 2025).

- Vishay. High Frequency 70 GHz Thin Film Chip Resistor, CH0603-50RJNT Datasheet. Revised Jun. 2024. Available online: https://www.vishay.com/docs/53014/ch.pdf (accessed on 7 February 2025).

- Renesas. Voltage Variable RF Attenuator, F2250NLGK8 Datasheet. Revised Jan. 2017. Available online: https://www.renesas.com/en/products/rf-products/rf-attenuators/f2250-wideband-voltage-variable-rf-attenuator?srsltid=AfmBOoqZ_Mjfhy9VJFWhGbyG79WwZIhRsc0apvcM9eGSicJtncJxTG5P (accessed on 7 February 2025).

- Zhao, X.-B.; Wei, F.; Zhang, P.F.; Shi, X.W. Mixed-Mode Magic-Ts and Their Applications on the Designs of Dual-Band Balanced Out-of-Phase Filtering Power Dividers. IEEE Trans. Microw. Theory Tech. 2023, 71, 3896–3905. [Google Scholar] [CrossRef]

- Versaci, M.; Laganà, F.; Morabito, F.C.; Palumbo, A.; Angiulli, G. Adaptation of an Eddy Current Model for Characterizing Subsurface Defects in CFRP Plates Using FEM Analysis Based on Energy Functional. Mathematics 2024, 12, 2854. [Google Scholar] [CrossRef]

| Parameter | Frequency (GHz) | ∆φ (°) | Gain (dB) | Phase Range/Resolution (°/bit) | Gain Imbalance (dB) |

|---|---|---|---|---|---|

| Value | 5 ± 1 | 45 | >0 | 360/continuous | <4 |

| Parameter | W1 | W2 | W3 | W4 | L1 | L2 | L3 | L4 | L5 | D1 | D2 | S1 | S2 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Value (mm) | 0.70 | 0.45 | 0.77 | 0.20 | 6.57 | 0.97 | 4.30 | 4.5 | 3.6 | 5.15 | 7.80 | 1.02 | 0.10 |

| Parameter | W1 | W2 | L1 | L2 | L3 | L4 | L5 | L6 | R1 | D1 |

|---|---|---|---|---|---|---|---|---|---|---|

| Value (mm) | 0.70 | 0.60 | 1.4 | 3.57 | 2.70 | 0.50 | 11.30 | 5.60 | 1.65 | 0.25 |

| Parameter | W1 | W2 | W3 | W4 | L1 | L2 | L3 | L4 | R1 |

|---|---|---|---|---|---|---|---|---|---|

| Value (mm) | 0.60 | 0.86 | 0.38 | 0.80 | 11.07 | 0.60 | 1.80 | 23 | 1 |

| Reference | [6] | [9] | [10] | [11] | This Work 1 1 | This Work 2 2 |

|---|---|---|---|---|---|---|

| Technology | PCB | 250 nm BiCMOS | PCB | 130 nm CMOS | PCB | PCB |

| Type | RTPS | VSPS | VSPS | VSPS | NQVSPS | NQVSPS |

| f0/FBW (GHz/%) | 2.5/20 | 10/40 | 1.175/21.3 | 5.4/18.6 | 4.9/53.1 | 4.44/77.3 |

| Phase range/resolution (°/bits) | 146.9/continuous | 360/6 | 320@1.16 GHz/continuous | 360/6 | 360/continuous | 360/continuous |

| RMS phase error (°) | 5.79 | 2–6.4 | - | 1.25–9.5 | - | - |

| RMS gain error (dB) | - | 1.6–2 | - | 0.5–0.7 | - | - |

| Gain (dB) | −0.94 ± 0.34 | −4.5 ± 2 | −3.1 ± 1 | −0.1 ± 1.15 | −13.45 ± 2.15 | 0.8 ± 5.5 |

| Minimum input P1dB (dBm) | - | −11 | 17.7 | −11.9 | - | 22.7 |

| Area ( ) 4 | - | - | 0.99 | - | 0.78 3 | 0.9 3 |

| Power consumption (mW) | 0 | 110 | 0 | 28 | 6 | 231 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kebe, M.; Yagoub, M.C.E.; Amaya, R.E. A Wideband Analog Vector Modulator Phase Shifter Based on Non-Quadrature Vector Operation. Electronics 2025, 14, 997. https://doi.org/10.3390/electronics14050997

Kebe M, Yagoub MCE, Amaya RE. A Wideband Analog Vector Modulator Phase Shifter Based on Non-Quadrature Vector Operation. Electronics. 2025; 14(5):997. https://doi.org/10.3390/electronics14050997

Chicago/Turabian StyleKebe, Mamady, Mustapha C. E. Yagoub, and Rony E. Amaya. 2025. "A Wideband Analog Vector Modulator Phase Shifter Based on Non-Quadrature Vector Operation" Electronics 14, no. 5: 997. https://doi.org/10.3390/electronics14050997

APA StyleKebe, M., Yagoub, M. C. E., & Amaya, R. E. (2025). A Wideband Analog Vector Modulator Phase Shifter Based on Non-Quadrature Vector Operation. Electronics, 14(5), 997. https://doi.org/10.3390/electronics14050997