Experimental Study on Electromagnetic Pulse Sensitivity for Power Modules of FPGAs

Abstract

:1. Introduction

2. Experimental Methods

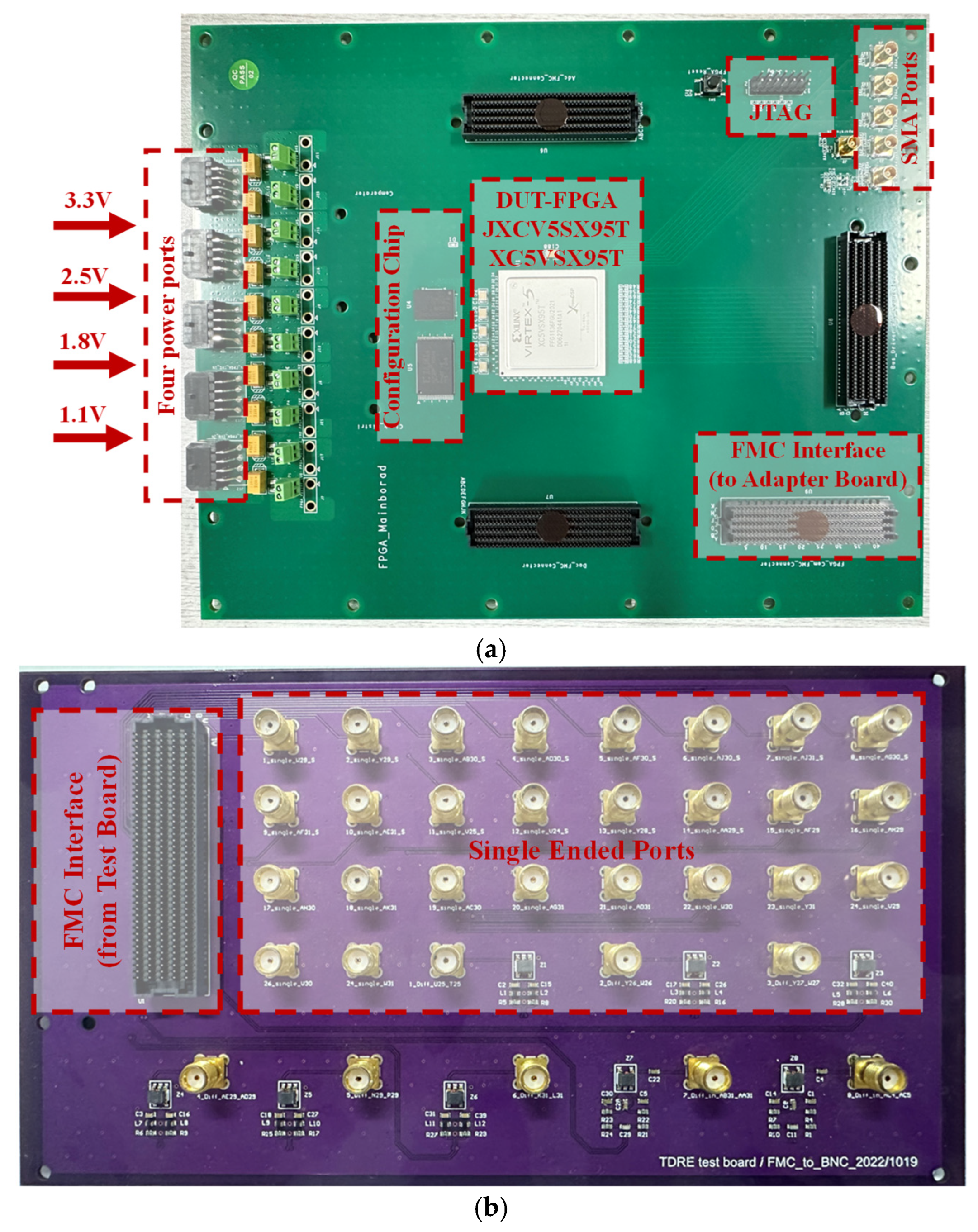

2.1. Device Under Test (DUT)

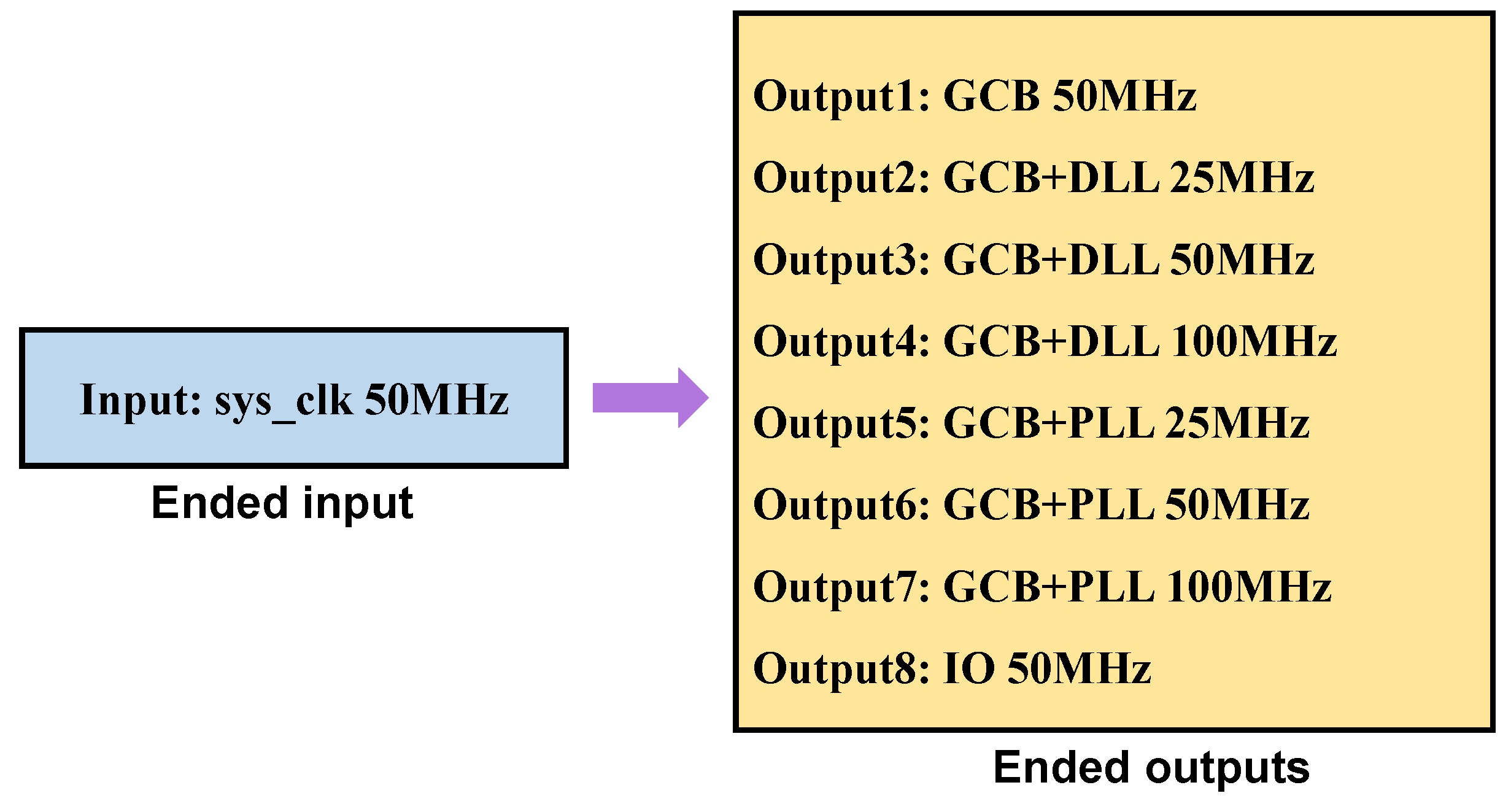

2.2. Test Program

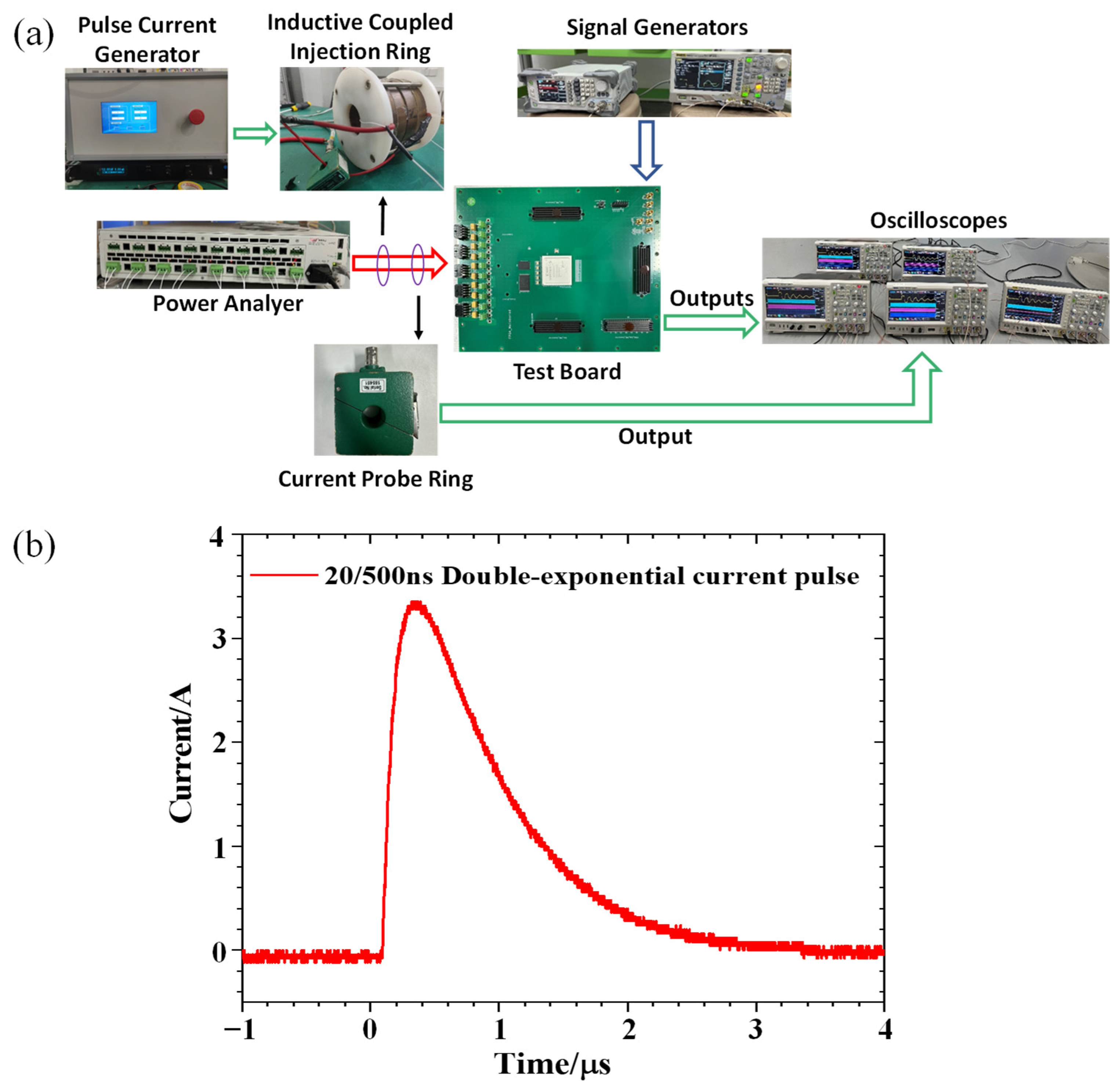

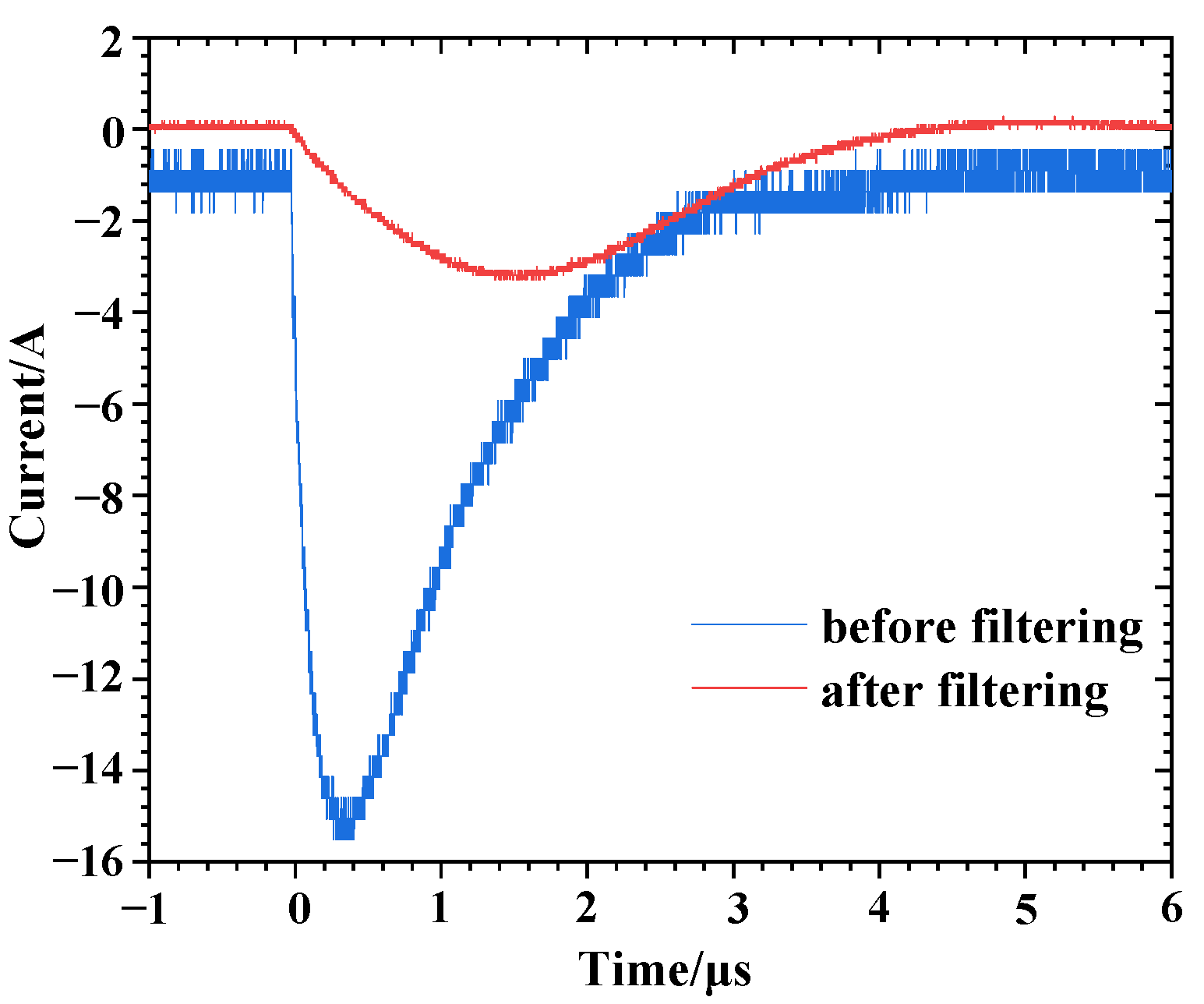

2.3. Pulsed Current Generation, Injection, and Detection

2.4. Flow of Experiments

3. Experimental Results and Analysis

3.1. Positive PCI into Power Lines of the JXCV5SX95T Test Board

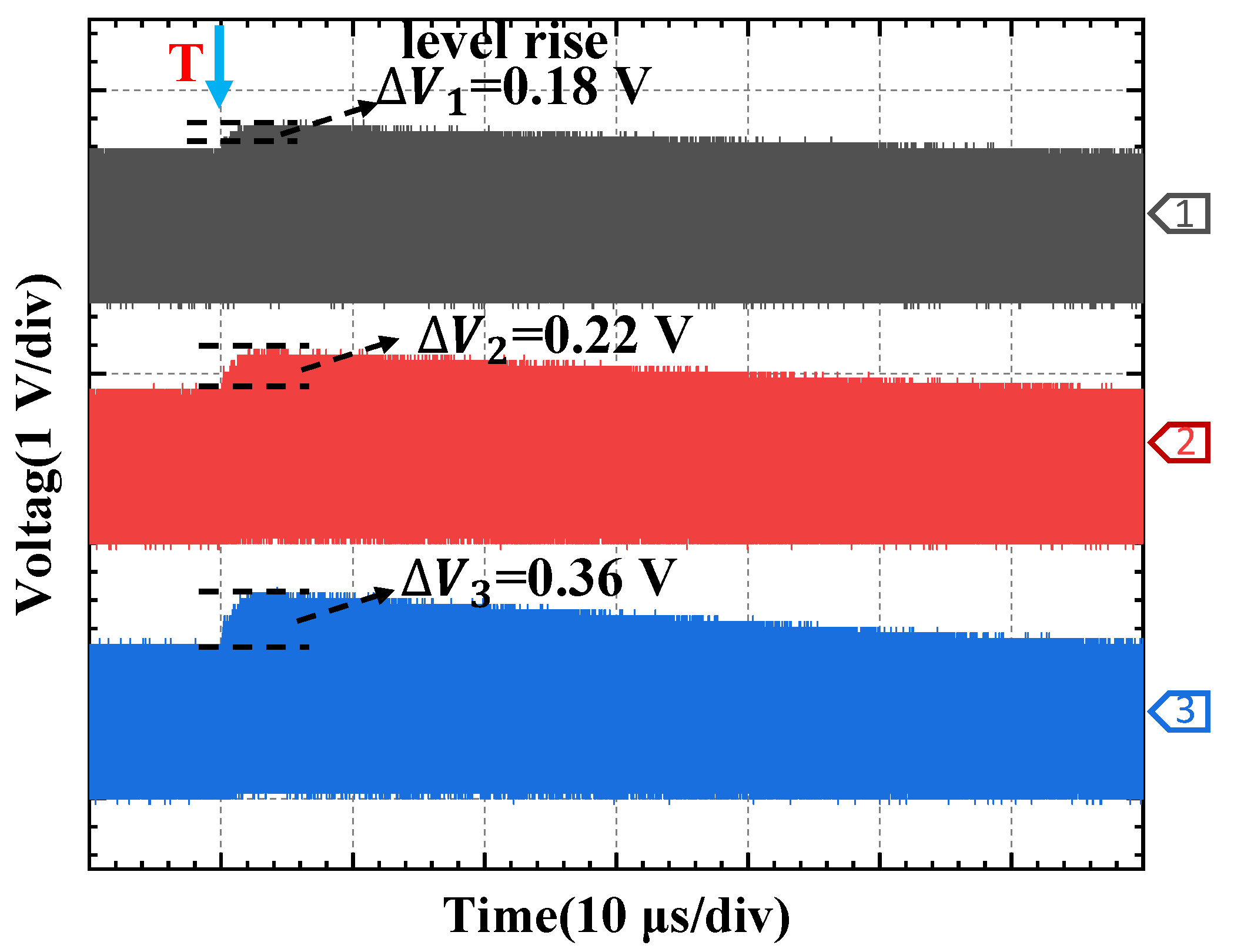

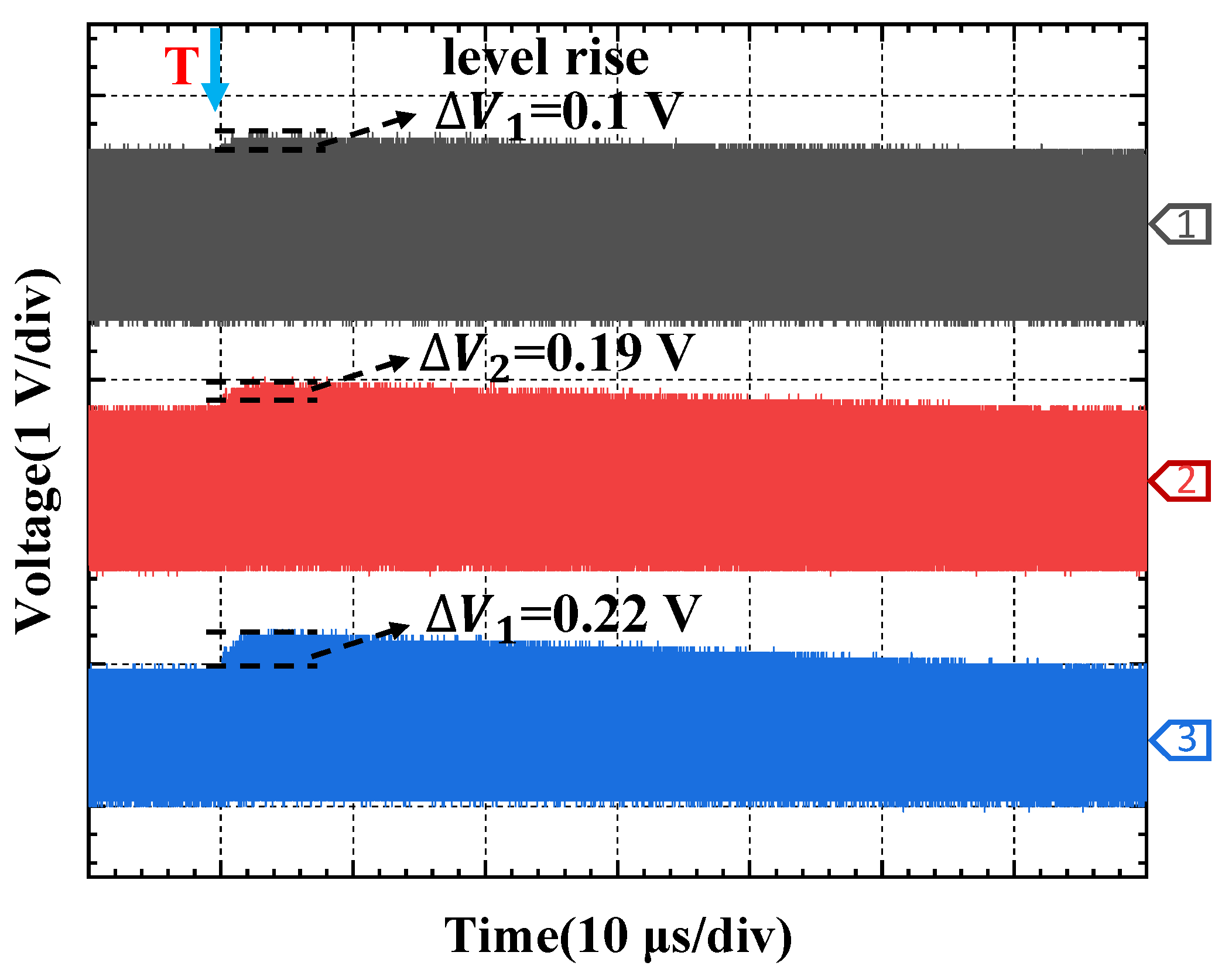

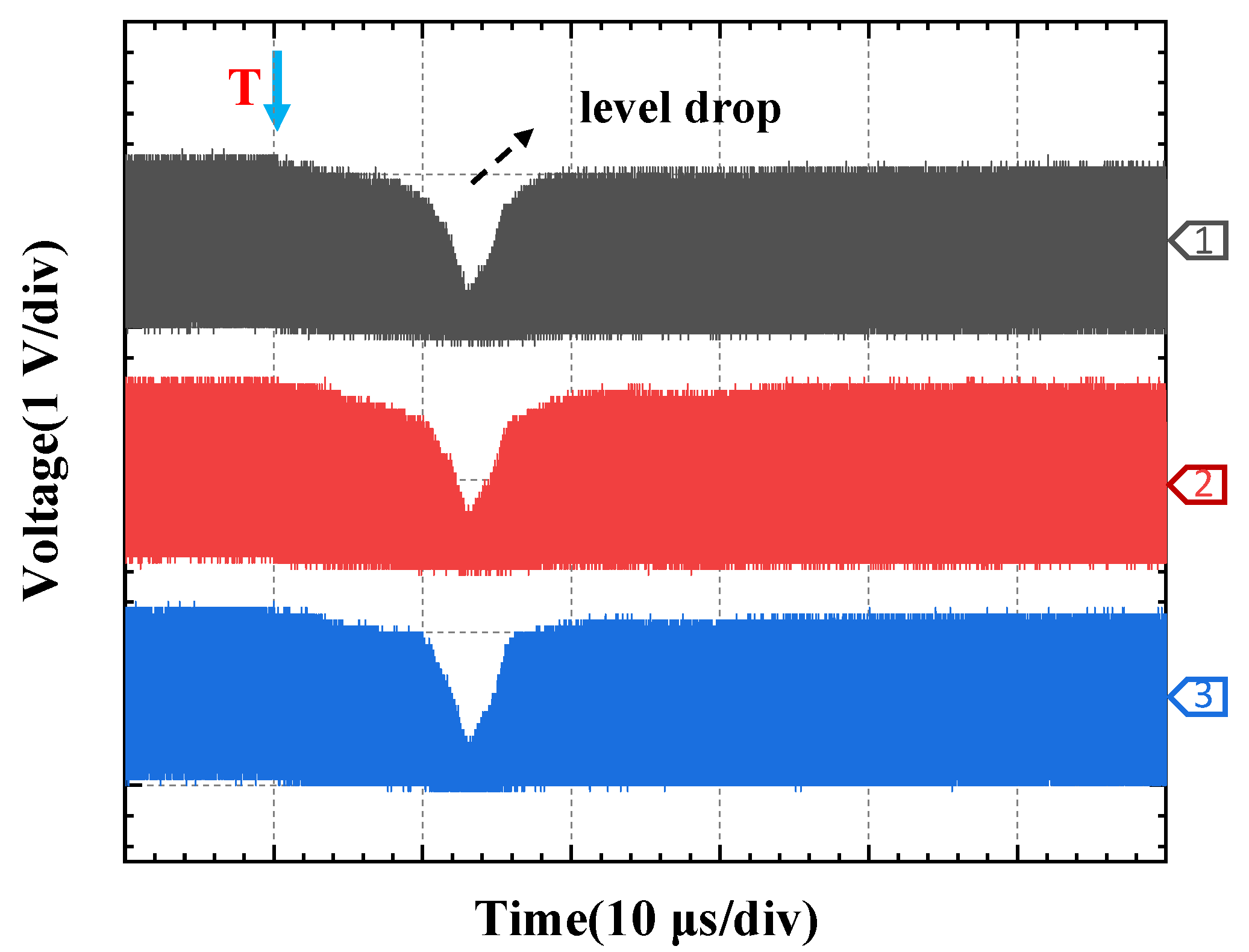

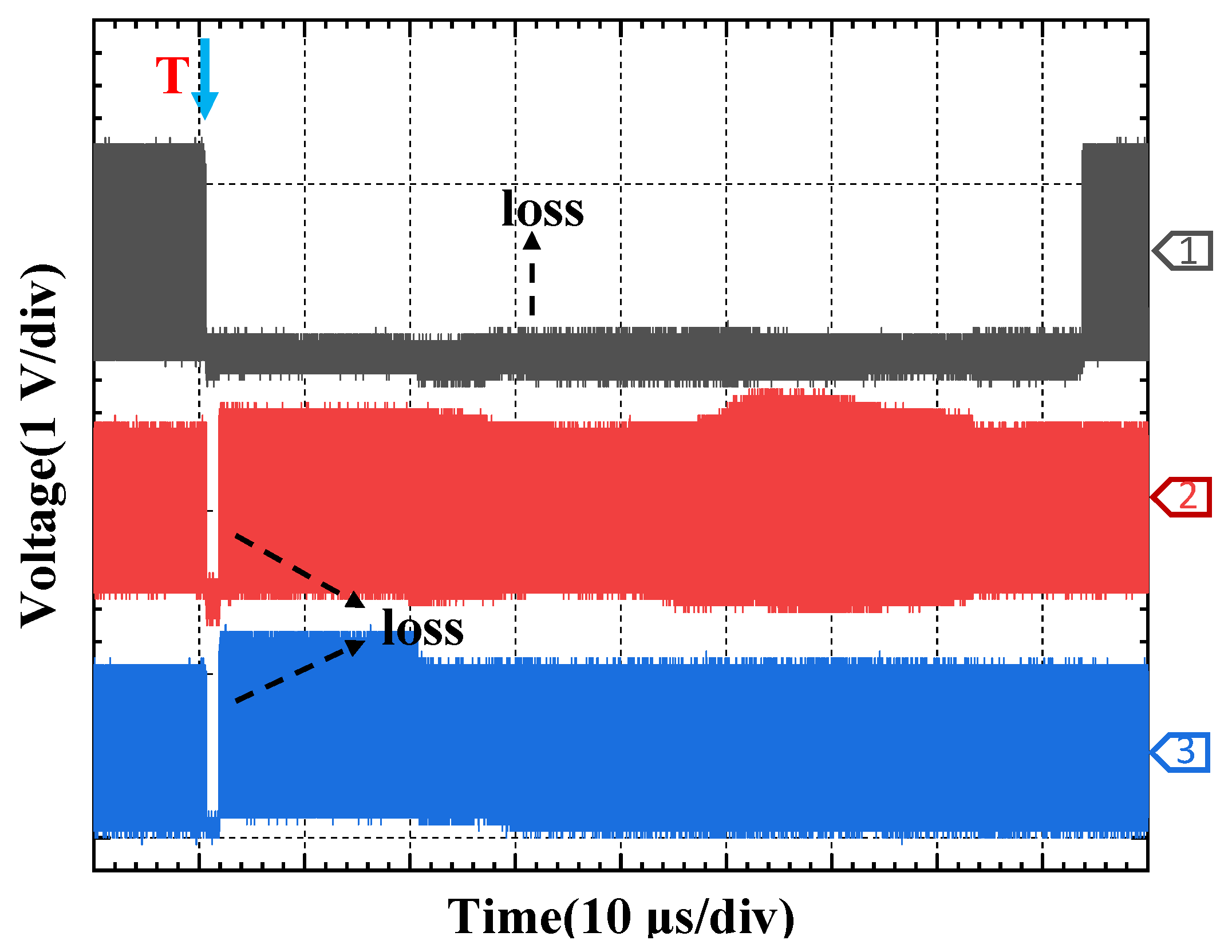

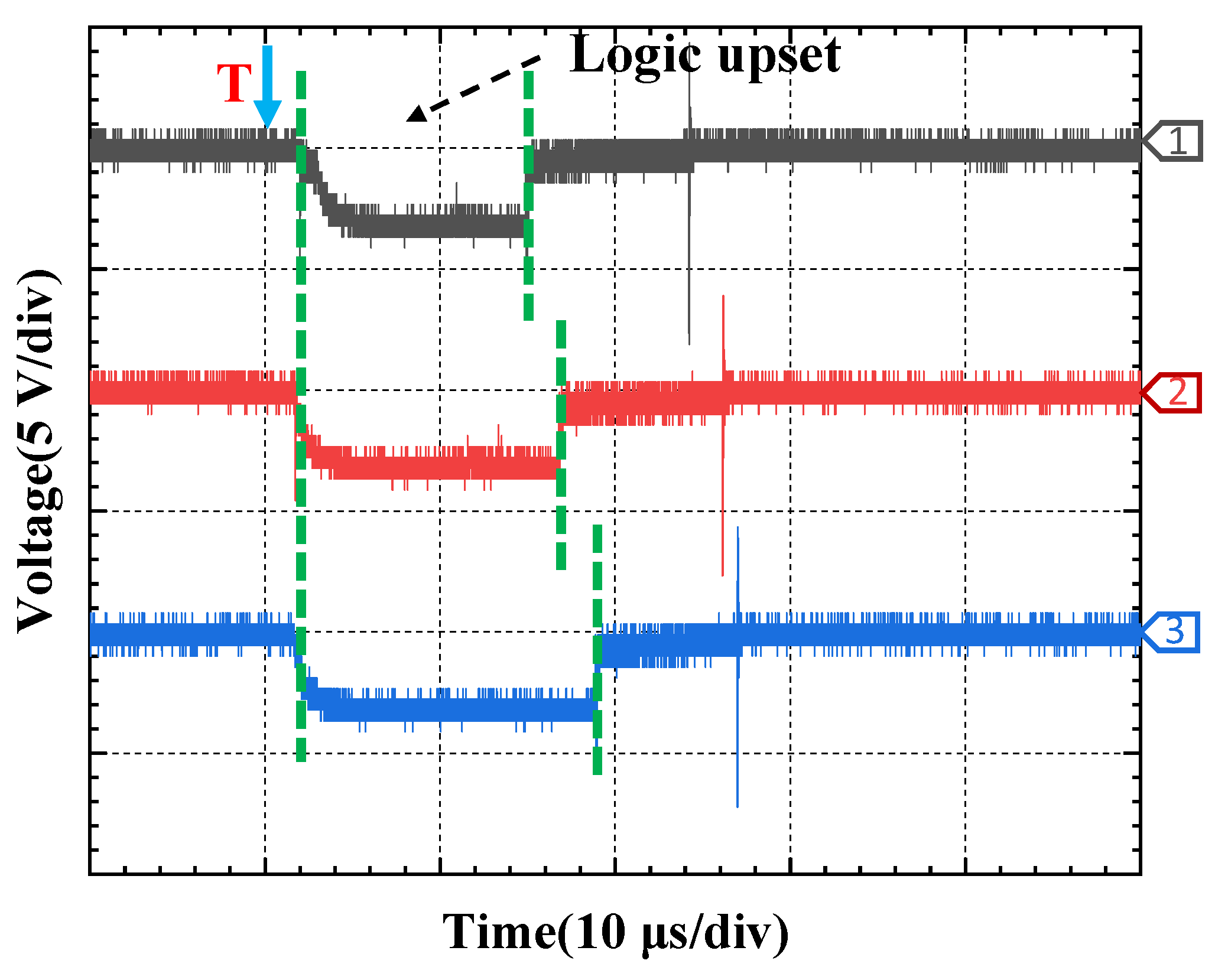

3.1.1. Injection into 1.8 V Power Line

3.1.2. Injection into 3.3 V Power Line

3.1.3. Injection into 2.5 V Power Line

3.2. The Comparison of PCIs of Different Polarities

3.2.1. Injection into 1.8 V Power Line

3.2.2. Injection into 3.3 V Power Line

3.2.3. Injection into 2.5 V Power Line

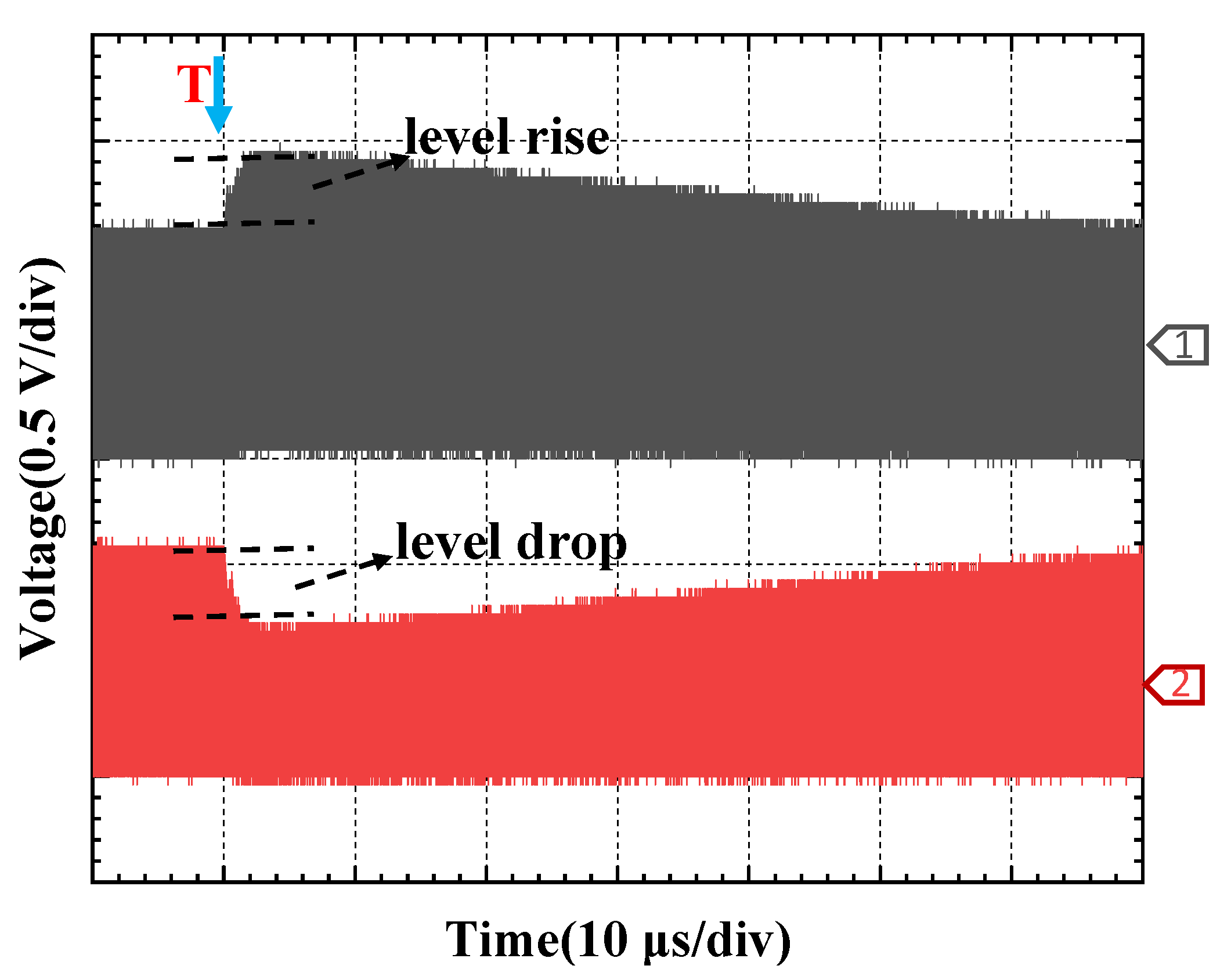

3.2.4. Injection into 1.1 V Power Line

3.3. The Comparison of JXCV5SX95T and XC5VSX95T

4. Discussion

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Fleetwood, D.M. Radiation Effects in a Post-Moore World. IEEE Trans. Nucl. Sci. 2021, 68, 509–545. [Google Scholar] [CrossRef]

- Darwish, M.N.; Dolly, M.C.; Goodwin, C.A.; Titus, J.L. Radiation Effects on Power Integrated Circuits. IEEE Trans. Nucl. Sci. 1988, 35, 1547–1551. [Google Scholar] [CrossRef]

- Bezhenova, V.; Michalowska-Forsyth, A.M. Effects of Ionizing Radiation on Integrated Circuits. Elektrotech. Inftech. 2016, 133, 39–42. [Google Scholar] [CrossRef]

- Ferlet-Cavrois, V.; Massengill, L.W.; Gouker, P. Single Event Transients in Digital CMOS—A Review. IEEE Trans. Nucl. Sci. 2013, 60, 1767–1790. [Google Scholar] [CrossRef]

- Lee, M.; Cho, S.; Lee, N.; Kim, J. Design for High Reliability of CMOS IC With Tolerance on Total Ionizing Dose Effect. IEEE Trans. Device Mater. Reliab. 2020, 20, 459–467. [Google Scholar] [CrossRef]

- Guo, Y.; Li, Y.; Li, J.; He, C.; Li, R.; Li, Y.; Li, P.; Liu, J. Experimental Study of Transient Dose Rate Effects of Two Level-Shifting Transceivers and Simulations on Their ESD Circuits. IEEE Trans. Nucl. Sci. 2022, 69, 1157–1166. [Google Scholar] [CrossRef]

- Hao, R.; Zhang, X.; Gao, H.; Wu, H.; Cheng, J.; Li, G.-P. A Novel High-Altitude Electromagnetic Pulse (HEMP) Protection Circuit for RF Applications. Microelectron. J. 2019, 84, 1–8. [Google Scholar] [CrossRef]

- Hoad, R.; Radasky, W.A. Progress in High-Altitude Electromagnetic Pulse (HEMP) Standardization. IEEE Trans. Electromagn. Compat. 2013, 55, 532–538. [Google Scholar] [CrossRef]

- Xie, H.; Liu, Y.; Li, Y.; Qiao, H. A Prediction Model Based on Artificial Neural Network for E1 HEMP Coupling With Distribution Power Lines. IEEE Trans. Power Deliv. 2022, 37, 5337–5344. [Google Scholar] [CrossRef]

- Giri, D.V.; Prather, W.D. High-Altitude Electromagnetic Pulse (HEMP) Risetime Evolution of Technology and Standards Exclusively for E1 Environment. IEEE Trans. Electromagn. Compat. 2013, 55, 484–491. [Google Scholar] [CrossRef]

- Li, C.; Liu, Y.; Liu, J.; Wei, A.; En, Y. Electromagnetic Interference Effects in the Bipolar Voltage Comparators. In Proceedings of the 10th International Conference on Reliability, Maintainability and Safety (ICRMS), Guangzhou, China, 6–8 August 2014; pp. 185–188. [Google Scholar]

- Feng, Y.; Sun, L.; Lu, J.; Li, Z.; Tian, J.; Qiu, Y. Equivalent Circuit and Damage Threshold Study of Communication Interfaces under HEMP. J. Electron. Test. 2024, 40, 615–624. [Google Scholar] [CrossRef]

- Du, C.; Xia, D.; Huang, Q.; Mao, C.; Cui, Z.; Fang, W.; Nie, X. Research on Electromagnetic Susceptibility of Electronic Modules in Component-Level HEMP PCI Test. Energies 2022, 15, 1409. [Google Scholar] [CrossRef]

- Li, B.; Boyer, A.; Bendhia, S.; Lemoine, C. Ageing Effect on Electromagnetic Susceptibility of a Phase Locked Loop. Microelectron. Reliab. 2010, 50, 1304–1308. [Google Scholar] [CrossRef]

- Kwak, S.; Nah, W.; Kim, S. Electromagnetic Susceptibility Analysis of I/O Buffers Using the Bulk Current Injection Method. J. Semicond. Technol. Sci. 2013, 13, 114–126. [Google Scholar] [CrossRef]

- Park, I.; Jang, I.; Jung, W.; Kim, S. Noise Immunity Modeling and Analysis of Delay-Locked Loop. In Proceedings of the 2015 IEEE 19th Workshop on Signal and Power Integrity (SPI), Berlin, Germany, 10 May 2015; pp. 1–4. [Google Scholar]

- Junping, C.; Changlin, Z.; Daojie, Y.; Zhijian, X.; Dongyao, Z. Electromagnetic susceptibility analysis of FPGA based on conducted coupling of power supply network. High Power Laser Part Beams 2019, 31, 023202–023207. [Google Scholar] [CrossRef]

- Swaminathan, M.; Chung, D.; Grivet-Talocia, S.; Bharath, K.; Laddha, V.; Xie, J. Designing and Modeling for Power Integrity. IEEE Trans. Electromagn. Compat. 2010, 52, 288–310. [Google Scholar] [CrossRef]

- Wu, T.-L.; Chuang, H.-H.; Wang, T.-K. Overview of Power Integrity Solutions on Package and PCB: Decoupling and EBG Isolation. IEEE Trans. Electromagn. Compat. 2010, 52, 346–356. [Google Scholar] [CrossRef]

- Jagadeesh, R.B.; Ramashastry, V.; Ramprasad, B.; Srihari, S.P.R.B.; Bhat, S.; Radhakrishna, V.S. IC Package with the System Board Interconnects—Simulation Showing PDN Noise Due to Simultaneous Switching IOs and Its Effect on Signal Integrity. In Proceedings of the 2022 IEEE Electrical Design of Advanced Packaging and Systems (EDAPS), Urbana, IL, USA, 12–14 December 2022; pp. 1–3. [Google Scholar]

- Wu, P.; Xu, Z.; Meng, C.; Wen, L.; Guo, Q. The Experiment Study of Effects on ADC Chip against Radiation and Electromagnetic Environment. In Proceedings of the 12th International Workshop on the Electromagnetic Compatibility of Integrated Circuits (EMC Compo), Hangzhou, China, 1 October 2019; pp. 207–209. [Google Scholar]

- Xu, X.-C.; Han, C.-Y.; Shao, E.; Lu, X.-J.; Fang, W.-X.; Chen, R.-Q.; Liu, H.-Z.; Shao, W.-H.; Shi, Y.-L. Study of the HPM Interference Effect on Integrated Circuit in a TEM Cell. In Proceedings of the 2019 International Conference on Quality, Reliability, Risk, Maintenance, and Safety Engineering (QR2MSE), Zhangjiajie, China, 6–9 August 2019; pp. 1–7. [Google Scholar]

- Zhou, Y.; Xie, Y.-Z.; Zhang, D.-Z.; Jing, Y. Modeling and Performance Evaluation of Inductive Couplers for Pulsed Current Injection. IEEE Trans. Electromagn. Compat. 2021, 63, 710–719. [Google Scholar] [CrossRef]

- Cui, Z.; Grassi, F.; Pignari, S.A.; Wei, B. Pulsed Current Injection Setup and Procedure to Reproduce Intense Transient Electromagnetic Disturbances. IEEE Trans. Electromagn. Compat. 2018, 60, 2065–2068. [Google Scholar] [CrossRef]

- XC5VSX95T-1FF1136C Xilinx Inc.|Integrated Circuits (ICs)|DigiKey. Available online: https://www.digikey.com/en/products/detail/amd/XC5VSX95T-1FFG1136C/1768662 (accessed on 22 June 2022).

- Vera, A.; Llamocca, D.; Pattichis, M.; Kemp, W.; Shedd, W.; Alexander, D.; Lyke, J. Dose Rate Upset Investigations on the Xilinx Virtex IV Field Programmable Gate Arrays. In Proceedings of the 2007 IEEE Radiation Effects Data Workshop, Honolulu, HI, USA, 23–27 July 2007; pp. 172–176. [Google Scholar]

- Vera, A.; Llamocca, D.; Fabula, J.; Kemp, W.; Marquez, R.; Shedd, W.; Alexander, D. Xilinx Virtex V Field Programmable Gate Array Dose Rate Upset Investigations. In Proceedings of the 2008 IEEE Radiation Effects Data Workshop, Tucson, AZ, USA, 14–18 July 2008; pp. 90–93. [Google Scholar]

- Li, Y.; Li, J.; Guo, Y.; He, C.; Li, R.; Chen, W.; Liao, W.; Li, Y.; Li, P.; Liu, J.; et al. Experimental Study of Transient Dose Rate Effect on System-in-Package SZ0501. IEEE Trans. Nucl. Sci. 2022, 69, 1840–1849. [Google Scholar] [CrossRef]

- Li, Y.; Guo, Y.; Li, J.; He, C.; Peng, Z.; Liu, J.; Li, R.; Zhao, H.; Chen, W.; Li, Y.; et al. Transient Dose Rate Effect Between System-in-Package and Printed Circuit Boards: A Comparative Experimental Study. IEEE Trans. Nucl. Sci. 2023, 70, 2106–2115. [Google Scholar] [CrossRef]

- Zhou, Y.; Xie, Y.; Zhang, D. Performance Evaluation of Inductive and Capacitive Couplers for Pulsed Current Injection. IEEE Trans. Electromagn. Compat. 2022, 64, 85–91. [Google Scholar] [CrossRef]

- Tang, K.T.; Friedman, E.G. Simultaneous Switching Noise in On-Chip CMOS Power Distribution Networks. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2002, 10, 487–493. [Google Scholar] [CrossRef]

- Li, N.; Li, Y.; Guo, Y.; He, C. Simulation Analysis of Electromagnetic Pulse Susceptibility and Hardening Design for System-in-Package SZ0501. Microelectron. Reliab. 2023, 141, 114892. [Google Scholar] [CrossRef]

- Li, J.; Li, Y.; Guo, Y.; Li, R.; Chen, W.; Liu, Y.; Peng, Z.; Liu, J.; He, C.; Li, P. Investigation of Transient Dose-Rate Effect on High-Speed Comparator SB9696. IEEE Trans. Nucl. Sci. 2023, 70, 1459–1469. [Google Scholar] [CrossRef]

- Shenglong, W.; Ling, S.; Haiyan, S.; Lingling, Y.; Boyuan, Z.; Junwei, L. Relationship between SSN and EMC in SiP. In Proceedings of the 14th International Conference on Electronic Packaging Technology, Dalian, China, 11–14 August 2013; pp. 622–625. [Google Scholar]

| Failure Stages | Failure Thresholds/A |

|---|---|

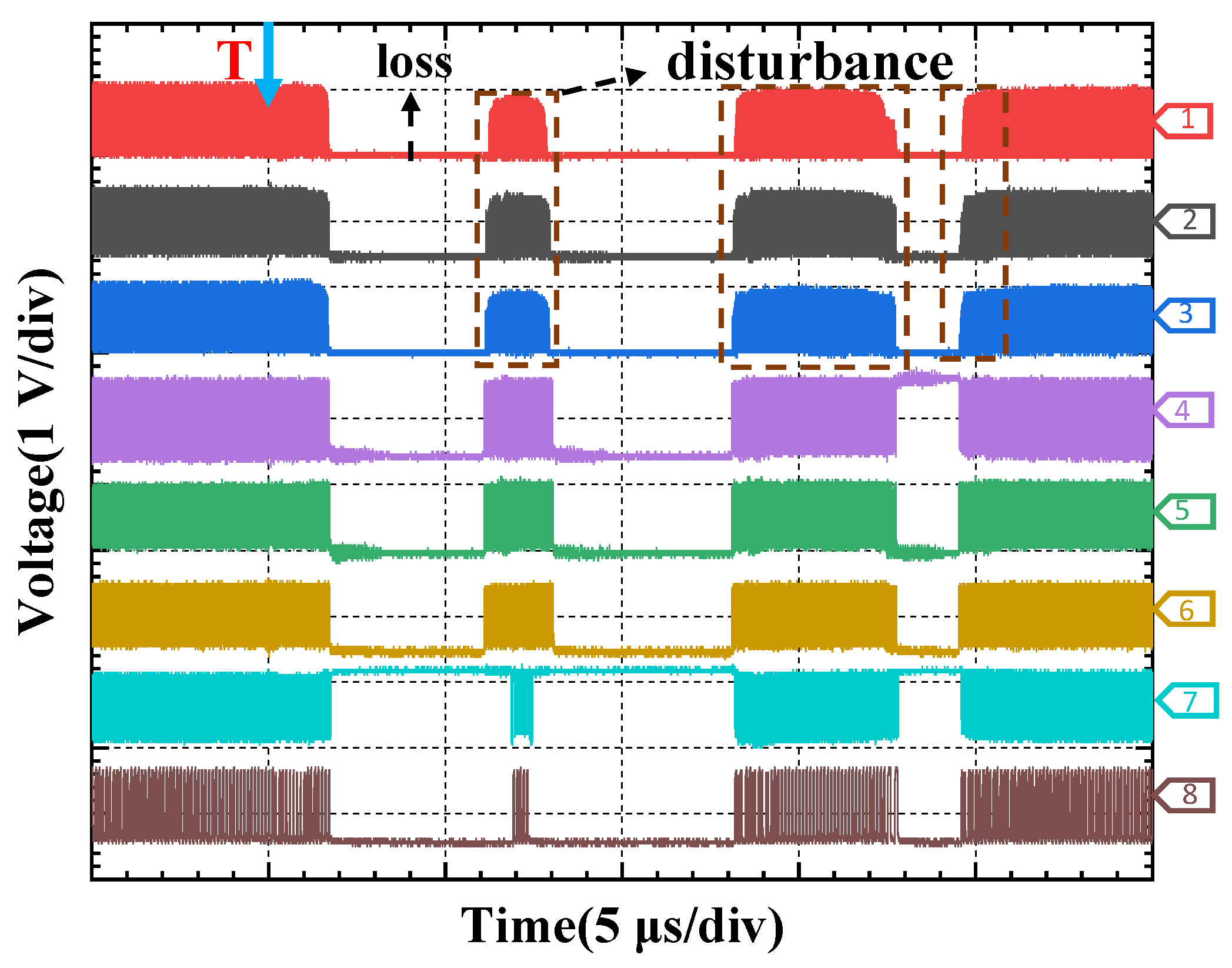

| FPGA IO 50 MHz, FPGA GCB 50 MHz, and ADC_CLK 50 MHz have disturbances simultaneously. | 72.9 |

| All HF outputs, except for DAC_SYNC_OUT, have a period of loss simultaneously. | 75.3 |

| HF Outputs | Injection Amplitude/A |

|---|---|

| FPGA DLL + BUFG 25 MHz | 58.1 |

| FPGA DLL + BUFG 50 MHz | 62.4 |

| FPGA DLL + BUFG 100 MHz | 64.9 |

| Failure Stages | Failure Thresholds/A |

|---|---|

| The constant high output (5 V) of bus driver has a temporary logic upset. | −97.5 |

| FPGA IO 50 MHz, FPGA GCB 50 MHz, and ADC_CLK 50 MHz have disturbances at the same time. | −100 |

| HF outputs except DAC_SYNC_OUT have a period of loss at the same time. | −110 |

| JXCV5SX95T loses all functions and is automatically reconfigured after a few seconds. | −126 |

| HF Outputs | Failure Thresholds/A |

|---|---|

| FPGA DLL + BUFG 100 MHz | −43.6 |

| FPGA PLL + BUFG 100 MHz | −43.6 |

| FPGA PLL + BUFG 50 MHz | −49.2 |

| DAC_SYNC_OUT 50 MHz | −49.2 |

| FPGA DLL + BUFG 50 MHz | −50.1 |

| FPGA BUFG 50 MHz | −50.1 |

| ADC_CLK 50 MHz | −51 |

| FPGA DLL + BUFG 25 MHz | −54.7 |

| FPGA PLL + BUFG 25 MHz | −55.7 |

| Failure Stages | Failure Thresholds/A |

|---|---|

| 100 MHz HF signals are lost for a period. | −77.8 |

| 50 MHz HF signals are lost for a period. | −80.2 |

| 25 MHz HF signals are lost for a period. | −83.2 |

| ADC sine-to-square (10 MHz) signals are lost for a period. | −83.9 |

| Power Line | Injection Polarity | Comparison of the Two FPGAs |

|---|---|---|

| 1.8 V 3.3 V 2.5 V | Positive Negative | The two FPGAs have the same failure characteristics but different failure thresholds. |

| 1.1 V | Positive | The two FPGAs have no output fault. |

| Negative | The two FPGAs have different failure characteristics and thresholds. |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Li, N.; Peng, Z.; Mao, C.; Qin, F.; Li, Y.; Li, Y.; Li, P.; Yang, W.; Bai, H.; Liang, J.; et al. Experimental Study on Electromagnetic Pulse Sensitivity for Power Modules of FPGAs. Electronics 2025, 14, 1167. https://doi.org/10.3390/electronics14061167

Li N, Peng Z, Mao C, Qin F, Li Y, Li Y, Li P, Yang W, Bai H, Liang J, et al. Experimental Study on Electromagnetic Pulse Sensitivity for Power Modules of FPGAs. Electronics. 2025; 14(6):1167. https://doi.org/10.3390/electronics14061167

Chicago/Turabian StyleLi, Ning, Zhigang Peng, Congguang Mao, Feng Qin, Yang Li, Yonghong Li, Pei Li, Weitao Yang, Haojie Bai, Jiayu Liang, and et al. 2025. "Experimental Study on Electromagnetic Pulse Sensitivity for Power Modules of FPGAs" Electronics 14, no. 6: 1167. https://doi.org/10.3390/electronics14061167

APA StyleLi, N., Peng, Z., Mao, C., Qin, F., Li, Y., Li, Y., Li, P., Yang, W., Bai, H., Liang, J., Hong, B., & He, C. (2025). Experimental Study on Electromagnetic Pulse Sensitivity for Power Modules of FPGAs. Electronics, 14(6), 1167. https://doi.org/10.3390/electronics14061167