A Control Technique for Galvanically Isolated DC–DC Converters with a Single Channel

Abstract

1. Introduction

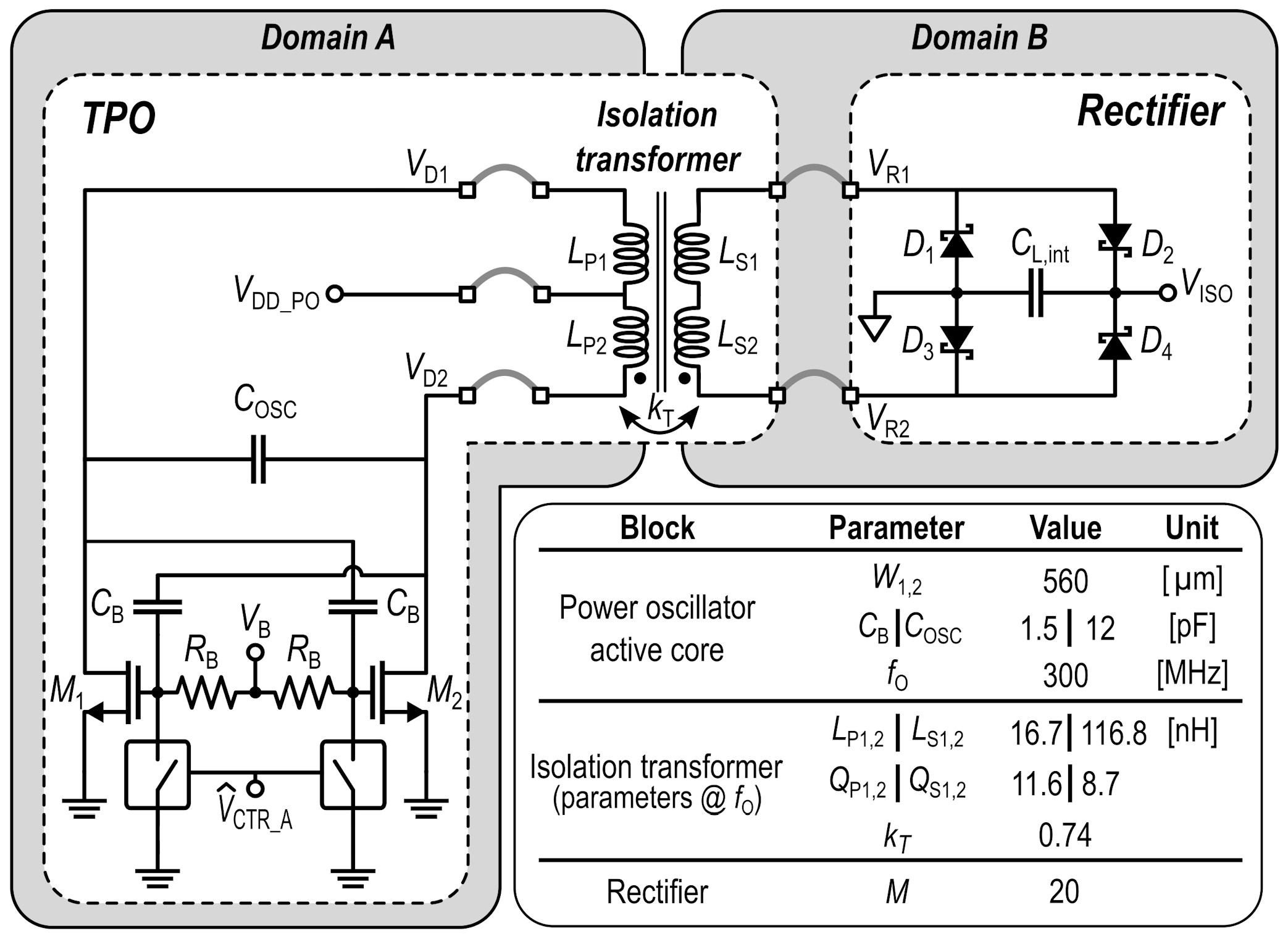

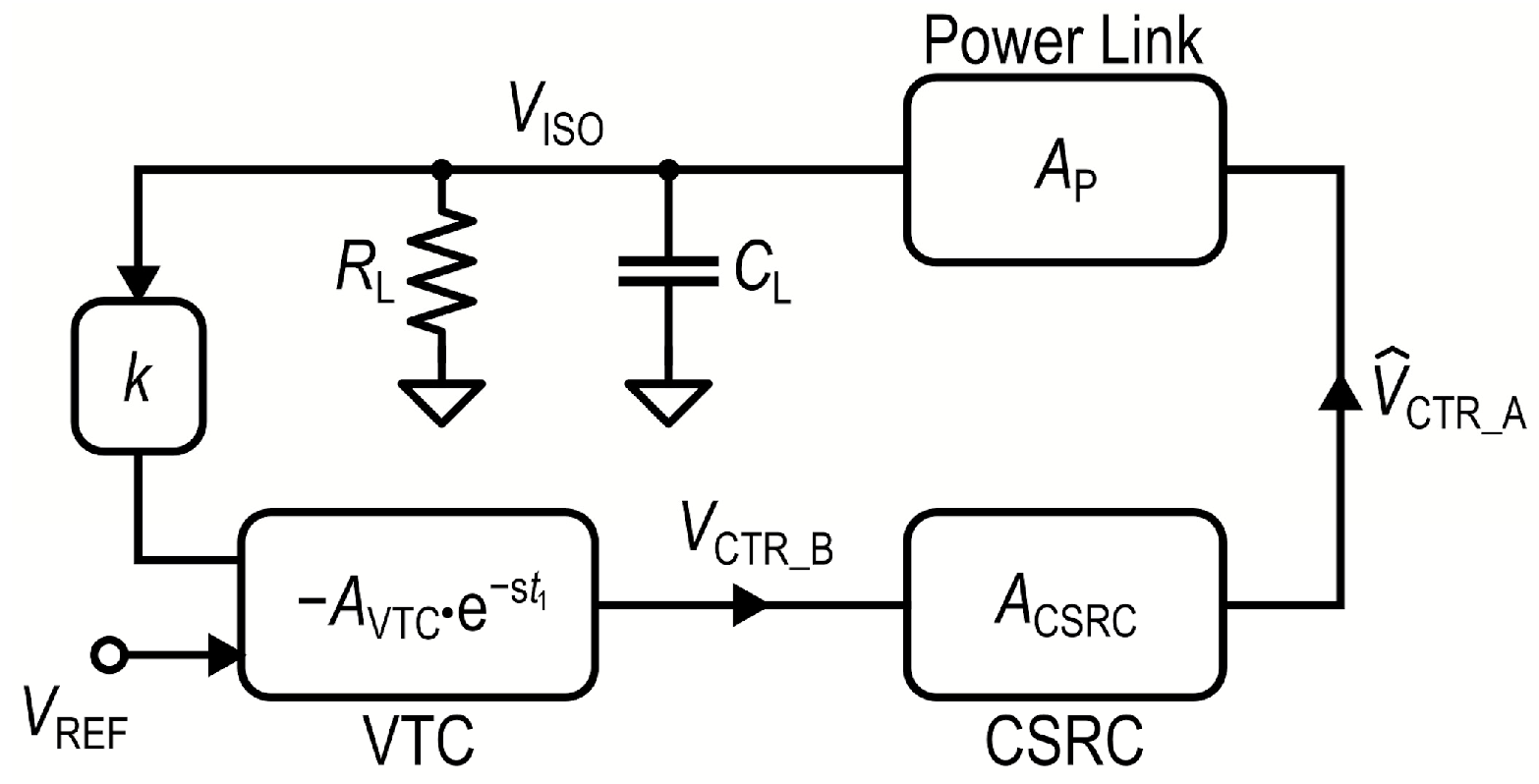

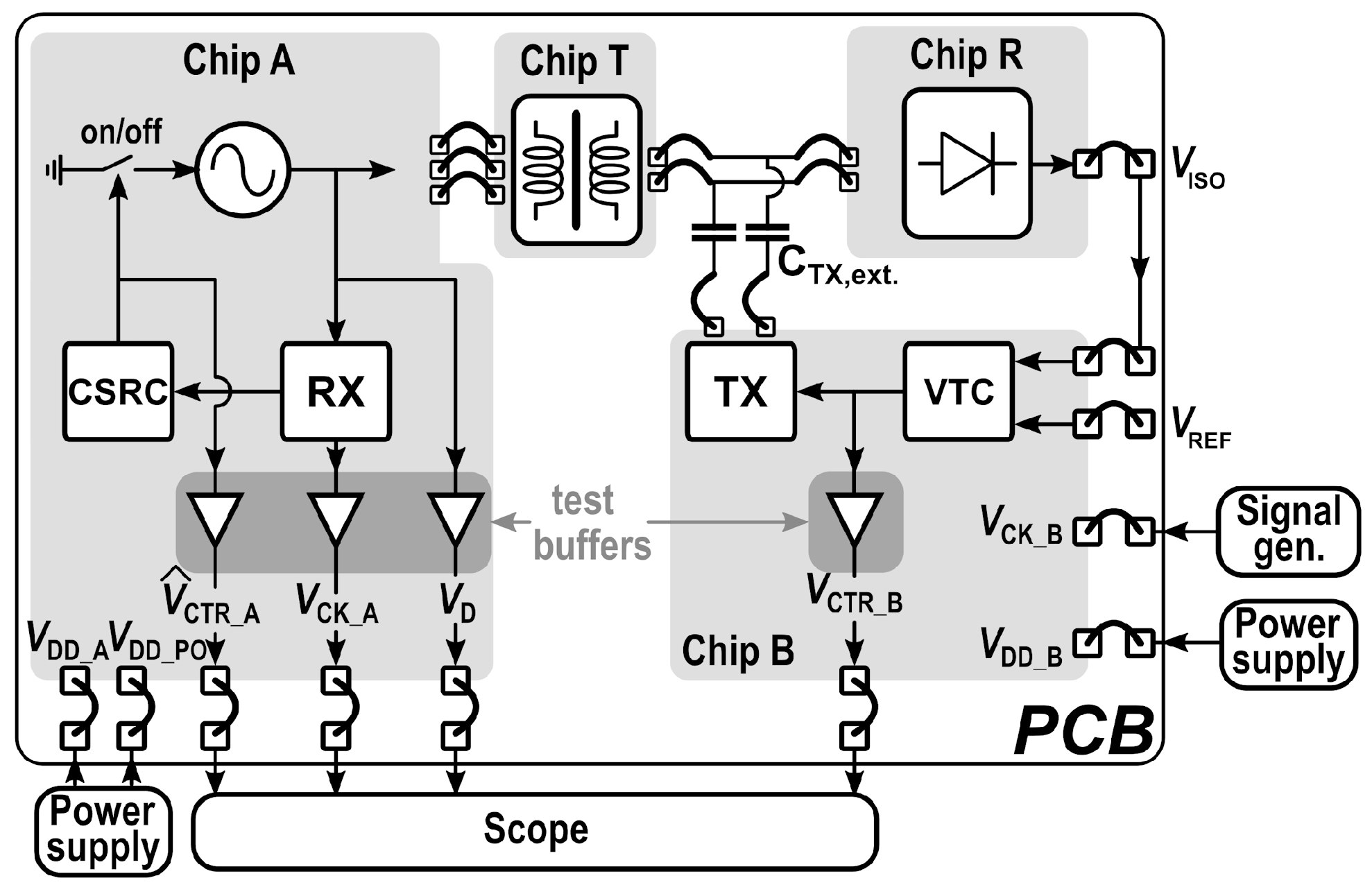

2. System Description

3. System Design

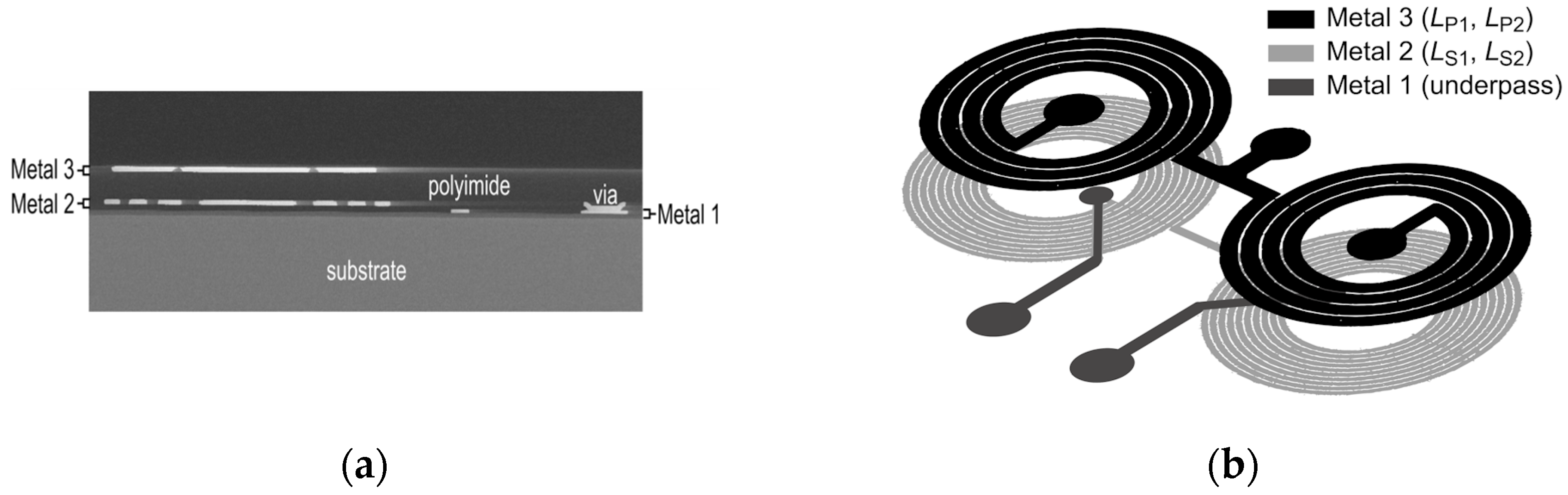

3.1. Power Link and Isolation Transformer

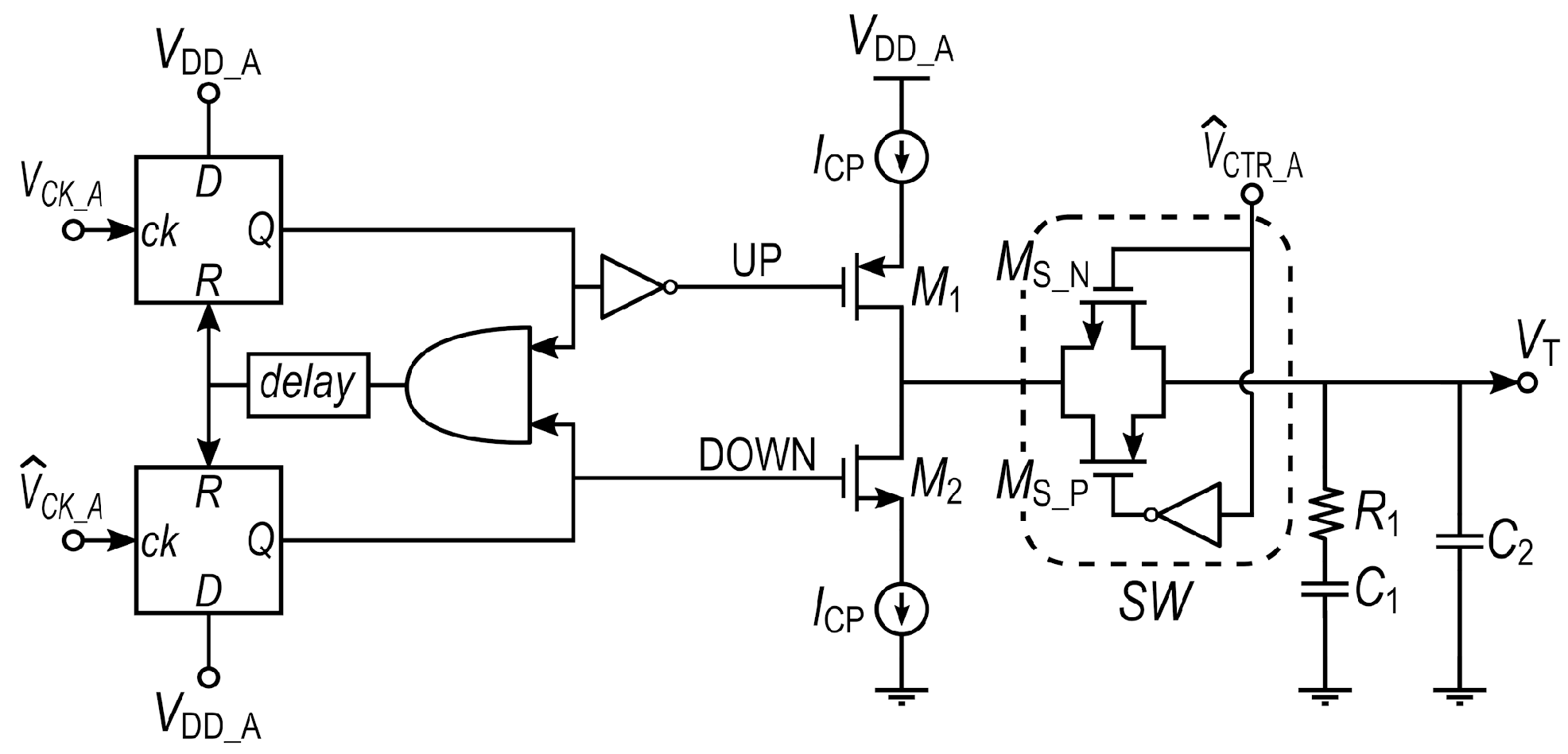

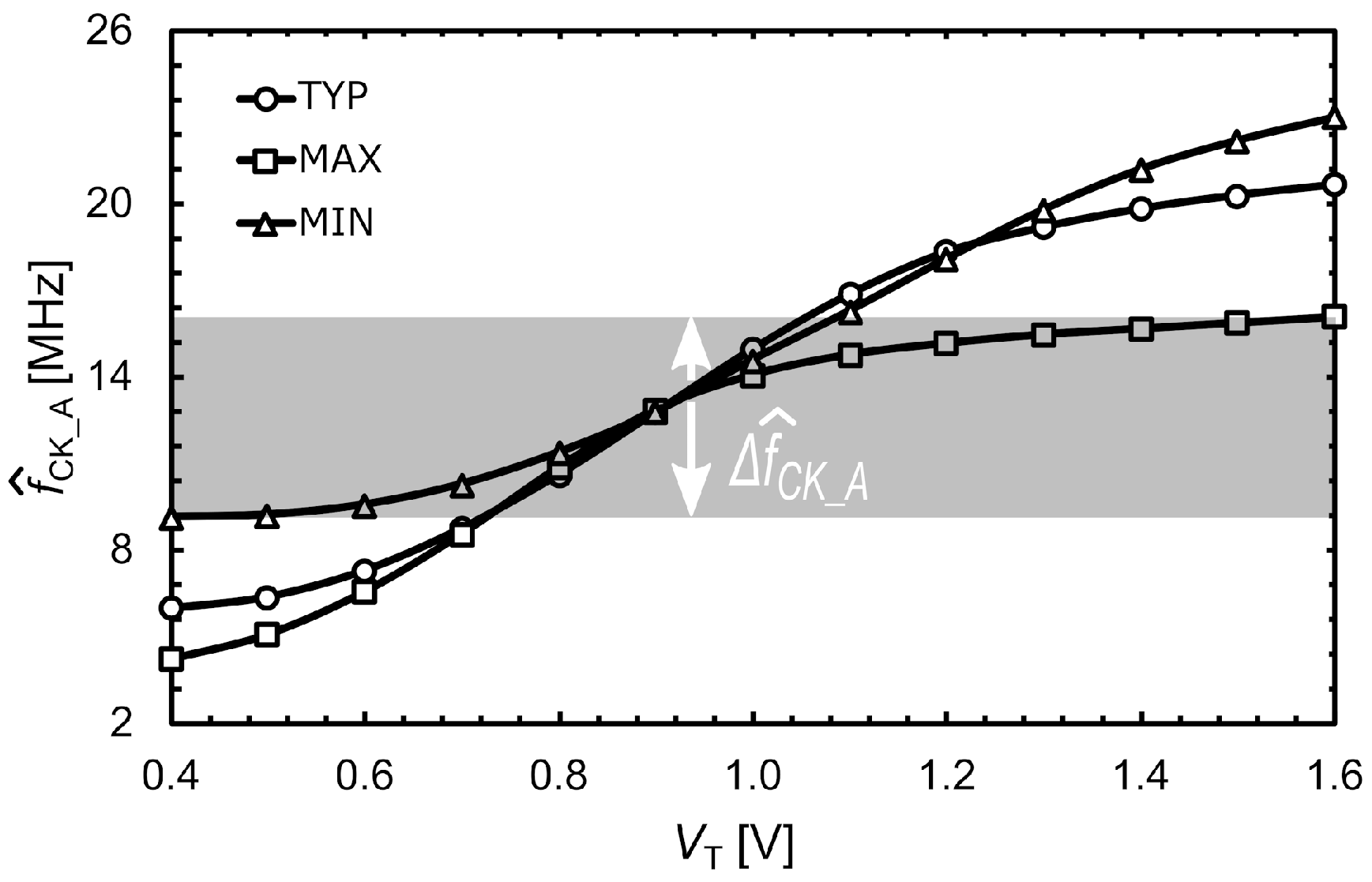

3.2. Control Link

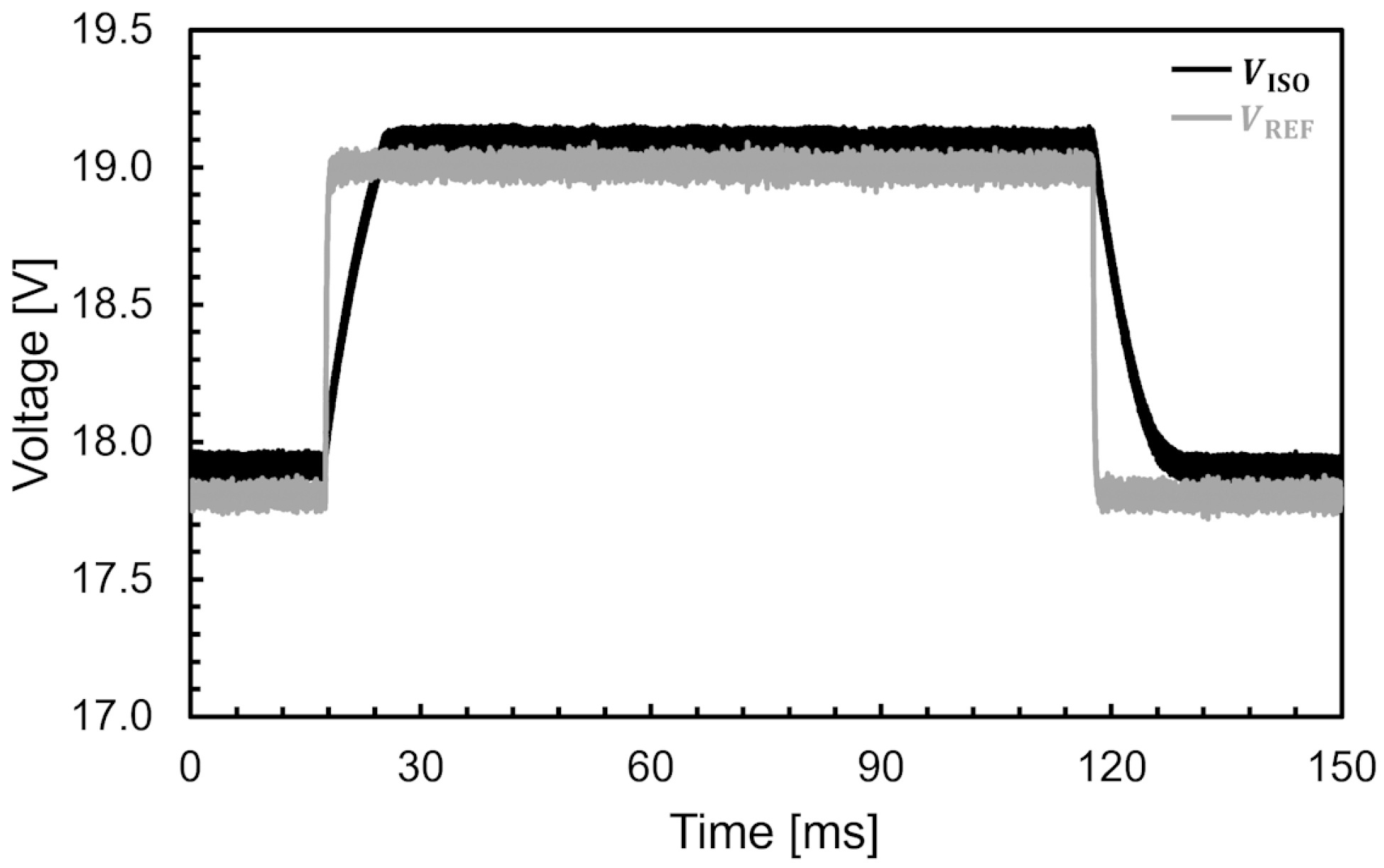

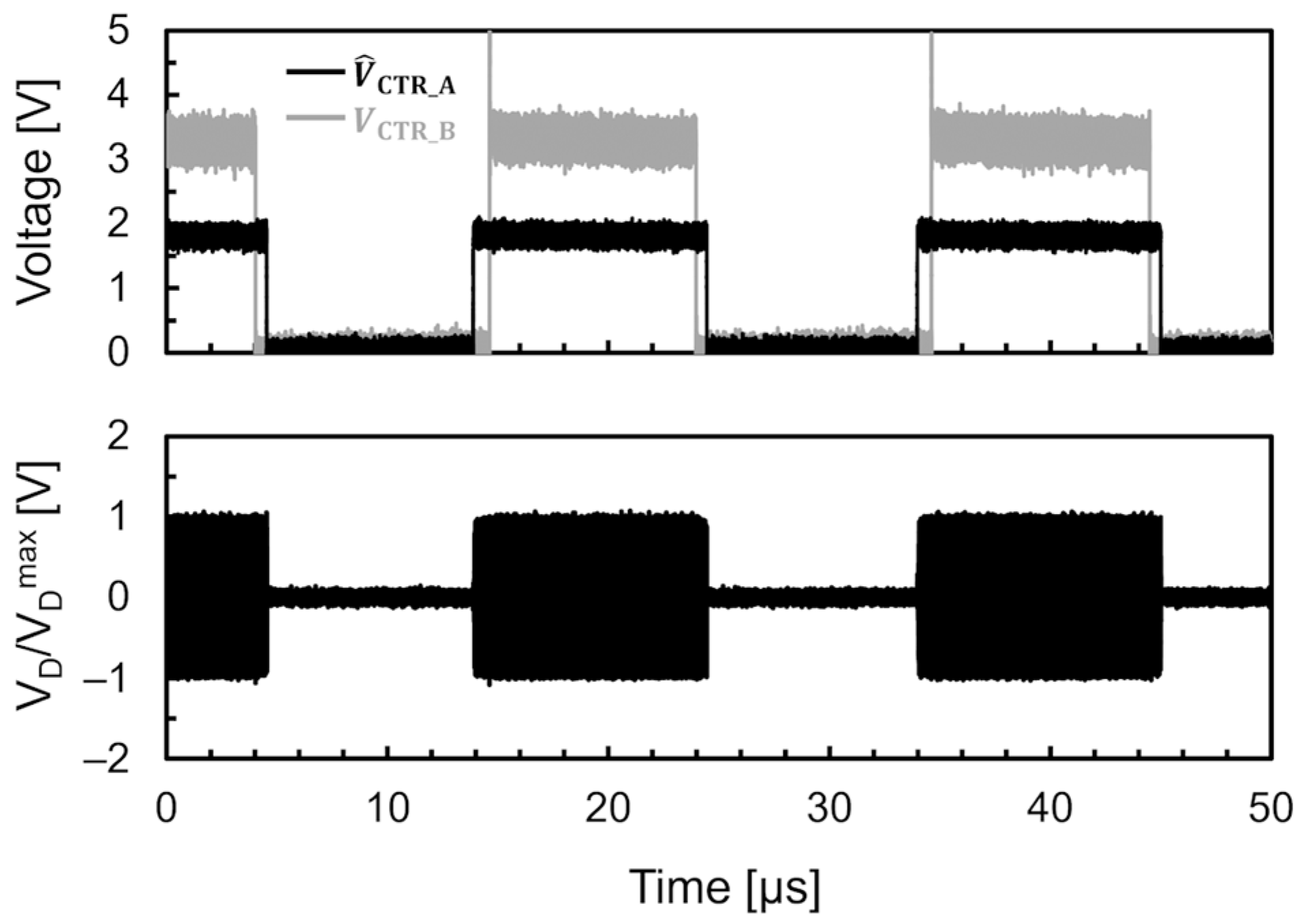

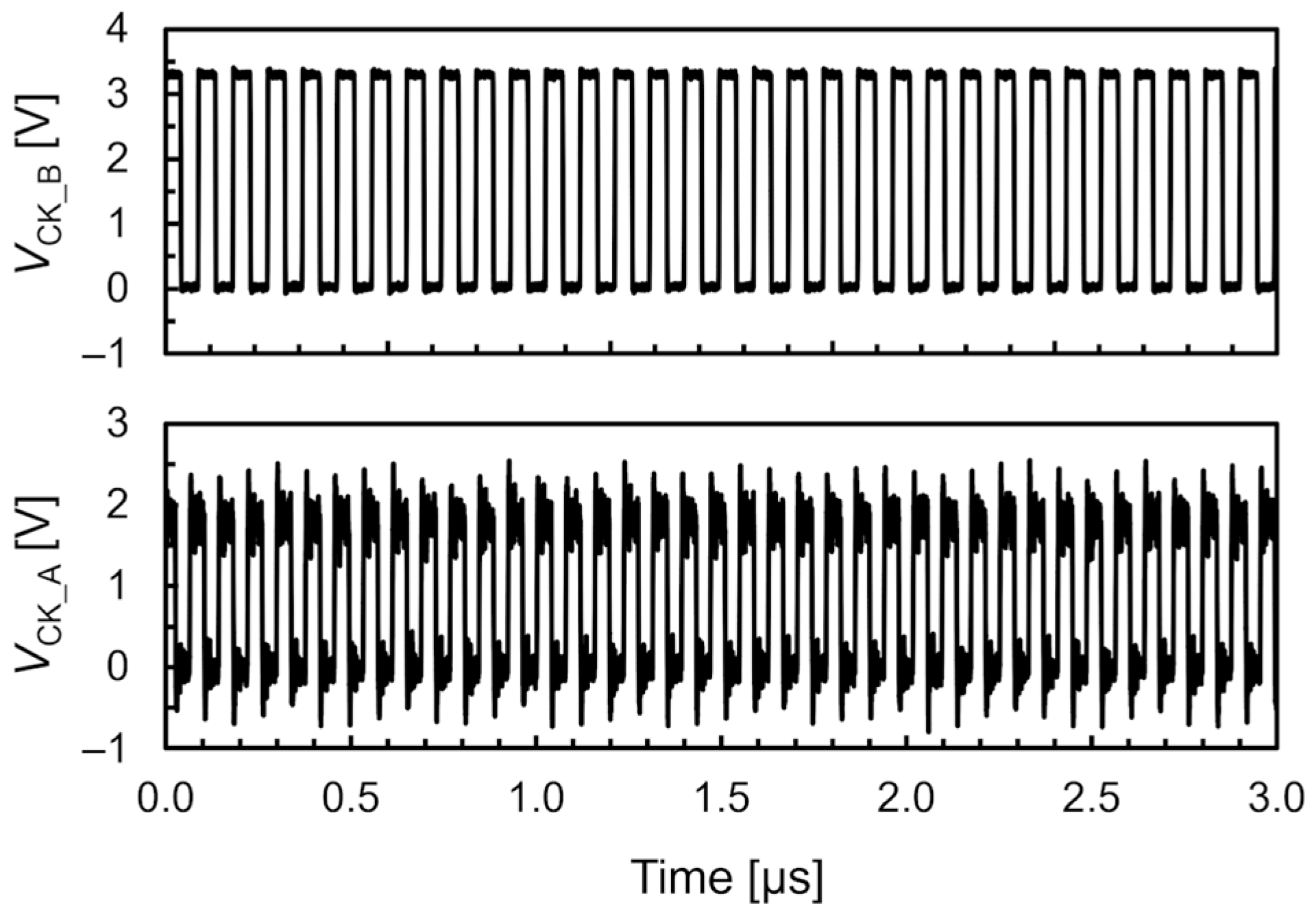

4. Experimental Results

5. Conclusions

6. Patents

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Analog Devices. Surging Across the Barrier: Digital Isolators Set the Standard for Reinforced Insulation. Available online: https://www.analog.com/en/resources/technical-articles/digital-isolators-set-the-standard-for-reinforced-insulation.html (accessed on 27 March 2025).

- NVE Corporation. Isolator High Voltage Safety Standards. 2024. Available online: https://www.nve.com (accessed on 28 March 2025).

- Maniar, K.; Mappus, S.; Merkin, T.; Triano, A.; Trowbridge, L. Addressing High-Voltage Design Challenges with Reliable and Affordable Isolation Technologies. Available online: https://www.ti.com/lit/wp/slyy204c/slyy204c.pdf (accessed on 28 March 2025).

- Krone, A.; Tuttle, T.; Scott, J.; Hein, J.; Dupuis, T.; Sooch, N. A CMOS direct access arrangement using digital capacitive isolation. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 7 February 2001; pp. 300–301. [Google Scholar]

- Kaeriyama, S.; Uchida, S.; Furumiya, M.; Okada, M.; Maeda, T.; Mizuno, M. A 2.5 kV isolation 35 kV/us CMR 250 Mbps digital isolator in standard CMOS with a small transformer driving technique. IEEE J. Solid-State Circuits 2012, 47, 435–443. [Google Scholar]

- Ma, S.; Feng, J.; Zhao, T.; Chen, B. A fully isolated amplifier based on charge-balanced SAR converters. IEEE Trans. Circuits Syst. I Reg. Papers 2018, 65, 1795–1804. [Google Scholar]

- DIN VDE Semiconductor Devices-Magnetic and Capacitive Coupler for Basic and Reinforced Isolation, VDE Verlag VDE V 0884–11, January 2017. Available online: https://www.vde-verlag.de/standards/0800375/din-vde-v-0884-11-vde-v-0884-11-2017-01.h (accessed on 28 March 2025).

- Chen, B. iCoupler Products with isoPower Technology: Signal and Power Transfer Across Isolation Barrier Using Microtransformers. Analog Devices, Norwood, MA, USA, Tech. Rep. Available online: https://www.analog.com/en/resources/technical-articles/icoupler-products-with-isopower-technology.html (accessed on 28 March 2025).

- Chen, B. Fully integrated isolated DC-DC converter using micro transformers. In Proceedings of the IEEE Applied Power Electronics Conference and Exposition (APEC), Austin, TX, USA, 24–28 February 2008; pp. 335–338. [Google Scholar]

- Qin, W.; Yang, X.; Ma, S.; Liu, F.; Zhao, Y.; Zhao, T.; Chen, B. An 800 mW fully integrated galvanic isolated power transfer system meeting CISPR 22 Class-B emission levels with 6 dB margin. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 17–21 February 2019; pp. 246–248. [Google Scholar]

- Tianting, Z.; Yue, Z.; Baoxing, C. An isolated DC-DC converter with fully integrated magnetic core transformer. In Proceedings of the IEEE Custom Integrated Circuits Conference (CICC), Austin, TX, USA, 30 April–3 May 2017; pp. 1–4. [Google Scholar]

- Chen, B. Isolated half-bridge gate driver with integrated high-side supply. In Proceedings of the IEEE Power Electronics Specialists Conference (PESC), 15–19 June 2008; pp. 3615–3618. [Google Scholar]

- Kamath, A.S.; Soundarapandian, K. High-Voltage Reinforced Isolation: Definitions and Test Methodologies. Texas Instrum., Dallas, TX, USA, Tech. Rep. November 2014. Available online: https://www.ti.com/lit/wp/slyy063/slyy063.pdf?ts=1741590137990 (accessed on 28 March 2025).

- Chen, B. High Frequency Power Converter Based on Transformers. U.S. Patent 7983059B2, 19 July 2011. [Google Scholar]

- Palumbo, V.; Ghidini, G.; Carollo, E.; Toia, F. INTEGRATED Transformer. U.S. Patent 10236115B2, 19 March 2019. [Google Scholar]

- Moghe, Y.; Terry, A.; Luzon, D. Monolithic 2.5 kV RMS, 1.8 V–3.3 V dual-channel 640Mbps digital isolator in 0.5 μm SOS. In Proceedings of the IEEE International SOI Conference, Napa, CA, USA, 1–4 October 2012; pp. 1–2. [Google Scholar]

- Pan, D.; Xiong, Z.; Lu, Q.; Miao, F.; Wu, L.; Cheng, L. A 250-Mb/s on-chip capacitive digital isolator with adaptive frequency control. IEEE Solid-State Circuits Lett. 2024, 7, 231–234. [Google Scholar]

- Texas Instruments. ISO7841x High-Performance, 8000-VPK Reinforced Quad-Channel Digital Isolator. Available online: http://www.ti.com (accessed on 28 March 2025).

- TI. Isolated Gate Drivers. Available online: https://www.ti.com/power-management/gate-drivers/isolated-gate-drivers/overview.html (accessed on 29 August 2021).

- Mahalingam, P.; Guiling, D.; Lee, S. Manufacturing challenges and method of fabrication of on-chip capacitive digital isolators. In Proceedings of the International Symposium on Semiconductor Manufacturing, Santa Clara, CA, USA, 15–17 October 2007; pp. 1–4. [Google Scholar]

- Analog Devices. ADuM6200-Dual-Channel, 5 kV Isolators with Integrated DC-to-DC Converter Datasheet. 2020. Available online: http://www.analog.com (accessed on 28 March 2025).

- Tan, Z.; Mueck, M.; Du, X.H.; Getzin, L.; Guidry, M.; Keating, S.; Xing, X.; Chen, B. A fully isolated delta-sigma ADC for shunt based current sensing. IEEE J. Solid-State Circuits 2016, 51, 2232–2240. [Google Scholar] [CrossRef]

- Ragonese, E.; Spina, N.; Castorina, A.; Lombardo, P.; Greco, N.; Parisi, A.; Palmisano, G. A fully integrated galvanically isolated DC-DC converter with data communication. IEEE Trans. Circuits Syst. I Reg. Papers 2018, 65, 1432–1441. [Google Scholar]

- Lombardo, P.; Fiore, V.; Ragonese, E.; Palmisano, G. A fully integrated half-duplex data/power transfer system with up to 40 Mb/s data rate, 23mW output power and on-chip 5 kV galvanic isolation. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 31 January–4 February 2016; pp. 300–301. [Google Scholar]

- Parisi, A.; Ragonese, E.; Spina, N.; Palmisano, G. Galvanically isolated DC–DC converter using a single isolation transformer for multi-channel communication. IEEE Trans. Circuits Syst. I Reg. Papers 2020, 67, 4434–4444. [Google Scholar]

- Hu, T.; Huang, M.; Martins, R.P.; Lu, Y. A 750 mW, 37% peak efficiency isolated DC–DC converter with 54/18Mb/s full-duplex communication using a single pair of transformers. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 18–22 February 2024; pp. 504–506. [Google Scholar]

- Hu, T.; Lu, Y.; Martins, R.P.; Huang, M. An isolated DC–DC converter with full-duplex communication using a single pair of transformers. IEEE J. Solid-State Circuits 2024. early access. [Google Scholar] [CrossRef]

- Fanori, L.; Andreani, P. Class-D CMOS oscillators. IEEE J. Solid-State Circuits 2013, 48, 3105–3119. [Google Scholar] [CrossRef]

- Lee, H.-C.; Jang, S.-L.; Wang, Y.-C. Fully-integrated capacitive cross-coupled class-D oscillator with frequency doubler. In Proceedings of the 2020 International Workshop on Electromagnetics: Applications and Student Innovation Competition (iWEM), Makung, Taiwan, 26–28 August 2020; pp. 1–2. [Google Scholar]

- Yun, R.; Sun, J.; Gaalaas, E.; Chen, B. A transformer-based digital isolator with 20kVPK surge capability and >200 kV/μS common mode transient immunity. In Proceedings of the IEEE Symposium on VLSI Circuits (VLSI-Circuits), Honolulu, HI, USA, 15–17 June 2016; pp. 1–2. [Google Scholar]

- Greco, N.; Parisi, A.; Spina, N.; Ragonese, E.; Palmisano, G. Scalable lumped models of integrated transformers for galvanically isolated power transfer systems. Integration 2018, 63, 323–331. [Google Scholar]

- Ragonese, E.; Spina, N.; Parisi, A.; Palmisano, G. An experimental comparison of galvanically isolated DC-DC converters: Isolation technology and integration approach. Electronics 2021, 10, 1186. [Google Scholar] [CrossRef]

- Ishihara, H.; Onizuka, K. A fully-generic-process galvanic isolator for gate driver with 123 mW 23% power transfer and full-triplex 21/14/0.5 Mb/s bidirectional communication utilizing reference-free dual-modulation FSK. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 16–20 February 2020; pp. 300–301. [Google Scholar]

- Li, L.; Fang, X.; Wu, R. An 11 MHz fully integrated 5 kV isolated DC-DC converter without cross-isolation-barrier feedback. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 16–20 February 2020; pp. 292–294. [Google Scholar]

| Parameters | Primary Coil | Secondary Coil |

|---|---|---|

| Number of turns (n) | 3.75 | 10 |

| Metal width (w) [µm] | 37 | 9.8 |

| Metal spacing (s) [µm] | 9.5 | 9.5 |

| Internal diameter (dIN) [µm] | 300 | 300 |

| Outer diameter (dOUT) [µm] | 676 | 686 |

| Block | Parameter | Value | Unit |

|---|---|---|---|

| Charge pump | ICP | 1 | µA |

| Switch, SW | W/LMS_P | 470/180 | nm/nm |

| W/LMS_N | 280/180 | nm/nm | |

| R1 | 290 | kΩ | |

| Loop filter | C1 | 10 | pF |

| C2 | 0.5 | pF | |

| Voltage-controlled oscillator | CVCO | 300 | fF |

| R1 | 21.5 | kΩ | |

| R2 | 77.5 | kΩ | |

| W/LMR | 0.28/0.4 | µm/µm | |

| W/LMINV,N | 1.4/180 | µm/nm | |

| W/LMINV,P | 2/180 | µm/nm |

| Parameters | [23] | [25] | [33] | [34] | This Work |

|---|---|---|---|---|---|

| Supply voltage [V] | 3.3 | 5 * | 5.5 | 3.3 | 5 * |

| Isolated output voltage [V] | 3.3 | 3.3 | 4 | 3.3 | 20 |

| Max. output power [mW] | 93 | 50 | 123 | 165 | 110 |

| Power efficiency [%] | 19 | 14 | 23 | 34 | 17 |

| Oscillation frequency [MHz] | 350 | 300 | ≈100 | 11 | 270 |

| Control scheme/frequency [kHz] | PWM/100 | Continuous time | n.a. ** | Open-loop capacitor-based controller | PWM/50 |

| Isolation level | Basic | Reinforced | Basic | Basic | Reinforced |

| Silicon technology | 0.35 μm BCD | 0.18 μm BCD, Schottky diode, 0.13 μm CMOS | 0.13 μm CMOS | 0.35 μm BCD | 0.18 μm BCD, Schottky diode, 0.13 μm CMOS, |

| Isolation technology | Integrated SiO2 transformers with Cu/Al metals | Post-processed polyimide transformer with Au metals | PCB transformers | Coreless micro transformer | Post-processed polyimide transformer with Au metals |

| No. of isolation transformers | 2 | 1 | 2 | 1 | 1 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Parisi, A.; Ragonese, E.; Spina, N.; Castorina, A.; Palmisano, G. A Control Technique for Galvanically Isolated DC–DC Converters with a Single Channel. Electronics 2025, 14, 1368. https://doi.org/10.3390/electronics14071368

Parisi A, Ragonese E, Spina N, Castorina A, Palmisano G. A Control Technique for Galvanically Isolated DC–DC Converters with a Single Channel. Electronics. 2025; 14(7):1368. https://doi.org/10.3390/electronics14071368

Chicago/Turabian StyleParisi, Alessandro, Egidio Ragonese, Nunzio Spina, Alessandro Castorina, and Giuseppe Palmisano. 2025. "A Control Technique for Galvanically Isolated DC–DC Converters with a Single Channel" Electronics 14, no. 7: 1368. https://doi.org/10.3390/electronics14071368

APA StyleParisi, A., Ragonese, E., Spina, N., Castorina, A., & Palmisano, G. (2025). A Control Technique for Galvanically Isolated DC–DC Converters with a Single Channel. Electronics, 14(7), 1368. https://doi.org/10.3390/electronics14071368