Radio Frequency (RF) Power Amplifier Design Providing High Power Efficiency in a Wide Dynamic Range

Abstract

:1. Introduction

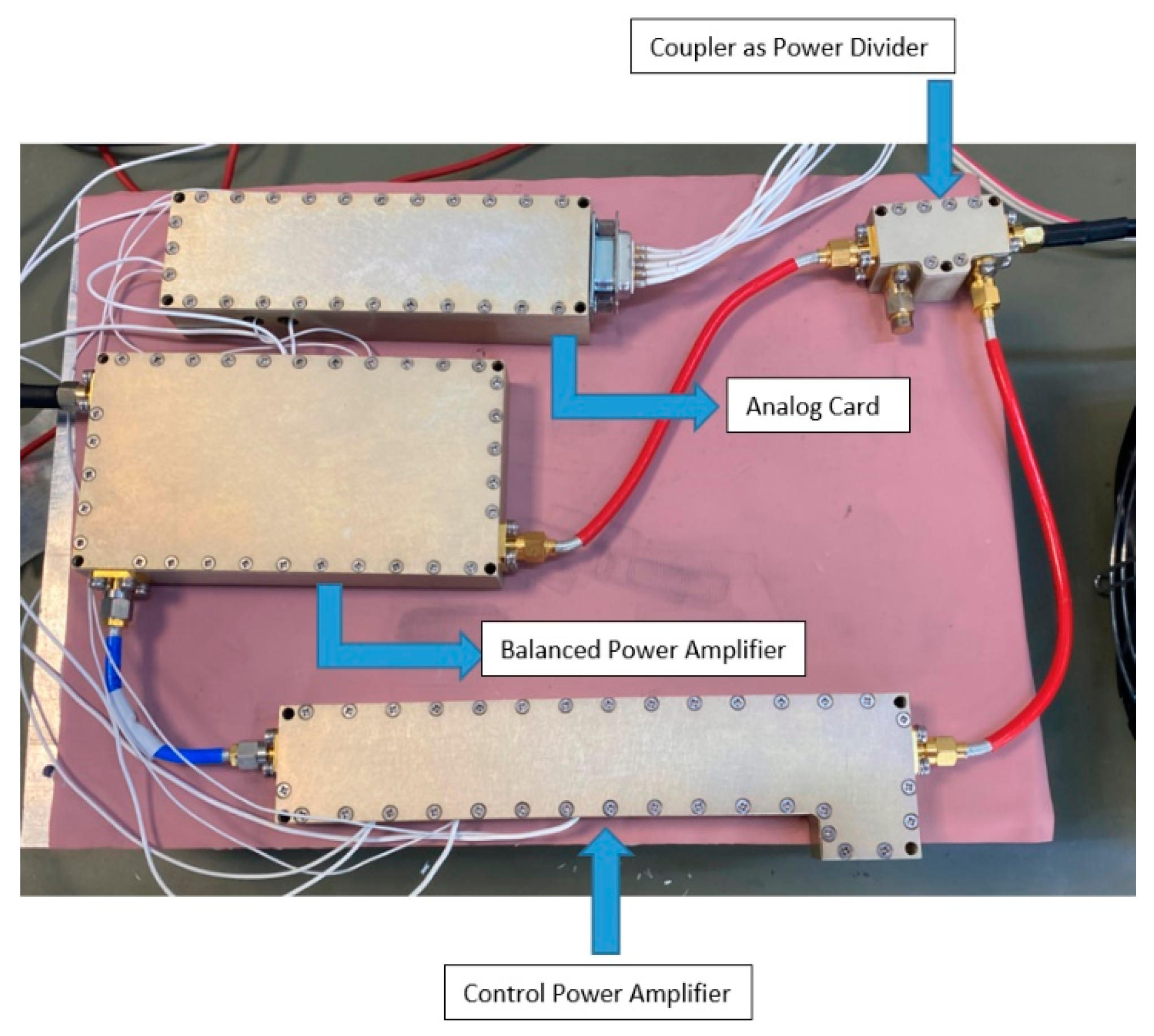

2. Materials and Methods

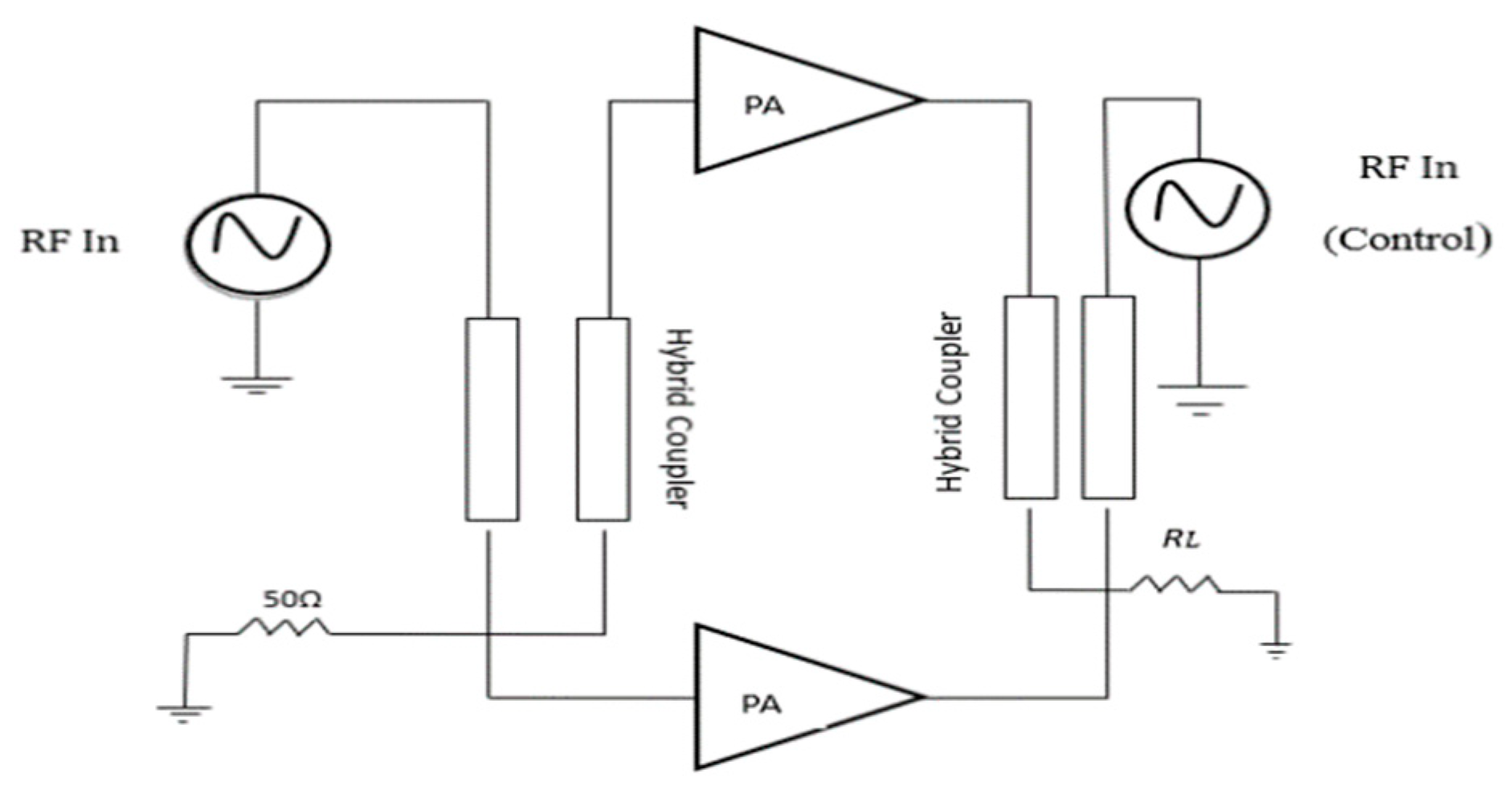

2.1. Load-Modulated Balanced Amplifier Design

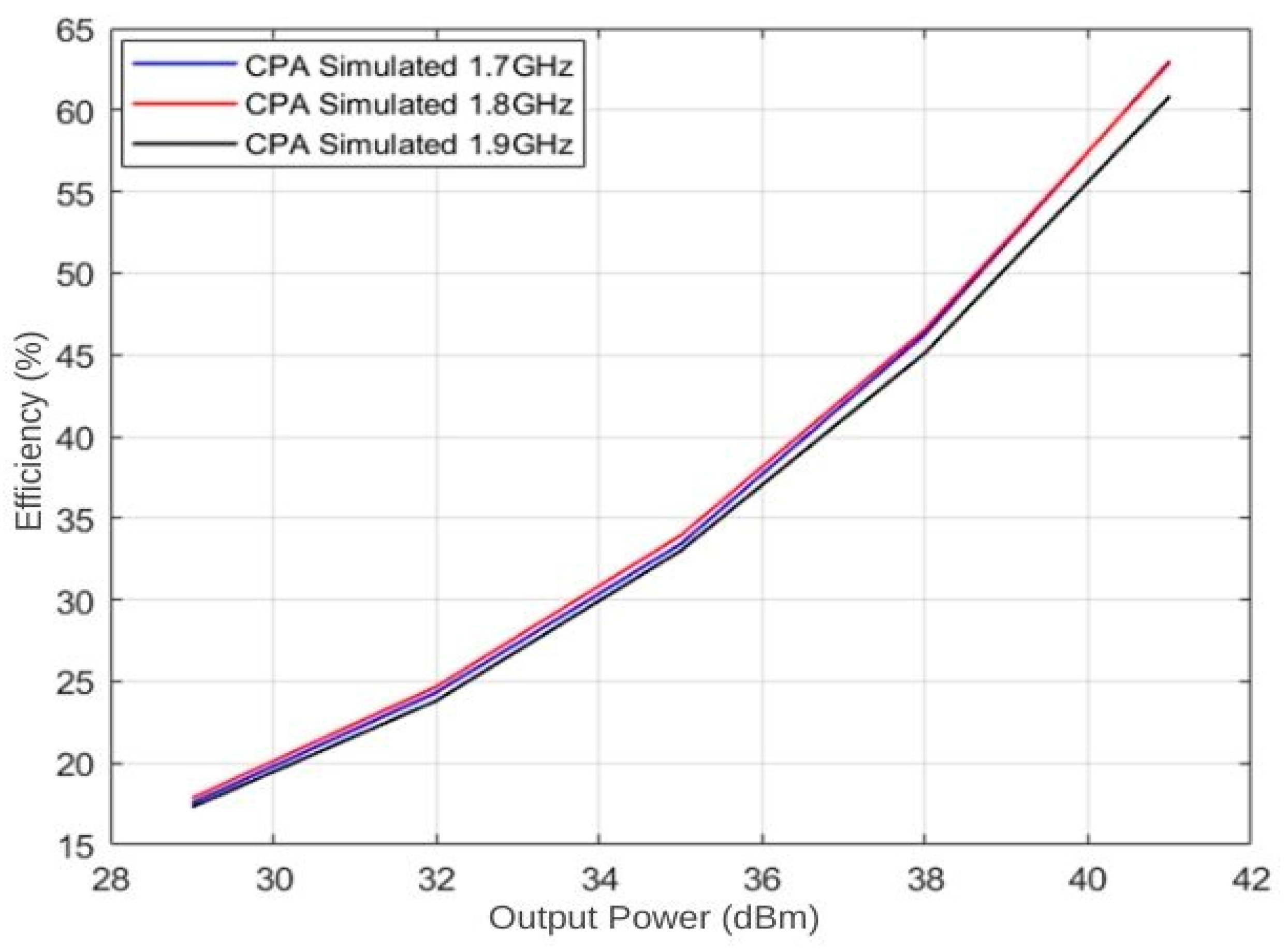

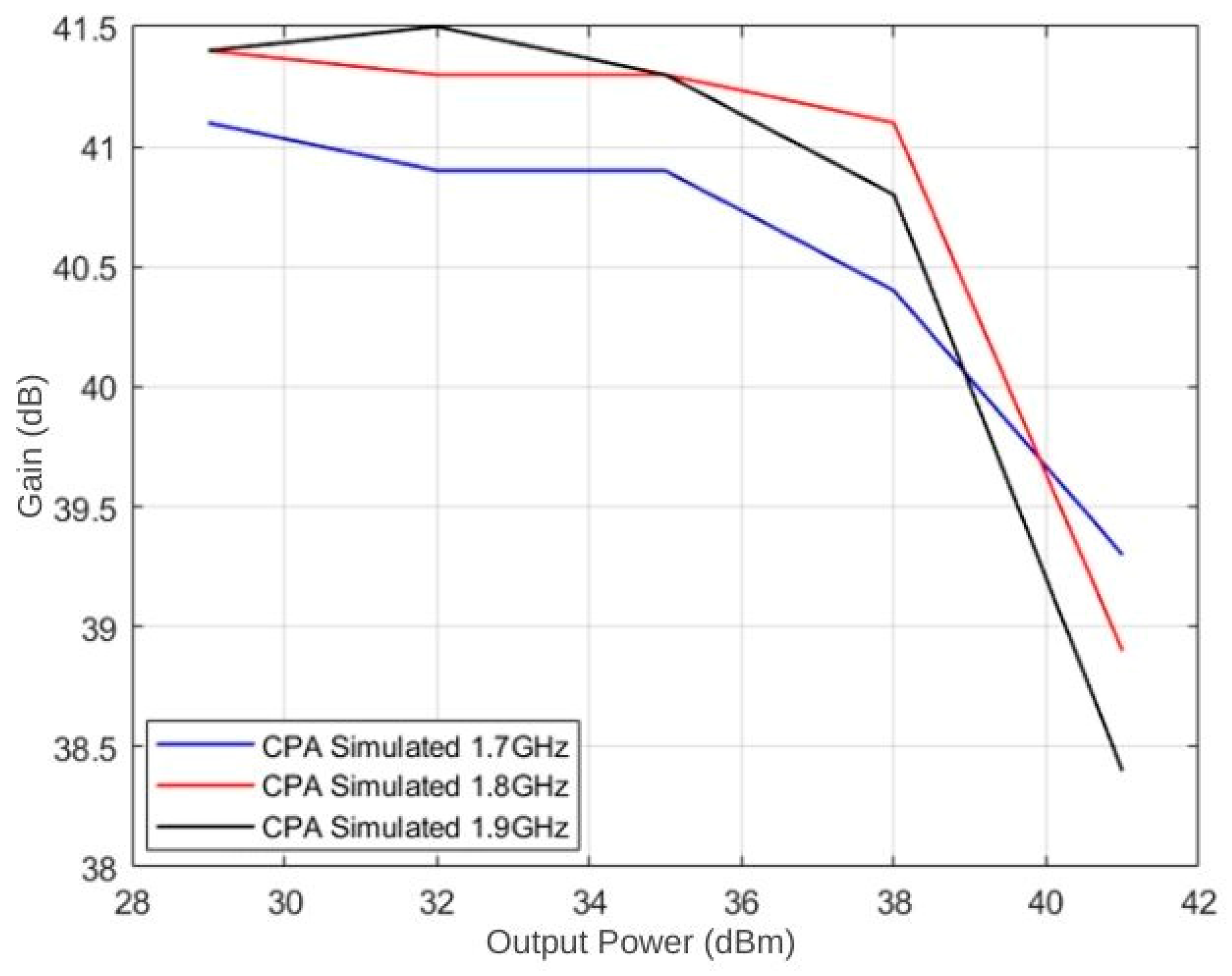

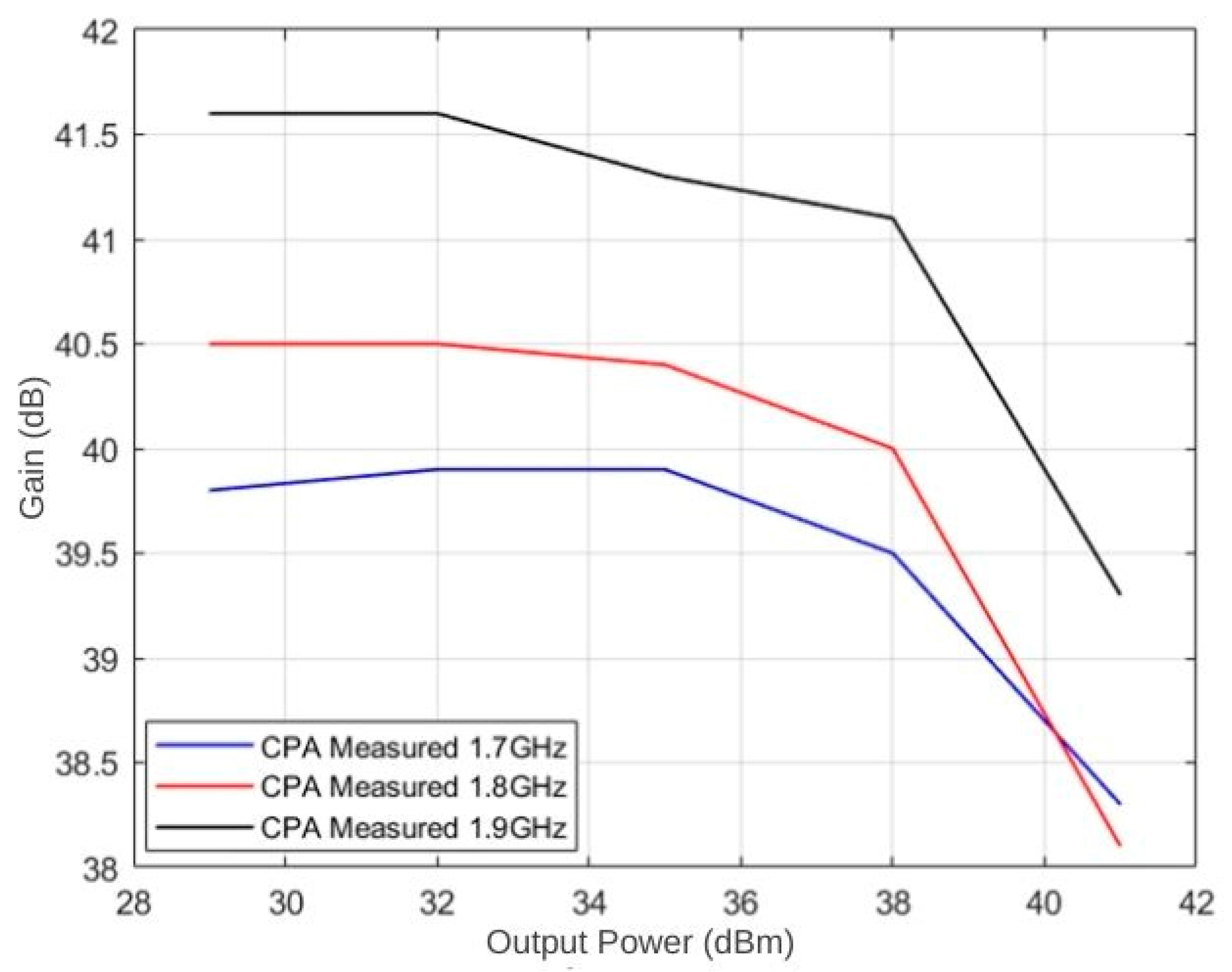

2.2. Control Path Power Amplifier Design

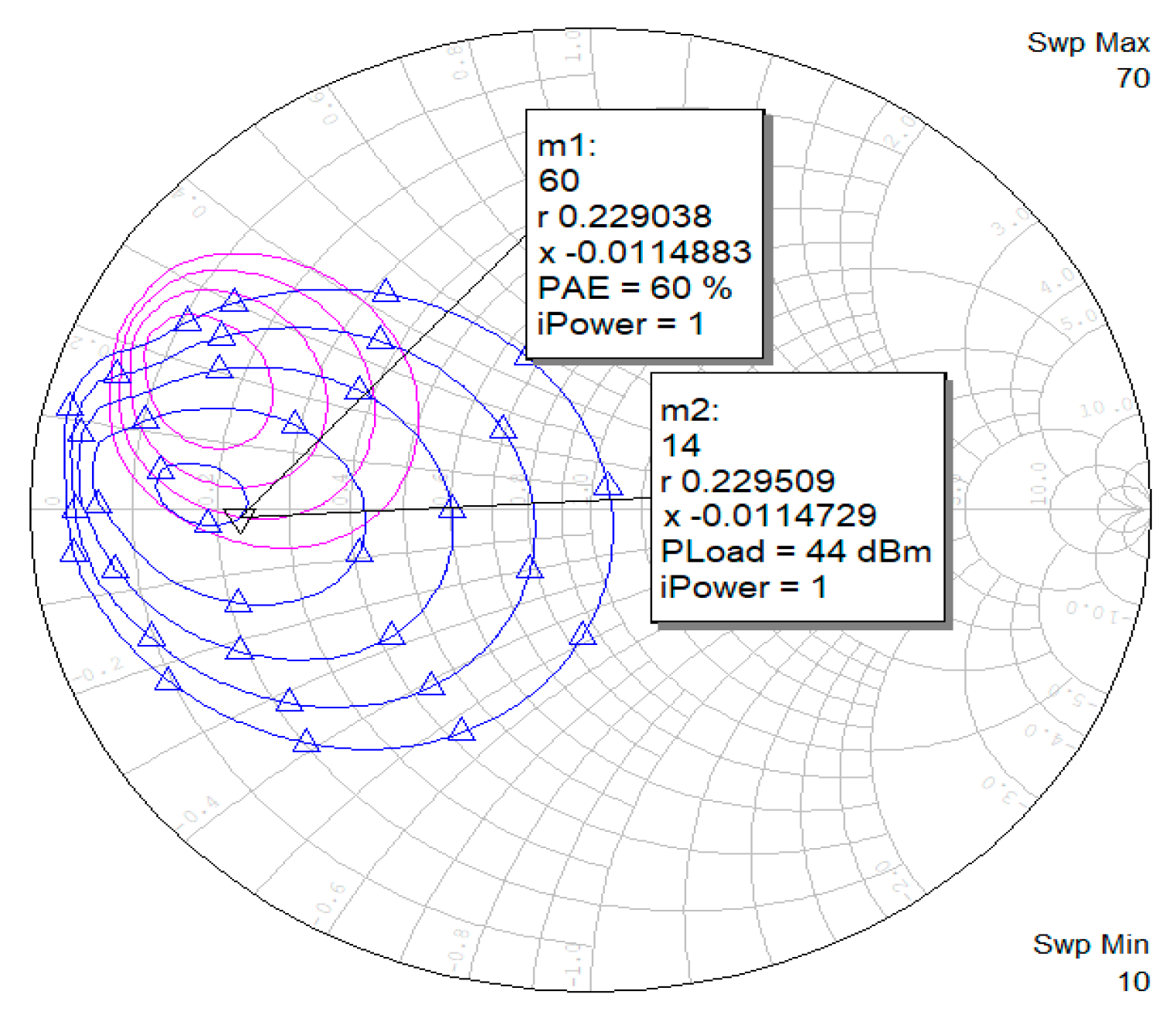

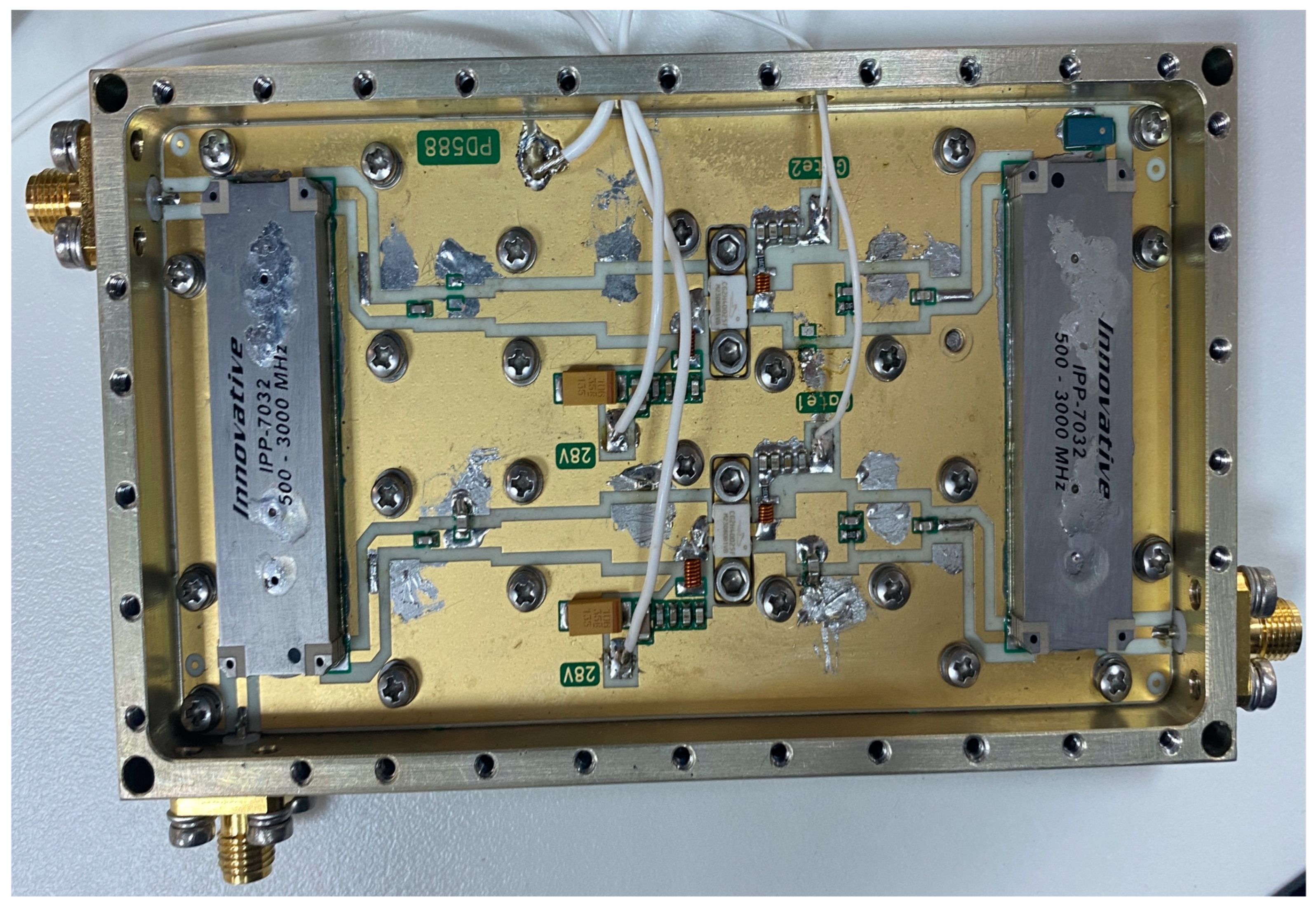

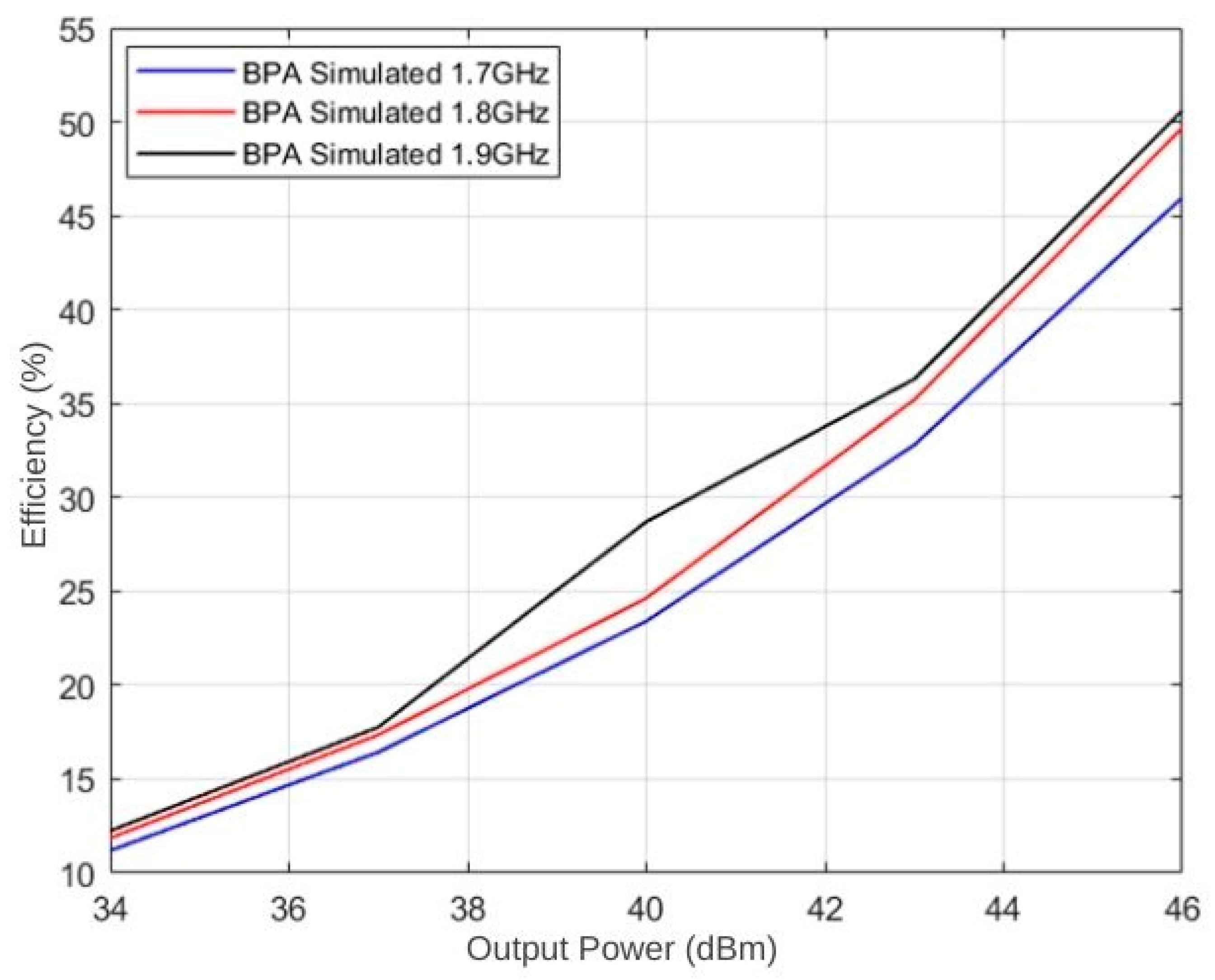

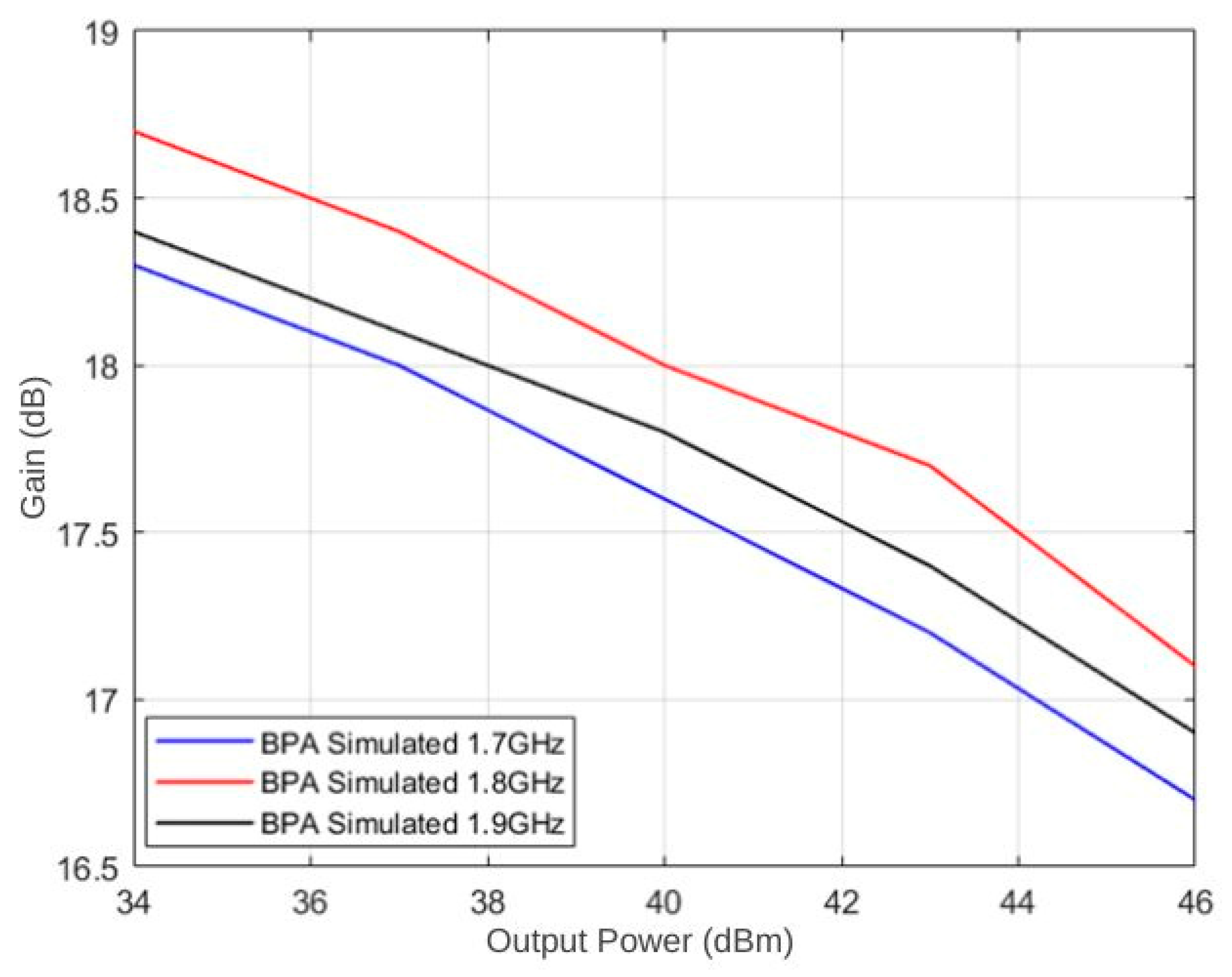

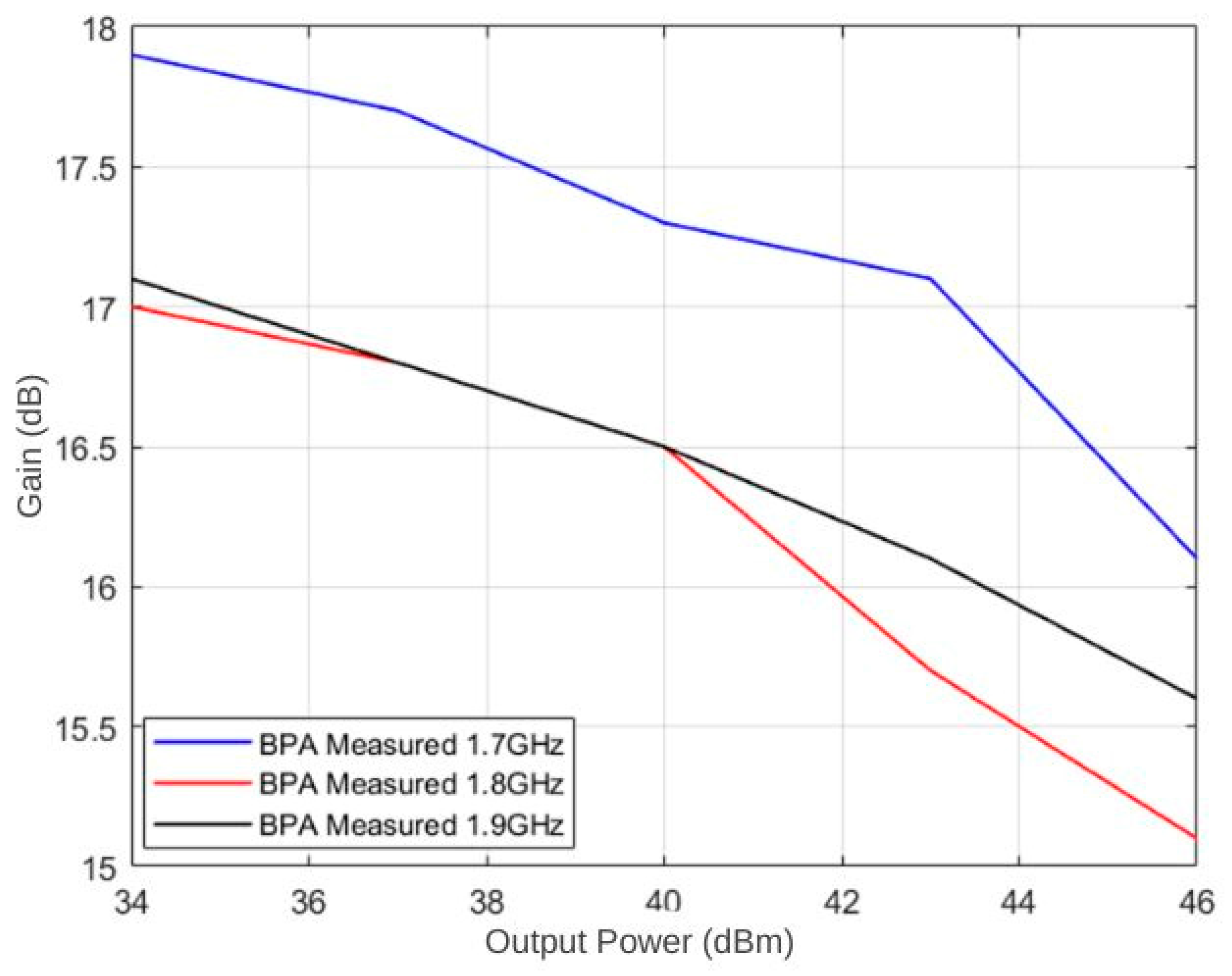

2.3. Balanced Pair (Main Path) Power Amplifier Design

2.4. Directional Coupler Design to Be Used as a Power Splitter

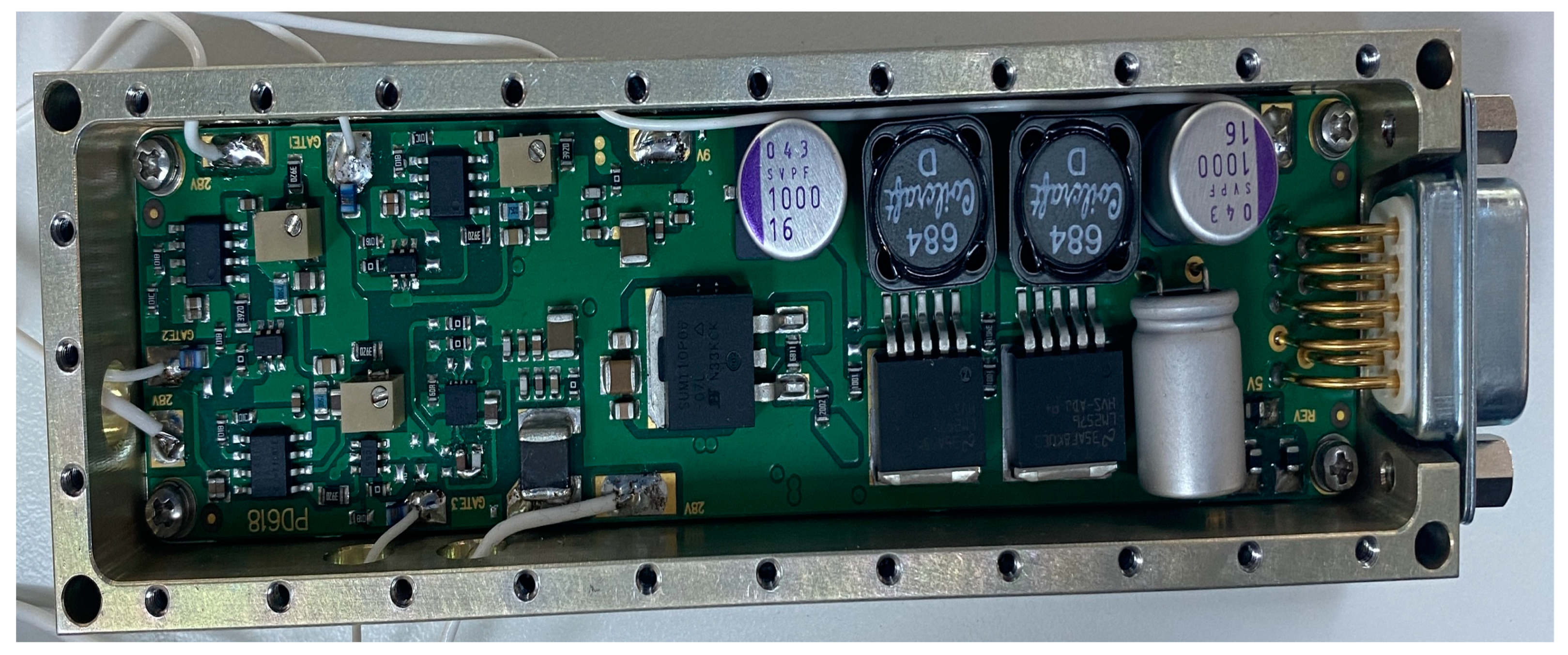

2.5. Analog Board Design

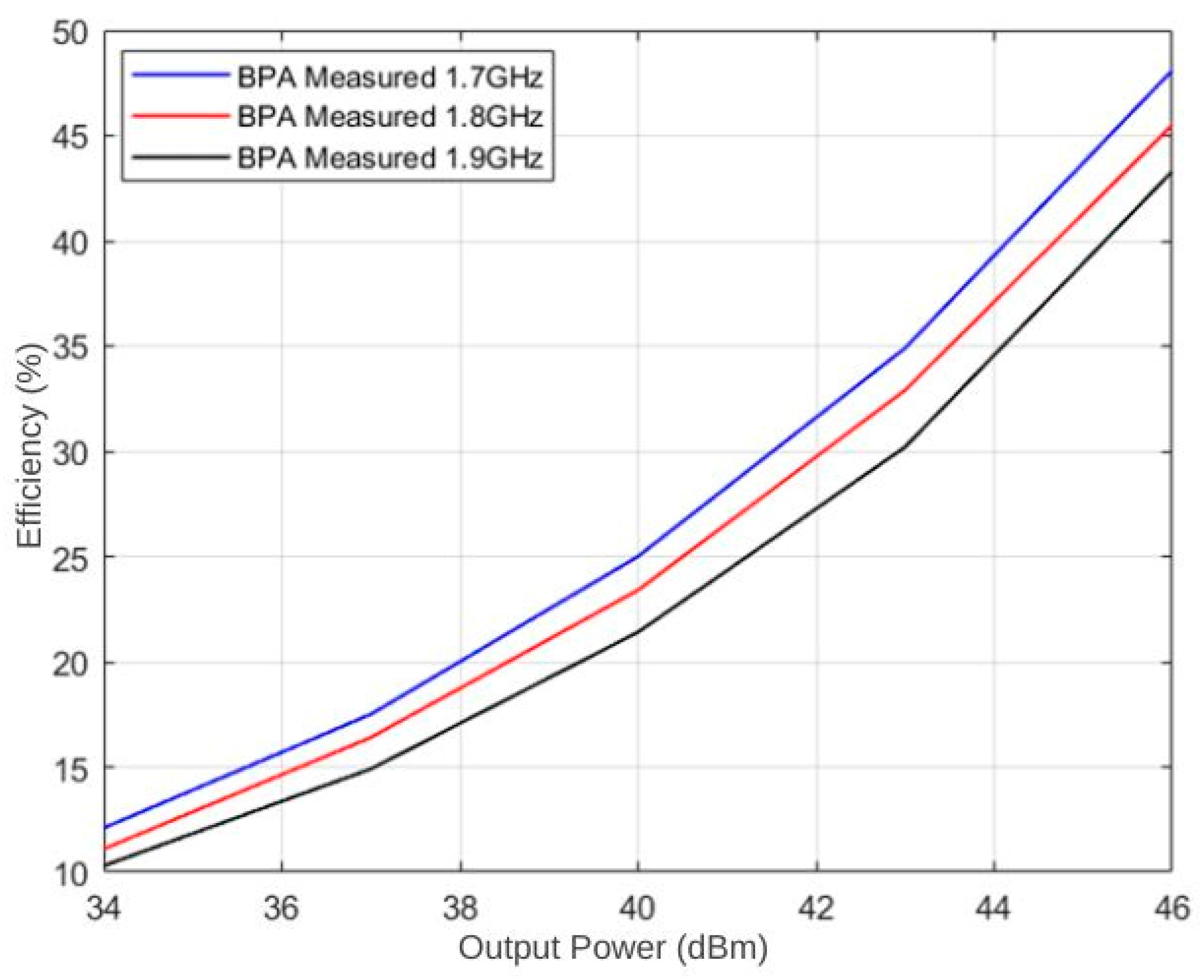

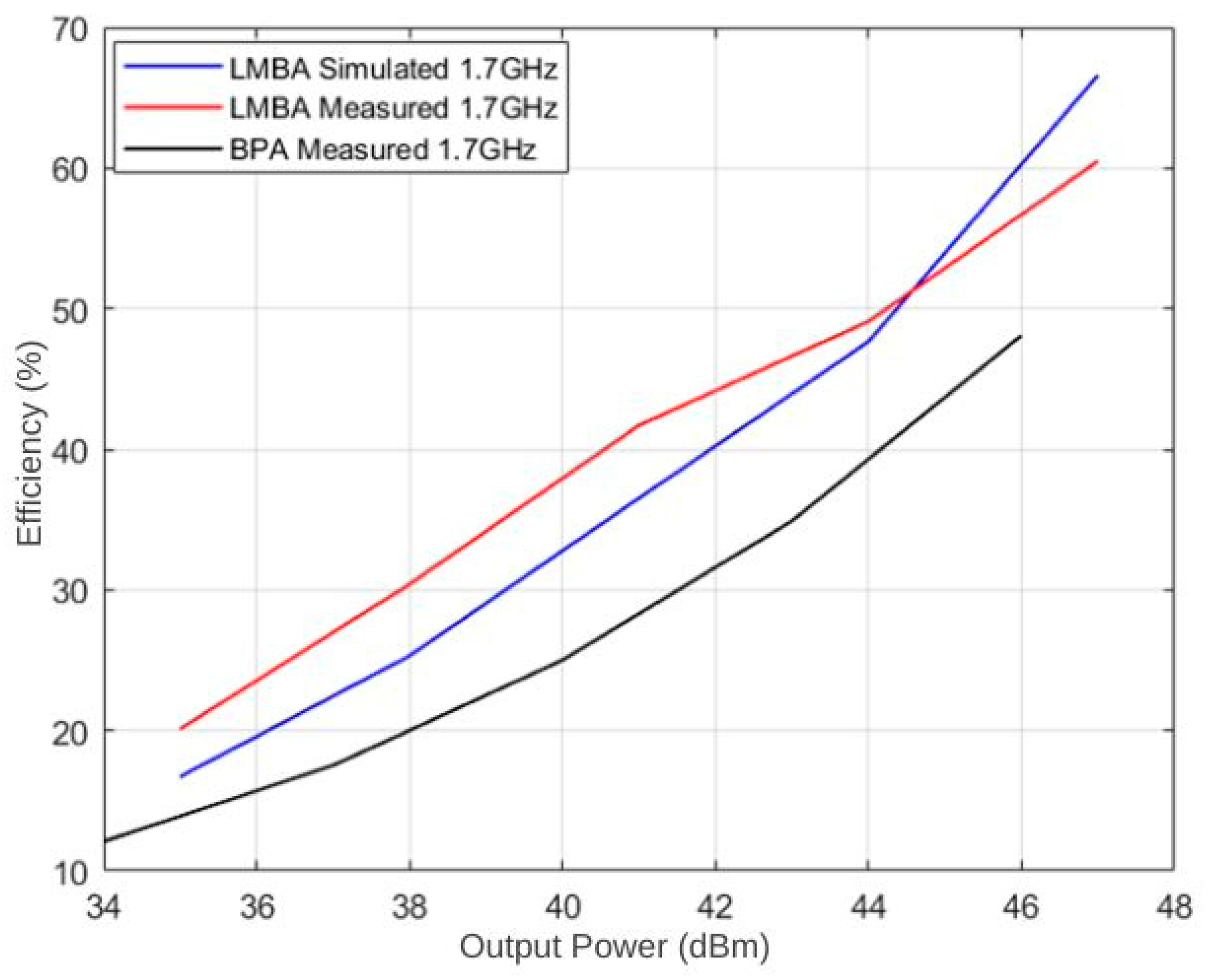

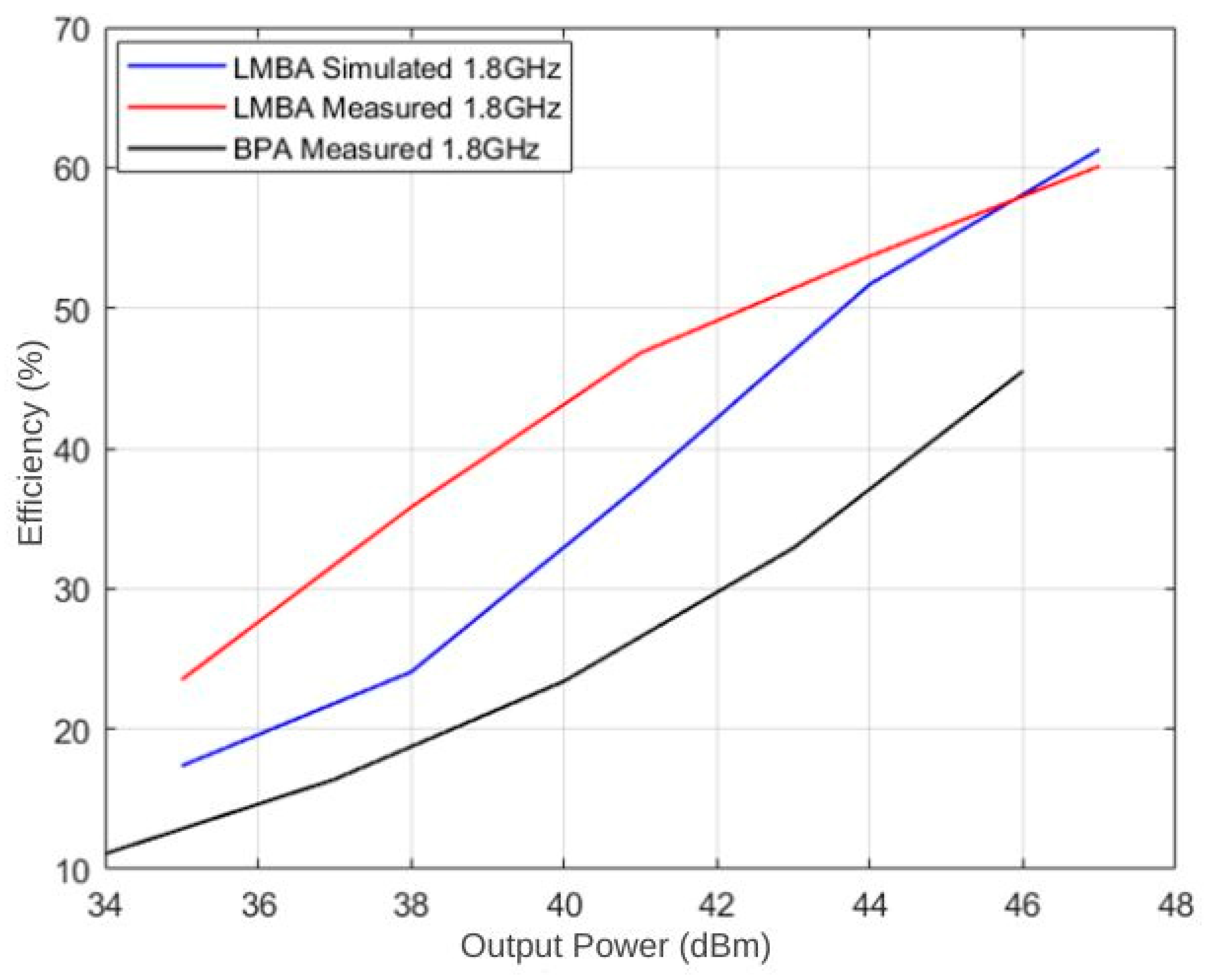

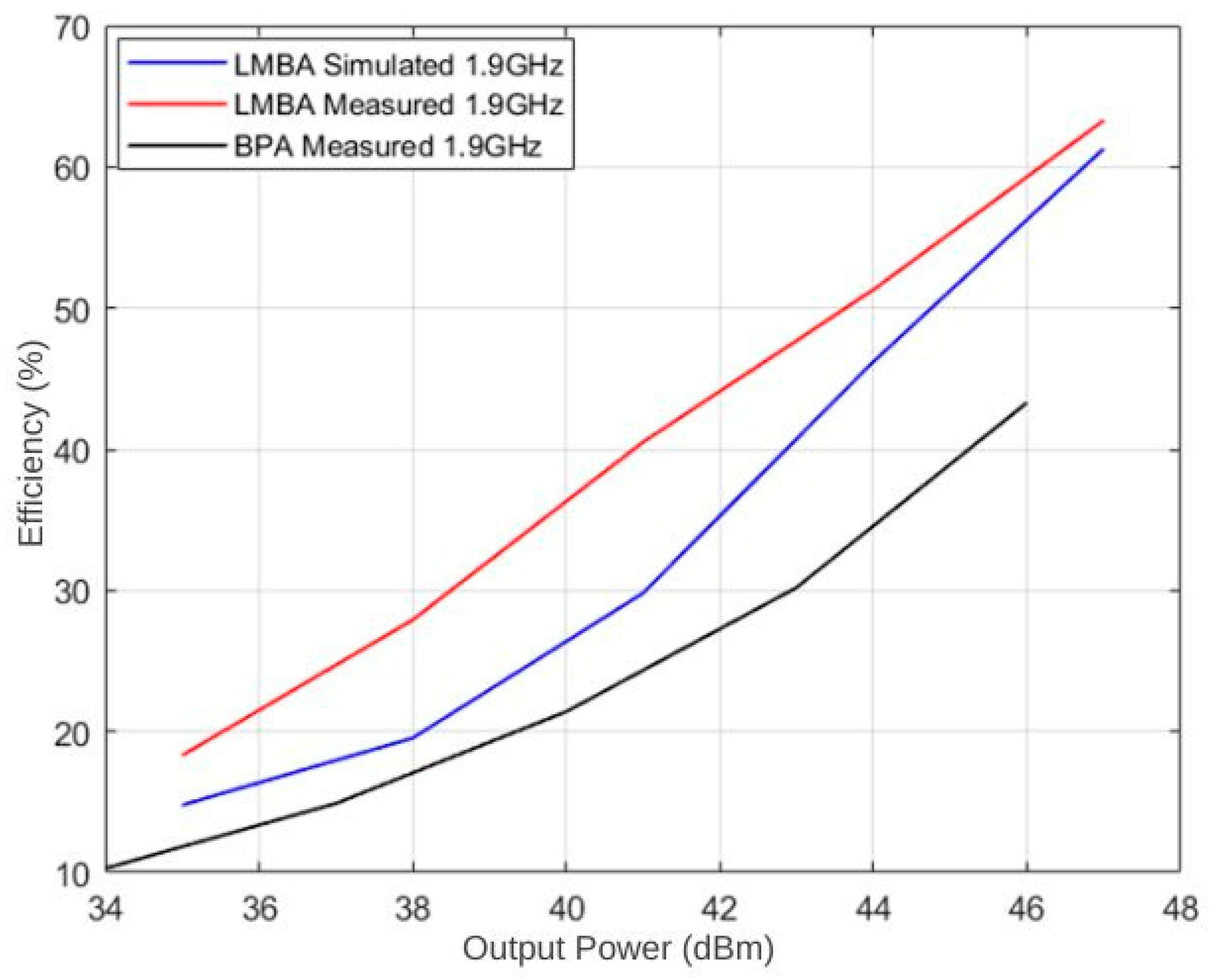

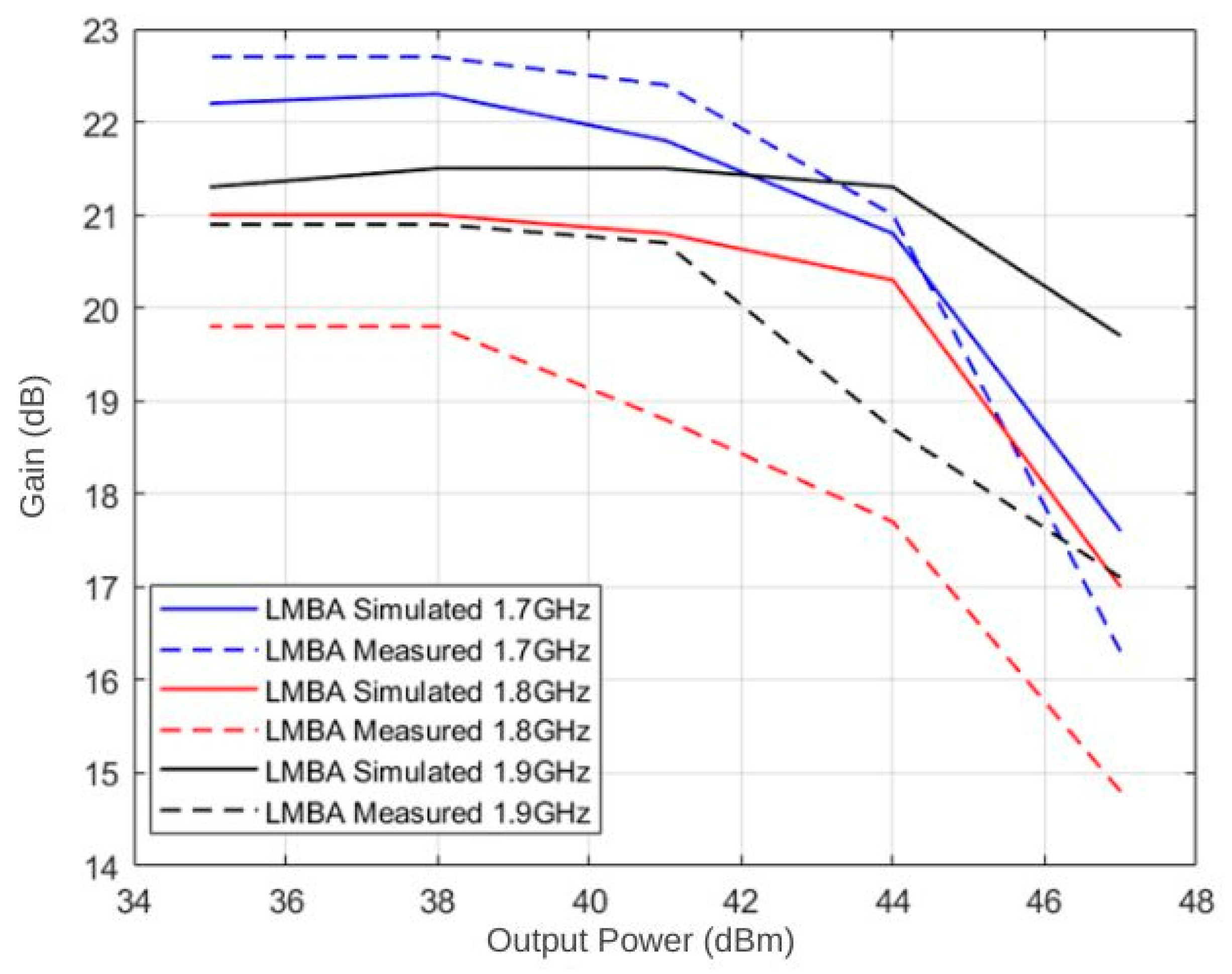

3. Measurement Results of the LMBA System

4. Discussion

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Bayraktar, F. Yüksek Verimli F-Sınıfı Mikrodalga Güç Yükselteç Tasarımı. Master’s Thesis, Elektrik Elektronik Mühendisliği, Hacettepe Üniversitesi, Ankara, Türkiye, 2017. [Google Scholar]

- Skaria, G. Class F and Inverse Class F Power Amplifier Subject to Electrical Stress Effect. Master’s Thesis, Department of Electrical Engineering and Computer Science, University of Central Florida, Orlando, FL, USA, 2011. [Google Scholar]

- El-Hamamsy, S.A. Design of high-efficiency RF Class-D power amplifier. IEEE Trans. Power Electron. 1997, 9, 297–308. [Google Scholar] [CrossRef]

- Collins, G.F.; Wood, J. Class-E power amplifier design at 2.5 GHz using a packaged transistor. In Proceedings of the 2013 IEEE Radio and Wireless Symposium, Austin, TX, USA, 20–23 January 2013; pp. 259–261. [Google Scholar] [CrossRef]

- Kahn, L.R. Single-Sideband Transmission by Envelope Elimination and Restoration. Proc. IRE 1952, 40, 803–806. [Google Scholar] [CrossRef]

- Jing, Y.; Zhu, B. A 2.4 GHz SiGe Envelope Tracking Power Amplifier for LTE Applications. In Proceedings of the 2023 6th World Conference on Computing and Communication Technologies (WCCCT), Chengdu, China, 6–8 January 2023; pp. 52–56. [Google Scholar] [CrossRef]

- Peker, K. Design of a High Efficiency Power Amplifier by Using Doherty Configuration. Master’s Thesis, Department of Electrical and Electronics Engineering, Bilkent University, Ankara, Turkey, 2010. [Google Scholar]

- Zeng, B.; Zheng, S.; Chan, W.S.; Zhou, X. Design of a High-Efficiency Outphasing Power Amplifier with Enhancing Back-Off Range for 5G Applications. In Proceedings of the 2023 IEEE Conference on Antenna Measurements and Applications (CAMA), Genoa, Italy, 15–17 November 2023; pp. 442–444. [Google Scholar] [CrossRef]

- Yang, K.; Yang, R.; Zhang, P.; Shi, W.; Hu, C.; Shi, W. Development Review of Highly Efficient Sequential Power Amplifier with Extended Back-Off Range for Broadband Application. Energies 2024, 17, 161. [Google Scholar] [CrossRef]

- Jin, D.; Latino, M.; Crupi, G.; Cai, J. Design and Experimental Validation of a High-Efficiency Sequential Load Modulated Balanced Amplifier. Electronics 2024, 13, 3897. [Google Scholar] [CrossRef]

- Jin, Y.; Dai, Z.; Ran, X.; Xu, C.; Li, M. A Dual Load-Modulated Doherty Power Amplifier Design Method for Improving Power Back-Off Efficiency. Sensors 2023, 23, 6598. [Google Scholar] [CrossRef] [PubMed]

- Niclas, K.B.; Wilser, W.T.; Gold, R.B.; Hitchens, W.R. Application of the Two-Way Balanced Amplifier Concept to Wide-Band Power Amplification Using GaAs MESFET’s. IEEE Trans. Microw. Theory Tech. 1980, 28, 172–179. [Google Scholar] [CrossRef]

- Quaglia, R.; Cripps, S. A Load Modulated Balanced Amplifier for Telecom Applications. IEEE Trans. Microw. Theory Tech. 2018, 66, 1328–1338. [Google Scholar] [CrossRef]

- Pednekar, P.H.; Barton, T.W. RF-input load modulated balanced amplifier. In Proceedings of the 2017 IEEE MTT-S International Microwave Symposium (IMS), Honololu, HI, USA, 4–9 June 2017; pp. 1730–1733. [Google Scholar] [CrossRef]

- Pednekar, P.H.; Berry, E.; Barton, T.W. RF-Input Load Modulated Balanced Amplifier with Octave Bandwidth. IEEE Trans. Microw. Theory Tech. 2017, 65, 5181–5191. [Google Scholar] [CrossRef]

- Pednekar, P.H.; Hallberg, W.; Fager, C.; Barton, T.W. Analysis and Design of a Doherty-Like RF-Input Load Modulated Balanced Amplifier. IEEE Trans. Microw. Theory Tech. 2018, 66, 5322–5335. [Google Scholar] [CrossRef]

- Cao, Y.; Lyu, H.; Chen, K. Load Modulated Balanced Amplifier with Reconfigurable Phase Control for Extended Dynamic Range. In Proceedings of the 2019 IEEE MTT-S International Microwave Symposium (IMS), Boston, MA, USA, 2–7 June 2019; pp. 1335–1338. [Google Scholar] [CrossRef]

- Aras, Y.E. Analytical Model and Design of Load Modulated Balanced Amplifier. Master’s Thesis, The Graduate School of Engineering and Science, Bilkent University, Ankara, Turkey, 2020. [Google Scholar]

- Xie, J.; Cheng, K.-K.M.; Fang, X.; Yu, P. Extension of Output Backoff Range in Three-Stage Load Modulated Balanced Amplifier Using Asymmetric Coupling and Non-Z0 Load. IEEE Trans. Microw. Theory Tech. 2025, 73, 553–567. [Google Scholar] [CrossRef]

- Ding, L.; Xia, J. Design of Load-modulated Balanced Amplifier Based on Broadand Output Matching Network. In Proceedings of the 2024 IEEE 12th Asia-Pacific Conference on Antennas and Propagation (APCAP), Nanjing, China, 22–25 September 2024; pp. 1–2. [Google Scholar] [CrossRef]

- Pednekar, P.H. Advanced Load Modulated Power Amplifier Architectures. Doctoral Thesis, Faculty of the Graduate School, University of Colorado at Boulder, Boulder, CO, USA, 2019. [Google Scholar]

- Mehter, E.; Bilgiç, R.; Üçüncü, M. Radar HF Bandı RF Güç Yükselteci Tasarımı ve Üretimi. Bitlis Eren Üniv. Fen Bilim. Derg. 2021, 10, 1232–1248. [Google Scholar] [CrossRef]

| Frequency (MHz) | Balanced Amplifier Max. Output Power (dBm)/Gain(dB) | Balanced Amplifier η @Pmax (%) | Balanced Amplifier η @6 dB OBO(%) |

|---|---|---|---|

| 1700 | 46 dBm/16 dB | 48.1 | 25 |

| 1800 | 46 dBm/15.1 dB | 45.5 | 23.4 |

| 1900 | 46 dBm/15.6 dB | 43.3 | 21.4 |

| Frequency (MHz) | LMBA Max. Output Power (dBm)/Gain (dB) | LMBA η @Pmax (%) | LMBA η @6 dB OBO(%) |

|---|---|---|---|

| 1700 | 47 dBm/16.3 dB | 60.5 | 41.7 |

| 1800 | 47 dBm/14.8 dB | 60.1 | 46.8 |

| 1900 | 47 dBm/17.1 dB | 63.3 | 40.5 |

| Studies | Frequency (GHz) | Max. Output Power (dBm) | η @Pmax (%) | OBO (dB) | η @6 dB OBO (%) |

|---|---|---|---|---|---|

| This study | 1.7–1.9 | 47 | 60.1–63.3 | 6 | 40.5–46.8 |

| Y. Erdem Aras [15] | 1.7 | 37.5 | 53 | 6 | 47 |

| P. Pednekar [14] | 1.8–3.8 | 44 | 46–70 | 6 | 33–49 |

| J. Xie [19] | 1.8–2.05 | 42–44.4 | 48.2–63.2 | 7.5 | 50.8–59.5 |

| L. Ding [20] | 1.4–2.8 | 43.7–44.3 | 64.6–70.5 | 10 | 44.9–50.4 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Mehter, E.; Üçüncü, M. Radio Frequency (RF) Power Amplifier Design Providing High Power Efficiency in a Wide Dynamic Range. Electronics 2025, 14, 1435. https://doi.org/10.3390/electronics14071435

Mehter E, Üçüncü M. Radio Frequency (RF) Power Amplifier Design Providing High Power Efficiency in a Wide Dynamic Range. Electronics. 2025; 14(7):1435. https://doi.org/10.3390/electronics14071435

Chicago/Turabian StyleMehter, Egemen, and Murat Üçüncü. 2025. "Radio Frequency (RF) Power Amplifier Design Providing High Power Efficiency in a Wide Dynamic Range" Electronics 14, no. 7: 1435. https://doi.org/10.3390/electronics14071435

APA StyleMehter, E., & Üçüncü, M. (2025). Radio Frequency (RF) Power Amplifier Design Providing High Power Efficiency in a Wide Dynamic Range. Electronics, 14(7), 1435. https://doi.org/10.3390/electronics14071435