Area-Efficient Embedded Resistor-Triggered SCR with High ESD Robustness

Abstract

:1. Introduction

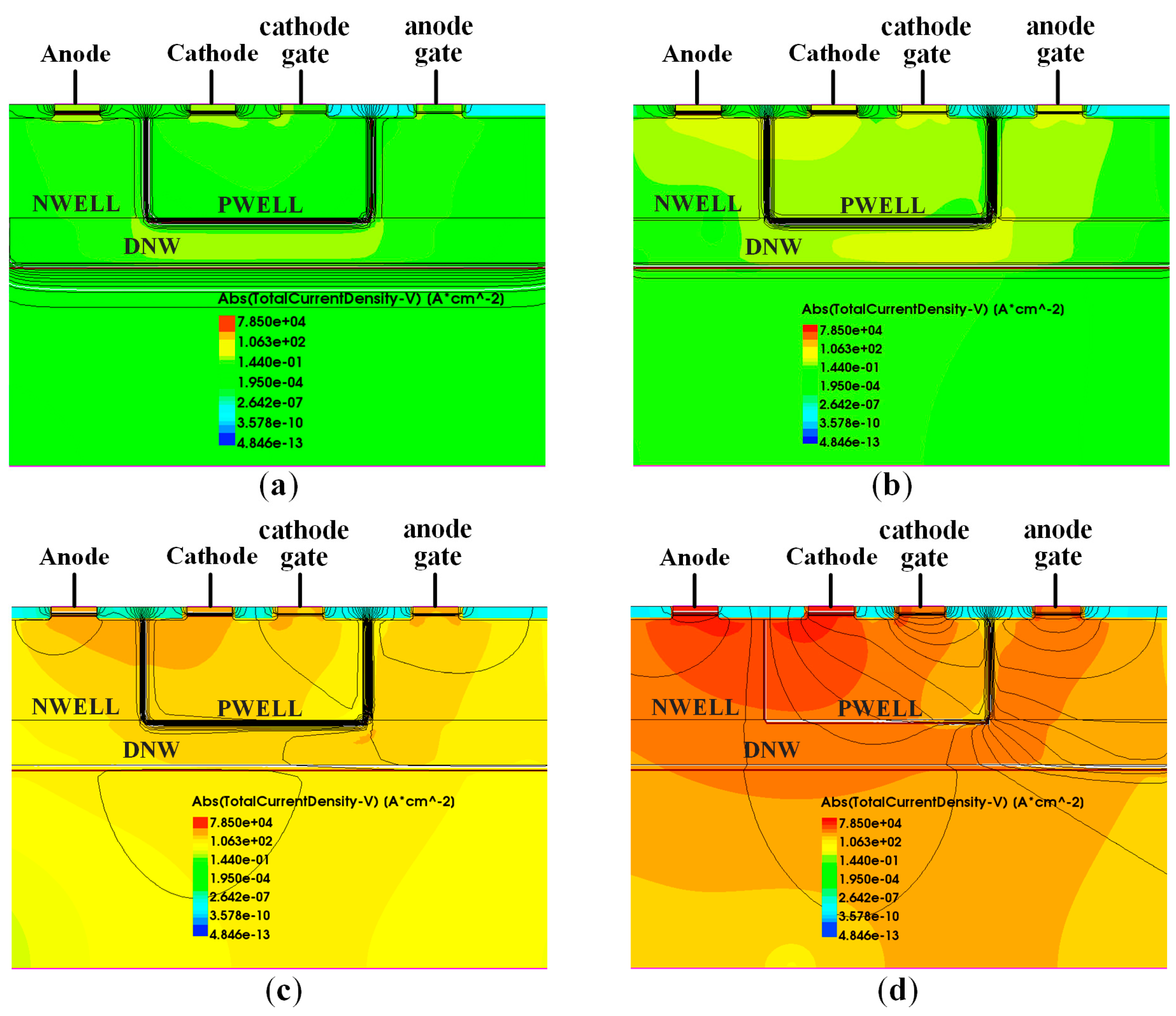

2. Proposed ESD Device Structure and Simulation

3. Layout Design of Proposed ERTSCR

4. Experimental Results and Discussion

4.1. TLP and HBM Results

4.2. VF-TLP Measurement and Results

4.3. Leakage Current Characteristics

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Salcedo, J.A.; Liou, J.J.; Bernier, J.C. Design and integration of novel SCR-based devices for ESD protection in CMOS/BiCMOS technologies. IEEE Trans. Electron Devices 2005, 52, 2682–2689. [Google Scholar] [CrossRef]

- Ker, M.D.; Hsu, K.C. Overview of on-chip electrostatic discharge protection design with SCR-based devices in CMOS integrated circuits. IEEE Trans. Device Mater. Reliab. 2005, 5, 235–249. [Google Scholar] [CrossRef]

- Duvvury, C.; Rountree, R. A synthesis of ESD input protection scheme. J. Electr. 1992, 29, 88–97. [Google Scholar] [CrossRef]

- Ker, M.D.; Wu, C.Y.; Chang, H.H. Complementary-LVTSCR ESD protection circuit for submicron CMOS VLSI/ULSI. IEEE Trans. Electron Devices 1996, 43, 588–598. [Google Scholar] [CrossRef]

- Ma, F.; Han, Y.; Dong, S.; Miao, M.; Liang, H. Improved Low-Voltage-Triggered SCR Structure for RF-ESD Protection. IEEE Electron Device Lett. 2013, 34, 1050–1052. [Google Scholar] [CrossRef]

- Russ, C.; Mergens, M.; Verhaege, K.; Armer, J.; Jozwiak, P.; Kolluri, G.; Avery, L. GGSCR: GGNMOS triggered silicon controlled rectifiers for ESD protection in deep submicron CMOS processes. In Proceedings of the 2001 IEEE Electrical Overstress/Electrostatic Discharge Symposium (EOS/ESD), Portland, OR, USA, 11–13 September 2001; pp. 22–31. [Google Scholar]

- Mergens, M.; Russ, C.C.; Verhaege, K.G.; Armer, J.; Jozwiak, P.C.; Mohn, R.P.; Keppens, B.; Trunh, C.S. Speed optimized Diode-Triggered SCR (DTSCR) for RF ESD protection of Ultra-Sensitive IC nodes in advanced technologies. IEEE Trans. Device Mater. Reliab. 2005, 5, 532–542. [Google Scholar] [CrossRef]

- Lin, C.; Fan, M. Optimization on Layout Style of Diode Stackup for On-Chip ESD Protection. IEEE Trans. Device Mater. Reliab. 2014, 14, 775–777. [Google Scholar] [CrossRef]

- Sun, R.C.; Wang, Z.; Klebanov, M.; Liang, W.; Liou, J.J.; Liu, D.G. Silicon-Controlled Rectifier for Electrostatic Discharge Protection Solutions with Minimal Snapback and Reduced Overshoot Voltage. IEEE Electron Device Lett. 2015, 36, 424–426. [Google Scholar] [CrossRef]

- Chen, J.; Lin, C.; Ker, M. On-Chip ESD Protection Device for High-Speed I/O Applications in CMOS Technology. IEEE Trans. Electron Devices 2017, 64, 3979–3985. [Google Scholar] [CrossRef]

- Lin, C.; Chen, C. Resistor-Triggered SCR Device for ESD Protection in High-Speed I/O Interface Circuits. IEEE Electron Device Lett. 2017, 38, 712–715. [Google Scholar] [CrossRef]

- Dong, A.; Salcedo, J.A.; Parthasarathy, S.; Zhou, Y.; Luo, S.; Hajjar, J.J.; Liou, J.J. ESD protection structure with reduced capacitance and overshoot voltage for high speed interface applications. Microelectron. Reliab. 2017, 79, 201–205. [Google Scholar] [CrossRef]

- Lin, C.; Chen, C. Low-C ESD Protection Design with Dual Resistor-Triggered SCRs in CMOS Technology. IEEE Trans. Device Mater. Reliab. 2018, 18, 197–204. [Google Scholar] [CrossRef]

- Du, X.; Dong, S.; Han, Y.; Liou, J.J. Analysis of metal routing technique in a novel dual direction multi-finger SCR ESD protection device. In Proceedings of the 2008 IEEE International Conference on Solid-State and Integrated-Circuit Technology (ICSICT), Beijing, China, 20–23 October 2008; pp. 337–340. [Google Scholar] [CrossRef]

- Wang, Z.; Liou, J. Evaluation of geometry layout and metal pattern to optimize ESD performance of silicon controlled rectifier (SCR). In Proceedings of the 2014 IEEE International Reliability Physics Symposium (IRPS), Waikoloa, HI, USA, 1–5 June 2014; pp. EL2.1–EL2.4. [Google Scholar] [CrossRef]

- Zhang, Y.; Zhang, H.; Chiu, C.; Tian, H. ESD damage mechanism study of metal fuse area. In Proceedings of the 2016 International Conference on Electronic Packaging Technology (ICEPT), Wuhan, China, 16–19 August 2016; pp. 1427–1429. [Google Scholar] [CrossRef]

- Gauthier, R.; Abou-Khalil, M.; Chatty, K.; Mitra, S.; Li, J. Investigation of Voltage Overshoots in Diode Triggered Silicon Controlled Rectifiers (DTSCRs) Under Very Fast Transmission Line Pulsing (VFTLP). In Proceedings of the 2009 IEEE Electrical Overstress/Electrostatic Discharge Symposium (EOS/ESD), Anaheim, CA, USA, 30 August–13 September 2009; pp. 1–10. [Google Scholar]

- Ker, M.; Lo, W. Design on the Low-Leakage Diode String for Using in the Power-Rail ESD Clamp Circuits in a 0.35-μm Silicide CMOS Process. IEEE Trans. Solid-State Circuits 2000, 35, 601–611. [Google Scholar] [CrossRef]

- Chen, S.; Chen, T.; Tang, T.; Chen, J.; Chou, C. Low-Leakage Diode String Designs Using Triple-Well Technologies for RF-ESD Applications. IEEE Electron Device Lett. 2003, 24, 595–597. [Google Scholar] [CrossRef]

- Lin, C.; Wu, P.; Ker, M. Area-Efficient and Low-Leakage Diode String for On-Chip ESD Protection. IEEE Trans. Electron Devices 2016, 63, 531–536. [Google Scholar] [CrossRef]

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hou, F.; Du, F.; Yang, K.; Liu, J.; Liu, Z. Area-Efficient Embedded Resistor-Triggered SCR with High ESD Robustness. Electronics 2019, 8, 445. https://doi.org/10.3390/electronics8040445

Hou F, Du F, Yang K, Liu J, Liu Z. Area-Efficient Embedded Resistor-Triggered SCR with High ESD Robustness. Electronics. 2019; 8(4):445. https://doi.org/10.3390/electronics8040445

Chicago/Turabian StyleHou, Fei, Feibo Du, Kai Yang, Jizhi Liu, and Zhiwei Liu. 2019. "Area-Efficient Embedded Resistor-Triggered SCR with High ESD Robustness" Electronics 8, no. 4: 445. https://doi.org/10.3390/electronics8040445

APA StyleHou, F., Du, F., Yang, K., Liu, J., & Liu, Z. (2019). Area-Efficient Embedded Resistor-Triggered SCR with High ESD Robustness. Electronics, 8(4), 445. https://doi.org/10.3390/electronics8040445