A High-Efficiency K-band MMIC Linear Amplifier Using Diode Compensation

Abstract

:1. Introduction

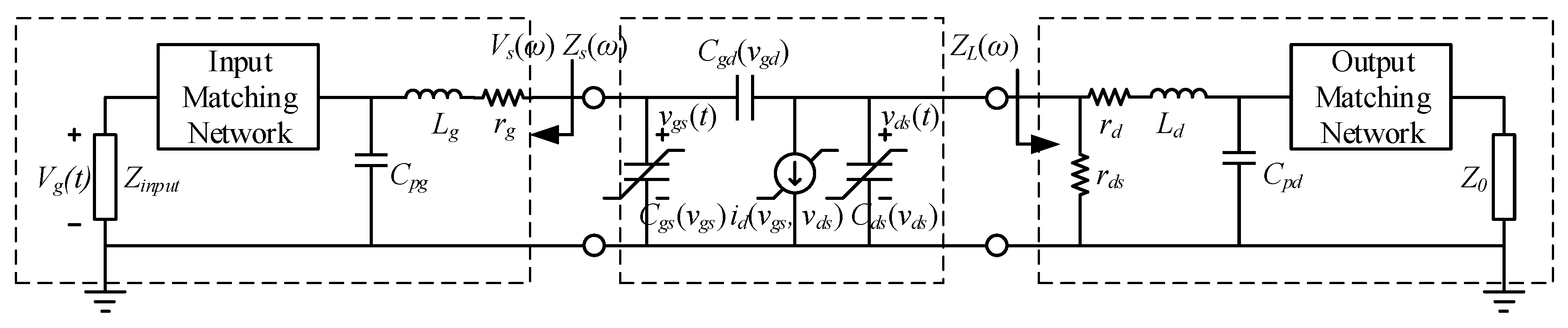

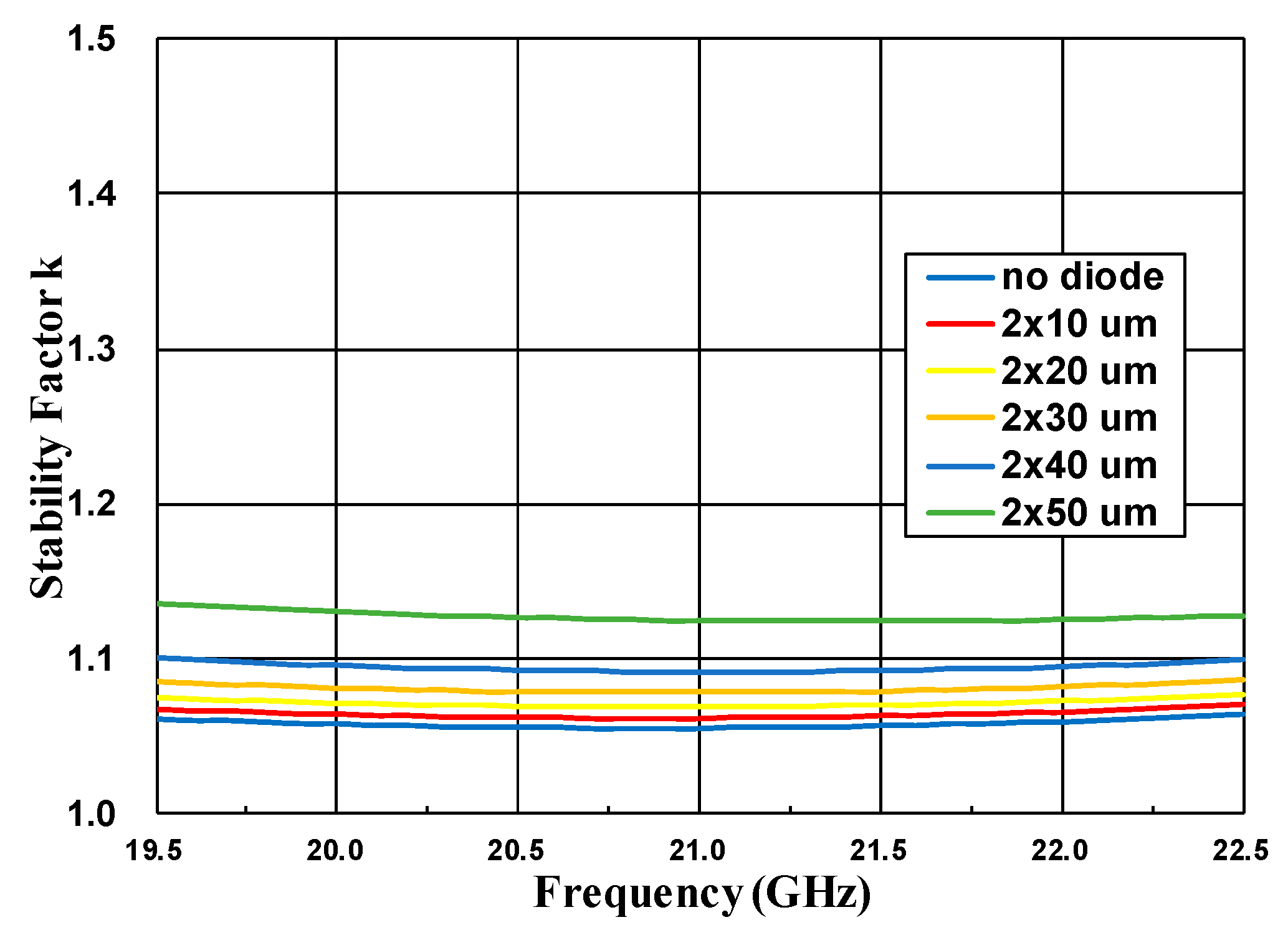

2. Nonlinear Analysis and Diode Compensation

- The size of the diode should be large enough to compensate for the input capacitance of the pHEMT as the input power increases;

- The barrier capacitance of the diode should not be too large to over change the input characteristics of the HMET and generate excessive feedback between drain and gate.

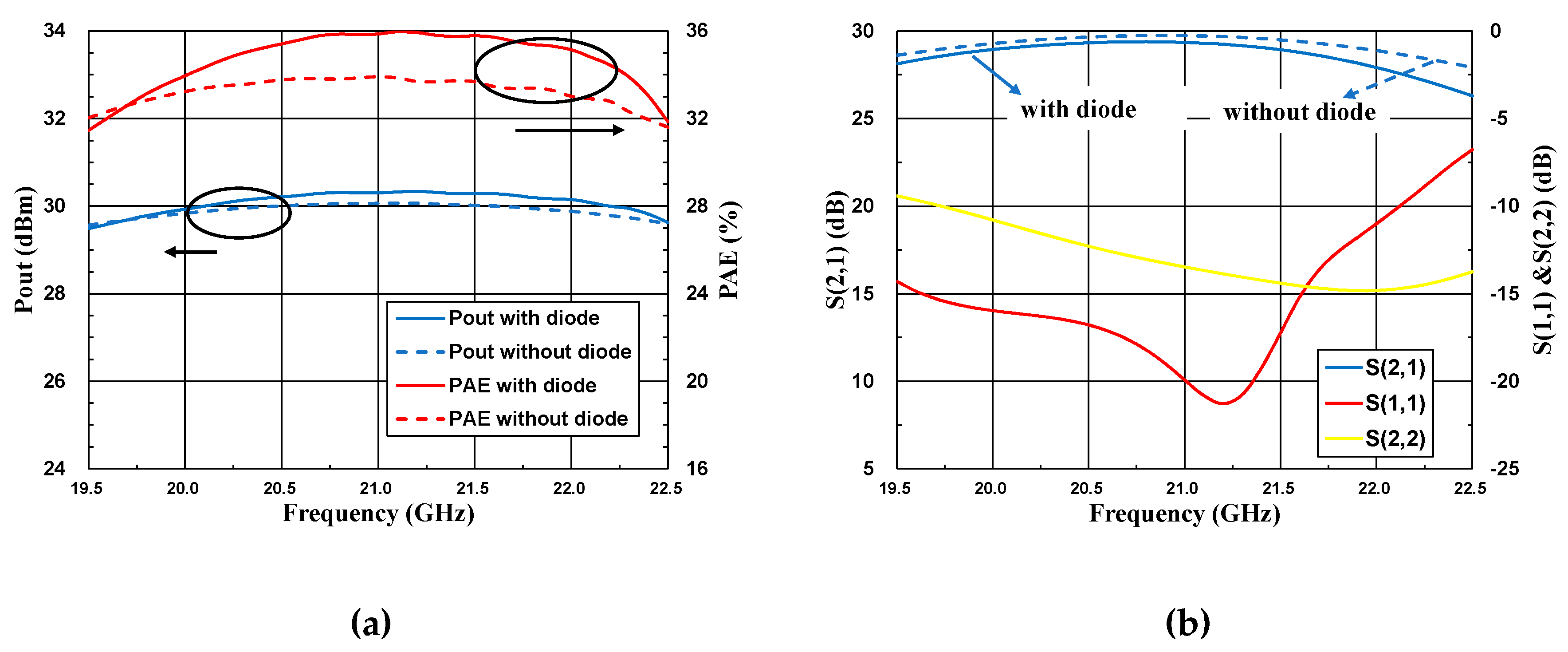

3. Circuit Design

4. Measurement Results

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Camarchia, V.; Guerrieri, S.D.; Ghione, G.; Pirola, M.; Quaglia, R.; Rubio, J.M.; Loran, B.; Palomba, F.; Sivverini, G. A K-band GaAs MMIC Doherty power amplifier for point-to-point microwave backhaul applications. In Proceedings of the 2014 International Workshop on Integrated Nonlinear Microwave and Millimetre-wave Circuits (INMMiC), Leuven, Belgium, 2–4 April 2014. [Google Scholar] [CrossRef]

- Lane, A.; Jenkins, J.; Green, C.; Myers, F. S and C band GaAs multifunction MMICs for phased array radar. In Proceedings of the 11th Annual Gallium Arsenide Integrated Circuit (GaAs IC) Symposium, San Diego, CA, USA, 22–25 October 1989; pp. 259–262. [Google Scholar] [CrossRef]

- Simons, K.A. The decibel relationships between amplifier distortion products. Proc. IEEE 1970, 58, 1071–1086. [Google Scholar] [CrossRef]

- Cho, K.-J.; Kim, W.-J.; Kim, J.-H.; Stapleton, S.P. Linearity optimization of a high power Doherty amplifier based on post-distortion compensation. IEEE Microw. Wireless Compon. Lett. 2005, 15, 748–750. [Google Scholar] [CrossRef]

- Roy, M.K. Distortion cancellation performance of miniature delay filters for feed-forward linear power amplifiers. IEEE Trans. Ultrason. Ferroelectr. Freq. Control 2002, 49, 1592–1595. [Google Scholar] [CrossRef]

- Wright, P.; Lees, J.; Benedikt, J.; Tasker, P.J.; Cripps, S.C. A methodology for realizing high efficiency class-J in a linear and broadband PA. IEEE Trans. Microw. Theory Techn. 2009, 57, 3196–3204. [Google Scholar] [CrossRef]

- Mrunal, A.K.; Shirasgaonkar, M.; Patrikar, R.M. Power amplifier linearization using a diode. In Proceedings of the MELECON 2006–2006 IEEE Mediterranean Electrotechnical Conference, Malaga, Spain, 16–19 May 2006; pp. 173–176. [Google Scholar] [CrossRef]

- Wren, M.; Brazil, T.J. The effect of the gate Schottky diode on pHEMT power amplifier performance. In Proceedings of the 2003 High Frequency Postgraduate Student Colloquium, Belfast, Ireland, 8–9 September 2003; pp. 52–55. [Google Scholar] [CrossRef]

- Nunes, L.C.; Cabral, P.M.; Pedro, J.C. A Physical Model of Power Amplifiers AM/AM and AM/PM Distortions and Their Internal Relationship. In Proceedings of the 2013 IEEE MTT-S International Microwave Symposium Digest (MTT), Seattle, WA, USA, 2–7 June 2013. [Google Scholar] [CrossRef]

- Fersch, T.; Quaglia, R.; Pirola, M.; Camarchia, V.; Ramella, C.; Khoshkholgh, A.J.; Ghione, G.; Weigel, R. Stacked GaAs pHEMTs: design of a K-band power amplifier and experimental characterization of mismatch effects. In Proceedings of the 2015 IEEE MTT-S International Microwave Symposium, Phoenix, AZ, USA, 17–22 May 2015; pp. 1–4. [Google Scholar] [CrossRef]

- Koo, B.; Park, C.; Lee, K.A.; Chun, J.H.; Hong, S. A 28-dBm pHEMT Power Amplifier Using Voltage Combiner for K-Band Applications. In Proceedings of the 38th European Microwave Conference, Amsterdam, Netherlands, 27–31 October 2008. [Google Scholar] [CrossRef]

- Brown, S.A.; Carroll, J.M. Compact, 1 Watt, power amplifier MMICs for K-band applications. In Proceedings of the GaAs IC Symposium, Seattle, WA, USA, 5–8 November 2000. [Google Scholar]

- Bessemoulin, A.; Mcculloch, M.G.; Alexander, A.; Mccann, D.; Mahon, S.J.; Harvey, J.T. Compact K-band watt-level GaAsPHEMT power amplifier MMIC with integrated ESD protection. In Proceedings of the 2006 European Microwave Integrated Circuits Conference, Manchester, UK, 10–13 September 2006. [Google Scholar]

- Wang, K.; Yan, Y.; Liang, X. A K-band power amplifier in a 0.15-um GaAs pHEMT process. In Proceedings of the 2018 IEEE MTT-S International Wireless Symposium (IWS), Chengdu, China, 6–10 May 2018; pp. 1–3. [Google Scholar]

| Parameter | Value | Parameter | Value |

|---|---|---|---|

| VTH (V) | −1.2 | ft (GHz) | 85 |

| VBDG (V) | 10 | Gm_Peak (mS/mm) | 495 |

| Idmax (mA/mm) | 650 | Pdensity (W/mm) | 0.8 |

| Idss (mA/mm) | 500 | CMIM (pF/mm2) | 400 |

| Parameter | Value | Parameter | Value |

|---|---|---|---|

| rg (Ω) | 1.5 | Ld (pH) | 8.5 |

| rd (Ω) | 1.2 | Ls (pH) | 0.7 |

| rs (Ω) | 0.2 | Cpg (fF) | 9.5 |

| Lg (pH) | 9.5 | Cpd (fF) | 17.5 |

| Parameter | Value |

|---|---|

| rgs (Ω) | 41.5 |

| Cpg (fF) | 89.0 |

| Cps (fF) | 33.5 |

| Lgs (pH) | 55.0 |

| Reference | Process | Frequency (GHz) | P−1dB (dBm) | PAE (%) | Gain (dB) | IMD3 (dBc) | Size (mm2) |

|---|---|---|---|---|---|---|---|

| [10] | 0.15 µm GaAs | 20–23 | 31 | 24 | 9.5 | - | - |

| [11] | 0.25 µm GaAs | 22.8–23.5 | 28 | 15.3 | 25 | - | 2.52 |

| [12] | 0.25 µm GaAs | 18–27 | 31.4 | 27 | 14 | 18 | 3.91 |

| [13] | 0.15 µm GaAs | 17–20 | 28 | 30 | 21 | 14 | 2.96 |

| [14] | 0.15 µm GaAs | 24–28 | 28 | 21 | 21 | 15 | 4.50 |

| This work | 0.15 µm GaAs | 20–22 | 30 | 34 | 27 | 20 | 2.80 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhu, H.; Chen, W.; Huang, J.; Wang, Z.; Yu, F. A High-Efficiency K-band MMIC Linear Amplifier Using Diode Compensation. Electronics 2019, 8, 487. https://doi.org/10.3390/electronics8050487

Zhu H, Chen W, Huang J, Wang Z, Yu F. A High-Efficiency K-band MMIC Linear Amplifier Using Diode Compensation. Electronics. 2019; 8(5):487. https://doi.org/10.3390/electronics8050487

Chicago/Turabian StyleZhu, Heng, Wei Chen, Jianhua Huang, Zhiyu Wang, and Faxin Yu. 2019. "A High-Efficiency K-band MMIC Linear Amplifier Using Diode Compensation" Electronics 8, no. 5: 487. https://doi.org/10.3390/electronics8050487

APA StyleZhu, H., Chen, W., Huang, J., Wang, Z., & Yu, F. (2019). A High-Efficiency K-band MMIC Linear Amplifier Using Diode Compensation. Electronics, 8(5), 487. https://doi.org/10.3390/electronics8050487