GA-BP in Thermal Fatigue Failure Prediction of Microelectronic Chips

Abstract

:1. Introduction

2. Thermal Fatigue Life Prediction Model

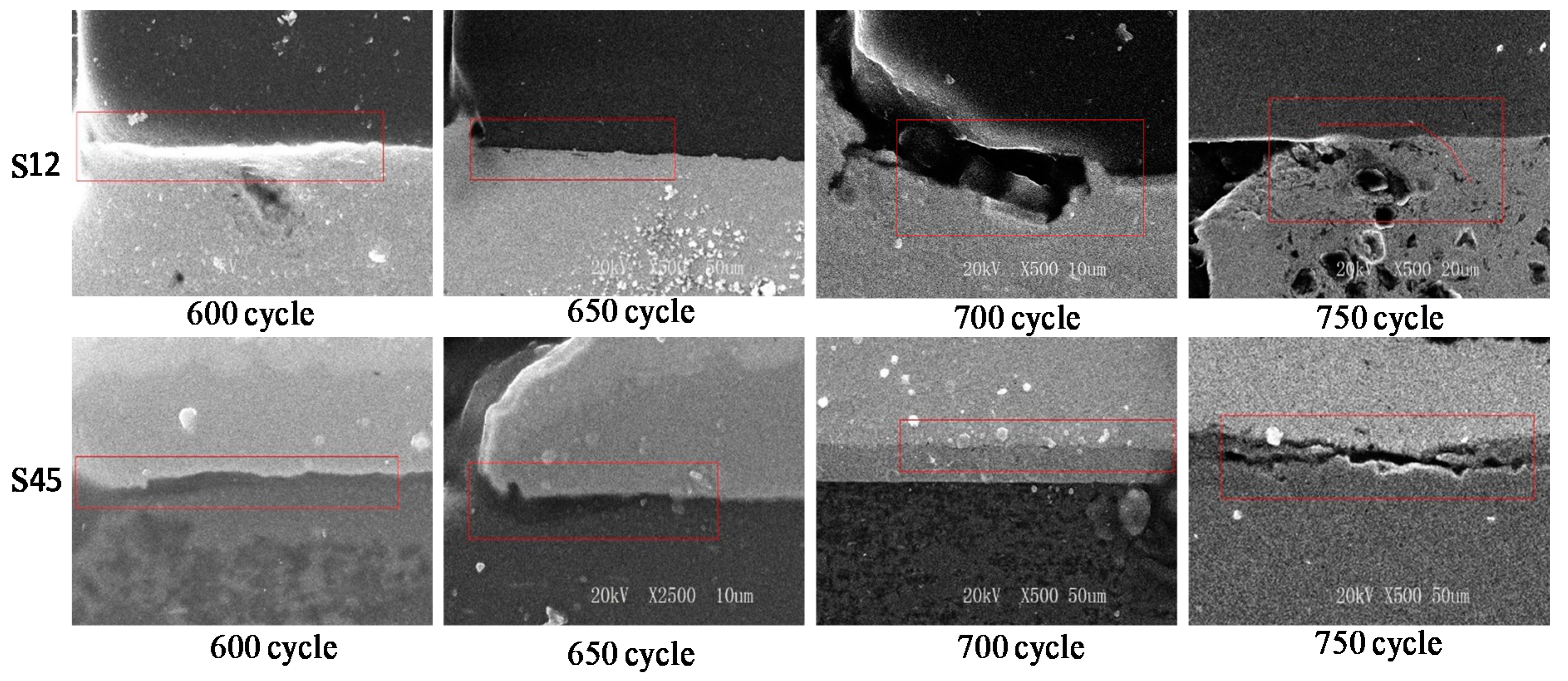

2.1. Thermal Fatigue Tests

2.2. FEM Model

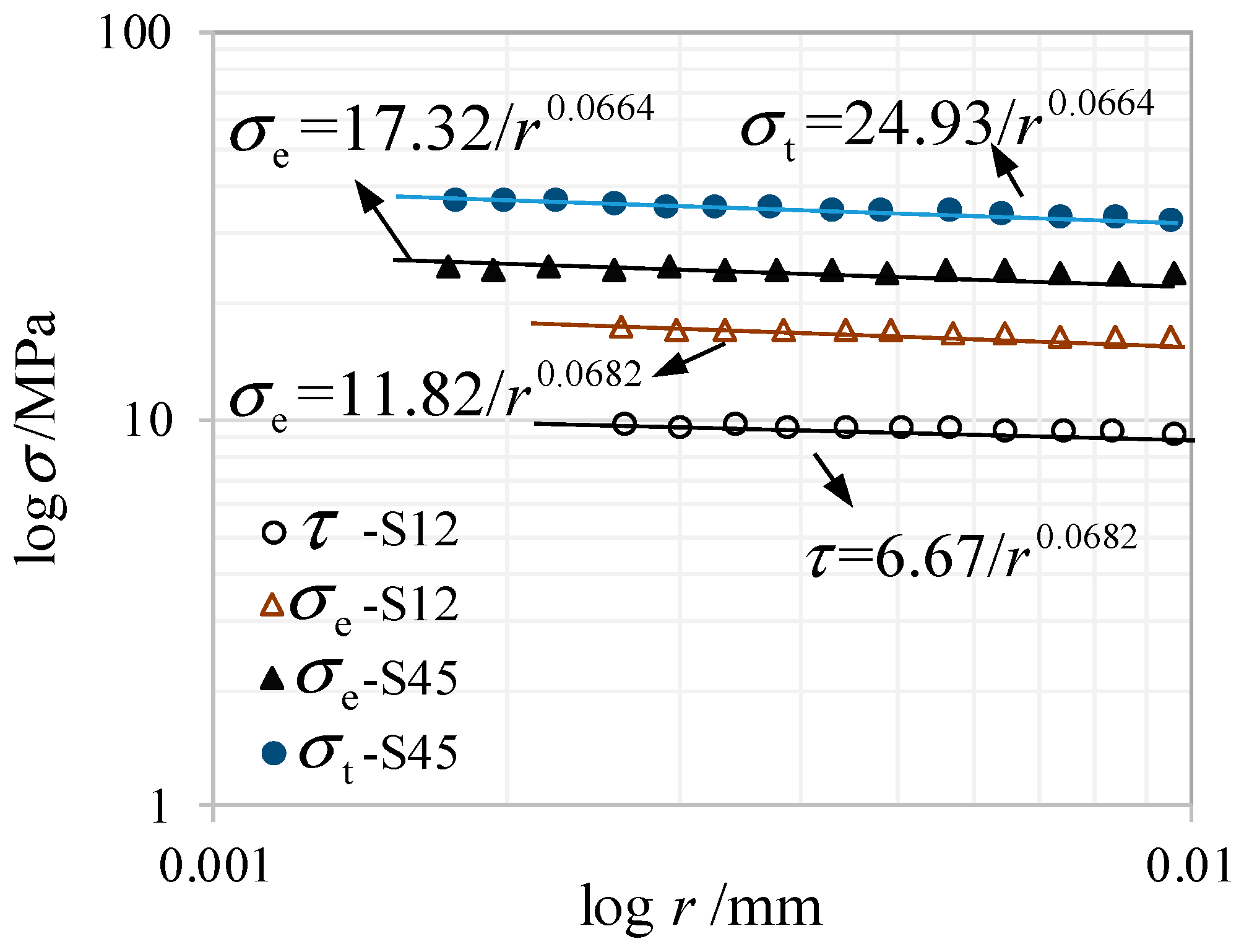

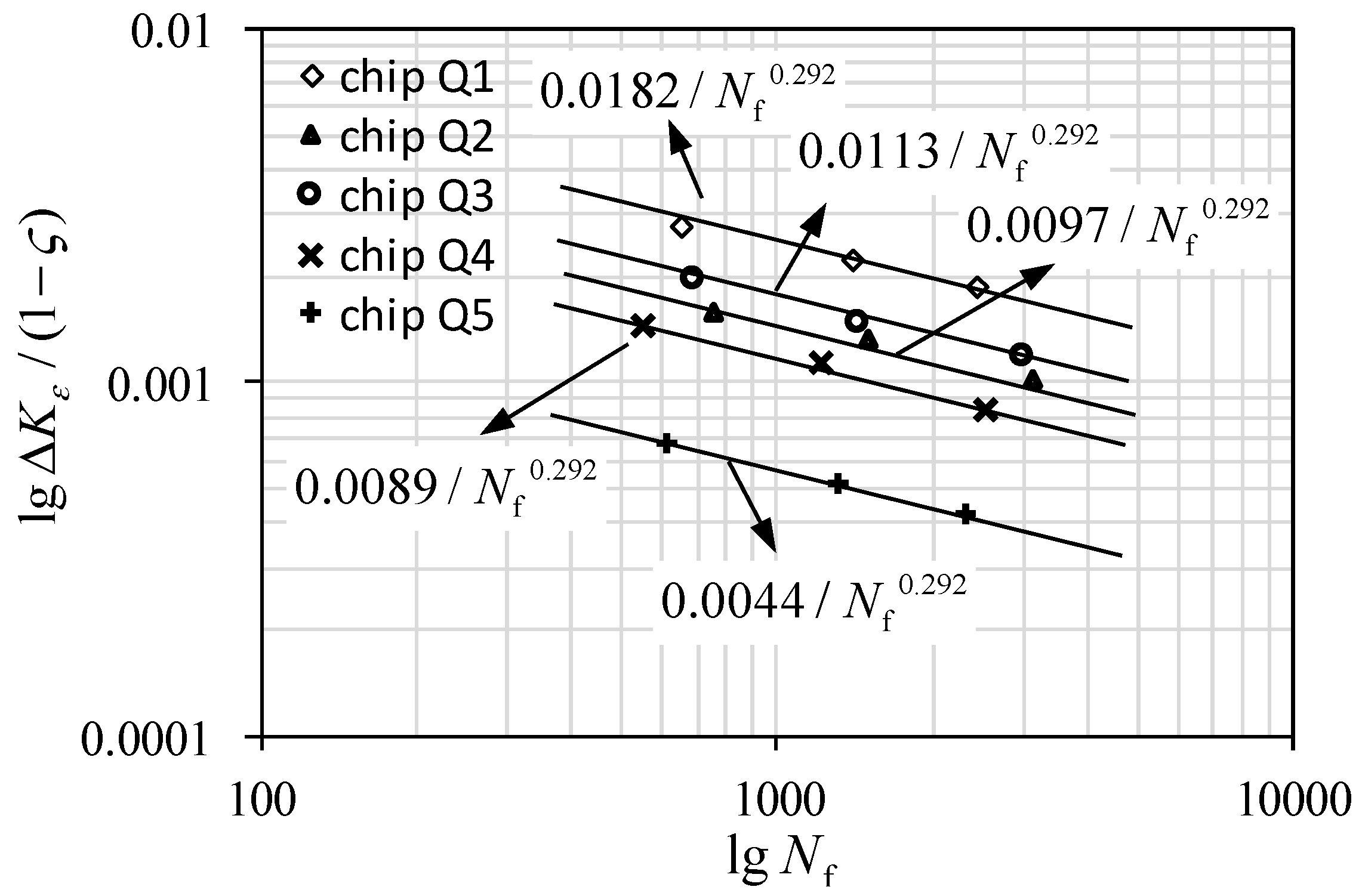

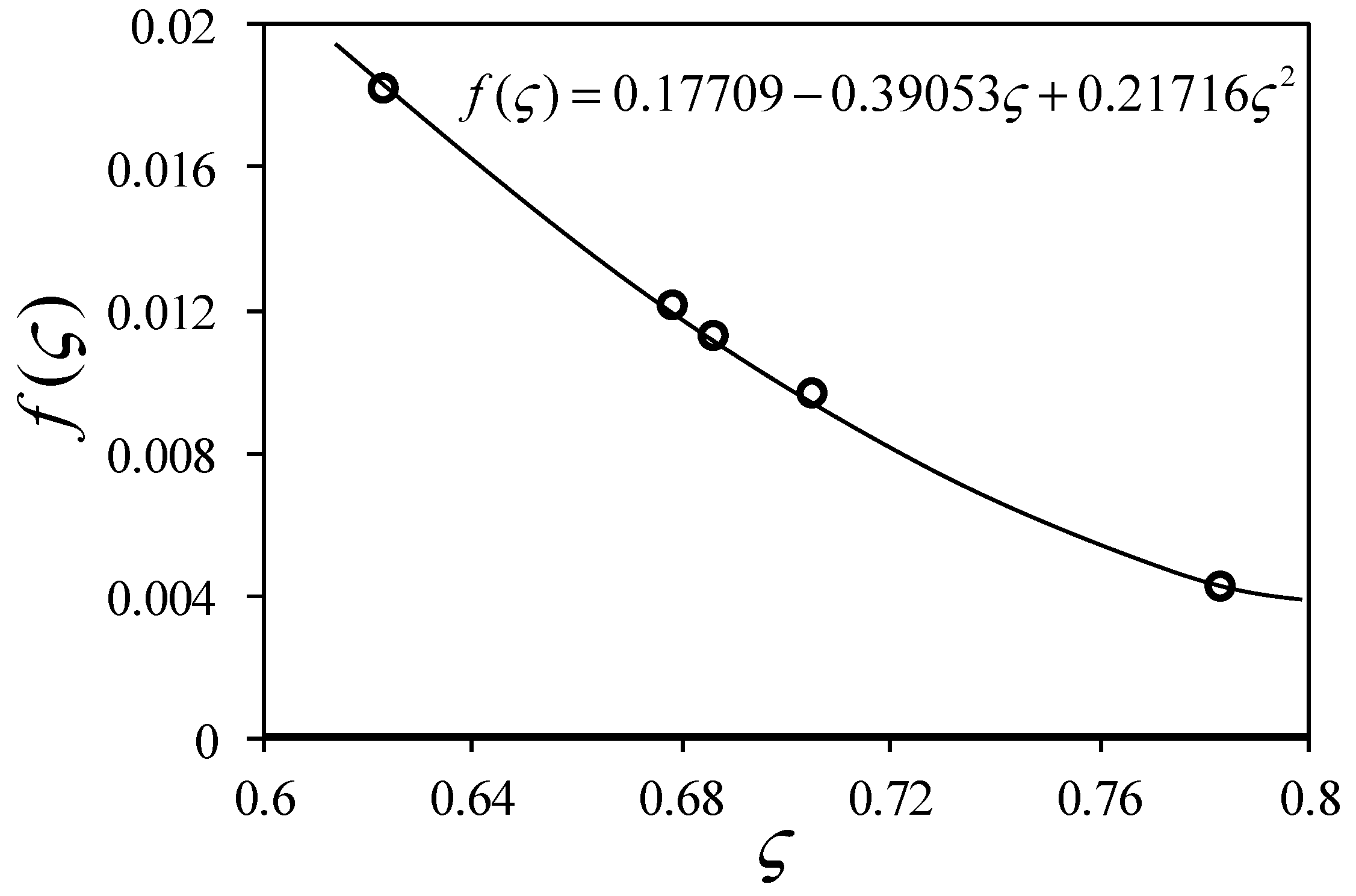

2.3. Thermal Fatigue Life Prediction Model

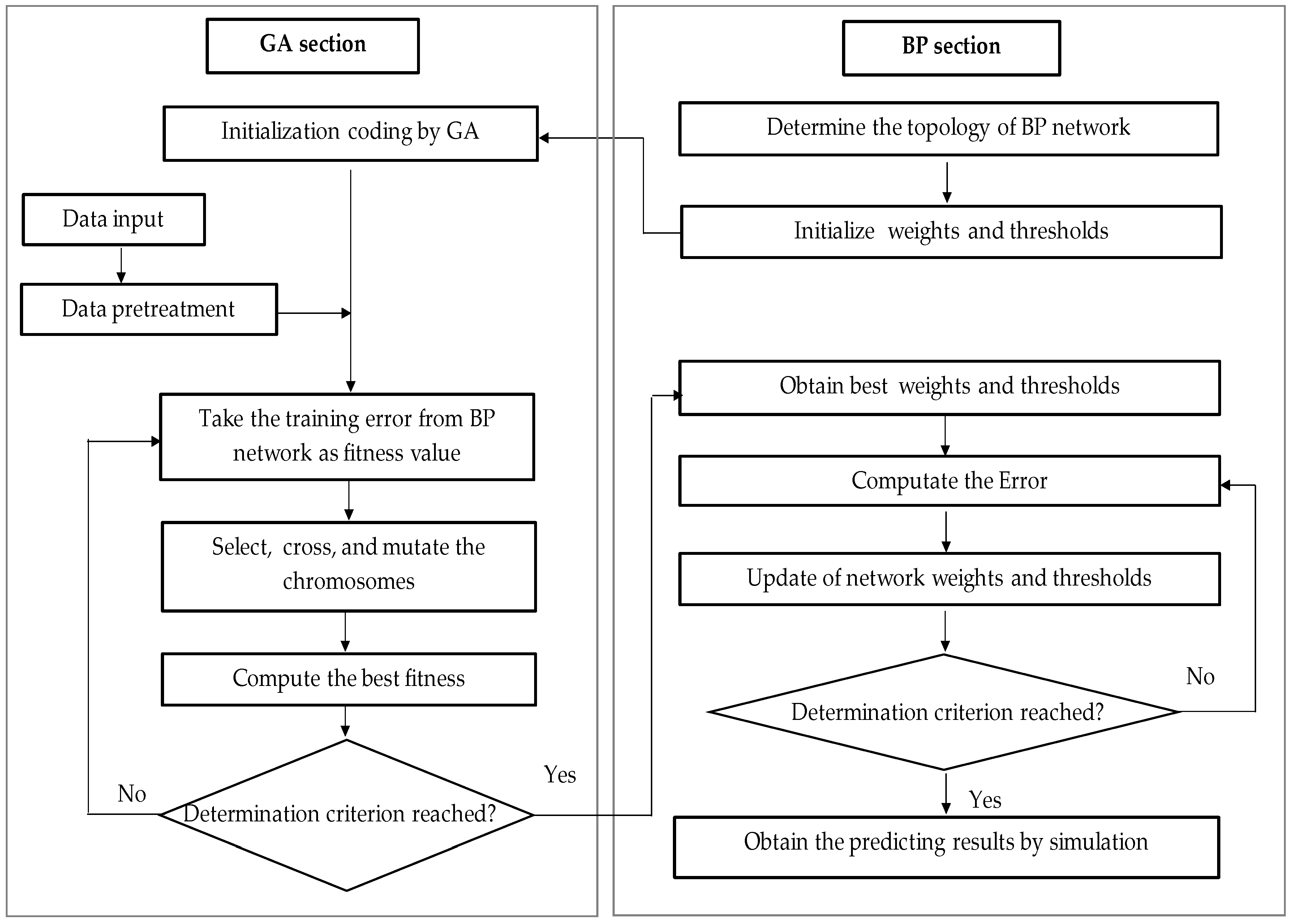

3. Method of the BP Artificial Neural Network Based on a Genetic Algorithm

3.1. GA-BP: Theoretical Background

3.2. GA-BP Hybrid Programming

4. GA-BP Model Developed for Thermal Fatigue Life Prediction

4.1. Variables in the Model

4.2. Predicted Results

5. Conclusions

Author Contributions

Acknowledgments

Conflicts of Interest

References

- Lee, W.W.; Nguyen, L.T.; Selvaduray, G.S. Solder joint fatigue models: review and applicability to chip scale packages. Microelectron. Reliab. 2000, 40, 231–244. [Google Scholar] [CrossRef]

- Su, S.N.; Akkara, F.J.; Abueed, M.; Jian, M.H.; Hamasha, S.; Suhling, J.; Lall, P. Fatigue properties of lead-free doped solder joints. In Proceedings of the 2018 17th IEEE Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems (ITherm), San Diego, CA, USA, 29 May–1 June 2018; pp. 1243–1248. [Google Scholar]

- Zhu, Q.S.; Gao, F.; Ma, H.C.; Liu, Z.Q.; Guo, J.D.; Zhang, L. Failure behavior of flip chip solder joint under coupling condition of thermal cycling and electrical current. J. Mater. Sci. Mater. Electron. 2018, 29, 5025–5033. [Google Scholar] [CrossRef]

- Xu, A.Q.; Nied, H.F. Finite element analysis of stress singularities in attached flip chip packages. ASME J. Electron. Packag. 2000, 122, 301–305. [Google Scholar] [CrossRef]

- Erinc, M.; Schreurs, P.J.G.; Geers, M.G.D. Integrated numerical-experimental analysis of interfacial fatigue fracture in SnAgCu solder joints. Int. J. Solids Struct. 2007, 44, 5680–5694. [Google Scholar] [CrossRef]

- Xiong, M.Y.; Zhang, L. Interface reaction and intermetallic compound growth behavior of Sn-Ag-Cu lead-free solder joints on different substrates in electronic packaging. J. Mater. Sci. 2019, 54, 1741–1768. [Google Scholar] [CrossRef]

- Vandevelde, B.; Gonzalez, M.; Limaye, P.; Ratchev, P.; Beyne, E. Thermal cycling reliability of SnAgCu and SnPb solder joints: A comparison for several IC-packages. Microelectron. Reliab. 2007, 47, 259–265. [Google Scholar] [CrossRef]

- Syed, A.R. Accumulated creep strain and energy density based thermal fatigue life prediction models for SnAgCu solder joints. In Proceedings of the 54th Electronic Components and Technology Conference (IEEE Cat. No.04CH37546), Las Vegas, NV, USA, 4 June 2004; pp. 737–746. [Google Scholar]

- Pang, J.H.L.; Tan, T.I.; Sitaraman, S.K. Thermo-mechanical analysis of solder joint fatigue and creep in a flip chip on board package subjected to temperature cycling loading. In Proceedings of the 48th IEEE Electronic Components and Technology Conference, Seattle, WA, USA, 25–28 May 1998; pp. 878–883. [Google Scholar]

- Zhu, S.P.; Huang, H.Z.; He, L.P.; Liu, Y.; Wang, Z.L. A generalized energy-based fatigue-creep damage parameters for life prediction of turbine disk alloys. Eng. Fract. Mech. 2012, 90, 89–100. [Google Scholar] [CrossRef]

- Hattori, T.; Sakata, S.; Murakami, G. A stress singularity parameter approach for evaluating the interfacial reliability of plastic encapsulated lsi devices. ASME J. Electron. Packag. 1989, 111, 243–248. [Google Scholar] [CrossRef]

- Gradin, P.A. A fracture criterion for edge-bonded bimaterial bodies. J. Compos. Mater. 1982, 16, 448–456. [Google Scholar] [CrossRef]

- Groth, H.L. Stress singularities and fracture at interface corners in bonded joints. Int. J. Adhes. Adhes. 1988, 8, 107–113. [Google Scholar] [CrossRef]

- Reedy, E.D., Jr.; Guess, T.R. Comparison of butt tensile strength data with interface corner stress intensity factor prediction. Int. J. Solids Struct. 2007, 30, 2929–2936. [Google Scholar] [CrossRef]

- Liang, J.; Gollhardt, N.; Lee, P.S.; Heinrich, S.; Schroeder, S. An integrated fatigue life prediction methodology for optimum design and reliability assessment of solder interconnections. In Proceedings of the Pacific Rim/ASME International Intersociety Electronic and Photonic Packaging Conference, Kohala Coast, HI, USA, 15–19 June 1997; pp. 1583–1592. [Google Scholar]

- Kim, D.G.; Kim, J.W.; Jung, S.B. Evaluation of solder joint reliability in flip chip package under thermal shock test. Thin Solid Films 2006, 504, 426–430. [Google Scholar] [CrossRef]

- Munz, D.; Yang, Y.Y. Stress singularities at interface in bonded dissimilar materials under mechanical and thermal loading. J. Appl. Mech. 1992, 59, 857–861. [Google Scholar] [CrossRef]

- Liu, S.Q.; McDonald, S.; Sweatman, K.; Nogita, K. The effects of precipitation strengthening and solid solution strengthening on strain rate sensitivity of lead-free solders: Review. Microelectron. Reliab. 2018, 84, 170–180. [Google Scholar] [CrossRef]

- Pleune, T.T.; Chopra, O.K. Using artificial neural networks to predict the fatigue life of carbon and low-alloy steels. Nucl. Eng. Des. 2000, 197, 1–12. [Google Scholar] [CrossRef]

- Venkatesh, V.H.; Rack, J. A neural network approach to elevated temperature creep-fatigue life prediction. Int. J. Fatigue 1999, 21, 225–234. [Google Scholar] [CrossRef]

- Haque, M.E.; Sudhakar, K.V. Prediction of corrosion-fatigue behavior DP steel through artificial neural network. Int. J. Fatigue 2001, 23, 1–4. [Google Scholar] [CrossRef]

- Kropat, E.; Weber, G.W. Fuzzy target-environment networks and fuzzy-regression approaches. Am. Inst. Math. Sci. 2018, 8, 135–155. [Google Scholar] [CrossRef]

- Mohantya, J.R.; Mahantaa, T.K.; Mohantyb, A.; Thatoi, D.N. Prediction of constant amplitude fatigue crack growth life of 2024 T3Al alloy with R-ratio effect by GP. Appl. Soft Comput. 2015, 26, 428–434. [Google Scholar] [CrossRef]

- Ding, S.F.; Su, C.Y.; Yu, J.Z. An optimizing BP neural network algorithm based on genetic algorithm. Artif. Intell. Rev. 2011, 36, 153–162. [Google Scholar] [CrossRef]

- Conkey, D.B.; Brown, A.N.; Caravaca-Aguirre, A.M.; Piestun, R. Genetic algorithm optimization for focusing through turbid media in noisy environments. Opt. Express 2012, 20, 4840–4849. [Google Scholar] [CrossRef] [PubMed]

- Vassilopoulos, A.P.; Bedi, R. Adaptive neuro-fuzzy inference system in modelling fatigue life of multidirectional composite laminates. Comput. Mate. Sci. 2008, 43, 1086–1093. [Google Scholar] [CrossRef]

- Huang, X.G.; Han, Z.Y. Interface singular field analysis and thermal fatigue failure of solder joint in a stacked electronic modules. J. Mater. Sci. Mater. Electron. 2016, 27, 8299–8311. [Google Scholar] [CrossRef]

- Qian, Z.F.; Lu, M.F.; Ren, W.; Liu, S. Fatigue life prediction of flip-chips in terms of nonlinear behaviors of solder and underfill. In Proceedings of the 49th Electronic Components and Technology Conference (Cat. No.99CH36299), San Diego, CA, USA, 1–4 June 1999; pp. 141–148. [Google Scholar]

- Chen, X.; Song, J.; Kim, K.S. Fatigue life of 63Sn–37Pb solder related to load drop under uniaxial and torsional loading. Int. J. Fatigue 2006, 28, 767–776. [Google Scholar] [CrossRef]

- Whitley, D. A genetic algorithm tutorial. Stat. Comput. 1994, 4, 65–85. [Google Scholar] [CrossRef]

- Leung, Y.W.; Wang, Y.P. An orthogonal genetic algorithm with quantization for global numerical optimization. IEEE Trans. Evol. Comput. 2001, 5, 41–53. [Google Scholar] [CrossRef]

- Yao, X.; Liu, Y. A new evolutionary system for evolving artificial neural networks. IEEE Trans. Neural Netw. 1997, 8, 694–713. [Google Scholar] [CrossRef]

- Cook, D.F.; Ragsdale, C.T.; Major, R.L. Combining a neural network with a genetic algorithm for process parameter optimization. Eng. Appl. Artif. Intell. 2000, 13, 391–396. [Google Scholar] [CrossRef]

- Gupta, J.N.D.; Sexton, R.S. Comparing backpropagation with a genetic algorithm for neural network training. Omega 1999, 27, 679–684. [Google Scholar] [CrossRef]

- Genel, K. Application of artificial neural network for predicting strain-life fatigue properties of steels on the basis of tensile tests. Int. J. Fatigue 2004, 26, 1027–1035. [Google Scholar] [CrossRef]

| Chip Type | Q1 | Q2 | Q3 | Q4 | Q5 |

|---|---|---|---|---|---|

| Nf (Tmax = 150 °C) | 650 | 750 | 690 | 550 | 615 |

| Nf (Tmax = 120 °C) | 1400 | 1500 | 1430 | 1220 | 1310 |

| Nf (Tmax = 100 °C) | 2430 | 3150 | 2980 | 2540 | 2330 |

| Chip Type | Interface Edge | Maximum Strain State | |

|---|---|---|---|

| ς | Kς (mmς) | ||

| Q1 | S12 | 0.622 | 0.000447 |

| S45 | 0.532 | 0.001150 | |

| Q2 | S12 | 0.789 | 0.000151 |

| S45 | 0.687 | 0.000238 | |

| Q3 | S12 | 0.762 | 0.000138 |

| S45 | 0.705 | 0.000176 | |

| Q4 | S12 | 0.745 | 0.000157 |

| S45 | 0.678 | 0.000163 | |

| Q5 | S12 | 0.658 | 0.000221 |

| S45 | 0.784 | 0.000067 | |

| Parameter | Implication | Range |

|---|---|---|

| P1 | Population size | 1000 |

| P2 | Function set | power |

| P3 | Number of generation | 100–5000 |

| P4 | Probability of reproduction | 0.1 |

| P5 | Probability of crossover | 0.9 |

| P6 | Maximum depth of initial random organisms | 4 |

| P7 | Maximum depth of organisms after crossover | 10 |

| Sample No. | Chip Type | h /mm | d /mm | E /GPa | Tmax /°C | Predicted ς | Estimated ς | Error /% | Predicted Kς | Estimated Kς | Error /% |

|---|---|---|---|---|---|---|---|---|---|---|---|

| 1 | I | 0.24 | 6.6 | 42.10 | 150 | 0.831 | 0.851 | 2.35 | 0.000974 | 0.001050 | 7.24 |

| 2 | I | 0.22 | 7.0 | 41.62 | 120 | 0.584 | 0.622 | 6.11 | 0.000821 | 0.000855 | 3.98 |

| 3 | II | 0.22 | 6.6 | 40.95 | 150 | 0.655 | 0.687 | 4.66 | 0.000478 | 0.000498 | 4.02 |

| 4 | II | 0.22 | 6.8 | 40.63 | 120 | 0.693 | 0.687 | −0.87 | 0.000398 | 0.000425 | 6.35 |

| 5 | III | 0.23 | 6.4 | 39.81 | 150 | 0.751 | 0.705 | −6.52 | 0.000412 | 0.000425 | 3.06 |

| 6 | III | 0.21 | 6.6 | 43.58 | 120 | 0.746 | 0.705 | −5.82 | 0.000324 | 0.000342 | 5.26 |

| 7 | IV | 0.24 | 6.6 | 42.15 | 150 | 0.647 | 0.678 | 4.57 | 0.000484 | 0.000523 | 7.46 |

| 8 | IV | 0.22 | 7.0 | 44.17 | 120 | 0.691 | 0.678 | −1.92 | 0.000419 | 0.000445 | 5.84 |

| 9 | V | 0.21 | 6.6 | 38.95 | 150 | 0.737 | 0.784 | 5.99 | 0.000158 | 0.000149 | −6.04 |

| 10 | V | 0.22 | 6.8 | 43.61 | 120 | 0.752 | 0.784 | 4.08 | 0.000121 | 0.000115 | −5.22 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Han, Z.; Huang, X. GA-BP in Thermal Fatigue Failure Prediction of Microelectronic Chips. Electronics 2019, 8, 542. https://doi.org/10.3390/electronics8050542

Han Z, Huang X. GA-BP in Thermal Fatigue Failure Prediction of Microelectronic Chips. Electronics. 2019; 8(5):542. https://doi.org/10.3390/electronics8050542

Chicago/Turabian StyleHan, Zhongying, and Xiaoguang Huang. 2019. "GA-BP in Thermal Fatigue Failure Prediction of Microelectronic Chips" Electronics 8, no. 5: 542. https://doi.org/10.3390/electronics8050542