Calculation of Semiconductor Power Losses of a Three-Phase Quasi-Z-Source Inverter

Abstract

:1. Introduction

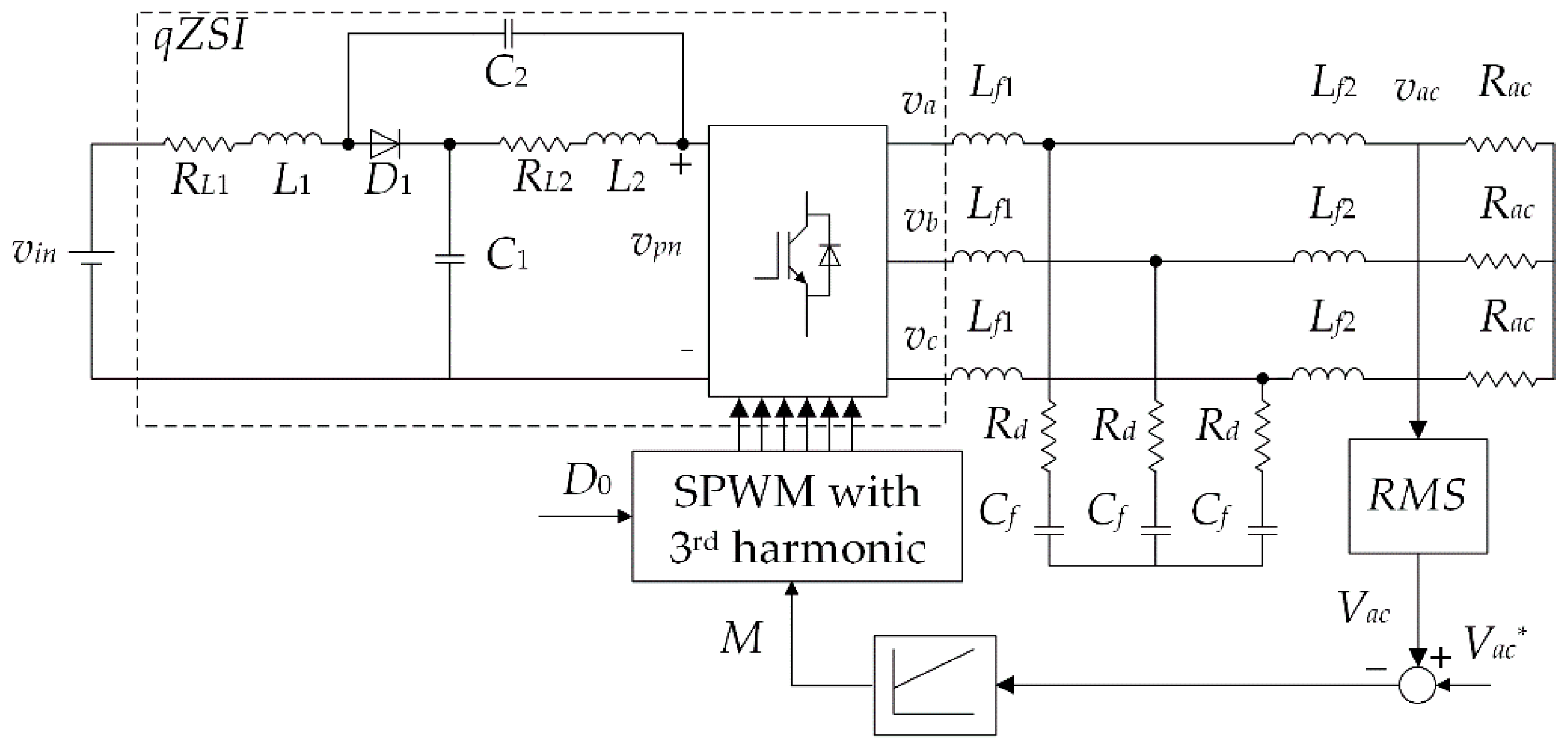

2. Quasi-Z-Source Inverter Power Losses

3. Proposed Semiconductor LCAs for the Quasi-Z-Source Inverter

3.1. Loss-Calculation Algorithm 1

3.2. Loss-Calculation Algorithm 2

4. Experimental Testing and Evaluation

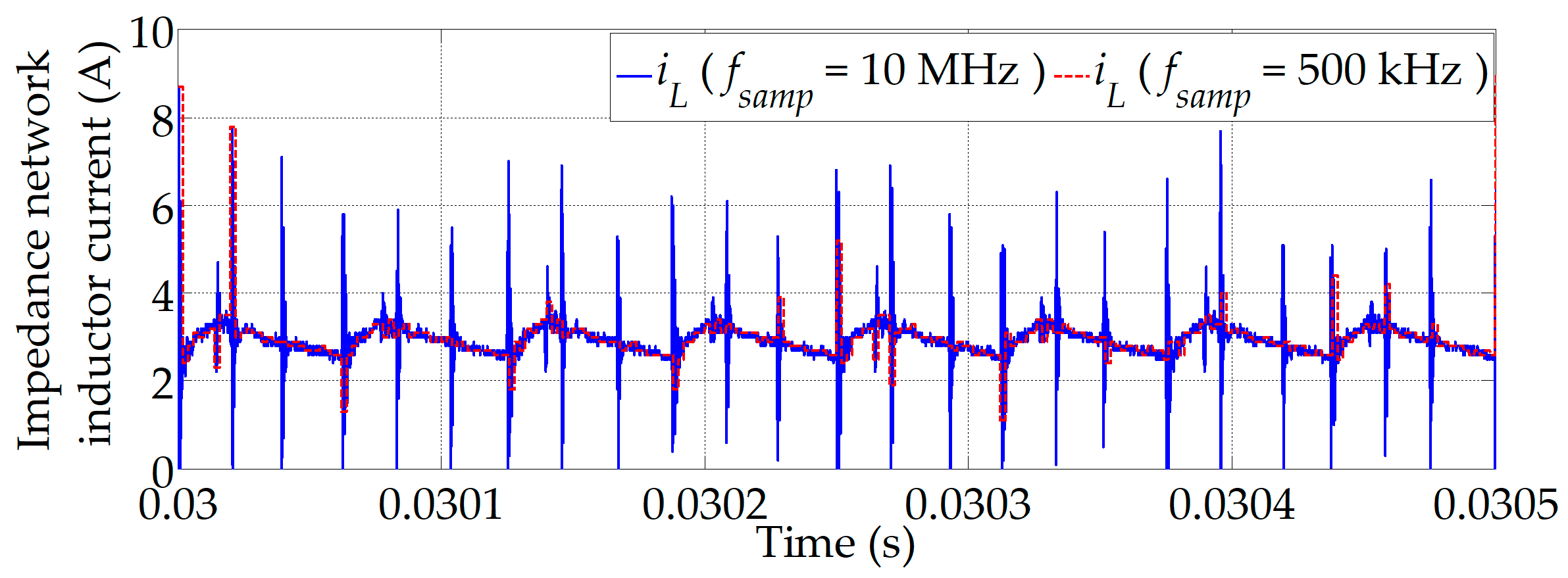

4.1. Implementation Requirements of the Proposed Loss-Calculation Algorithms

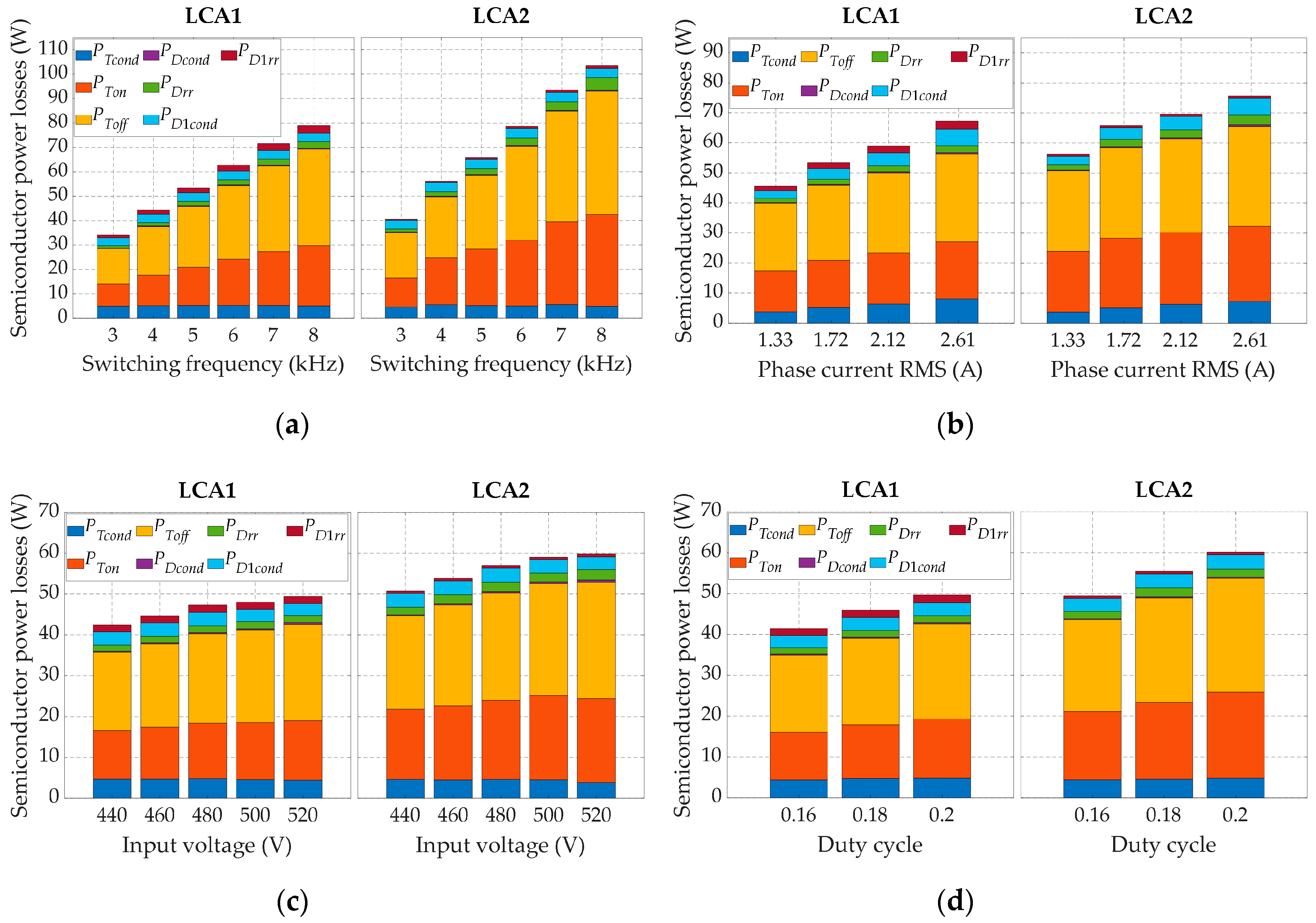

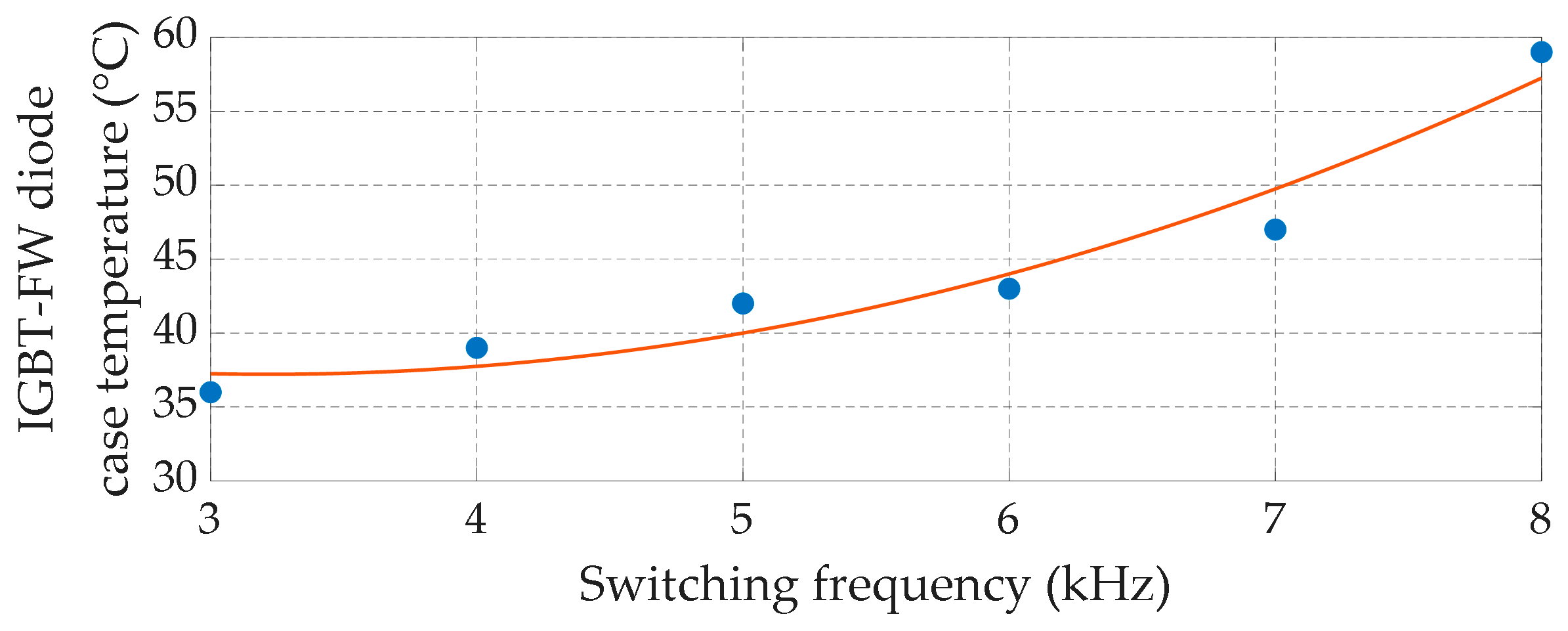

4.2. Experimental Results

4.2.1. Correction of the IGBT Switching Losses Calculation

4.2.2. Efficiency and Semiconductor Losses Share of the qZSI

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

Appendix A

- Rce = 0.066105 Ω, Vce,0 = 0.6823 V

- RD = 0.0862 Ω, VD,0 = 0.774 V

- RD1 = 0.1225 Ω, VD1,0 = 0.999 V

- a0on = 0.18, a1on = 0.074, a2on = −7.2 × 10−4, a3on = 2.537 × 10−5

- a0off = 0.258, a1off = 0.081, a2off = −1.41 × 10−4, a3off = 0

- b0D = 0.036, b1D = 0.04, b2D = −3.76 × 10−4, b3D = 9.9 × 10−7

- b0D1 = 0.0145, b1D1 = 0.052, b2D1 = −0.0012, b3D1 = 5.34 × 10−6

Appendix B

Appendix C

Appendix D

References

- Peng, F.Z. Z-source inverter. IEEE Trans. Ind. Appl. 2003, 39, 504–510. [Google Scholar] [CrossRef]

- Ellabban, O.; Abu-Rub, H. Z-source inverter: Topology improvements review. IEEE Ind. Electron. 2016, 10, 6–24. [Google Scholar] [CrossRef]

- Siwakoti, Y.P.; Peng, F.Z.; Blaabjerg, F.; Loh, F.C.; Town, G.E. Impedance-source networks for electric power conversion part I: A topological review. IEEE Trans. Power Electr. 2015, 30, 699–716. [Google Scholar] [CrossRef]

- Siwakoti, Y.P.; Peng, F.Z.; Blaabjerg, F.; Loh, F.C.; Town, G.E.; Yang, S. Impedance-source networks for electric power conversion part II: Review of control and modulation techniques. IEEE Trans. Power Electr. 2015, 30, 1887–1906. [Google Scholar] [CrossRef]

- Anderson, J.; Peng, F.Z. Four quasi-Z-source inverters. In Proceedings of the 2008 IEEE Power Electronics Specialists Conference, Rhodes, Greece, 15–19 June 2008. [Google Scholar] [CrossRef]

- Franke, W.T.; Mohr, M.; Fuchs, F.W. Comparison of a Z-Source inverter and a voltage-source inverter linked with a DC/DC-boost-converter for wind turbines concerning their efficiency and installed semiconductor power. In Proceedings of the 2008 IEEE Power Electronics Specialists Conference, Rhodes, Greece, 15–19 June 2008. [Google Scholar] [CrossRef]

- Noroozi, N.; Yaghoubi, M.; Zolghadri, M.R. A modulation method for leakage current reduction in a three-phase grid-tie quasi-Z-source inverter. IEEE Trans. Power Electr. 2019, 34, 5439–5450. [Google Scholar] [CrossRef]

- Cauffet, G.; Keradec, J.P. Digital oscilloscope measurements in high-frequency switching power electronics. IEEE Trans. Instrum. Meas. 1992, 41, 856–860. [Google Scholar] [CrossRef]

- Tektronix. Measuring Power Supply Switching Loss with an Oscilloscope, 1st ed.; Tektronix: Beaverton, OR, USA, 2016. [Google Scholar]

- Iijima, R.; Isobe, T.; Tadano, H. Loss analysis of Z-source inverter using SiC-MOSFET from the perspective of current path in shoot-through mode. In Proceedings of the 18th European Conference on Power Electronics and Applications, Karlsruhe, Germany, 5–9 September 2016. [Google Scholar] [CrossRef]

- Casanellas, F. Losses in PWM inverters using IGBTs. IEE P.-Elect. Pow. Appl. 1994, 141, 235–239. [Google Scholar] [CrossRef]

- Berringer, K.; Marvin, J.; Perruchoud, P. Semiconductor power losses in ac inverters. In Proceedings of the IEEE Industry Applications Conference, Orlando, FL, USA, 8–12 October 1995. [Google Scholar] [CrossRef]

- Bierhoff, M.H.; Fuchs, F.W. Semiconductor losses in voltage source and current source IGBT converters based on analytical derivation. In Proceedings of the IEEE 35th Annual Power Electronics Specialists Conference, Aachen, Germany, 20–25 June 2004. [Google Scholar] [CrossRef]

- Shen, M.; Joseph, A.; Wang, J.; Peng, F.Z.; Adams, D.J. Comparison of traditional inverters and Z-source inverter for fuel cell vehicles. IEEE Trans. Power Electr. 2007, 22, 1453–1463. [Google Scholar] [CrossRef]

- Shen, M.; Joseph, A.; Huang, Y.; Peng, F.Z.; Qian, Z. Design and development of a 50kW Z-source inverter for fuel cell vehicles. In Proceedings of the CES/IEEE 5th International Power Electronics and Motion Control Conference, Shanghai, China, 14–16 August 2006. [Google Scholar] [CrossRef]

- Battiston, A.; Martin, J.; Miliani, E.; Nahid-Mobarakeh, B.; Pierfederici, S.; Meibody-Tabar, F. Comparison criteria for electric traction systems using Z-source/quasi Z-source inverter and conventional architectures. IEEE J. Em. Sel. Top. P. 2014, 2, 467–476. [Google Scholar] [CrossRef]

- Lei, Q.; Peng, F.Z.; He, L.; Yang, S. Power loss analysis of current-fed quasi-Z-source inverter. In Proceedings of the IEEE Energy Conversion Congress and Exposition (ECCE 2010), Atlanta, GA, USA, 12–16 September 2010. [Google Scholar] [CrossRef]

- Zdanowski, M.; Peftitsis, D.; Piasecki, S.; Rabkowski, J. On the design process of a 6-kVA quasi-Z-inverter employing SiC power devices. IEEE Trans. Power Electr. 2016, 31, 7499–7508. [Google Scholar] [CrossRef]

- Abdelhakim, A.; Davari, P.; Blaabjerg, F.; Mattavelli, P. Switching loss reduction in three-phase quasi-Z-source inverters utilizing modified space vector modulation strategies. IEEE Trans. Power Electr. 2017, 33, 4045–4060. [Google Scholar] [CrossRef]

- Bazzi, A.M.; Kimball, J.W.; Kepley, K.; Krein, P.T. A simple analysis tool for estimating power losses in an IGBT-diode pair under hysteresis control in three-phase inverters. In Proceedings of the Twenty-Four Annual IEEE Applied Power Electronics Conference and Exposition, Washington, DC, USA, 15–19 February 2009. [Google Scholar] [CrossRef]

- Bazzi, A.M.; Krein, P.T.; Kimball, J.W.; Kepley, K. IGBT and diode loss estimation under hysteresis switching. IEEE Trans. Power Electron. 2012, 27, 1044–1048. [Google Scholar] [CrossRef]

- Ivakhno, V.; Zamaruiev, V.; Ilina, O. Estimation of semiconductor switching losses under hard switching using Matlab/Simulink subsystem. Electr. Control Commun. Eng. 2013, 2, 20–26. [Google Scholar] [CrossRef]

- Micrometals. Power conversion and line filter application; Issue, L., Ed.; Micrometals Inc.: Anaheim, CA, USA, 2007. [Google Scholar]

- Semikron. Application Manual Power Semiconductors, 2nd ed.; ISLE Verlag: Ilmenau, Germany, 2015. [Google Scholar]

- Grgić, I.; Bubalo, M.; Vukadinović, D.; Bašić, M. Power losses analysis of a three-phase quasi-Z-source inverter. In Proceedings of the 5th International Conference on Smart and Sustainable Technologies, Split, Croatia, 23–26 September 2020. [Google Scholar]

- Cougo, B.; Schneider, H.; Meynard, T. Accurate switching energy estimation of wide bandgap devices used in converters for aircraft applications. In Proceedings of the 15th European Conference on Power Electronics and Applications, Lille, France, 2–6 September 2013. [Google Scholar] [CrossRef]

| Interval | NnST,on | NnST,off | NST,on | NST,off |

|---|---|---|---|---|

| I1 = [0, φ] | 0 | 0 | 2 | 2 |

| I2 = [φ, π/6] | 1 | 1 | 1 | 1 |

| I3 = [π/6, 5π/6] | 1 | 0 | 0 | 1 |

| I4 = [5π/6, (π + φ)] | 1 | 1 | 1 | 1 |

| I5 = [(π + φ), 2π] | 0 | 0 | 2 | 2 |

| Interval | NnST,on | NnST,off | NST,on | NST,off |

|---|---|---|---|---|

| I’1 = [0, φ] | 0 | 0 | 2 | 2 |

| I’2 = [φ, 5π/6] | 1 | 0 | 0 | 1 |

| I’3 = [5π/6, 7π/6] | 1 | 1 | 1 | 1 |

| I’4 = [7π/6, (π + φ)] | 0 | 1 | 2 | 1 |

| I’5 = [(π + φ), 2π] | 0 | 0 | 2 | 2 |

| Switching Frequency | LCA1 | LCA1cor | LCA2 | LCA2cor |

|---|---|---|---|---|

| 3 kHz | 12 W (25%) | −2 W (−4%) | 6 W (12%) | −15 W (−31%) |

| 4 kHz | 27 W (38%) | 6 W (8%) | 15 W (21%) | −8 W (−11%) |

| 5 kHz | 32 W (37%) | 6 W (7%) | 19 W (22%) | −9 W (−10%) |

| 6 kHz | 46 W (42%) | 16 W (14%) | 30 W (27%) | −3 W (−3%) |

| 7 kHz | 53 W (43%) | 17 W (14%) | 32 W (25%) | −10 W (−8%) |

| 8 kHz | 65 W (45%) | 24 W (16%) | 40 W (27%) | −6 W (−4%) |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Grgić, I.; Vukadinović, D.; Bašić, M.; Bubalo, M. Calculation of Semiconductor Power Losses of a Three-Phase Quasi-Z-Source Inverter. Electronics 2020, 9, 1642. https://doi.org/10.3390/electronics9101642

Grgić I, Vukadinović D, Bašić M, Bubalo M. Calculation of Semiconductor Power Losses of a Three-Phase Quasi-Z-Source Inverter. Electronics. 2020; 9(10):1642. https://doi.org/10.3390/electronics9101642

Chicago/Turabian StyleGrgić, Ivan, Dinko Vukadinović, Mateo Bašić, and Matija Bubalo. 2020. "Calculation of Semiconductor Power Losses of a Three-Phase Quasi-Z-Source Inverter" Electronics 9, no. 10: 1642. https://doi.org/10.3390/electronics9101642