Numerical Simulation Analysis of Switching Characteristics in the Source-Trench MOSFET’s

Abstract

:1. Introduction

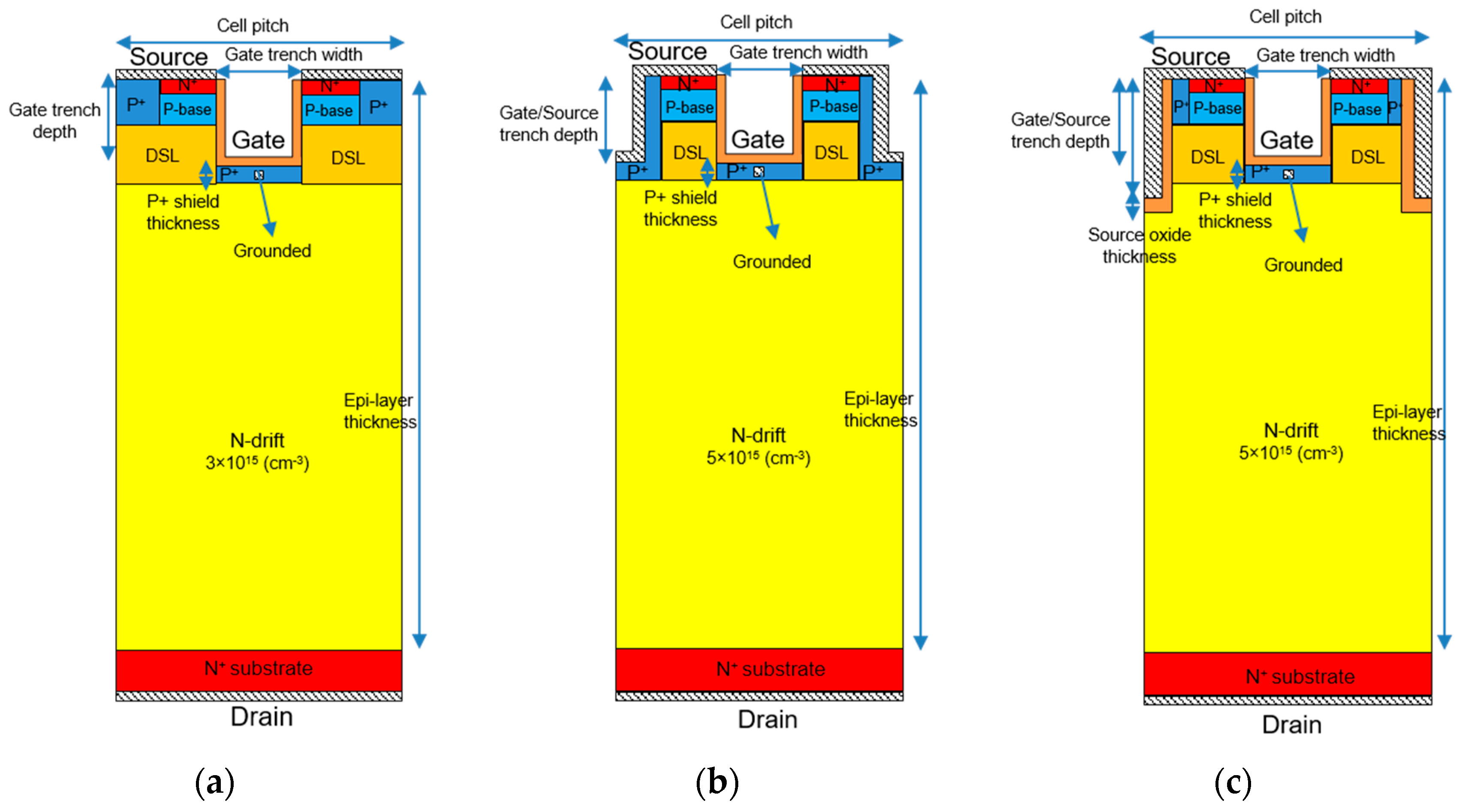

2. Device Structures

3. Results and Discussion

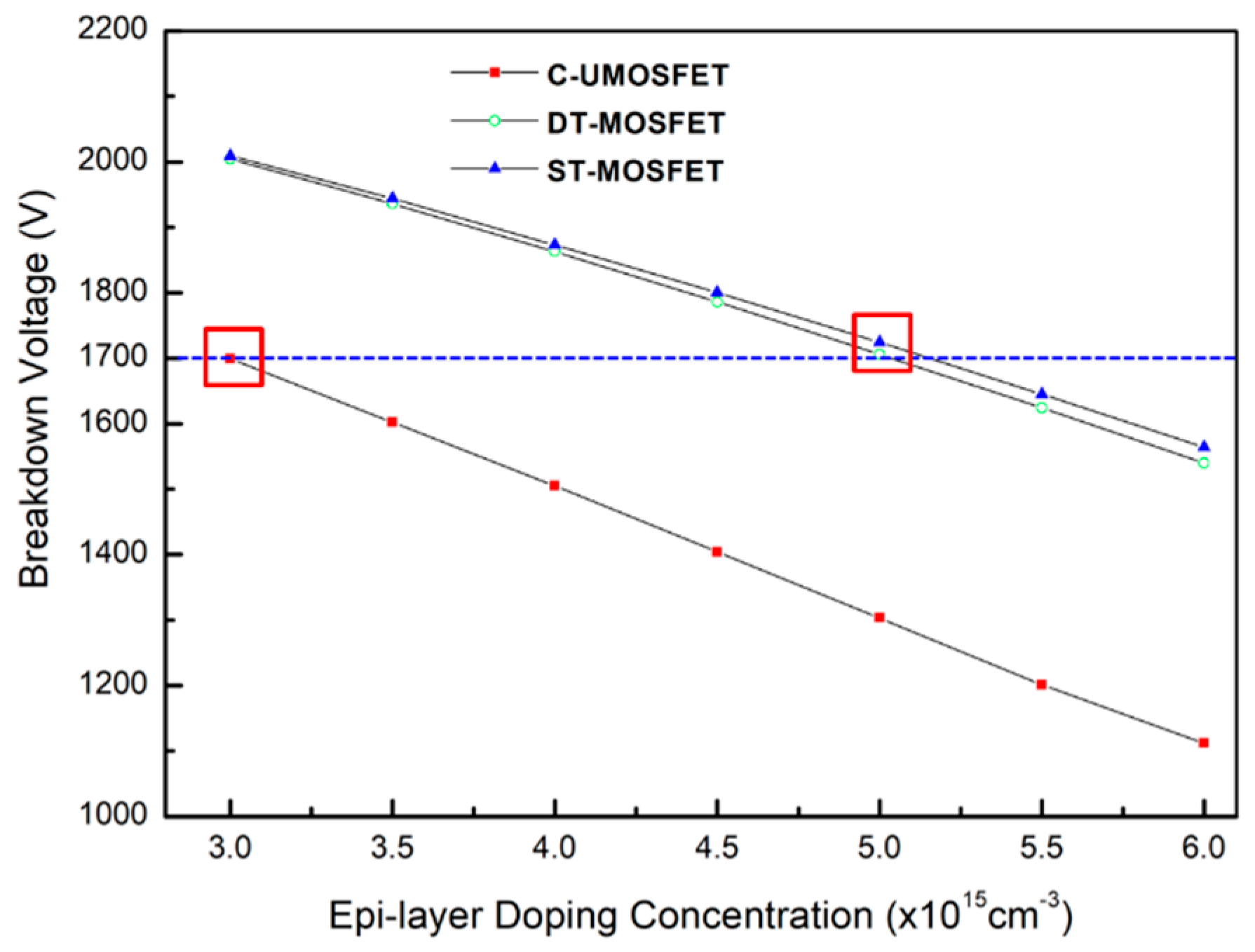

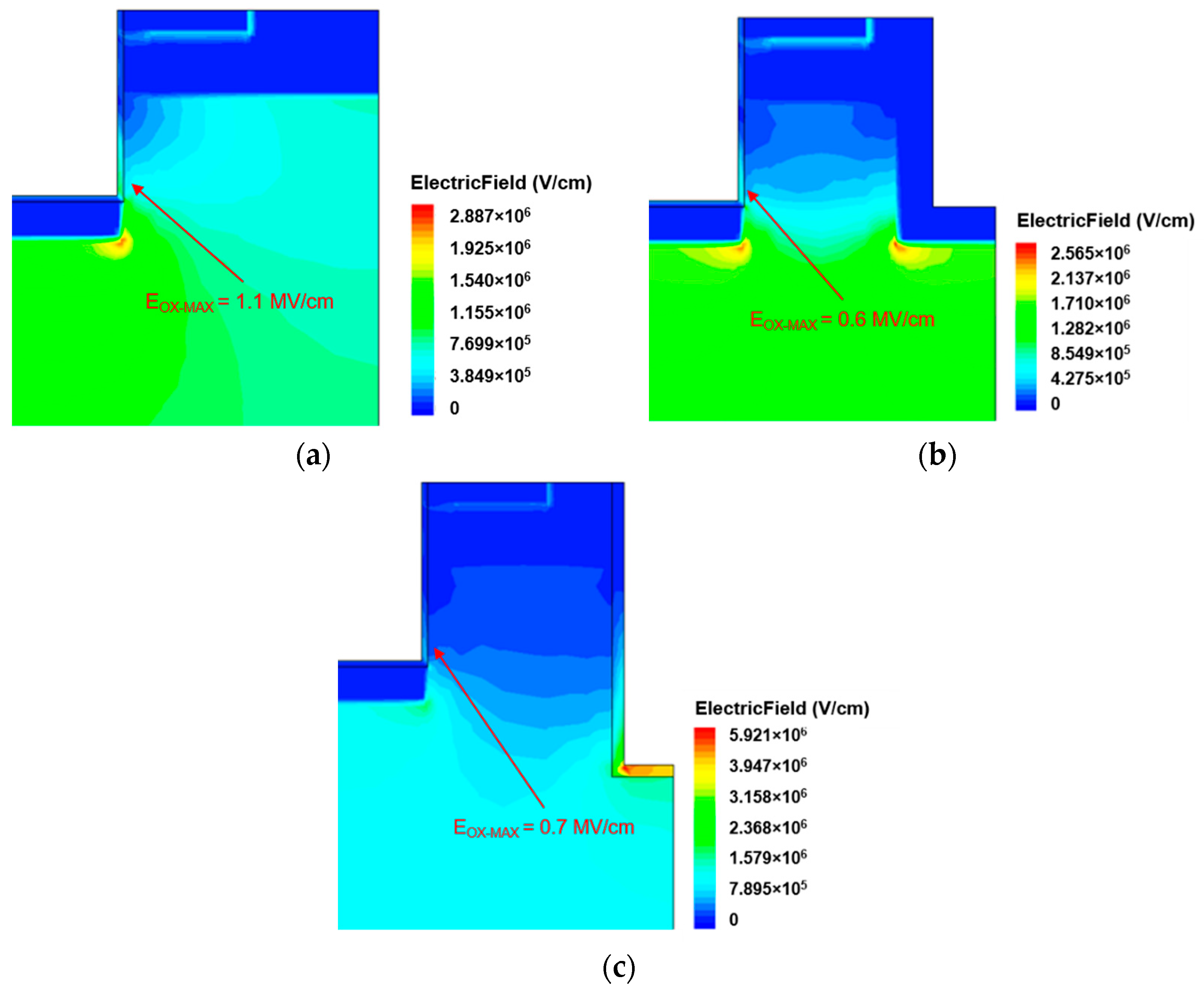

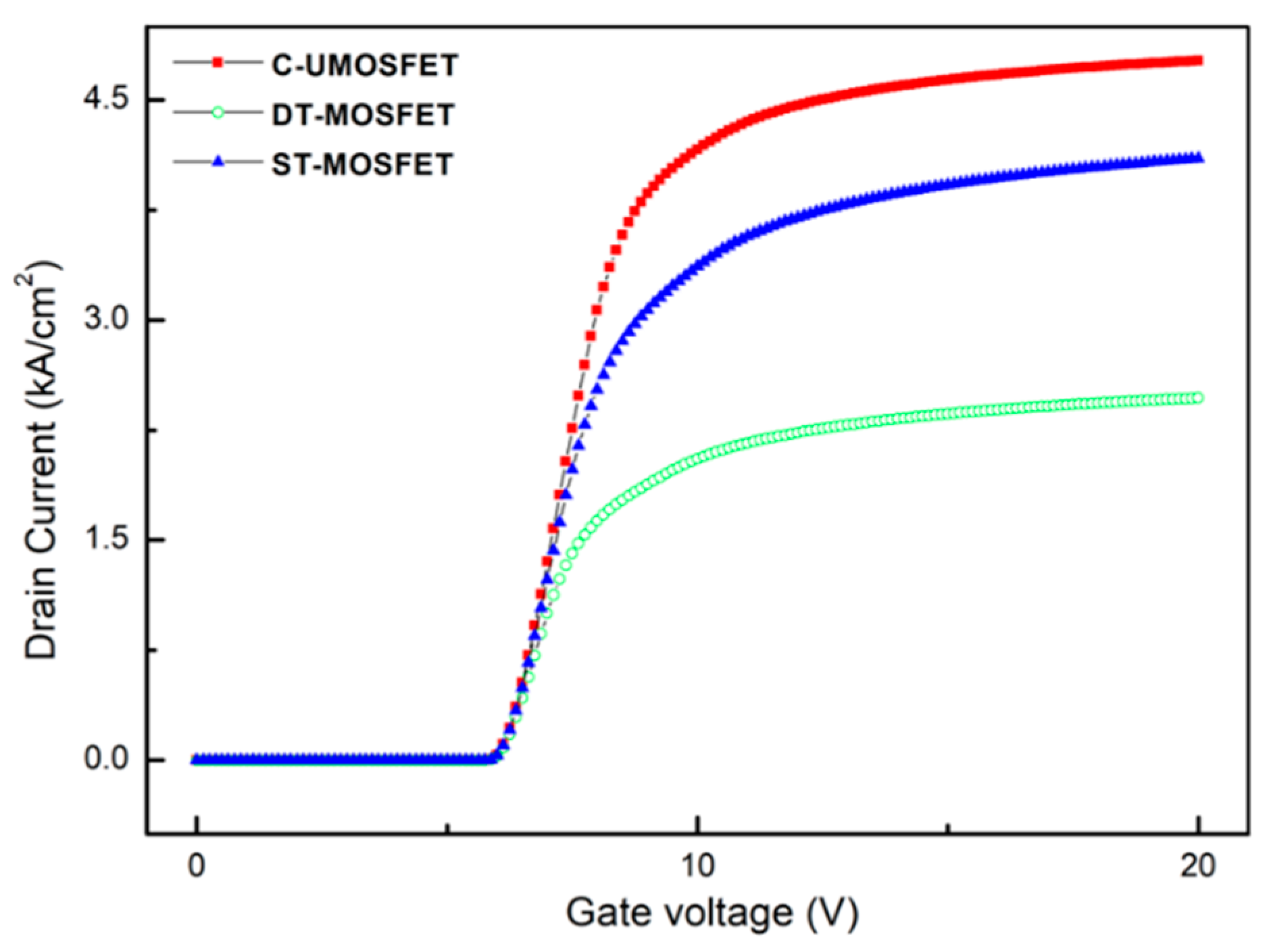

3.1. Static Characteristics

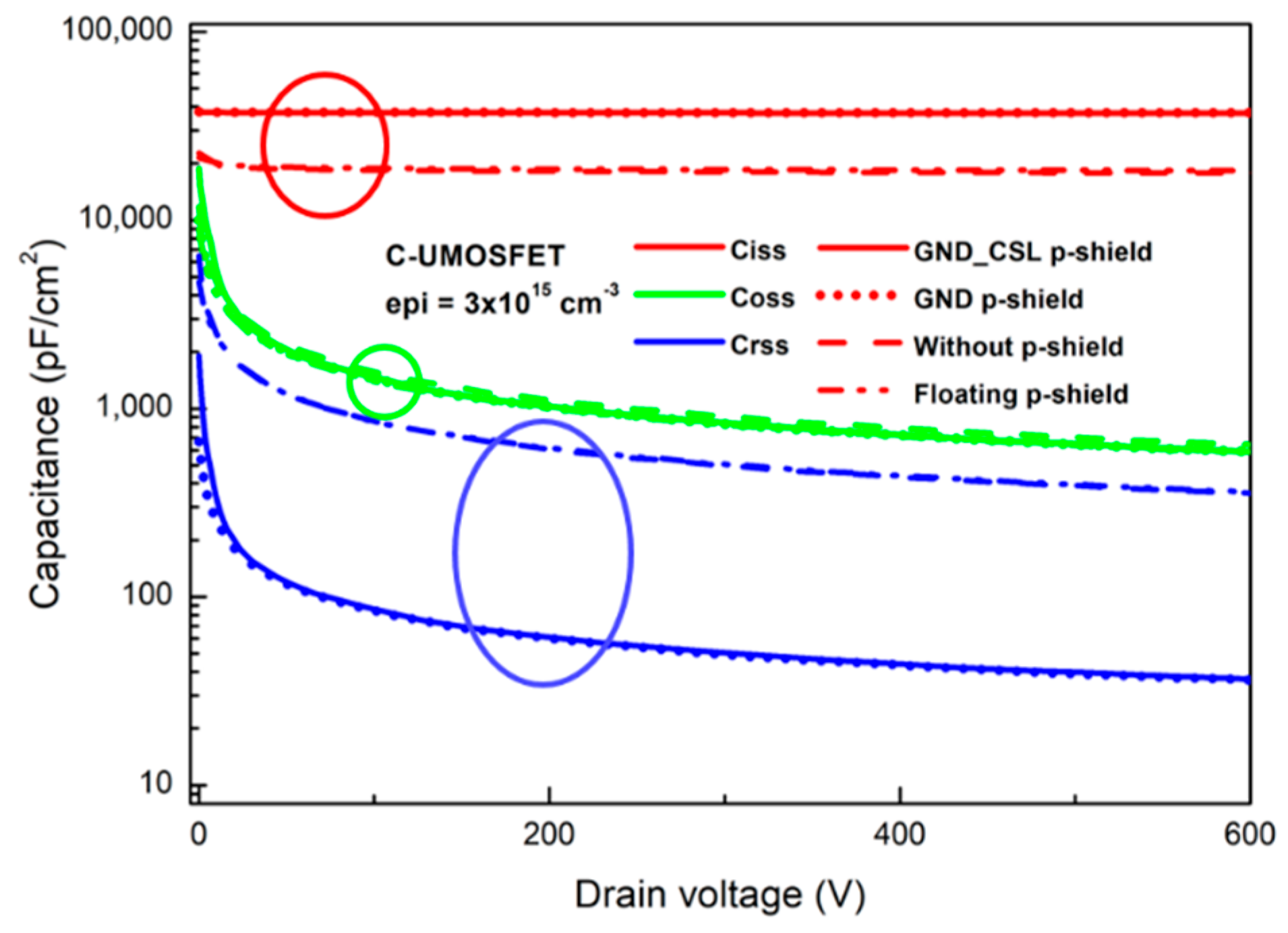

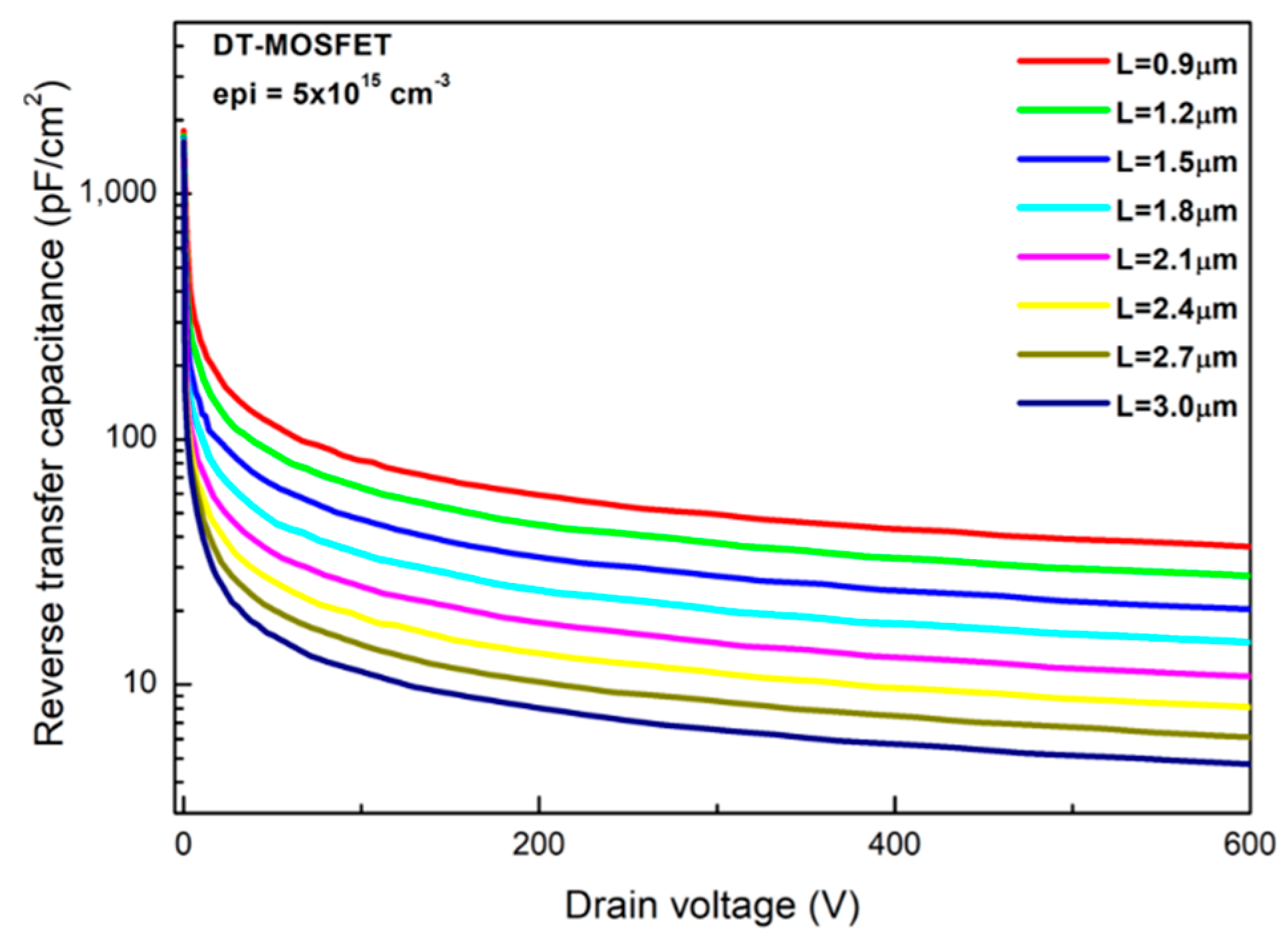

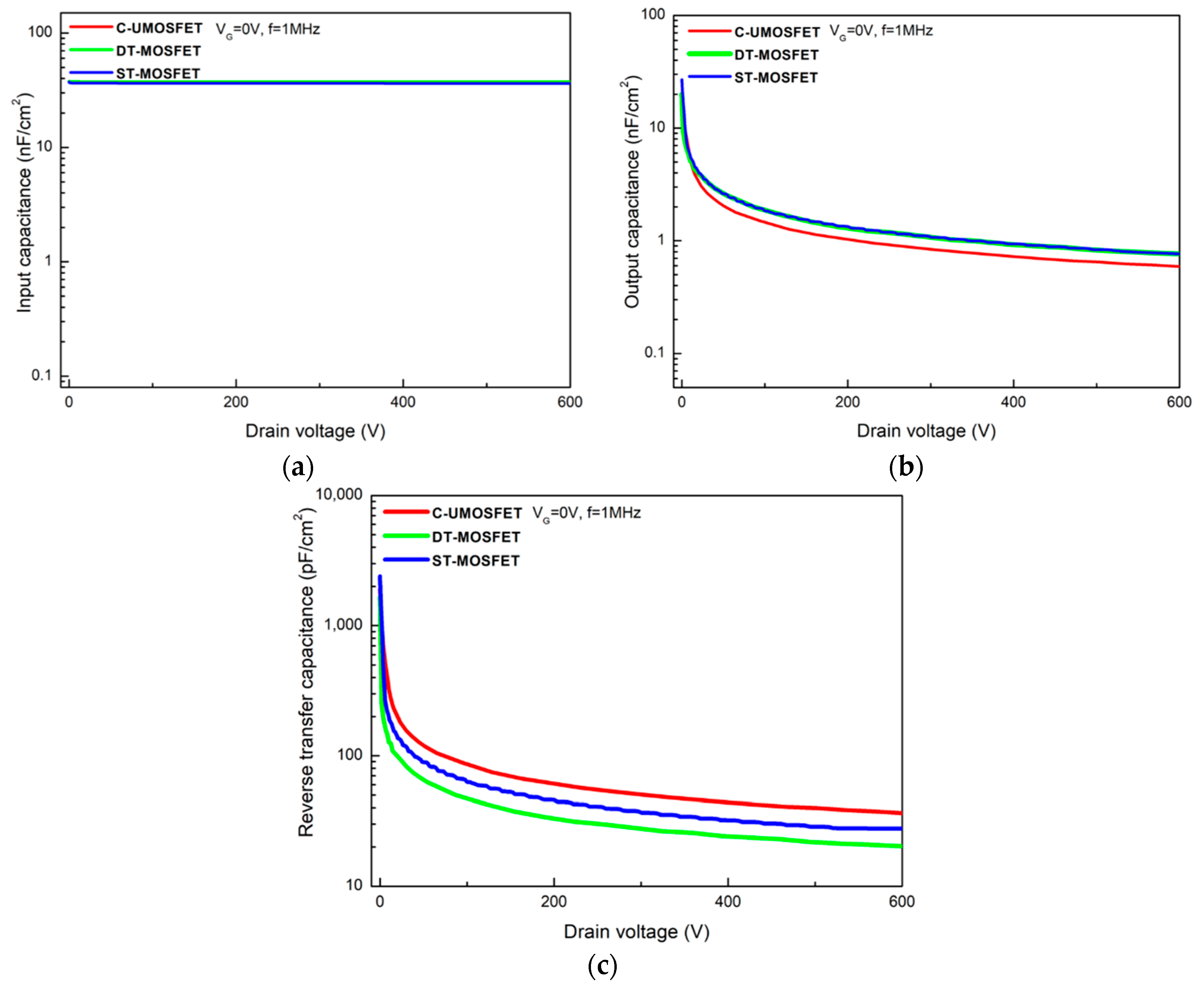

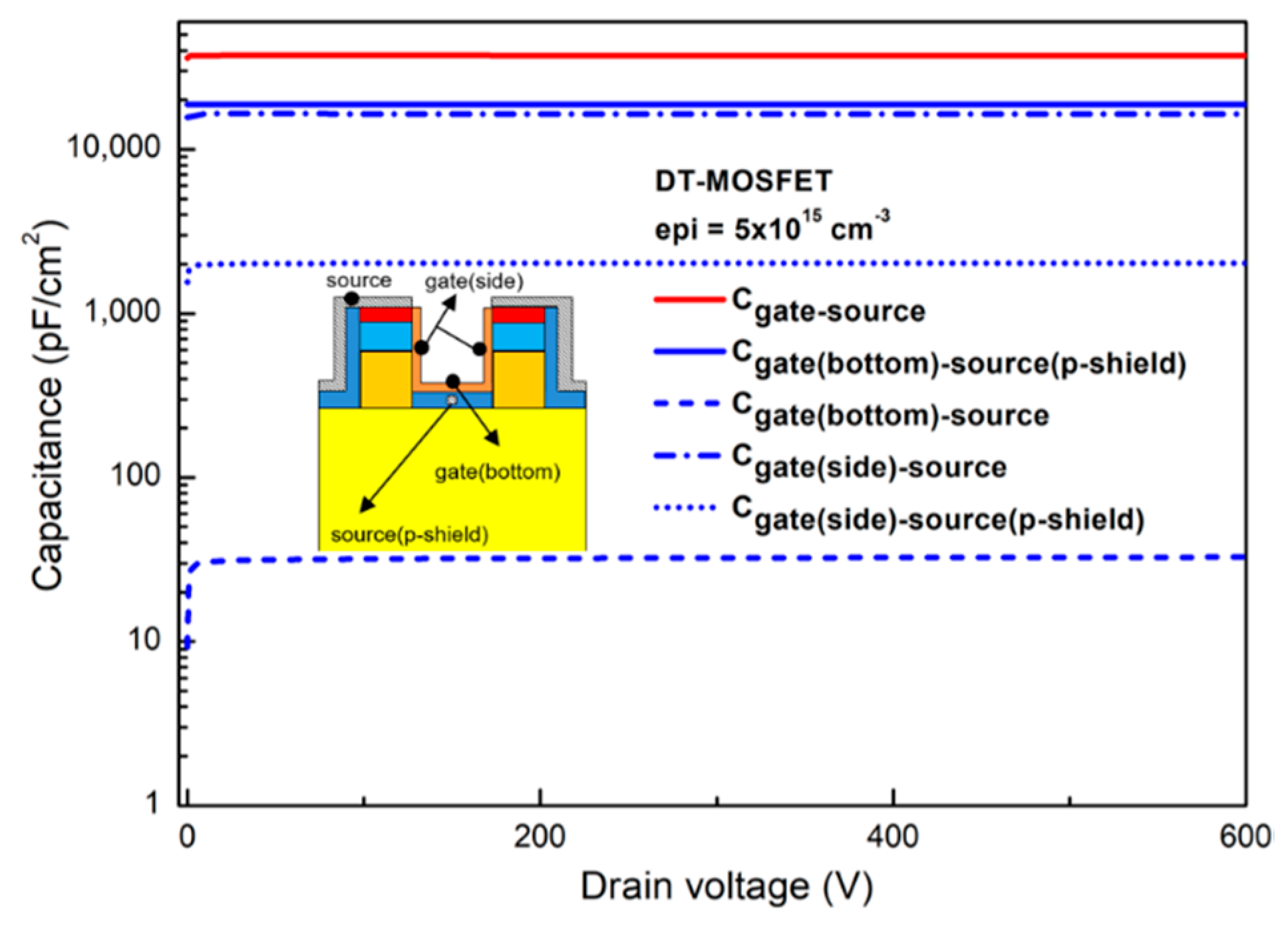

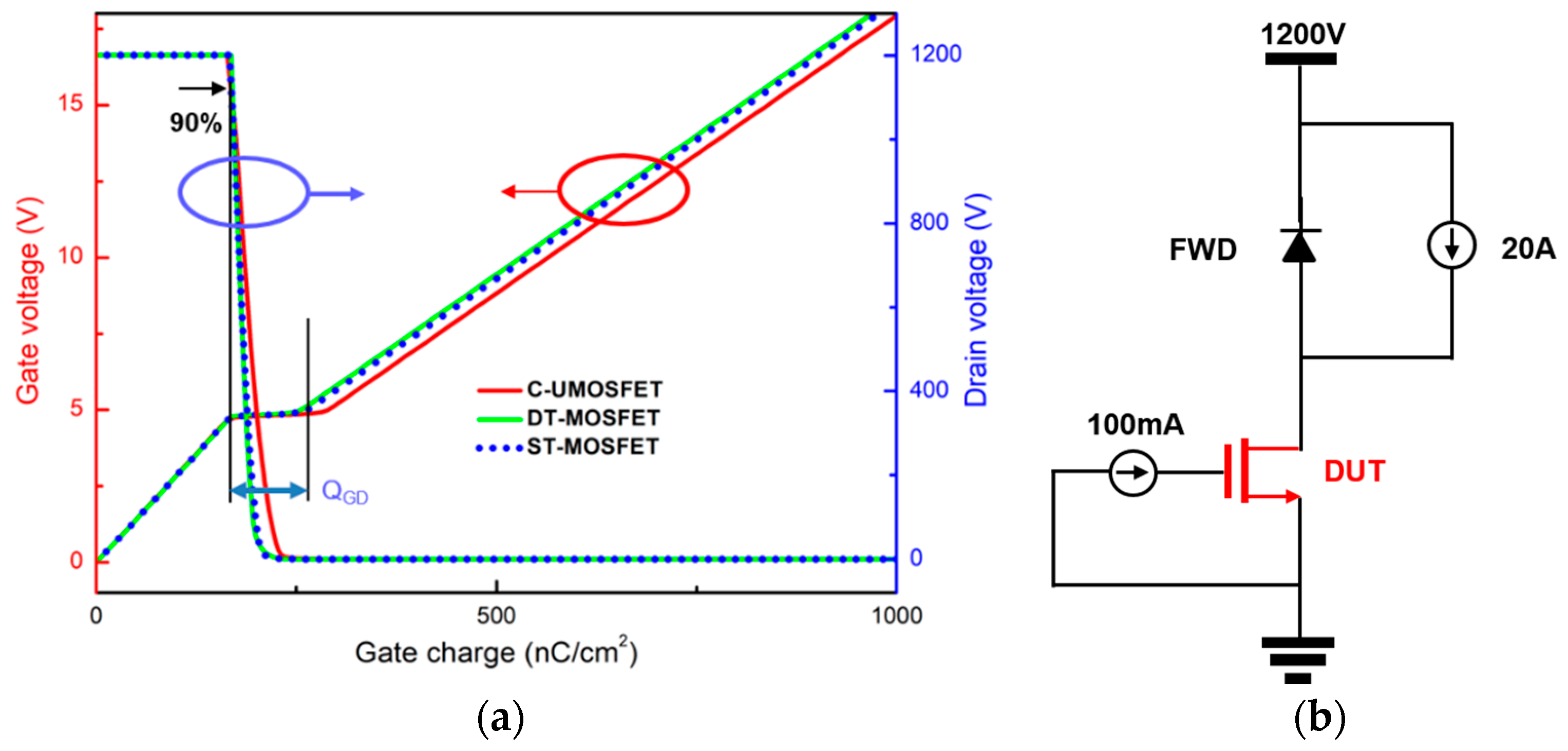

3.2. Terminal Capacitance Characteristics

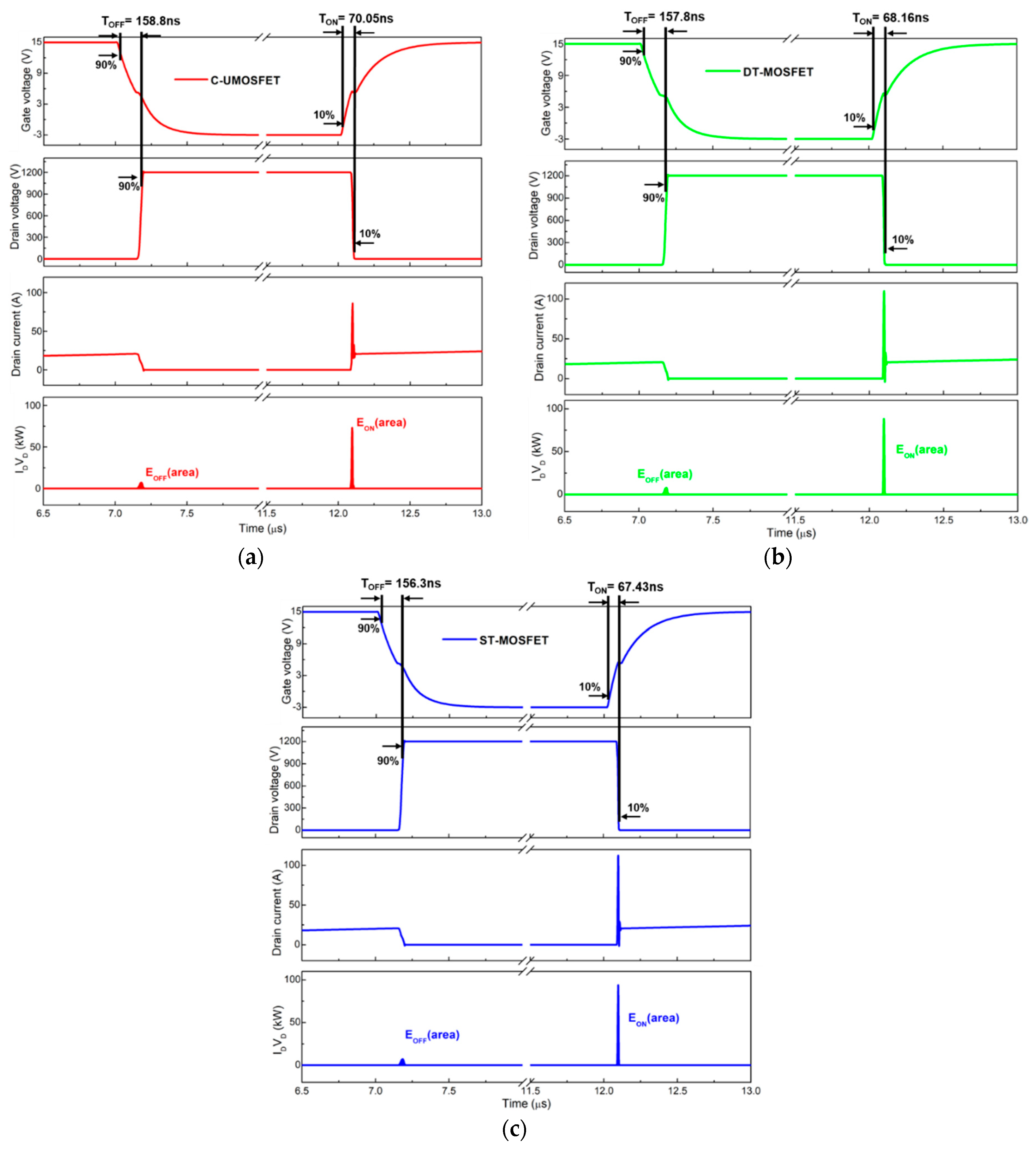

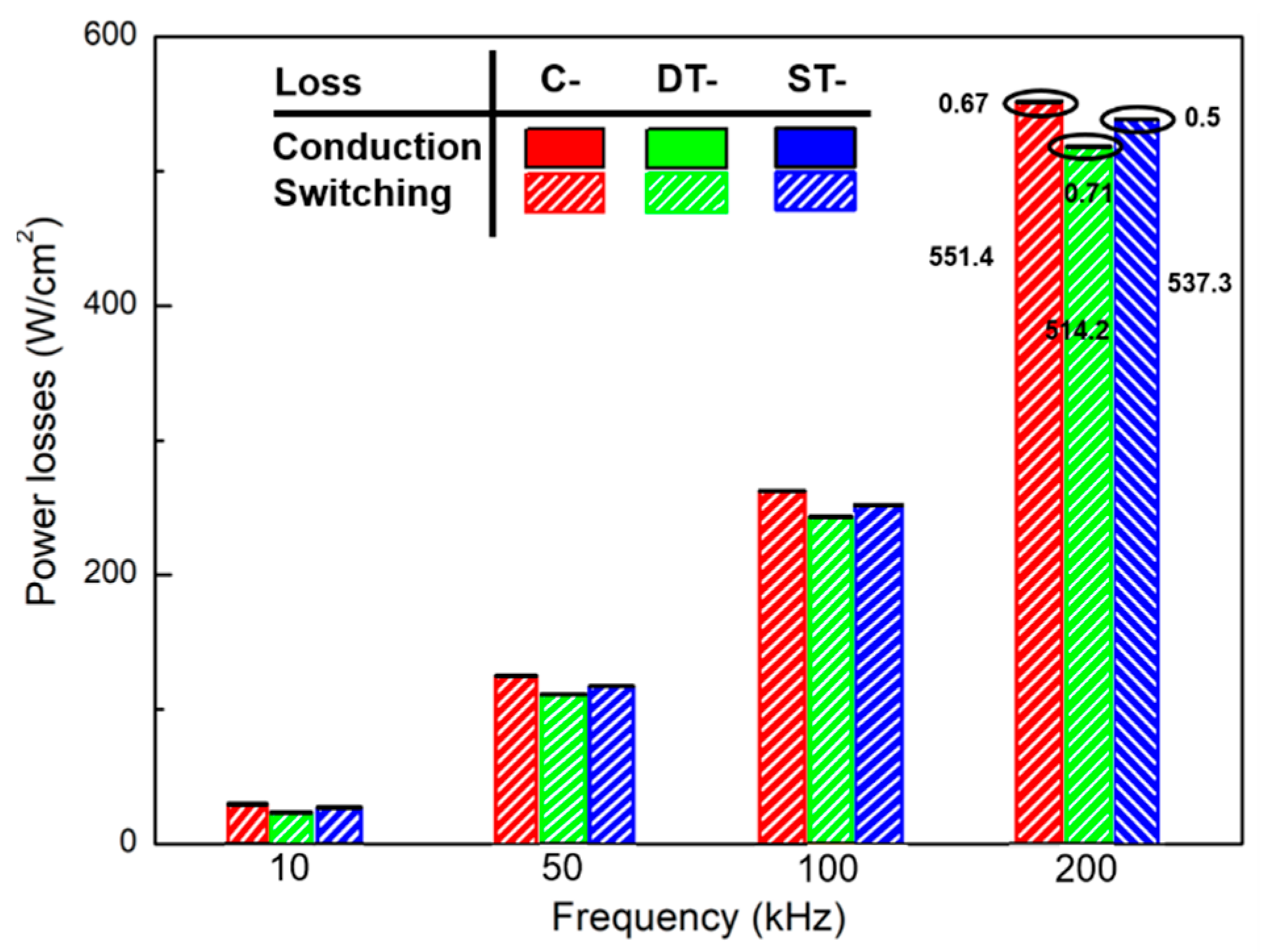

3.3. Dynamic Charateristics

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Zhang, M.; Wei, J.; Jiang, H.; Chen, K.J.; Cheng, C.H. A new SiC trench MOSFET structure with protruded p-base for low oxide field and enhanced switching performance. IEEE Trans. Device Mater. Rel. 2017, 17, 432–437. [Google Scholar] [CrossRef]

- Cooper, J.A.; Agarwal, A. SiC power-switching devices—The second electronics revolution? Proc. IEEE 2002, 90, 956–968. [Google Scholar] [CrossRef]

- Ebihara, Y.; Ichimura, A.; Mitani, A.; Noborio, M.; Takeuchi, Y.; Mizuno, S.; Yamamoto, T.; Tsuruta, K. Deep-P Encapsulated 4HSiC Trench MOSFETs With Ultra Low RonQgd. In Proceedings of the IEEE 30th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Chicago, IL, USA, 13–17 May 2018; pp. 44–48. [Google Scholar]

- Cooper, J.; Melloch, M.; Singh, R.; Agarwal, A.; Palmour, J. Status and prospects for SiC power MOSFETs. IEEE Trans. Electron Devices 2002, 49, 658–664. [Google Scholar] [CrossRef]

- Yano, H.; Nakao, H.; Hatayama, T.; Uraoka, Y.; Fuyuki, T. Increased Channel Mobility in 4H-SiC UMOSFETs Using On-Axis Substrates. Mater. Sci. Forum 2007, 556–557, 807–810. [Google Scholar] [CrossRef]

- Banzhaf, C.T.; Grieb, M.; Trautmann, A.; Bauer, A.J.; Frey, L. Characterization of Diverse Gate Oxides on 4H-SiC 3D Trench-MOS Structures. Mater. Sci. Forum 2013, 740, 691–694. [Google Scholar] [CrossRef]

- Kojima, T.; Harada, S.; Kobayashi, Y.; Sometani, M.; Ariyoshi, K.; Senzaki, J.; Takei, M.; Tanaka, Y.; Okumura, H. Self-aligned formation of the trench bottom shielding region in 4H-SiC trench gate MOSFET. Jpn. J. Appl. Phys. 2016, 55, 04ER02. [Google Scholar] [CrossRef]

- Vudumula, P.; Kotamraju, S. Design and Optimization of 1.2-kV SiC Planar Inversion MOSFET Using Split Dummy Gate Concept for High-Frequency Applications. IEEE Trans. Electron Devices 2019, 66, 5266–5271. [Google Scholar] [CrossRef]

- Agarwal, A.K.; Siergiej, R.R.; Seshadri, S.; White, M.H.; McMullin, P.G.; Burk, A.A.; Rowland, L.B.; Brandt, C.D.; Hopkins, R.H. A critical look at the performance advantages and limitations of 4H-SiC power UMOSFET structures. In Proceedings of the 8th International Symposium on Power Semiconductor Devices and ICs, Maui, HI, USA, 23 May 1996; pp. 119–122. [Google Scholar]

- Singh, R.; Hefner, A.R. Reliability of SiC MOS devices. Solid State Electron. 2004, 48, 1717–1720. [Google Scholar] [CrossRef]

- Siemieniec, R.; Peters, D.; Esteve, R.; Bergner, W.; Basler, T.; Zippelius, B.; Kuck, D.; Aichinger, T. A SiC Trench MOSFET concept offering improved channel mobility and high reliability. In Proceedings of the 19th European Conference on Power Electronics and Applications (EPE’17 ECCE Europe), Warsaw, Poland, 11–14 September 2017; pp. P.1–P.13. [Google Scholar]

- Kagawa, Y.; Fujiwara, N.; Sugawara, K.; Tanaka, R.; Fukui, Y.; Yamamoto, Y.; Miura, N.; Imaizumi, M.; Nakata, S.; Yamakawa, S. 4H-SiC Trench MOSFET with Bottom Oxide Protection. Mater. Sci. Forum 2014, 778–780, 919–922. [Google Scholar] [CrossRef]

- Kobayashi, Y.; Kinoshita, A.; Onishi, Y. Simulation Based Prediction of SiC Trench MOSFET Characteristics. FUJI Elect. Rev. 2016, 62, 12–16. [Google Scholar]

- Baliga, B.J. Silicon Carbide Power Devices; World Scientific: Singapore, 2006; pp. 339–358. [Google Scholar]

- Li, Y.; Cooper, J.; Capano, M. High-voltage (3 kV) UMOSFETs in 4H-SiC. IEEE Trans. Electron Devices 2002, 49, 972–975. [Google Scholar] [CrossRef]

- Yang, T.; Bai, S.; Huang, R. 4H-SiC trench MOSFET with splitting double-stacked shielded region. Superlattices Microstruct. 2018, 122, 419–425. [Google Scholar] [CrossRef]

- Wei, J.; Zhang, M.; Jiang, H.; Cheng, C.-H.; Chen, K.J. Low ON-Resistance SiC Trench/Planar MOSFET With Reduced OFF-State Oxide Field and Low Gate Charges. IEEE Electron Device Lett. 2016, 37, 1458–1461. [Google Scholar] [CrossRef]

- Jiang, H.; Wei, J.; Dai, X.; Ke, M.; Deviny, I.; Mawby, P. SiC Trench MOSFET With Shielded Fin-Shaped Gate to Reduce Oxide Field and Switching Loss. IEEE Electron Device Lett. 2016, 37, 1324–1327. [Google Scholar] [CrossRef]

- Zhou, X.; Yue, R.; Zhang, J.; Dai, G.; Li, J.; Wang, Y. 4H-SiC trench MOSFET with floating/grounded junction barrier-controlled gate structure. IEEE Trans. Electron Devices 2017, 64, 4568–4574. [Google Scholar] [CrossRef]

- Peters, D.; Basler, T.; Zippelius, B.; Aichinger, T.; Bergner, W.; Esteve, R.; Kueck, D.; Siemieniec, R. The new CoolSiC™ Trench MOSFET Technology for Low Gate Oxide Stress and High Performance. In Proceedings of the International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremberg, Germany, 16–18 May 2017; pp. 168–174. [Google Scholar]

- Peters, D.; Siemieniec, R.; Aichinger, T.; Basler, T.; Esteve, R.; Bergner, W.; Kueck, D. Performance and ruggedness of 1200V SiC Trench MOSFET. In Proceedings of the 29th International Symposium on Power Semiconductor Devices and IC’s (ISPSD), Sapporo, Japan, 28 May–1 June 2017; pp. 239–242. [Google Scholar]

- Nakamura, T.; Nakano, Y.; Aketa, M.; Mitani, S.; Sakairi, H.; Yokotsuji, Y. High performance SiC trench devices with ultra-low Ron. In Proceedings of the International Electron Devices Meeting, Washington, DC, USA, 5–7 December 2011; pp. 26.5.1–26.5.3. [Google Scholar]

- Sampath, M.; Morisette, D.; Cooper, J.A. Comparison of singleand double-trench UMOSFETs in 4H-SiC. In Materials Science Forum; Trans Tech Publications Ltd.: Freienbach, Switzerland, 2018; Volume 924, pp. 752–755. [Google Scholar]

- Wei, J.; Liu, S.; Yang, L.; Tang, L.; Lou, R.; Li, T.; Fang, J.; Li, S.; Zhang, C.; Sun, W. Investigations on the Degradations of Double-Trench SiC Power MOSFETs Under Repetitive Avalanche Stress. IEEE Trans. Electron Devices 2018, 66, 546–552. [Google Scholar] [CrossRef]

- Kyogoku, S.; Tanaka, K.; Ariyoshi, K.; Iijima, R.; Kobayashi, Y.; Harada, S. Role of Trench Bottom Shielding Region on Switching Characteristics of 4H-SiC Double-Trench Mosfets. Mater. Sci. Forum 2018, 924, 748–751. [Google Scholar] [CrossRef]

- Kim, T.; Kim, K. High Breakdown Voltage and Low On-Resistance 4H-SiC UMOSFET with Source-Trench Optimization. ECS J. Solid State Sci. Technol. 2019, 8, Q147–Q152. [Google Scholar] [CrossRef]

- Kobayashi, Y.; Harada, S.; Ishimori, H.; Takasu, S.; Kojima, T.; Ariyoshi, K.; Sometani, M.; Senzaki, J.; Takei, M.; Tanaka, Y.; et al. 3.3 kV-Class 4H-SiC UMOSFET by Double-Trench with Tilt Angle Ion Implantation. Mater. Sci. Forum 2016, 858, 974–977. [Google Scholar] [CrossRef]

- Jiang, J.-Y.; Wu, T.-L.; Zhao, F.; Huang, C.-F. Numerical Study of 4H-SiC UMOSFETs with Split-Gate and P+ Shielding. Energies 2020, 13, 1122. [Google Scholar] [CrossRef] [Green Version]

- Saha, A.; Cooper, J.A. A 1-kV 4H-SiC Power DMOSFET Optimized for Low on-Resistance. IEEE Trans. Electron Devices 2007, 54, 2786–2791. [Google Scholar] [CrossRef]

- Synopsys Inc. Sentaurus Device, User Manual, Version O-2018.06; Synopsys Inc.: Mountain View, CA, USA, 2018. [Google Scholar]

- Lombardi, C.; Manzini, S.; Saporito, A.; Vanzi, M. A physically based mobility model for numerical simulation of nonplanar devices. IEEE Trans. Comput. Des. Integr. Circuits Syst. 1988, 7, 1164–1171. [Google Scholar] [CrossRef]

- Hatakeyama, T.; Nishio, J.; Ota, C.; Shinohe, T. Physical modeling and scaling properties of 4H-SiC power devices. In Proceedings of the International Conference On Simulation of Semiconductor Processes and Devices, Tokyo, Japan, 1–3 September 2005; pp. 171–174. [Google Scholar]

- Zhao, Y.; Niwa, H.; Kimoto, T. Impact ionization coefficients of 4H-SiC in a wide temperature range. Jpn. J. Appl. Phys. 2018, 58, 018001. [Google Scholar] [CrossRef]

- Kang, H.; Udrea, F. On the Quasi-Saturation in State-of-the-Art Power MOSFETs. IEEE Electron Device Lett. 2019, 40, 754–756. [Google Scholar] [CrossRef]

- Goh, J.; Kim, K. Low on-resistance 4H-SiC UMOSFET with local floating superjunction. J. Comput. Electron. 2019, 19, 234–241. [Google Scholar] [CrossRef]

- Dimarino, C.; Chen, Z.; Danilovic, M.; Boroyevich, D.; Burgos, R.; Mattavelli, P. High-temperature characterization and comparison of 1.2 kV SiC power MOSFETs. In Proceedings of the IEEE Energy Conversion Congress and Exposition, Denver, CO, USA, 15–19 September 2013; pp. 3235–3242. [Google Scholar] [CrossRef]

- Baliga, B.J. Fundamentals of Power Semiconductor Devices; Springer: Berlin, Germany, 2008; pp. 279–497. [Google Scholar]

- Wei, J.; Zhang, M.; Jiang, H.; Wang, H.; Chen, K.J. Dynamic Degradation in SiC Trench MOSFET With a Floating p-Shield Revealed with Numerical Simulations. IEEE Trans. Electron Devices 2017, 64, 2592–2598. [Google Scholar] [CrossRef]

- Alatise, O.; Parker-Allotey, N.-A.; Jennings, M.; Mawby, P.; Kennedy, I.; Petkos, G. Modeling the Impact of the Trench Depth on the Gate–Drain Capacitance in Power MOSFETs. IEEE Electron Device Lett. 2011, 32, 1269–1271. [Google Scholar] [CrossRef] [Green Version]

- Luo, X.; Liao, T.; Wei, J.; Fang, J.; Yang, F.; Zhang, B. A novel 4H-SiC trench MOSFET with double shielding structures and ultralow gate-drain charge. J. Semicond. 2019, 40, 052803. [Google Scholar] [CrossRef]

- Han, K.J.; Baliga, B.J.; Sung, W. A Novel 1.2 kV 4H-SiC Buffered-Gate (BG) MOSFET: Analysis and Experimental Results. IEEE Electron Device Lett. 2017, 39, 248–251. [Google Scholar] [CrossRef]

- Zhang, J.; Rees, F.L.; Hull, B.; Casady, J.B.; Allen, S.; Palmour, J.W. Impact of next-generation 1700V SiC MOSFETs in a 125kW PV converter. In Proceedings of the IEEE Energy Conversion Congress and Exposition (ECCE), Cincinnati, OH, USA, 1–5 October 2017; pp. 911–916. [Google Scholar]

- Tian, K.; Hallen, A.; Qi, J.; Ma, S.; Fei, X.; Zhang, A.; Liu, W. An Improved 4H-SiC Trench-Gate MOSFET With Low ON-Resistance and Switching Loss. IEEE Trans. Electron Devices 2019, 66, 2307–2313. [Google Scholar] [CrossRef]

- Graovac, D.; Purschel, M.; Kiep, A. MOSFET power losses calculation using the data-sheet parameters application note, v1.1. Infineon Technol. AG 2006, 1, 1–23. [Google Scholar]

- Backlund, B.; Schnell, R.; Ulrich, S.; Roland, F. Applying IGBTs; Application Note 5SYA2053-01; ABB: Lenzburg, Switzerland, 2007. [Google Scholar]

| Parameter | C- | DT- | ST- |

|---|---|---|---|

| Cell pitch (μm) | 5.55 | 5.55 | 5.55 |

| Gate-trench width (μm) | 1.55 | 1.55 | 1.55 |

| Gate-trench depth (μm) | 1.5 | 1.5 | 1.5 |

| P-base width (μm) | 2 | 2 | 2 |

| P+ shield width (μm) | 1.55 | 1.55 | 1.55 |

| Channel length (μm) | 0.5 | 0.5 | 0.5 |

| Gate oxide thickness (μm) | 0.05 | 0.05 | 0.05 |

| Epi-layer thickness (μm) | 18 | 18 | 18 |

| P+ shield thickness (μm) | 0.3 | 0.3 | 0.3 |

| N-sub thickness (μm) | 1 | 1 | 1 |

| Source-trench width (μm) | - | 0.5 | 0.5 |

| Source-trench depth (μm) | - | 1.5 | 2.4 |

| Source oxide thickness (μm) | - | - | 0.1 |

| Source doping concentration (cm−3) | 1 × 1019 | 1 × 1019 | 1 × 1019 |

| P-base doping concentration (cm−3) | 1 × 1017 | 1 × 1017 | 1 × 1017 |

| P+ shield doping concentration (cm−3) | 5 × 1018 | 5 × 1018 | 5 × 1018 |

| Epi-layer doping concentration (cm−3) | 3 × 1015 | 5 × 1015 | 5 × 1015 |

| N-sub doping concentration (cm−3) | 1 × 1019 | 1 × 1019 | 1 × 1019 |

| DSL doping concentration (cm−3) | 1 × 1016 | 1 × 1016 | 1 × 1016 |

| Parameter | C- | DT- | ST- |

|---|---|---|---|

| Breakdown voltage [V] | 1699 | 1706 | 1724 |

| RON-SP [mΩ∙cm2] | 3.37 | 3.57 | 2.52 |

| EOX-MAX (@VG = 0 V, VD = 1200 V) [MV/cm] | 1.11 | 0.62 | 0.72 |

| VTH [V] | 5.74 | 5.75 | 5.75 |

| DC-FOM (BV2/RON-SP) [MW/cm2] | 857 | 815 | 1179 |

| Parameter | C- | DT- | ST- |

|---|---|---|---|

| CISS (@VD = 600 V, f = 1 MHz) [nF/cm2] | 37 | 37.3 | 36.2 |

| COSS (@VD = 600 V, f = 1 MHz) [pF/cm2] | 590 | 763 | 765 |

| CRSS (@VD = 600 V, f = 1 MHz) [pF/cm2] | 36.5 | 20.3 | 27.7 |

| QG [nC/cm2] | 839 | 805 | 813 |

| QGD [nC/cm2] | 115 | 81 | 89 |

| HF-FOM < RON-SP × QG > [mΩ∙nC] | 2827 | 2874 | 2049 |

| HF-FOM < RON-SP × QGD > [mΩ∙nC] | 388 | 289 | 224 |

| Parameter | C- | DT- | ST- |

|---|---|---|---|

| TD-ON [ns] | 56.87 | 57.68 | 56.70 |

| TR [ns] | 13.18 | 10.48 | 10.73 |

| TON [ns] | 70.05 | 68.16 | 67.43 |

| TD-OFF [ns] | 135.1 | 137.4 | 132.7 |

| TF [ns] | 23.75 | 20.48 | 23.53 |

| TOFF [ns] | 158.8 | 157.8 | 156.3 |

| EON [μJ] | 655.3 | 610.7 | 637.5 |

| EOFF [μJ] | 171.8 | 160.6 | 168.5 |

| ESW [μJ] | 827.1 | 771.2 | 806.0 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Cheon, J.; Kim, K. Numerical Simulation Analysis of Switching Characteristics in the Source-Trench MOSFET’s. Electronics 2020, 9, 1895. https://doi.org/10.3390/electronics9111895

Cheon J, Kim K. Numerical Simulation Analysis of Switching Characteristics in the Source-Trench MOSFET’s. Electronics. 2020; 9(11):1895. https://doi.org/10.3390/electronics9111895

Chicago/Turabian StyleCheon, Jinhee, and Kwangsoo Kim. 2020. "Numerical Simulation Analysis of Switching Characteristics in the Source-Trench MOSFET’s" Electronics 9, no. 11: 1895. https://doi.org/10.3390/electronics9111895

APA StyleCheon, J., & Kim, K. (2020). Numerical Simulation Analysis of Switching Characteristics in the Source-Trench MOSFET’s. Electronics, 9(11), 1895. https://doi.org/10.3390/electronics9111895