Implementation of a Wide Input Voltage Resonant Converter with Voltage Doubler Rectifier Topology

Abstract

1. Introduction

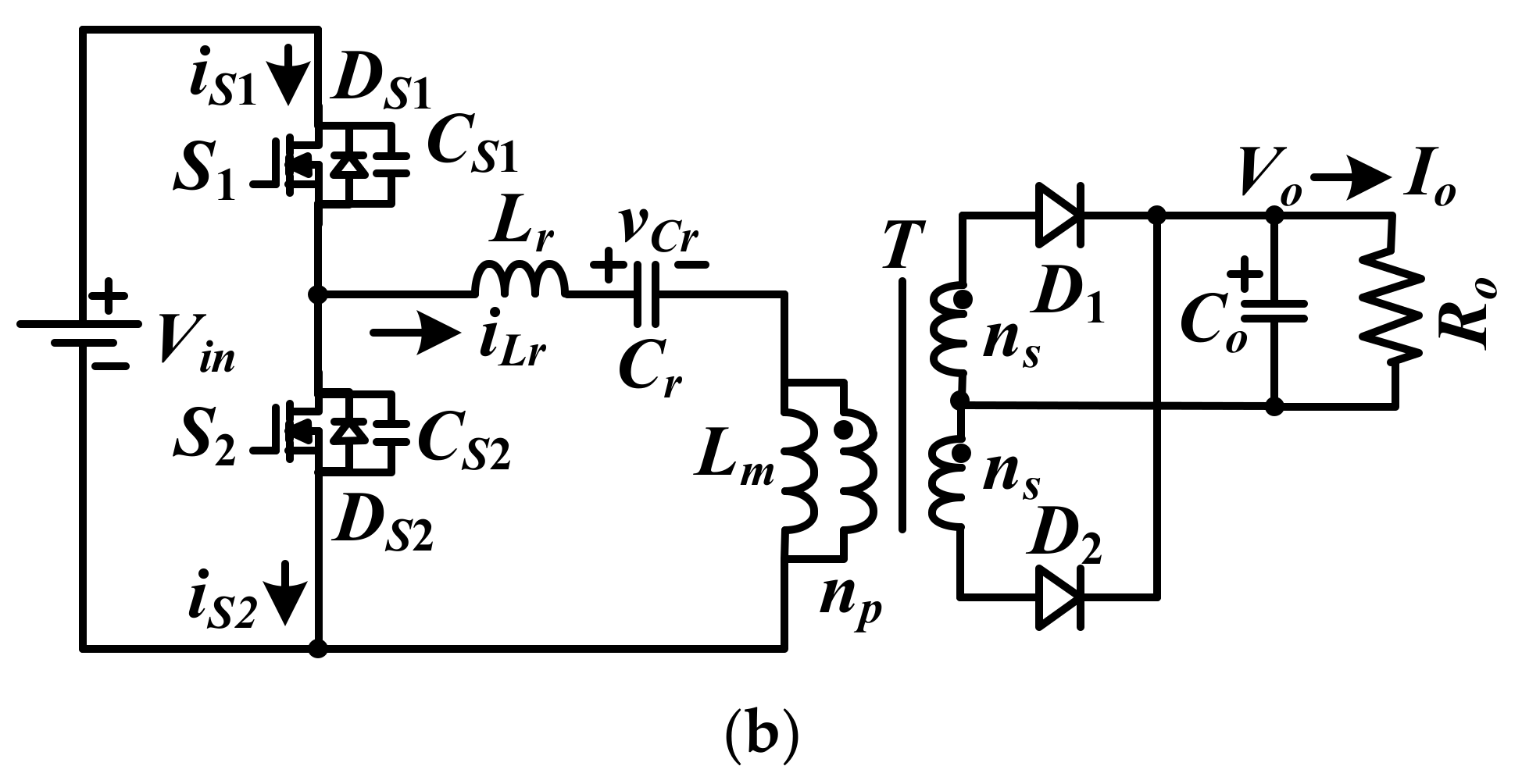

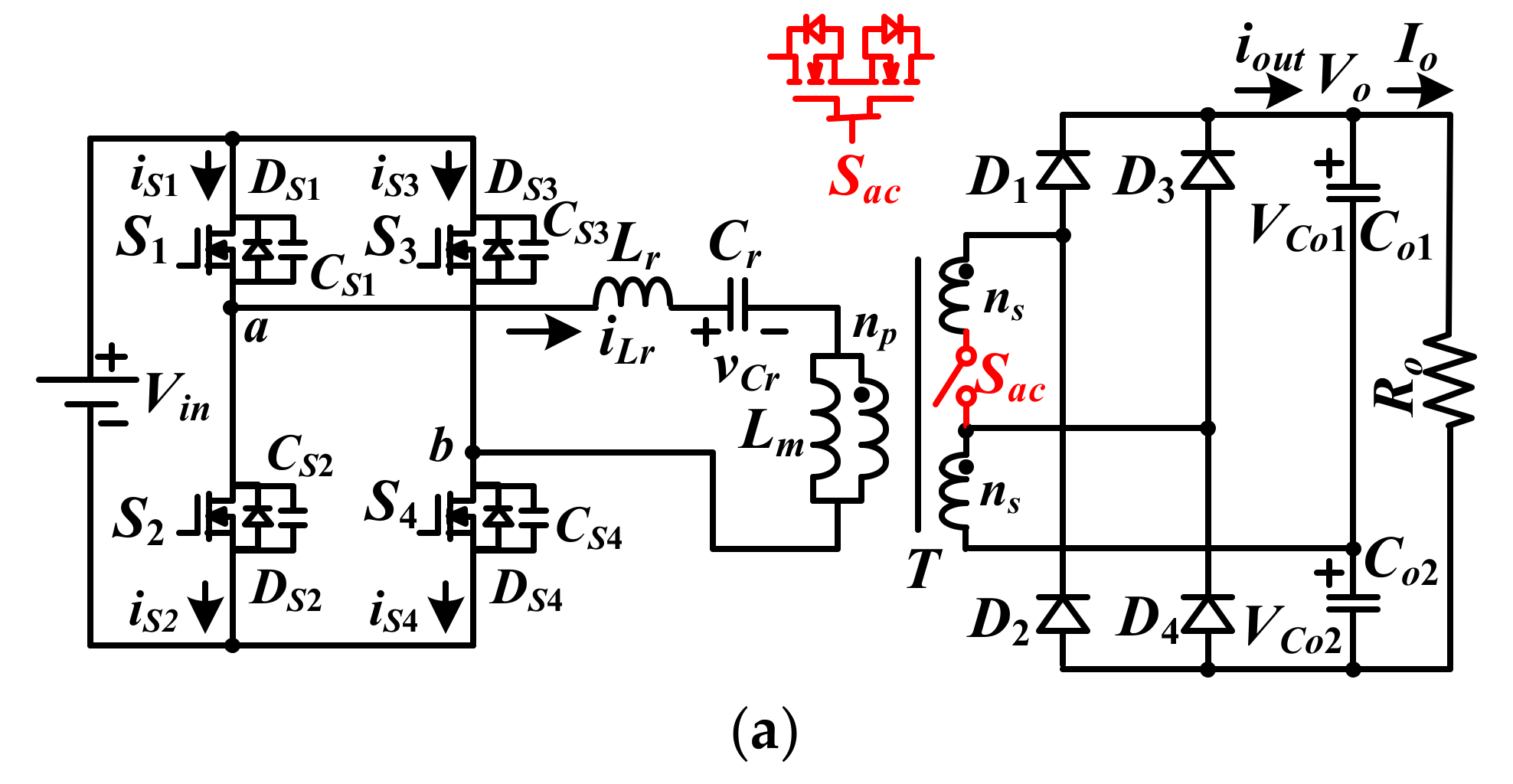

2. Circuit Configuration and Principles of Operation

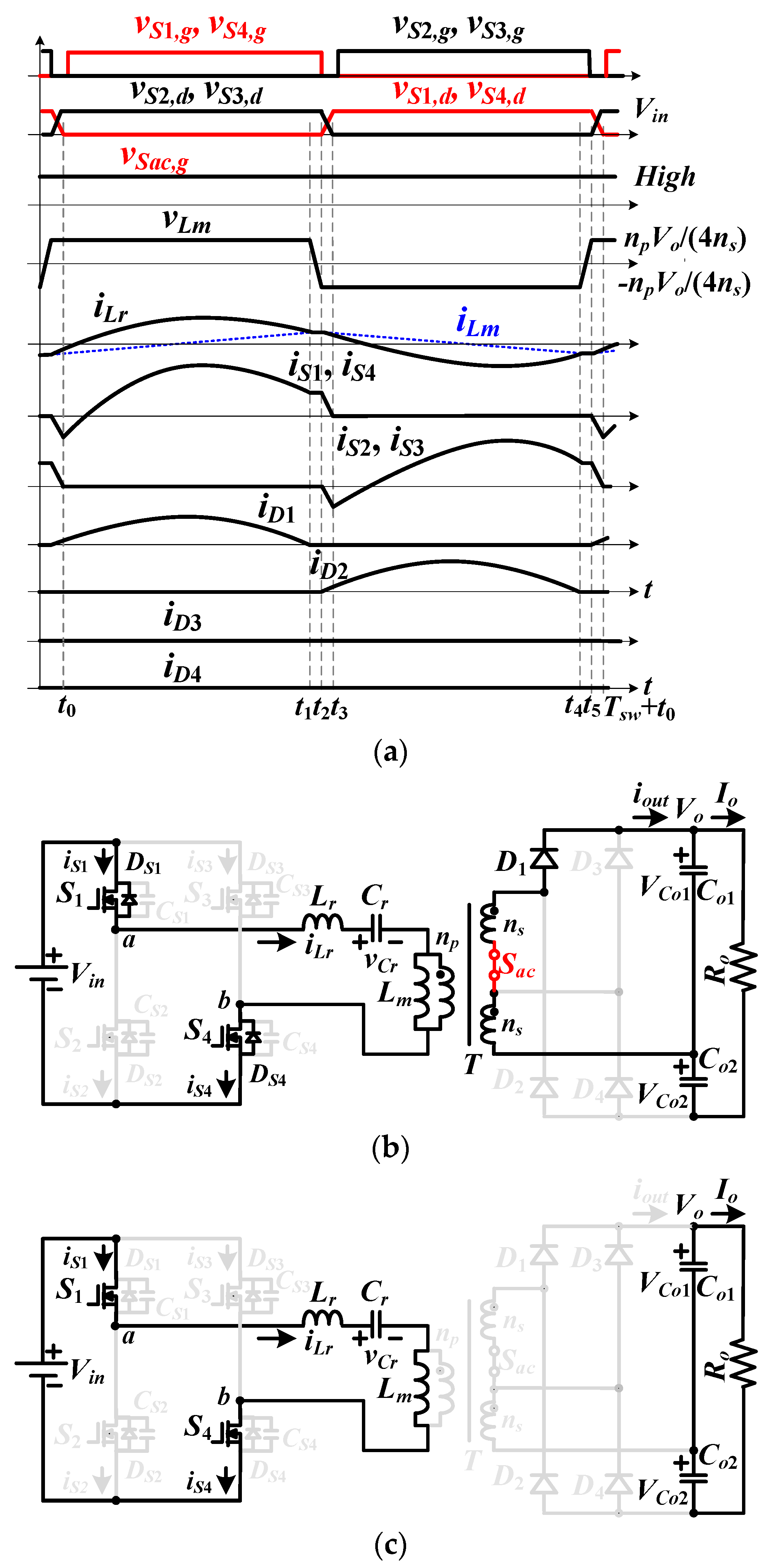

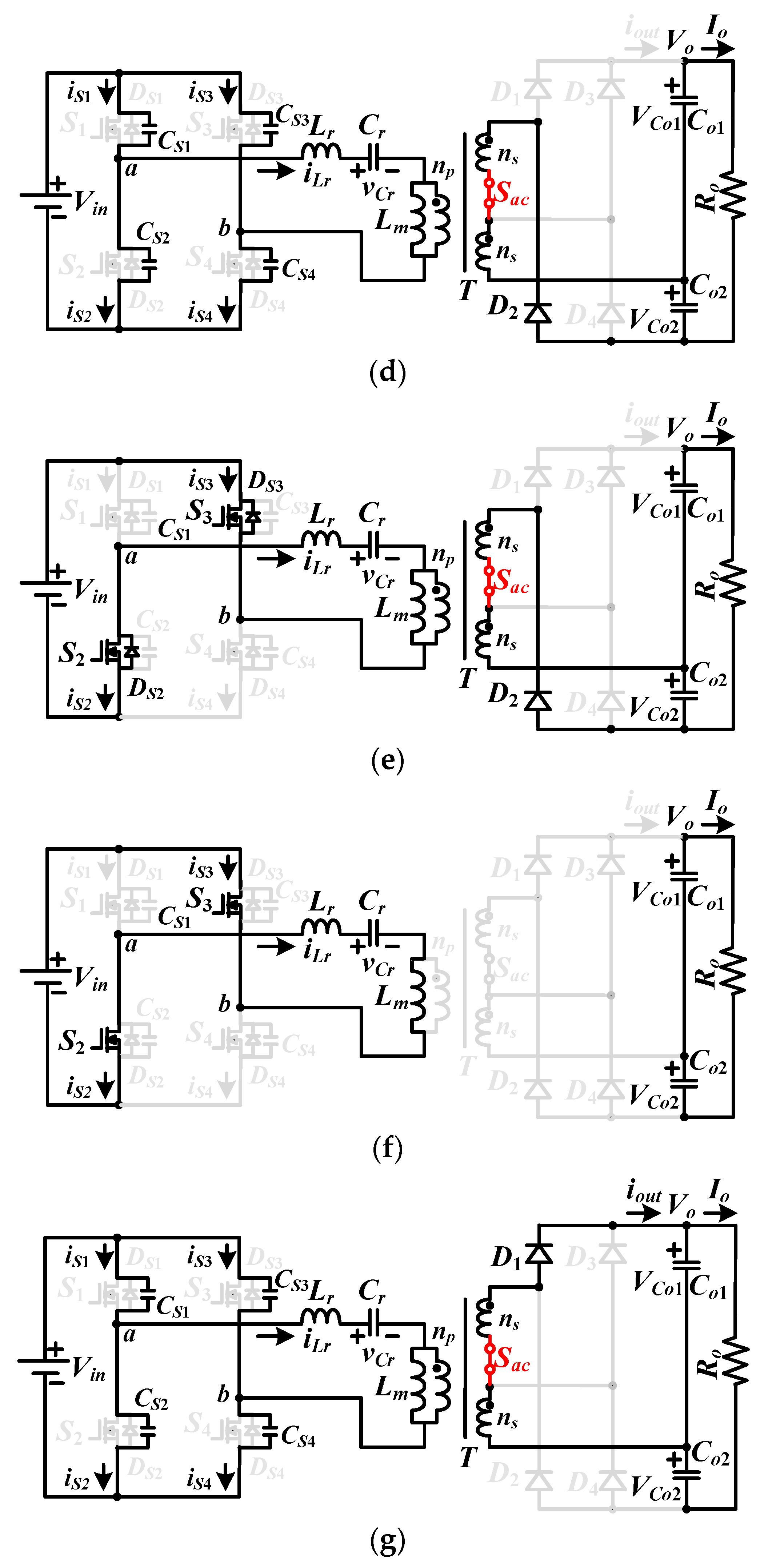

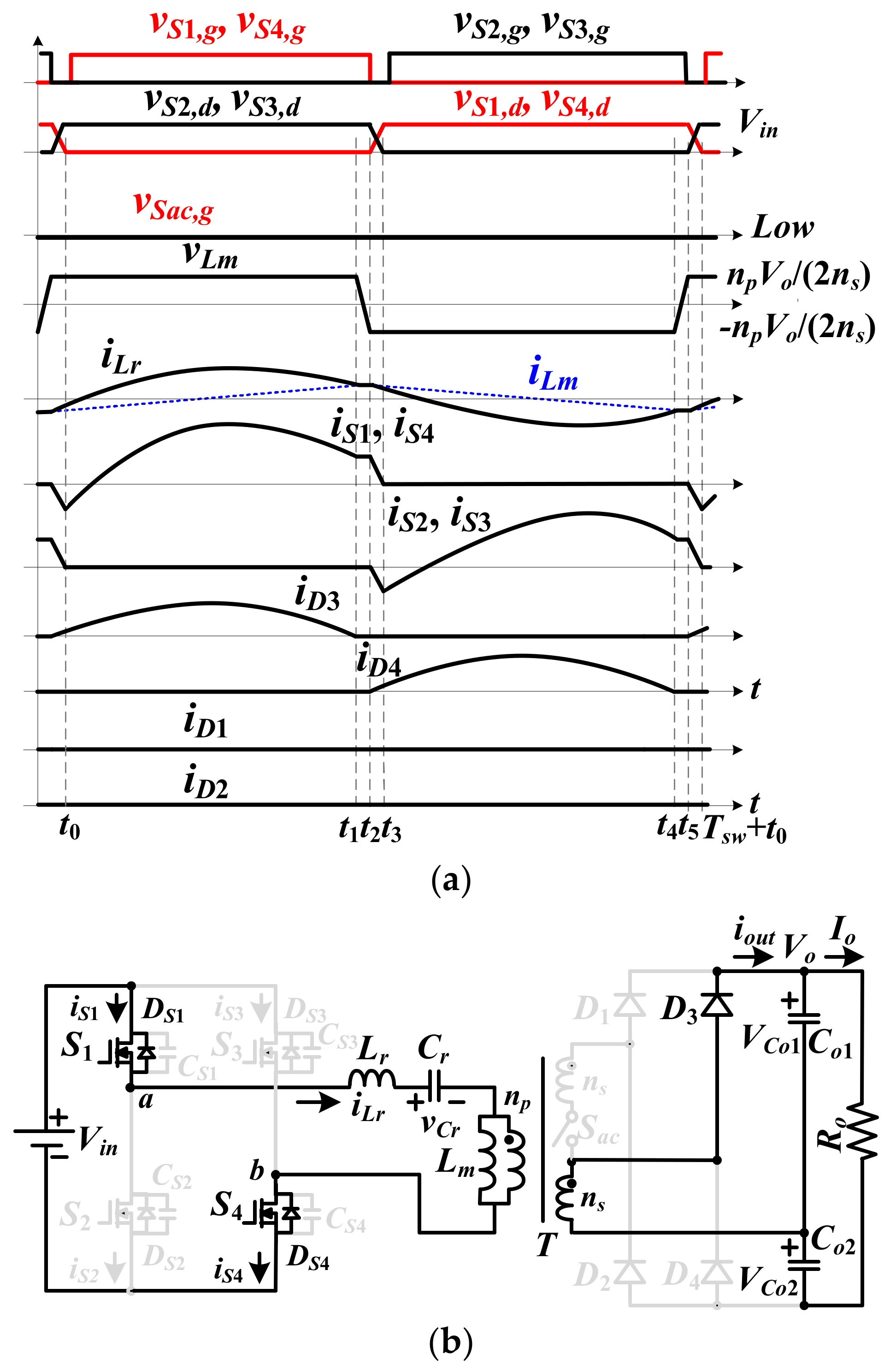

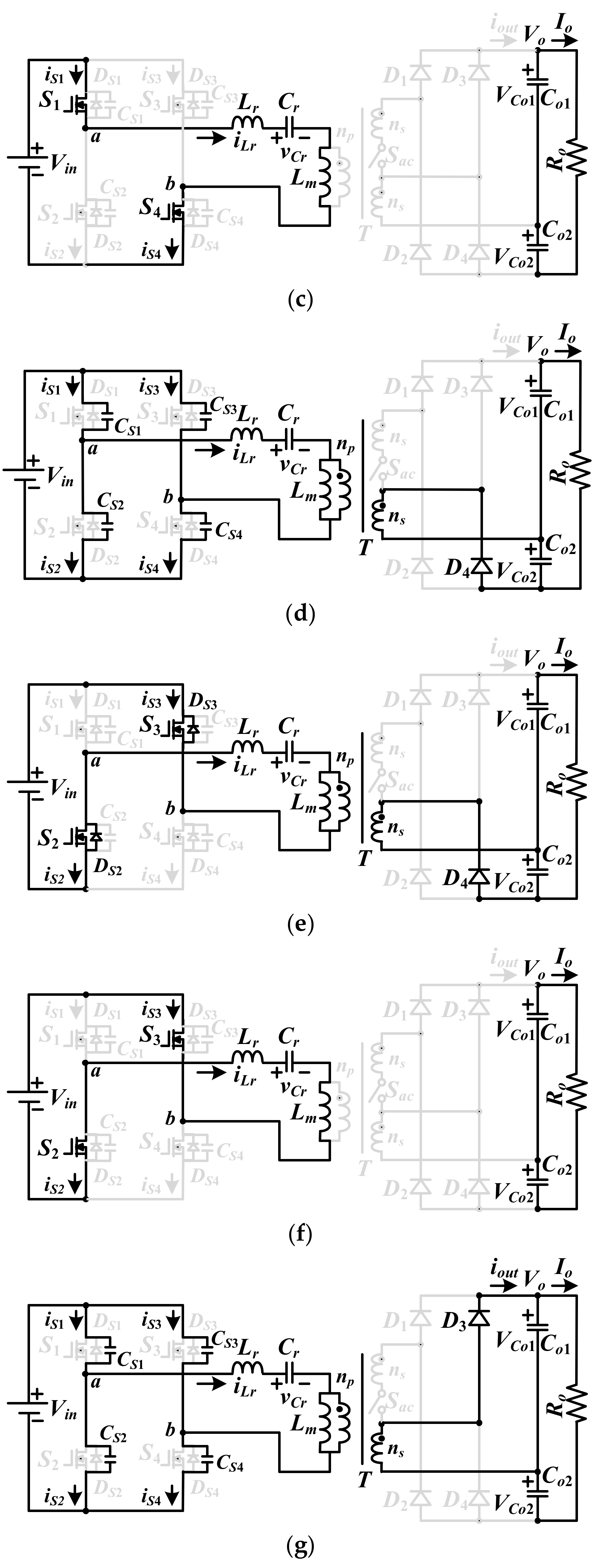

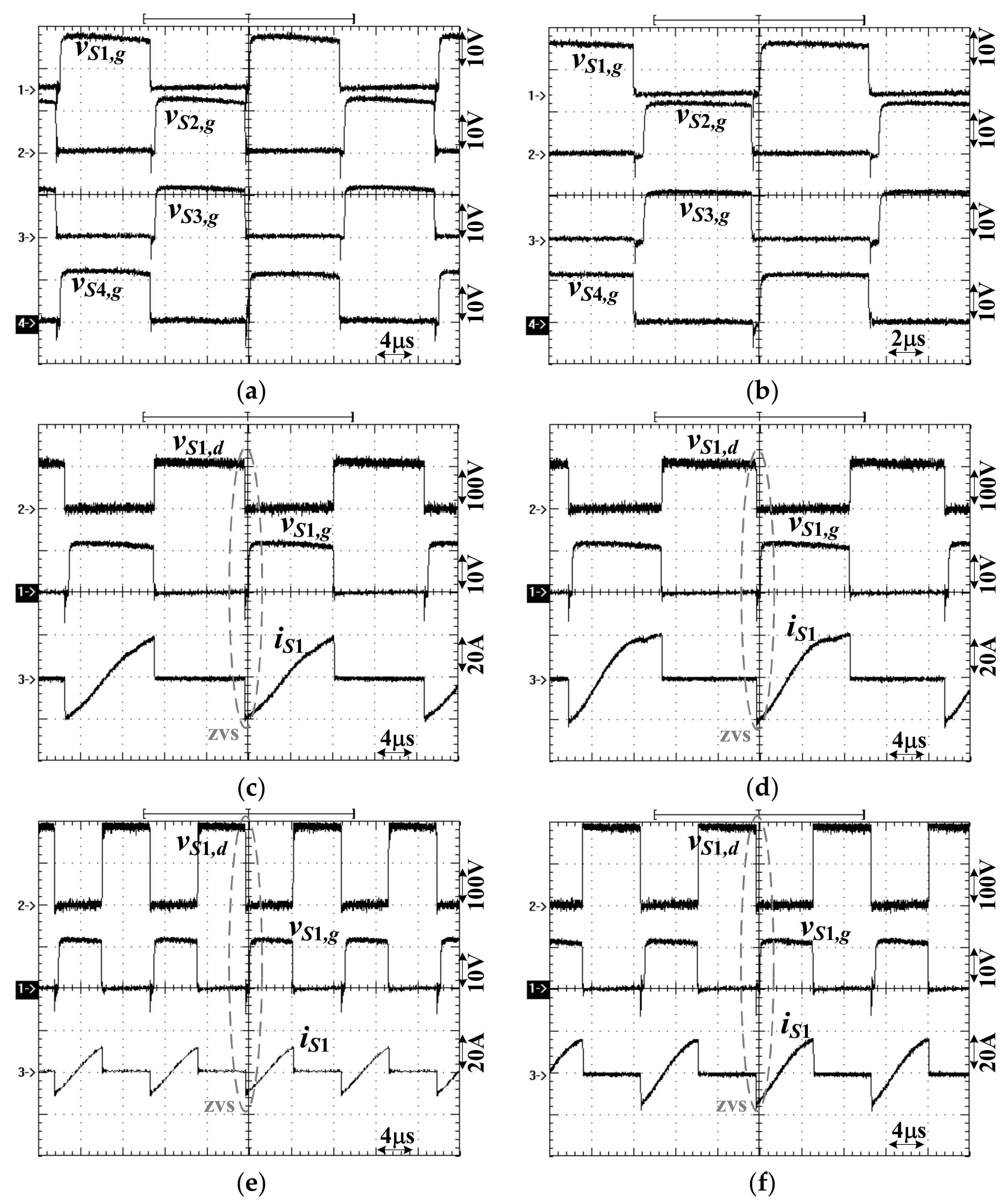

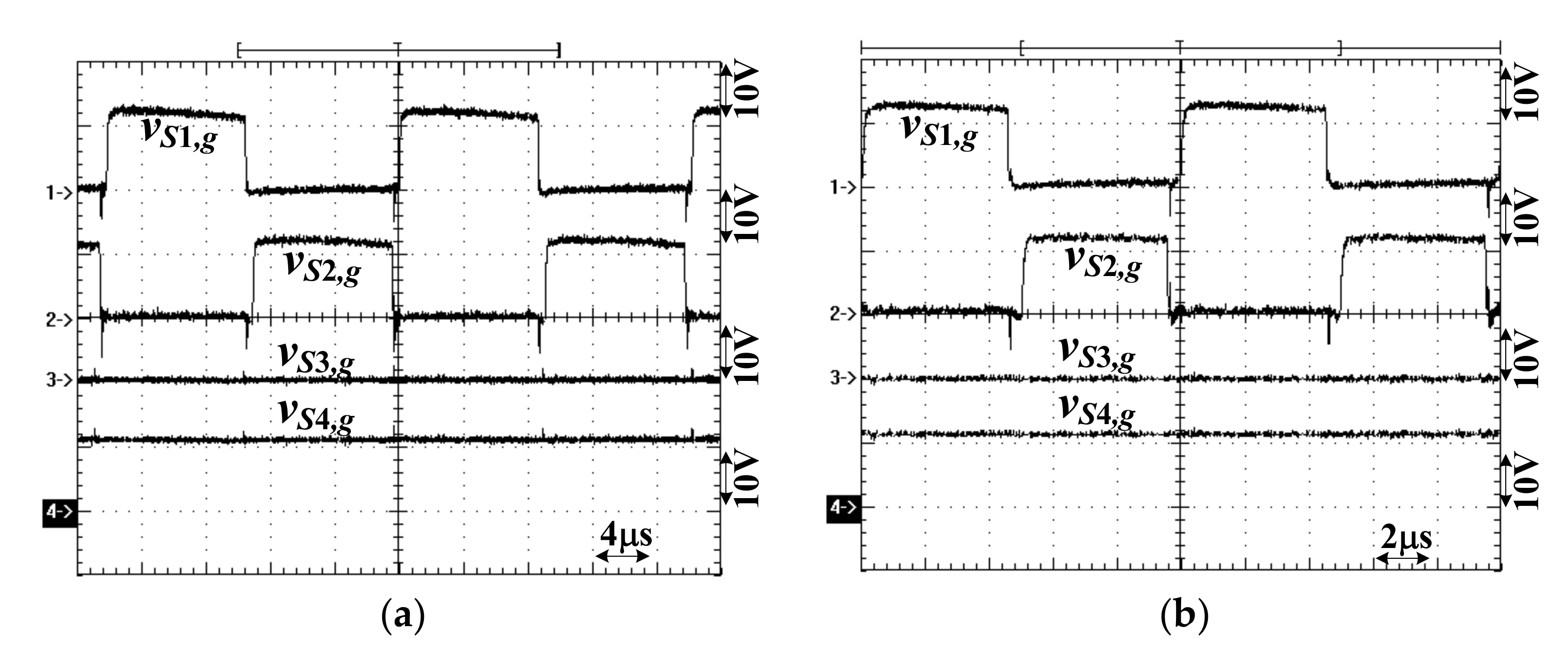

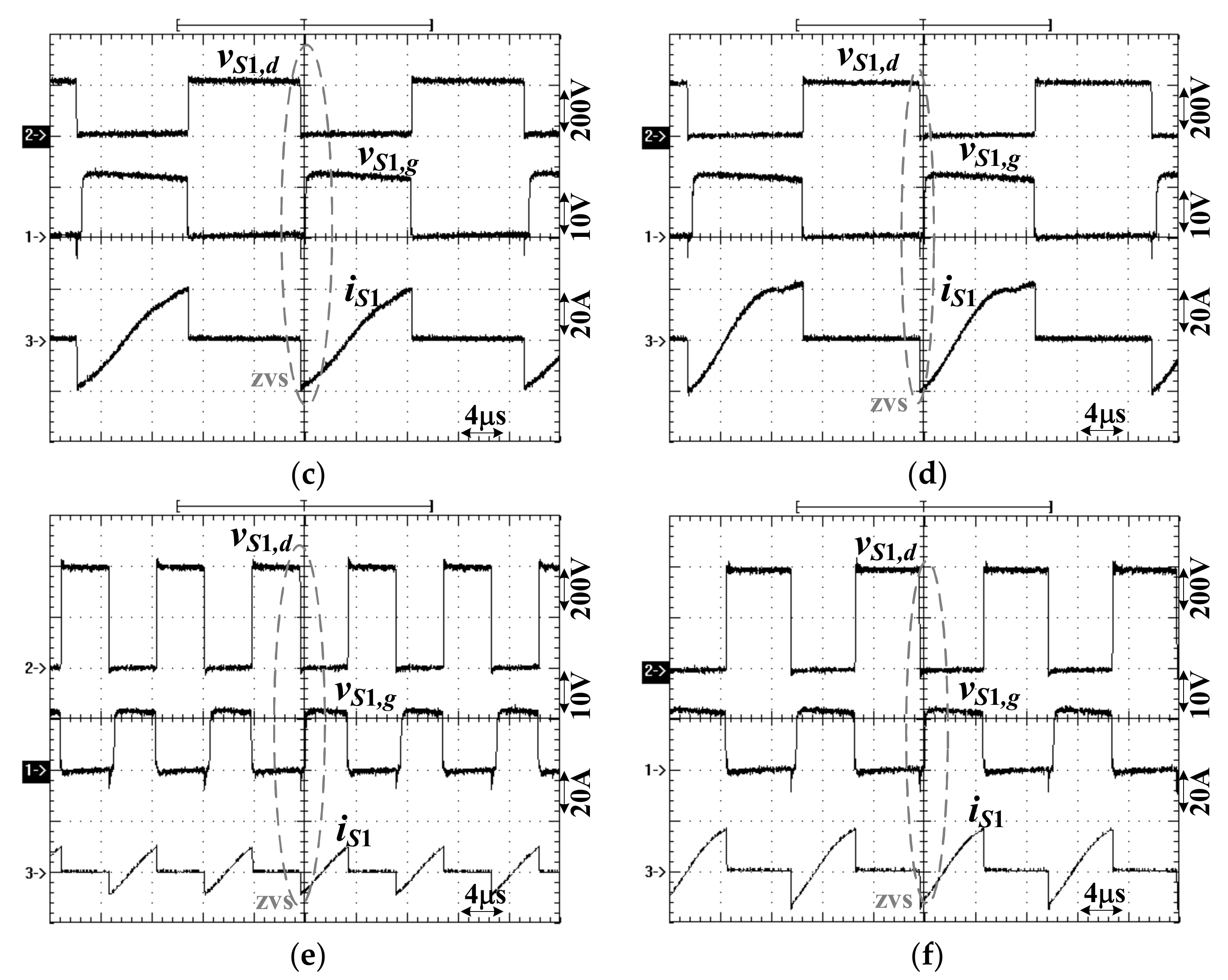

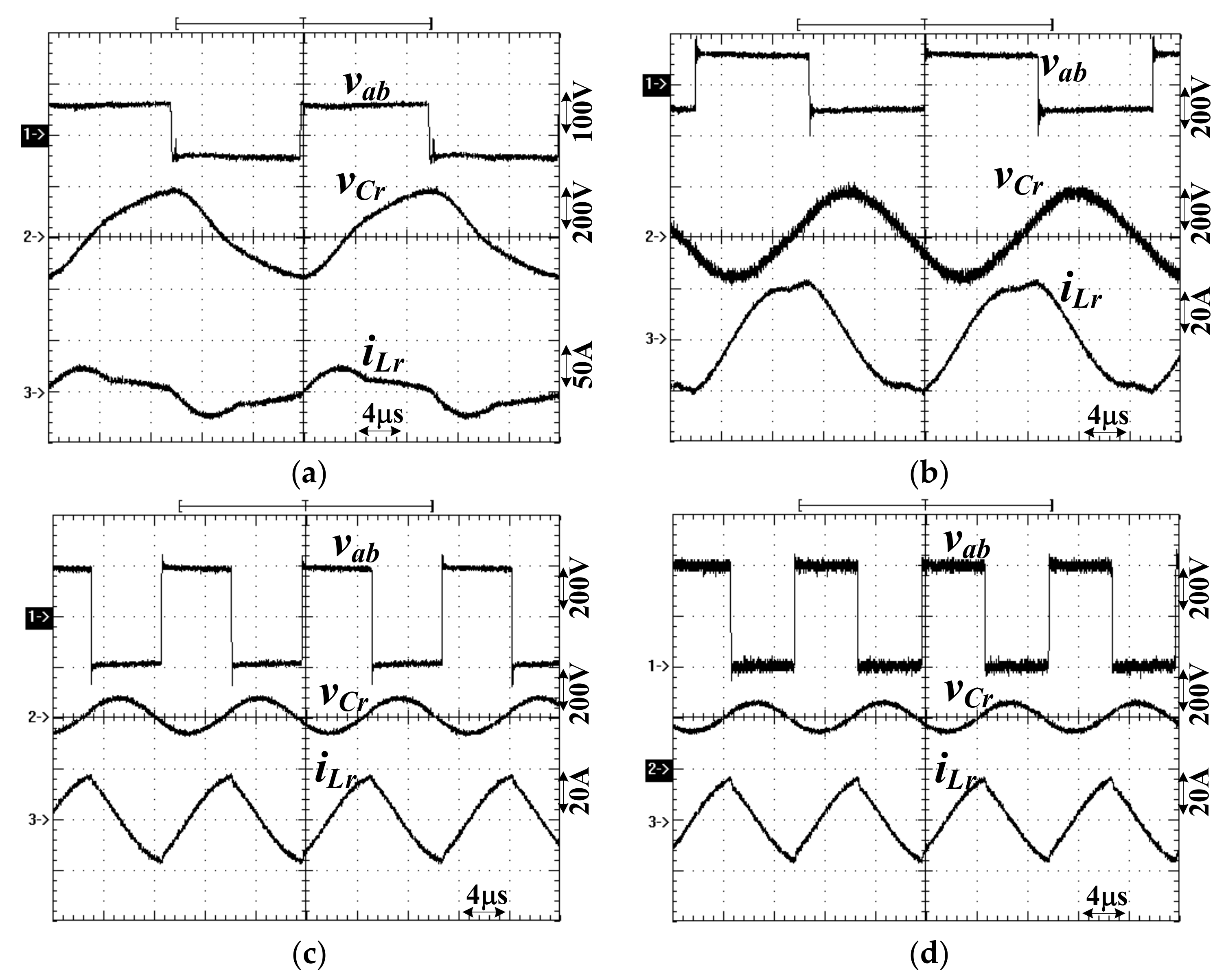

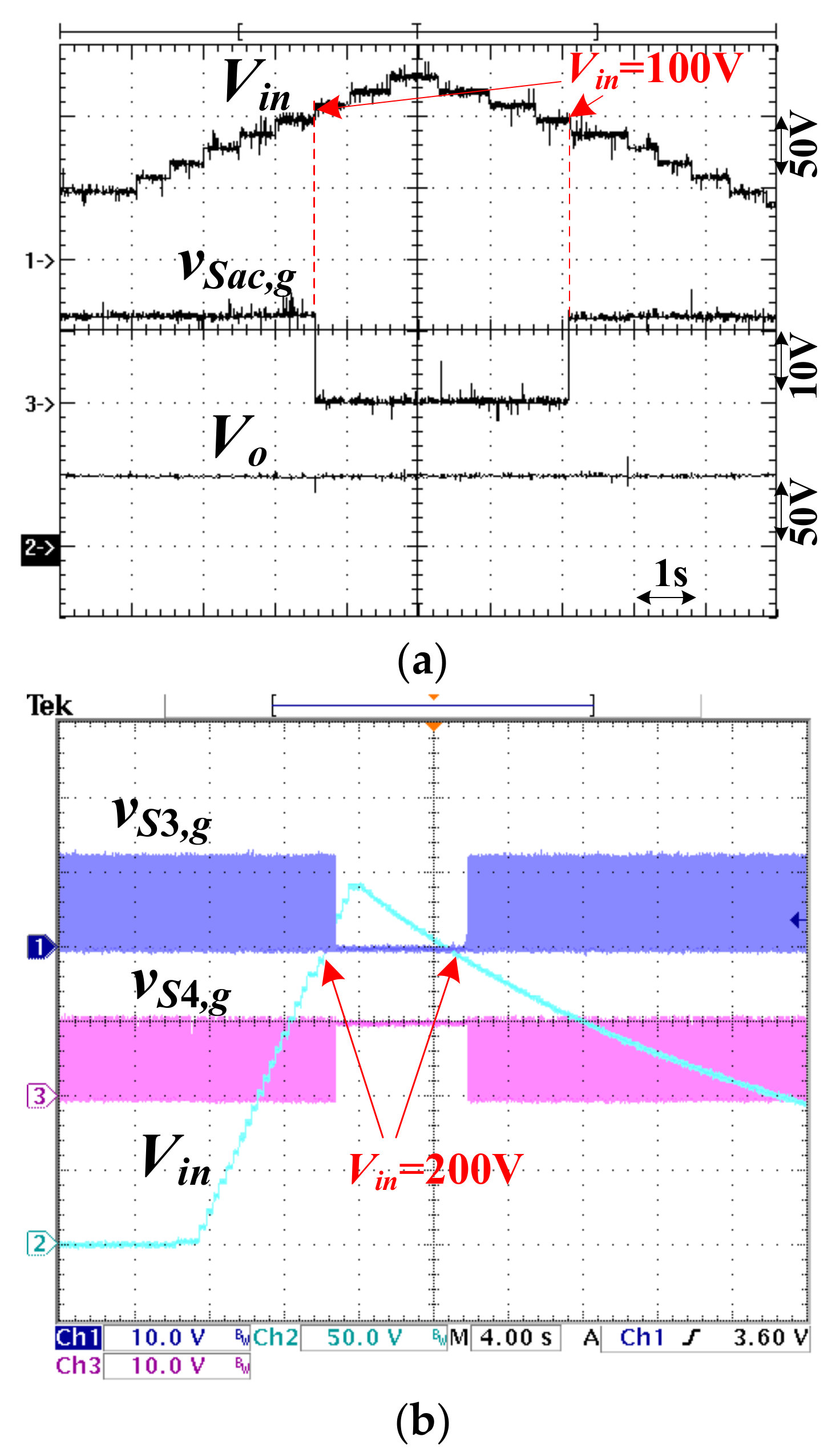

2.1. Low Voltage Region (Vin,L: 50–100 V)

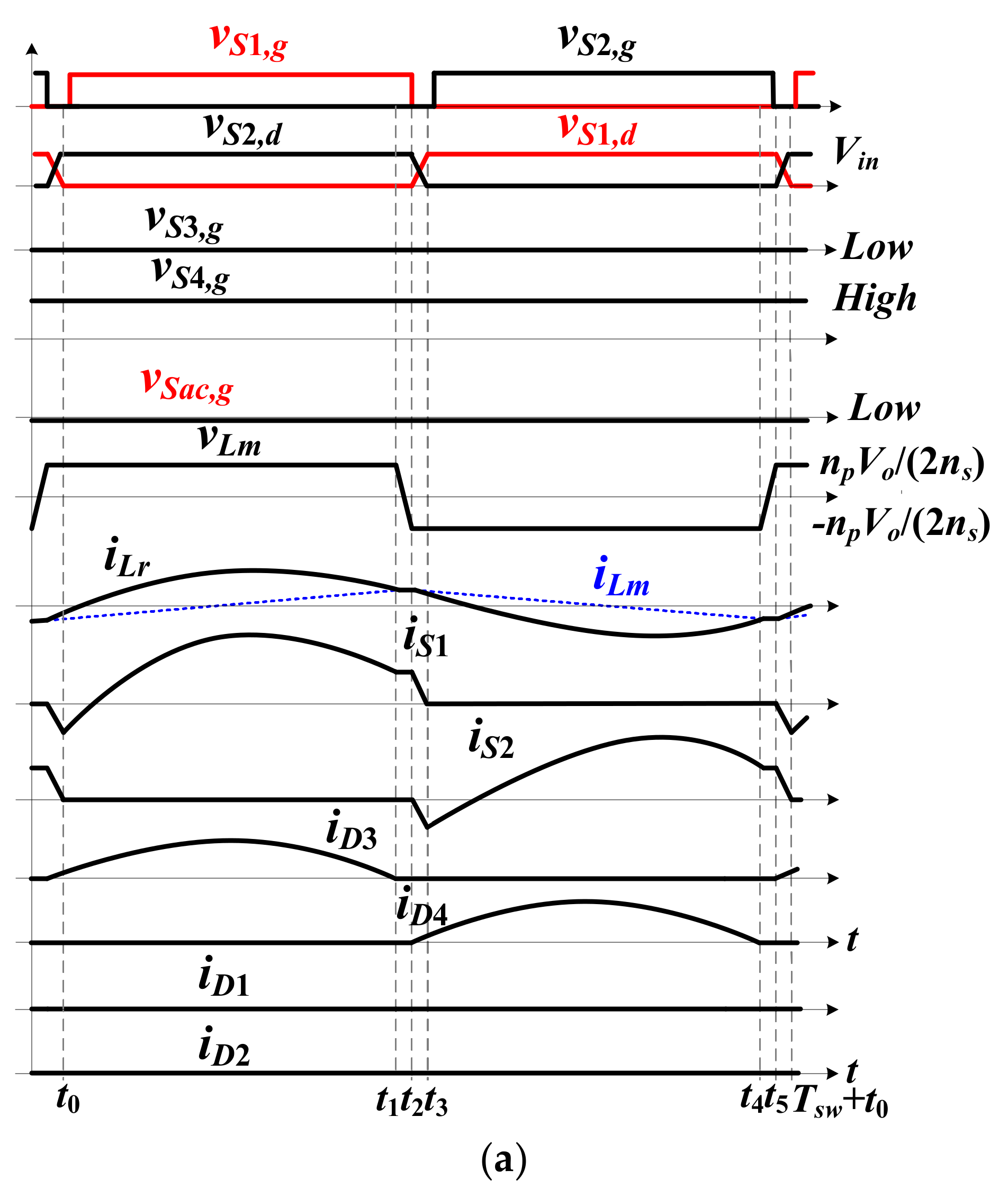

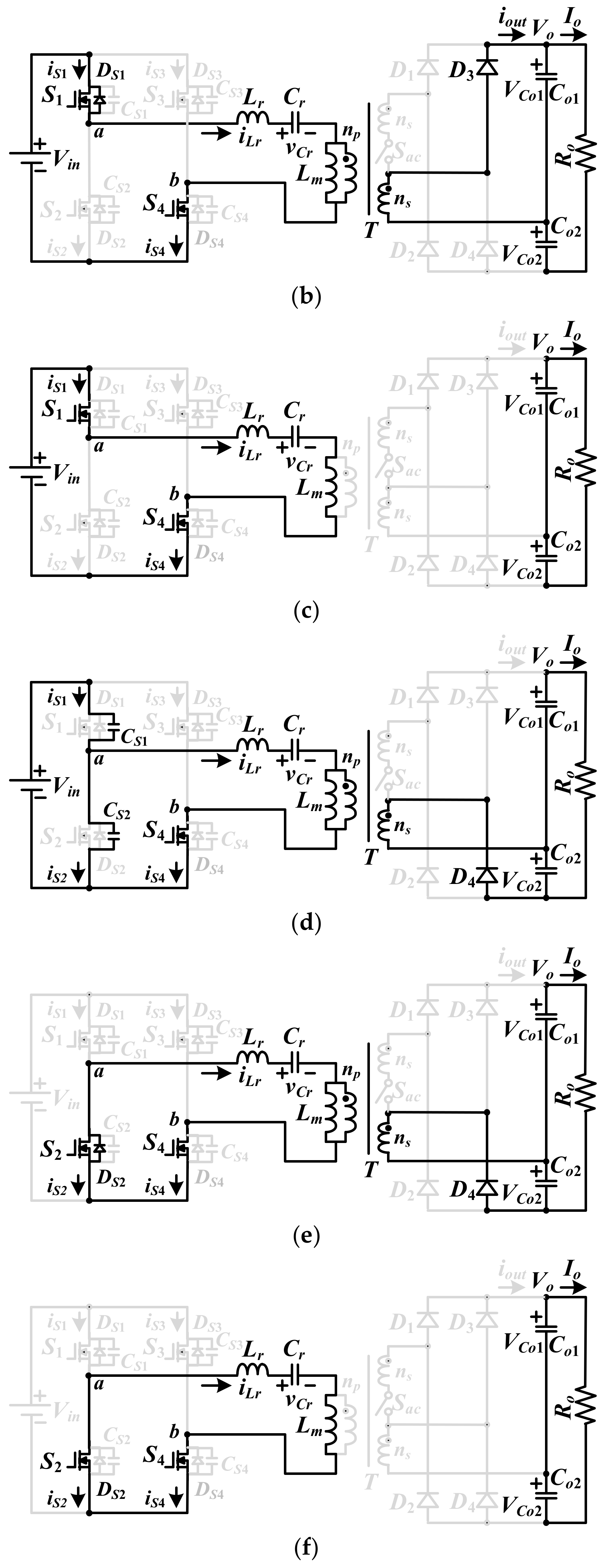

2.2. Medium Voltage Region (Vin,M: 100–200 V)

2.3. High Voltage Region (Vin,H: 200–400 V)

3. Circuit Characteristics and Design Example

4. Experimental Results

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Kim, J.Y.; Kim, H.S.; Baek, J.W.; Jeong, D.K. Analysis of effective three-level neutral point clamped converter system for the bipolar LVDC distribution. Electronics 2019, 8, 691. [Google Scholar] [CrossRef]

- Almalaq, Y.; Matin, M. Three topologies of a non-isolated high gian switched-capacitor step-up cuk converter for renewable energy applications. Electronics 2018, 7, 94. [Google Scholar] [CrossRef]

- Lin, B.R. Phase-shift pwm converter with wide voltage operation capability. Electronics 2020, 9, 47. [Google Scholar] [CrossRef]

- Lin, B.R. Analysis of a dc converter with low primary current loss and balance voltage and current. Electronics 2019, 8, 439. [Google Scholar] [CrossRef]

- Steigerwald, R.L. A comparison of half-bridge resonant converter topologies. IEEE Trans. Power Electron. 1988, 3, 174–182. [Google Scholar] [CrossRef]

- Lin, B.R.; Chu, C.W. Hybrid full-bridge and LLC converter with wide ZVS range and less output inductance. IET Power Electron. 2016, 9, 377–384. [Google Scholar] [CrossRef]

- Lee, J.B.; Kim, J.K.; Baek, J.I.; Kim, J.H.; Moon, G.W. Resonant capacitor on/off control of half-bridge LLC converter for high efficiency server power supply. IEEE Trans. Ind. Electron. 2016, 63, 5410–5415. [Google Scholar] [CrossRef]

- Sun, W.; Xing, Y.; Wu, H.; Ding, J. Modified high-efficiency LLC converters with two split resonant branches for wide input-voltage range applications. IEEE Trans. Power Electron. 2018, 33, 7867–7870. [Google Scholar] [CrossRef]

- Hu, H.; Fang, X.; Chen, F.; Shen, Z.J.; Batarseh, I. A modified high-efficiency LLC converter with two transformers for wide input-voltage range applications. IEEE Trans. Power Electron. 2013, 28, 1946–1960. [Google Scholar] [CrossRef]

- Lu, J.; Kumar, A.; Afridi, K.K. Step-down impedance control network resonant DC-DC converter utilizing an enhanced phase-shift control for wide-input-range operation. IEEE Trans. Ind. Appl. 2018, 54, 4523–4536. [Google Scholar] [CrossRef]

- Jeong, Y.; Kim, J.K.; Lee, J.B.; Moon, G.W. An asymmetric half-bridge resonant converter having a reduced conduction loss for DC/DC power applications with a wide range of low-input voltage. IEEE Trans. Power Electron. 2017, 32, 7795–7804. [Google Scholar] [CrossRef]

- Lin, B.R. Resonant converter with soft switching and wide voltage operation. Energies 2019, 12, 3479. [Google Scholar] [CrossRef]

- Lin, B.R. Series resonant converter with auxiliary winding turns: Analysis, design and implementation. Int. J. Electron. 2018, 105, 836–847. [Google Scholar] [CrossRef]

- Lin, B.R. Resonant converter with wide input voltage range and input current ripple free. IET Proc. Electron. Lett. 2018, 54, 1086–1088. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lin, B.-R.; Liu, Y.-C. Implementation of a Wide Input Voltage Resonant Converter with Voltage Doubler Rectifier Topology. Electronics 2020, 9, 1931. https://doi.org/10.3390/electronics9111931

Lin B-R, Liu Y-C. Implementation of a Wide Input Voltage Resonant Converter with Voltage Doubler Rectifier Topology. Electronics. 2020; 9(11):1931. https://doi.org/10.3390/electronics9111931

Chicago/Turabian StyleLin, Bor-Ren, and Yen-Chun Liu. 2020. "Implementation of a Wide Input Voltage Resonant Converter with Voltage Doubler Rectifier Topology" Electronics 9, no. 11: 1931. https://doi.org/10.3390/electronics9111931

APA StyleLin, B.-R., & Liu, Y.-C. (2020). Implementation of a Wide Input Voltage Resonant Converter with Voltage Doubler Rectifier Topology. Electronics, 9(11), 1931. https://doi.org/10.3390/electronics9111931