A Power Efficient Frequency Divider With 55 GHz Self-Oscillating Frequency in SiGe BiCMOS

Abstract

:1. Introduction

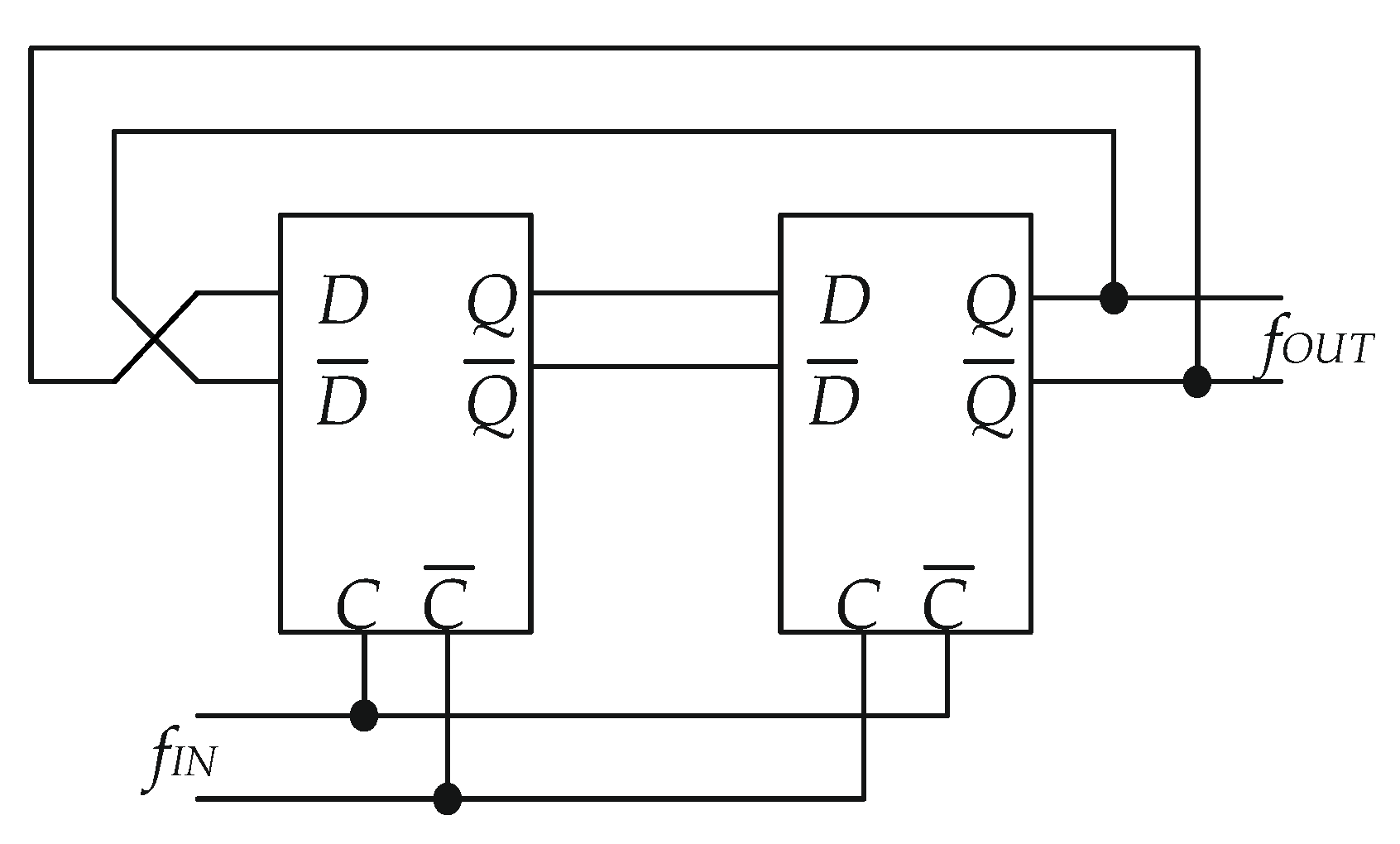

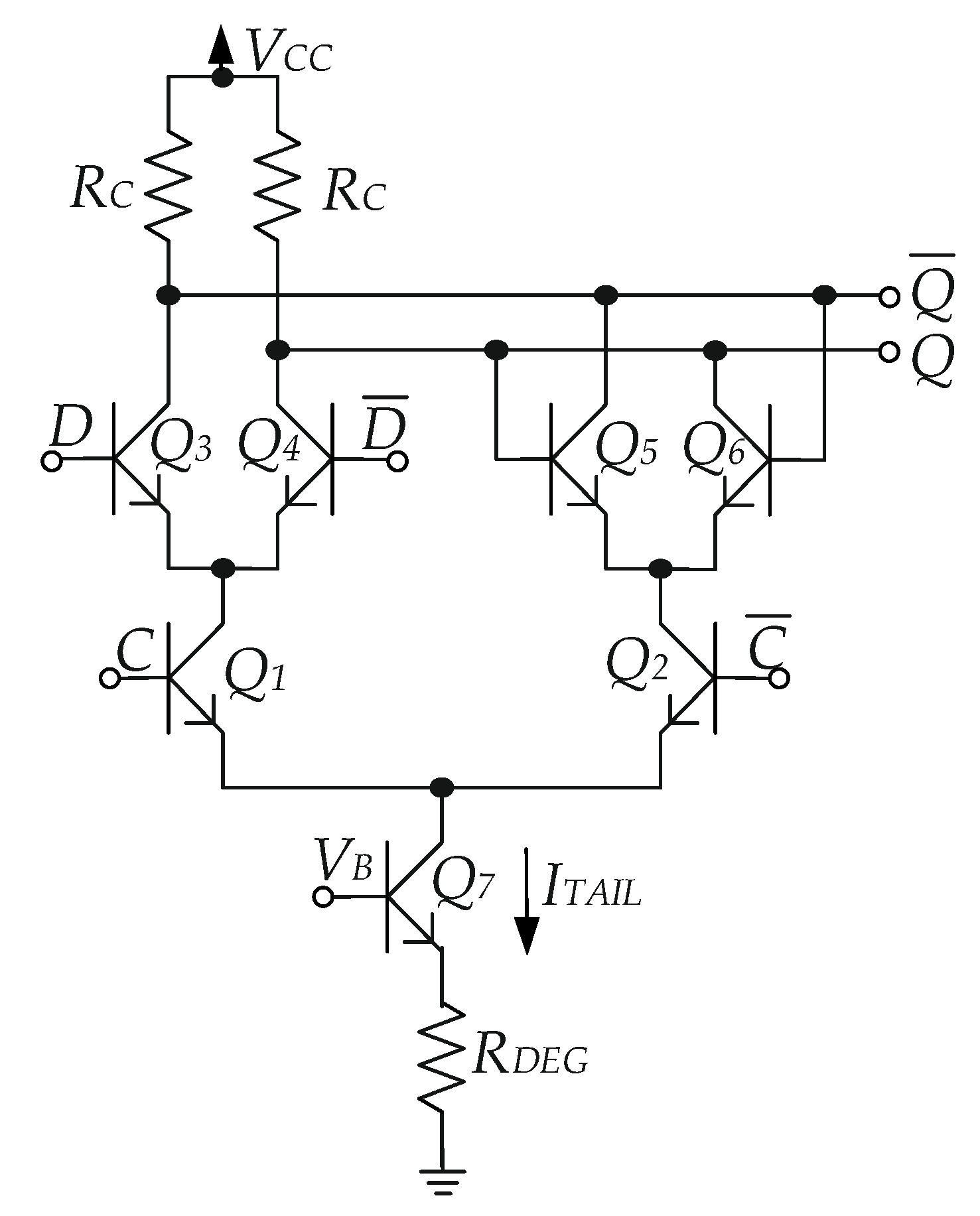

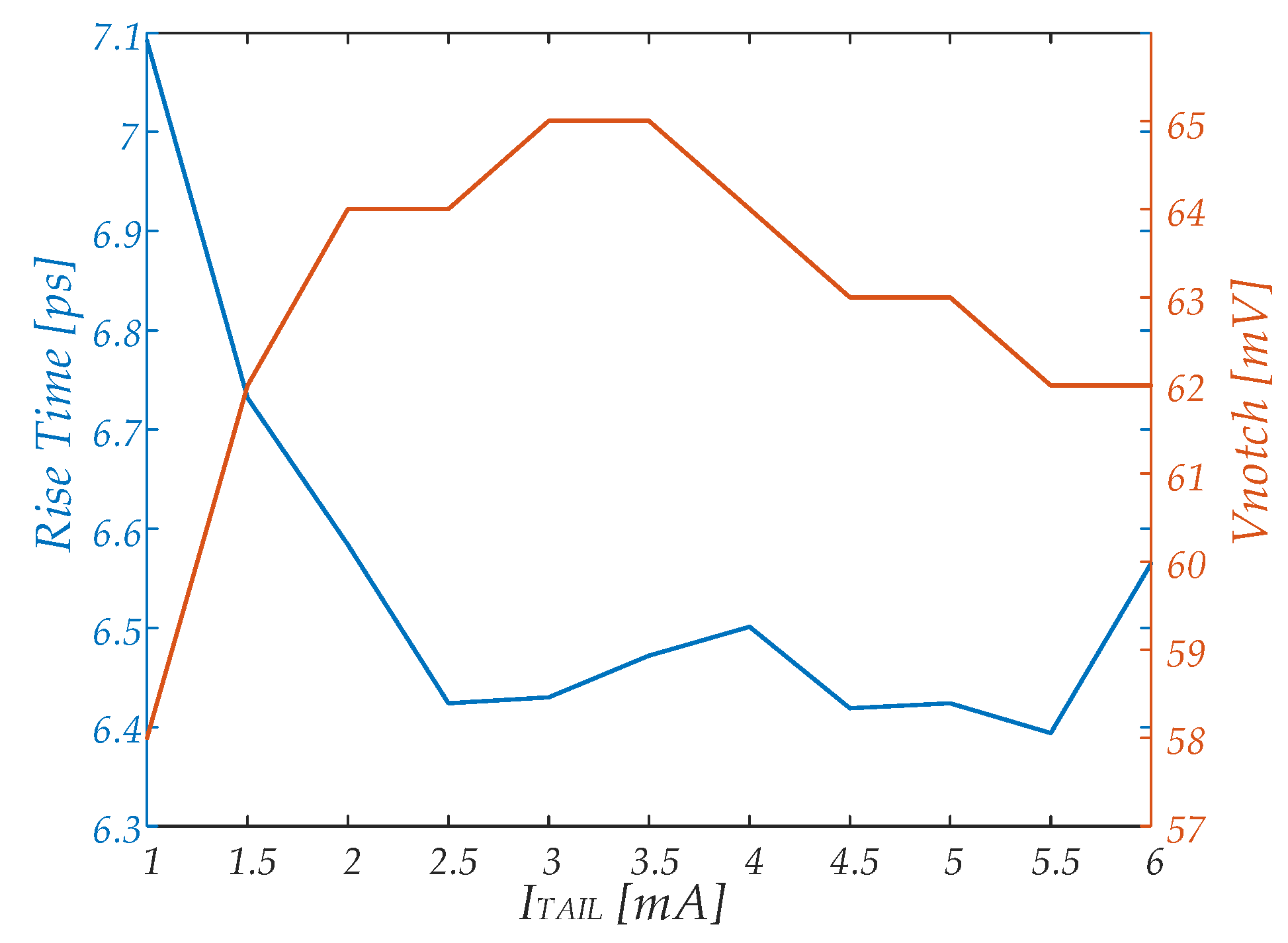

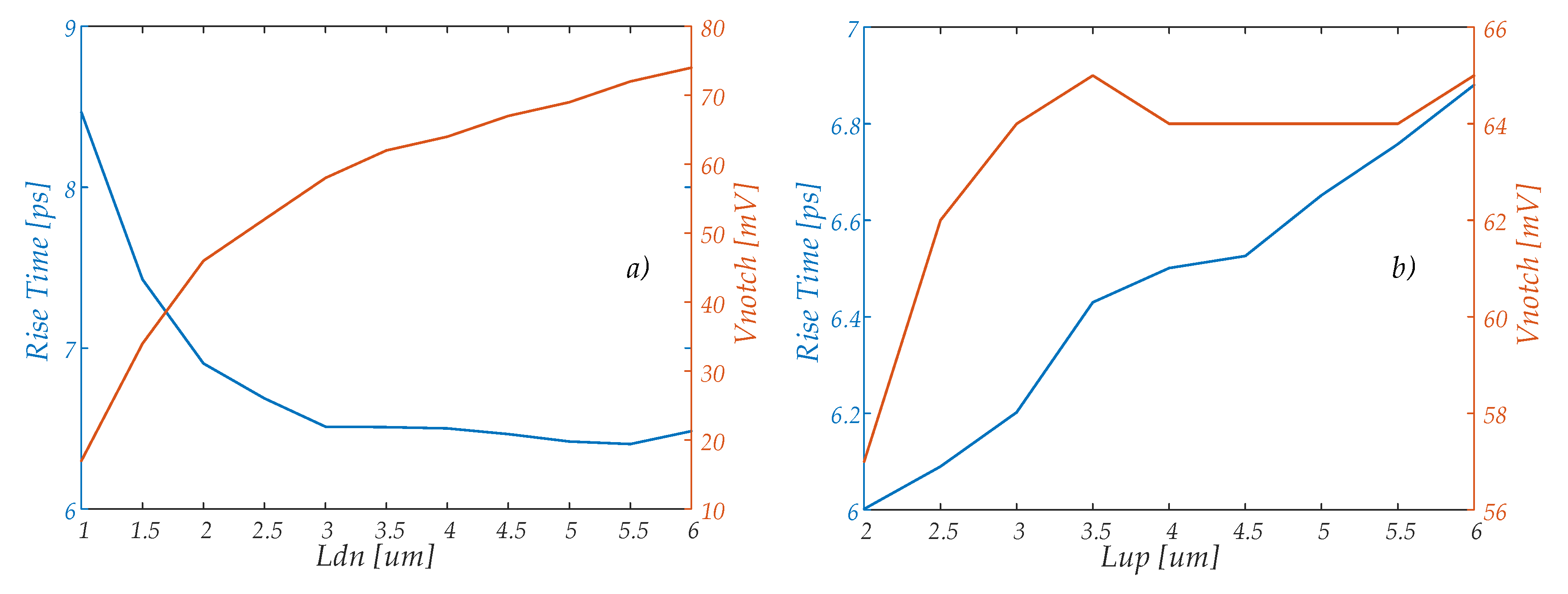

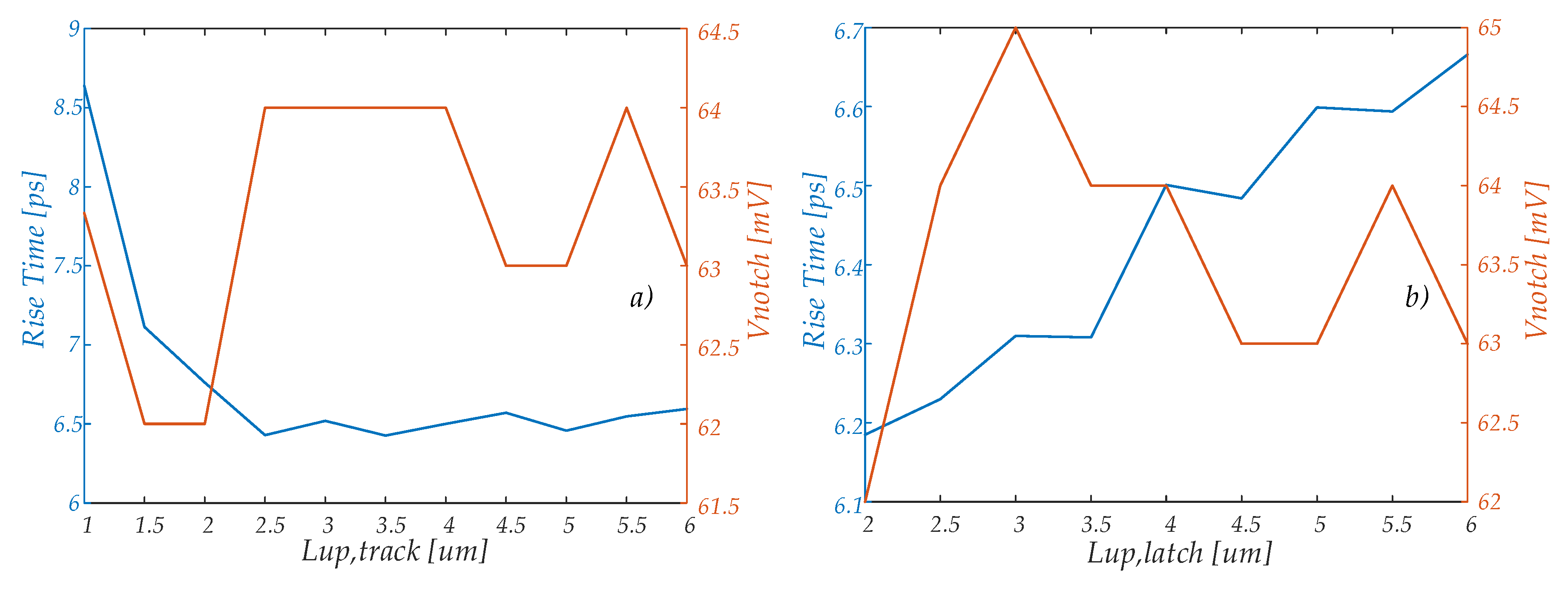

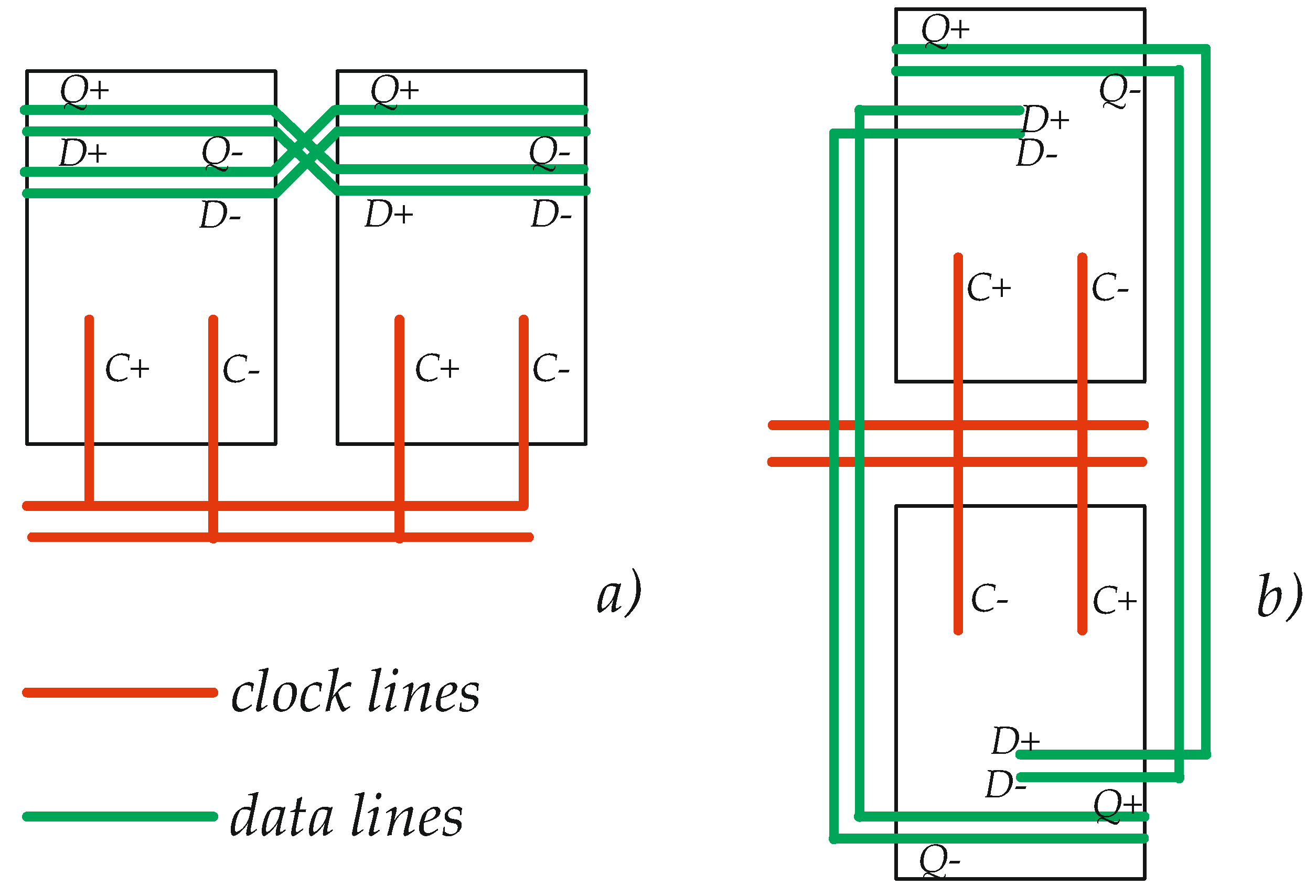

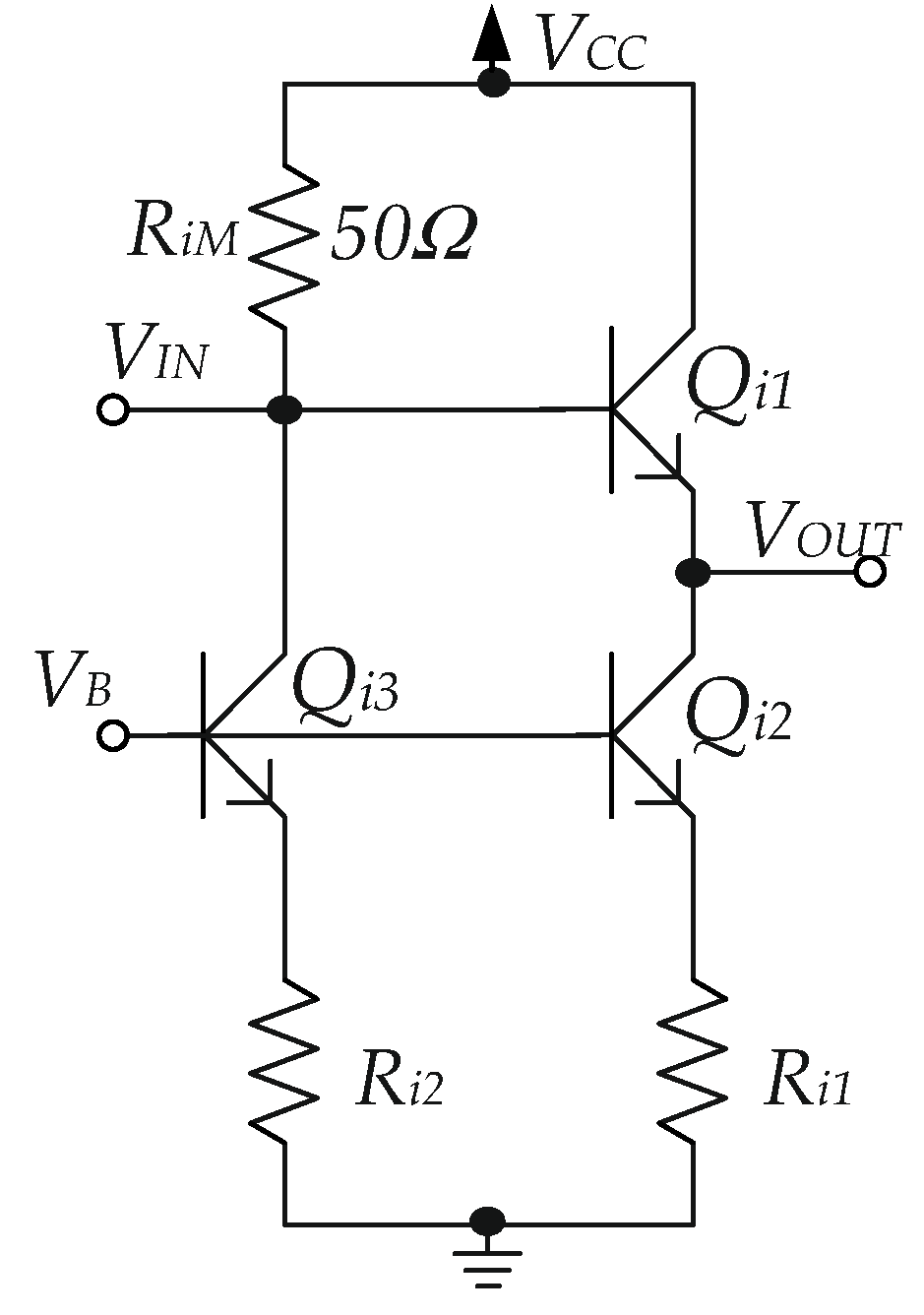

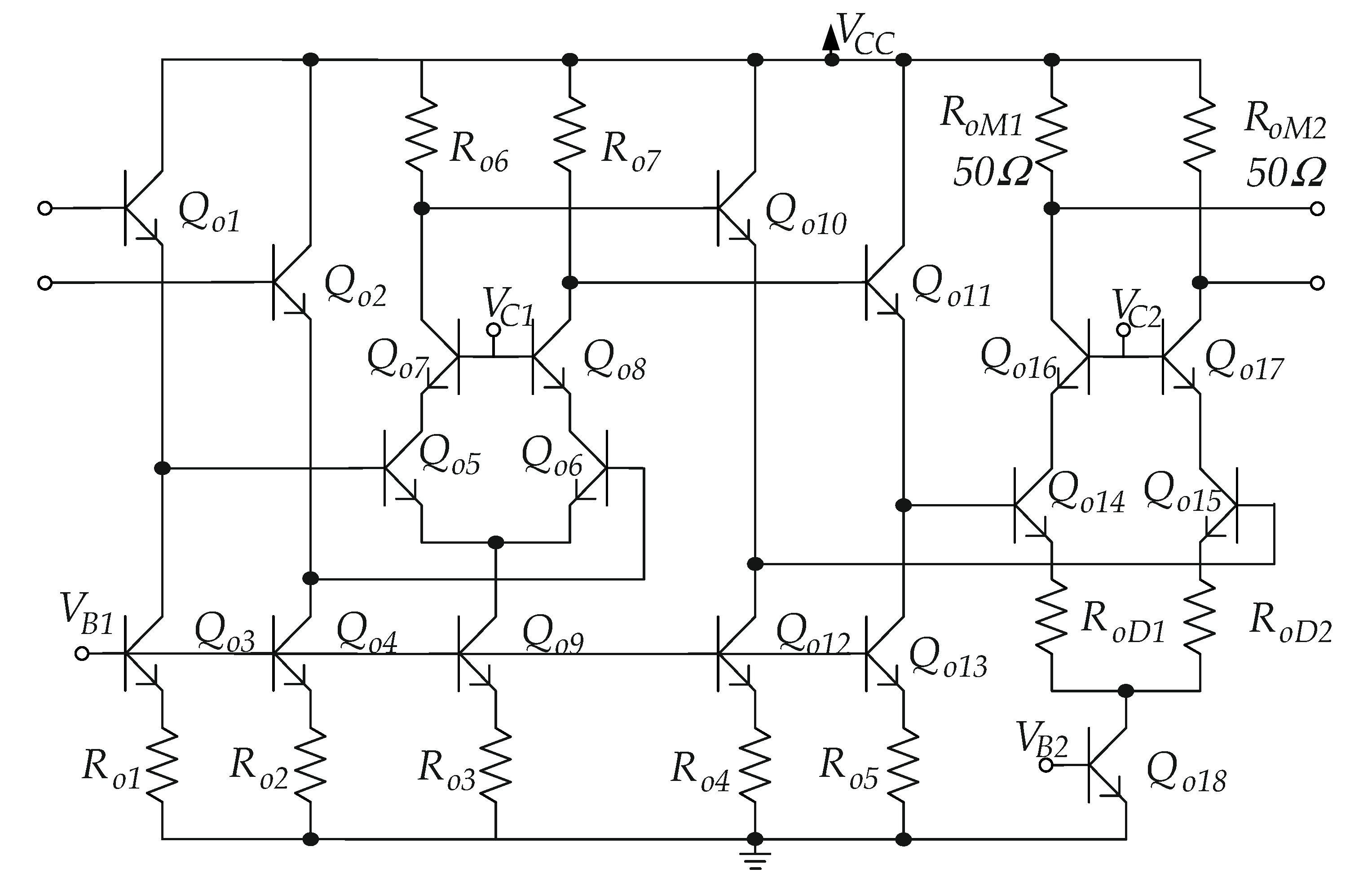

2. Frequency Divider Design

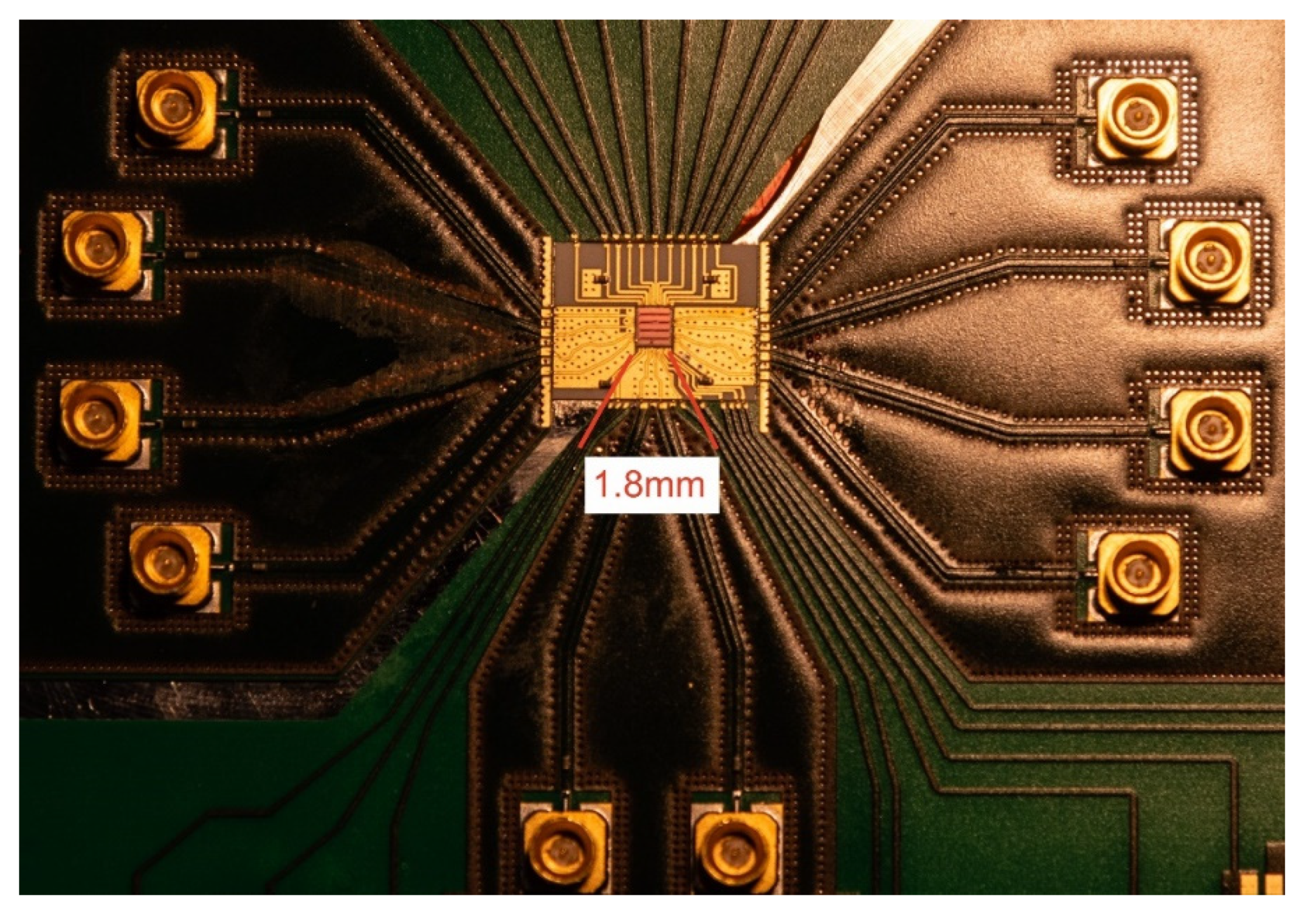

3. Design of the Divider Test Chip

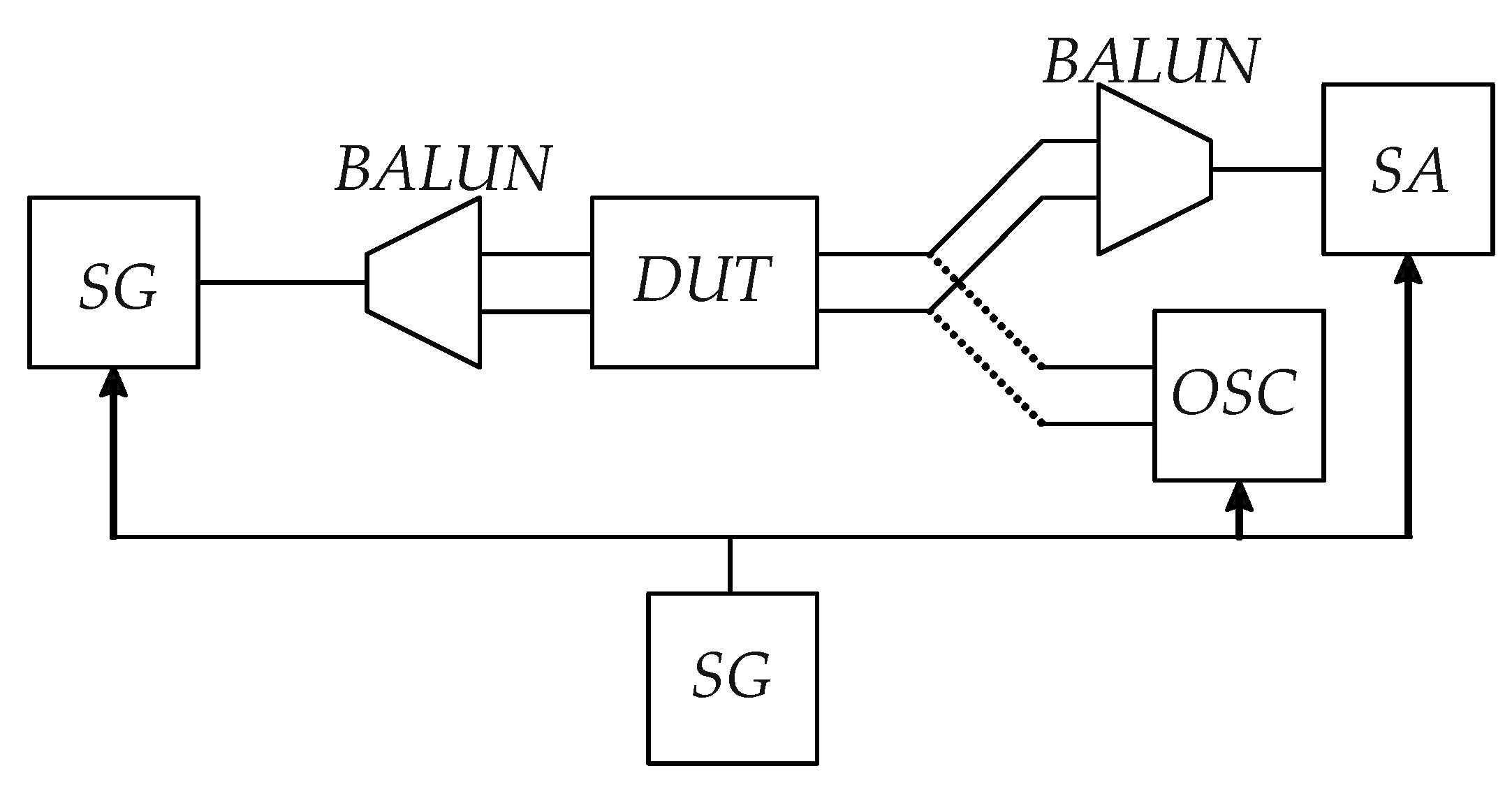

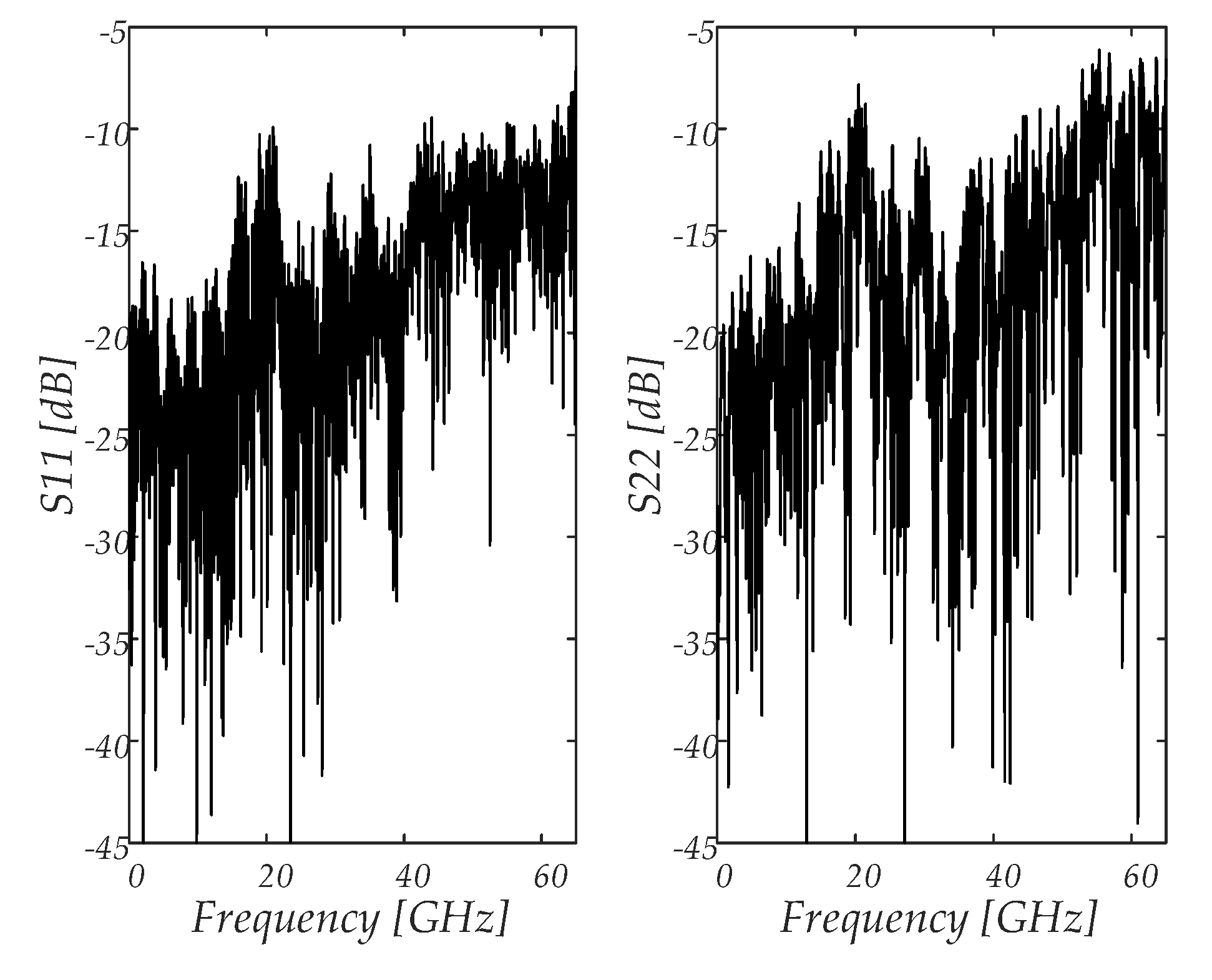

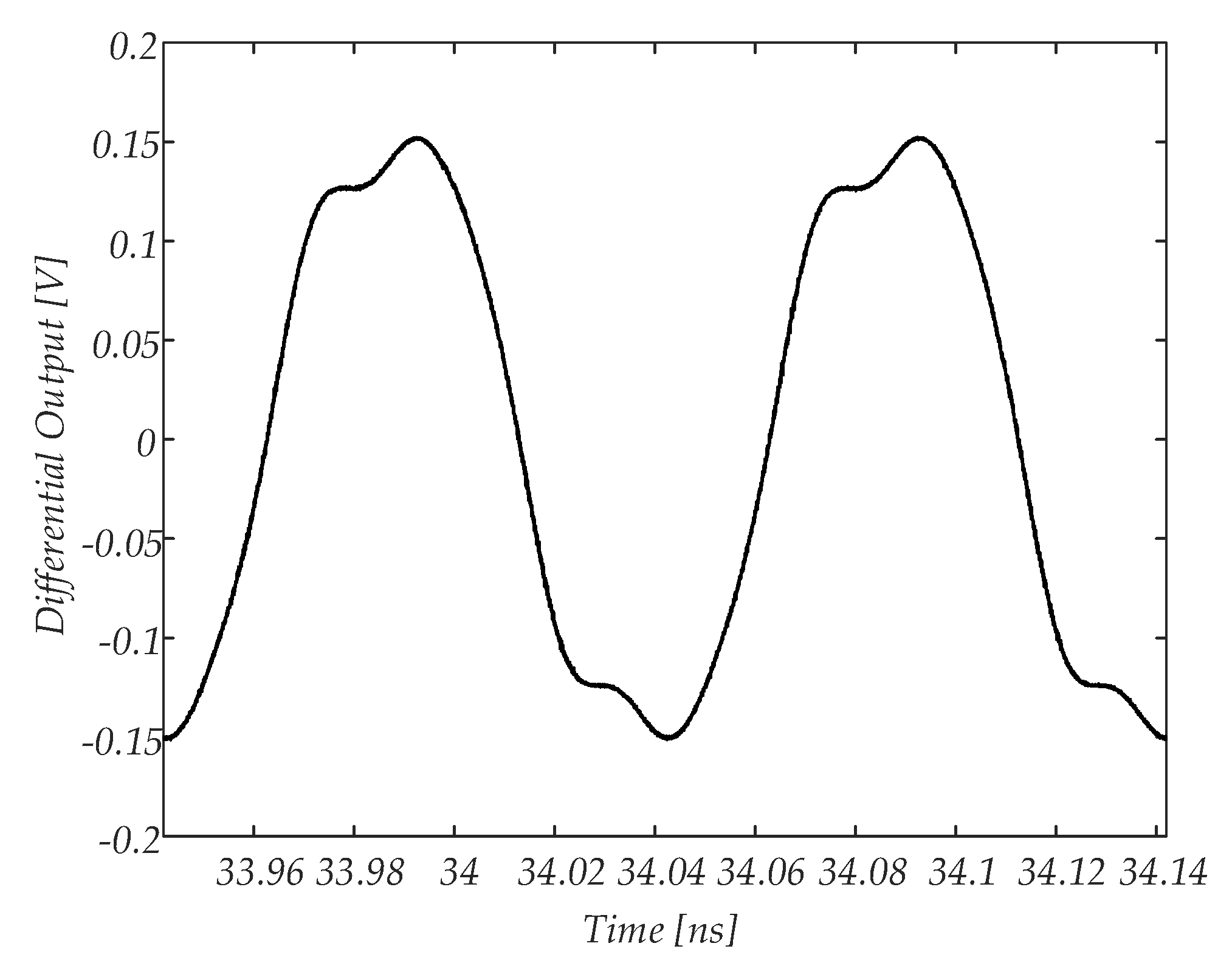

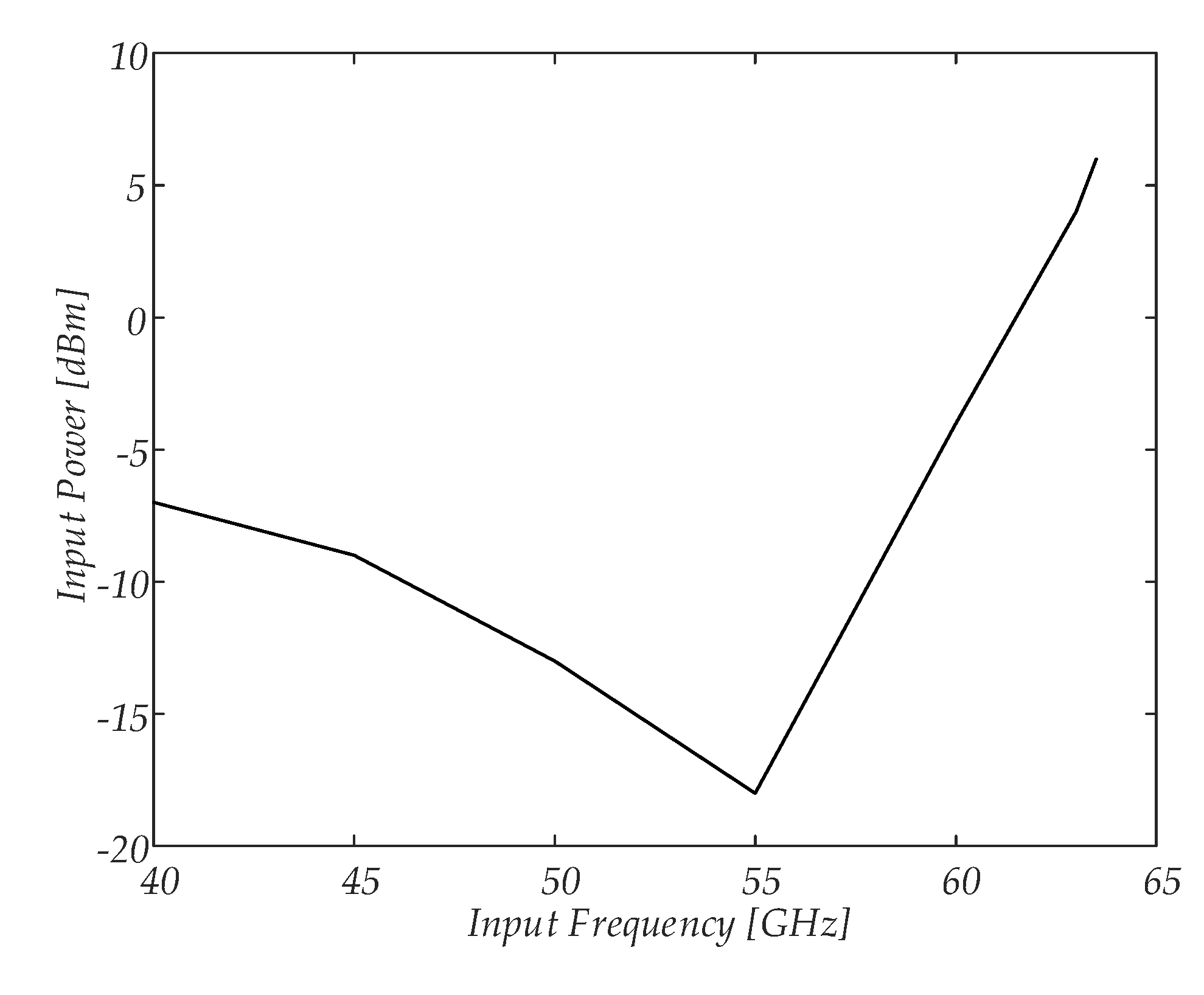

4. Measurement Results

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Shopov, S.; Balteanu, A.; Hasch, J.; Chevalier, P.; Cathelin, A.; Voinigescu, S.P. A 234-261-GHz 55-nm SiGe signal source with 5.4–7.2 dBm output power, 1.3% DC-to-RF efficiency, and 1-GHz divided-down output. IEEE J. Solid-State Circ. 2016, 51, 2054–2065. [Google Scholar] [CrossRef]

- Herzel, F.; Borngräber, J.; Ergintav, A. A 60 GHz frequency divider with quadrature outputs in 130nm SiGe BiCMOS technology for optical OFDM systems. In Proceedings of the 2015 10th European Microwave Integrated Circuits Conference (EuMIC), Paris, France, 7–8 September 2015; pp. 69–72. [Google Scholar] [CrossRef]

- Shu, G.; Choi, W.S.; Saxena, S.; Talegaonkar, M.; Anand, T.; Elkholy, A.; Elshazly, A.; Hanumolu, P.K. A 4-to-10.5 Gb/s continuous-rate digital clock and data recovery with automatic frequency acquisition. IEEE J. Solid-State Circ. 2016, 51, 428–439. [Google Scholar] [CrossRef]

- Hwang, H.; Kim, J. A 100 Gb/s quad-lane SerDes receiver with a pi-based quarter-rate all-digital CDR. Electronics 2020, 9, 1113. [Google Scholar] [CrossRef]

- Awny, A.; Moeller, L.; Junio, J.; Scheytt, J.C.; Thiede, A. Design and measurement techniques for an 80 Gb/s 1-tap decision feedback equalizer. IEEE J. Solid-State Circ. 2014, 49, 452–470. [Google Scholar] [CrossRef]

- Kull, L.; Luu, D.; Menolfi, C.; Brändli, M.; Francese, P.A.; Morf, T.; Kossel, M.; Cevrero, A.; Ozkaya, I.; Toifl, T. A 24-72-GS/s 8-b time-interleaved SAR ADC with 2.0-3.3-pJ/conversion and >30 dB SNDR at Nyquist in 14-nm CMOS FinFET. IEEE J. Solid-State Circ. 2018, 53, 3508–3516. [Google Scholar] [CrossRef]

- Grahn, J.V.; Fosshaug, H.; Jargelius, M.; Jönsson, P.; Linder, M.; Malm, B.G.; Mohadjeri, B.; Pejnefors, J.; Radamson, H.H.; Sandén, M.; et al. A low-complexity 62-GHz fT SiGe heterojunction bipolar transistor process using differential epitaxy and in situ phosphorus-doped poly-Si emitter at very low thermal budget. Solid-State Electron. 2000, 44, 549–554. [Google Scholar] [CrossRef]

- Rücker, H.; Heinemann, B. High-performance SiGe HBTs for next generation BiCMOS technology. Semicond. Sci. Technol. 2018, 33, 114003. [Google Scholar] [CrossRef]

- Zirath, H.; Carpenter, S.; He, Z.; Vassilev, V.; Bao, M. D-band MMIC design for high datarate wireless and wire-bound communication based on state-of-the-art InP DHBT and SiGe BiCMOS processes. In Proceedings of the 2018 Asia-Pacific Microwave Conference (APMC), Kyoto, Japan, 6–9 November 2018. [Google Scholar] [CrossRef]

- Voinigescu, S.P.; Shopov, S.; Hoffman, J.; Vasiliakopoulos, K. Analog and mixed-signal millimeter-wave SiGe BiCMOS circuits: State of the art and future scaling. In Proceedings of the 2016 IEEE Compound Semiconductor Integrated Circuit Symposium (CSICS), Austin, TX, USA, 23–26 October 2016. [Google Scholar] [CrossRef]

- Dyskin, A.; Kallfass, I. Amalytical approach for SiGe HBT static frequency divider design for millimeter-wave frequency operation. IEEE Trans. Microw. Theory Techn. 2018, 66, 1411–1417. [Google Scholar] [CrossRef]

- Seo, M.; Urteaga, M.; Young, A.; Rodwell, M. A 305–330+ GHz 2:1 dynamic frequency divider using InP HBTs. IEEE Microw. Wirel. Compon. Lett. 2010, 20, 468–470. [Google Scholar] [CrossRef]

- Lin, Y.H.; Wang, H. A 35.7–64.2 GHz low power Miller divider with weak inversion mixer in 65 nm CMOS. IEEE Microw. Wireless Compon. Lett. 2016, 26, 948–950. [Google Scholar] [CrossRef]

- Lin, B.-Y.; Liu, S.-I. Analysis and design of D-band injection-locked frequency dividers. IEEE J. Solid-State Circ. 2011, 46, 1250–1264. [Google Scholar] [CrossRef]

- Ali, U.; Bober, M.; Thiede, A.; Wagner, S. 100–166 GHz wide band high speed digital dynamic frequency divider design in 0.13 m SiGe BiCMOS technology. In Proceedings of the 2015 10th European Microwave Integrated Circuits Conference (EuMIC), Paris, France, 7–8 September 2015; pp. 73–76. [Google Scholar] [CrossRef]

- Monsurrò, P.; Trifiletti, A.; Angrisani, L.; D’Arco, M. Streamline calibration modelling for a comprehensive design of ATI-based digitizers. Measurement 2018, 125, 386–393. [Google Scholar] [CrossRef]

- Alioto, M.; Di Cataldo, G.; Palumbo, G. Design of low-power high-speed bipolar frequency dividers. Electron. Lett. 2002, 38, 158–160. [Google Scholar] [CrossRef]

- Schröter, M.; Rein, H.-M. Investigation of very fast and high-current transients in digital bipolar IC’s using both a new compact model and a device simulator. IEEE J. Solid-State Circ. 1995, 30, 551–562. [Google Scholar] [CrossRef]

- Chevalier, P.; Avenier, G.; Ribes, G.; Montagné, A.; Canderle, E.; Céli, D.; Derrier, N.; Deglise, C.; Durand, C.; Quémerais, T. A 55 nm triple gate oxide 9 metal layers SiGe BiCMOS technology featuring 320 GHz fT/370 GHz fMAX HBT and high-Q millimeter-wave passives. In Proceedings of the 2014 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2014; pp. 77–79. [Google Scholar] [CrossRef]

- Laskin, E.; Nicolson, S.T.; Chevalier, P.; Chantre, A.; Sautreuil, B.; Voinigescu, S.P. Low-power, low-phase noise SiGe HBT static frequency divider topologies up to 100 GHz. In Proceedings of the 2006 Bipolar/BiCMOS Circuits and Technology Meeting, Maastricht, The Netherlands, 8–10 October 2006. [Google Scholar] [CrossRef]

- Voinigescu, S.P.; Aroca, R.; Dickson, T.O.; Nicolson, S.T.; Chalvatzis, T.; Chevalier, P.; Garcia, P.; Garnier, C.; Sautreuil, B. Towards a sub-2.5V, 100-Gb/s serial transceiver. In Proceedings of the 2007 IEEE Custom Integrated Circuits Conference, San Jose, CA, USA, 16–19 September 2007; pp. 471–478. [Google Scholar] [CrossRef]

- Trotta, S.; Li, H.; Trivedi, V.P.; John, J. A tunable flipflop-based frequency divider up to 113 GHz and a fully differential 77GHz push-push VCO in SiGe BiCMOS technology. In Proceedings of the 2009 IEEE Radio Frequency Integrated Circuits Symposium, Boston, MA, USA, 7–9 June 2009; pp. 47–50. [Google Scholar] [CrossRef]

- D’Amore, M.; Monier, C.; Lin, S.; Oyama, B.; Scott, D.; Kaneshiro, E.; Gutierrez-Aitken, A.; Oki, A. A 0.25μm InP DHBT 200GHz+ static frequency divider. In Proceedings of the CSICS 2009 IEEE Compound Semiconductor Integrated Circuit Symposium, Greensboro, NC, USA, 11–14 October 2009. [Google Scholar] [CrossRef]

- Knapp, H.; Meister, T.F.; Liebl, W.; Claeys, D.; Popp, T.; Aufinger, K.; Schäfer, H.; Böck, J.; Boguth, S.; Lachner, R. Static frequency dividers up to 133 GHz in SiGe:C bipolar technology. In Proceedings of the 2010 IEEE Bipolar/BiCMOS Circuits and Technology Meeting (BCTM), Austin, TX, USA, 4–6 October 2010; pp. 29–32. [Google Scholar] [CrossRef]

- Ali, U.; Bober, M.; Thiede, A.; Awny, A.; Fischer, G. High speed static frequency divider design with 111.6 GHz self-oscillation frequency (SOF) in 0.13 m SiGe BiCMOS technology. In Proceedings of the 2015 German Microwave Conference, Nuremberg, Germany, 16–18 March 2015; pp. 241–243. [Google Scholar] [CrossRef]

- Dyskin, A.; Harati, P.; Kallfass, I. Layout and interconnect optimization for low-power and high-sensitivity operation of E-band SiGe HBT frequency dividers. IEEE Microw. Wirel. Compon. Lett. 2018, 28, 67–69. [Google Scholar] [CrossRef]

- Rehman, S.U.; Ferchichi, A.; Khafaji, M.M.; Carta, C.; Ellinger, F. A 1–60 GHz 9.6 mW 0.18 V output-swing static clock divider circuit in 45-nm SOI CMOS. In Proceedings of the 2018 25th IEEE International Conference on Electronics, Bordeaux, France, 9–12 December 2018; pp. 41–44. [Google Scholar] [CrossRef]

- Zhou, P.; Chen, J.; Yan, P.; Hou, D.; Hong, W. A low power, high sensitivity SiGe HBT static frequency divider up to 90 GHz for millimeter-wave application. China Commun. 2019, 16, 85–94. [Google Scholar]

| Transistor | Total Emitter Area (μm2) | HBT Type and Number of Emitters |

|---|---|---|

| Q1, Q2 | 0.8 | HS, 1 emitter |

| Q3, Q4, Q5, Q6 | 0.8 | HS, 1 emitter |

| Q7 | 3.2 | HS, 2 emitters |

| Resistor | Value | - |

| RC | 37.5 Ω | - |

| Rdeg | 50 Ω | - |

| Transistor | Total Emitter Area (μm2) | HBT Type and Number of Emitters |

|---|---|---|

| Qi1 | 1.6 | HS, 2 emitters |

| Qi2, Qi3 | 1.6 | HV, 2 emitters |

| Resistor | Value | - |

| RiM | 50 Ω | - |

| Ri1, Ri2 | 100 Ω | - |

| Transistor | Total Emitter Area (μm2) | HBT Type and Number of Emitters |

|---|---|---|

| Qo1, Qo2 | 0.4 | HS, 1 emitter |

| Qo3, Qo4 | 1.6 | HS, 2 emitters |

| Qo5, Qo6 | 1.2 | HS, 2 emitters |

| Qo7, Qo8 | 0,6 | HS, 1 emitter |

| Qo9 | 1.6 | HS, 2 emitters |

| Qo10, Qo11 | 1.6 | HS, 2 emitters |

| Qo12, Qo13 | 1.6 | HS, 2 emitters |

| Qo14, Qo15 | 4 | HS, 4 emitters |

| Qo16, Qo17 | 2 | HS, 4 emitters |

| Qo18 | 8.4 | HS, 8 emitters |

| Resistor | Value | - |

| Ro1, Ro2, Ro3 | 100 Ω | - |

| Ro6, Ro7 | 100 Ω | - |

| Ro4, Ro5 | 100 Ω | - |

| RoM1, RoM2 | 50 Ω | - |

| RoD1, RoD2 | 21.5 Ω | - |

| Block | Power Consumption |

|---|---|

| Input Buffer | 26.8 mW |

| Divider Core | 23.7 mW |

| Limiter with EFs | 28.9 mW |

| Output Buffer | 78.6 mW |

| Biasing | 51.9 mW |

| Reference | Technology (fT) | Inductor | SOF | fmax | Pcore | FOM |

|---|---|---|---|---|---|---|

| [20] | SiGe (230) | Y | 77 | 100 | 122 | 0.63 |

| [21] | CMOS 65 nm | Y | 79.2 | 90 | 19.2 | 4.12 |

| [21] | SiGe (150) | Y | 92 | 104 | 56 | 1.64 |

| [22] | SiGe (200) | N | 104 | 113 | 115 | 0.90 |

| [23] | InP (530) | Y | 173 | 200 | 228 | 0.76 |

| [24] | SiGe (230) | N | 56 | 87 | 14 | 4.00 |

| [24] | SiGe (230) | N | 96 | 133 | 210 | 0.46 |

| [5] | SiGe (240) | N | 70.3 | 100 | 141 | 0.50 |

| [25] | SiGe (300) | No | 111.6 | 128.7 | 196 | 0.57 |

| [2] | SiGe (240) | Y | 52 | 60 | 115 | 0.45 |

| [26] | SiGe (250) | N | 77 | 80 | 80 | 0.96 |

| [27] | CMOS 45 nm | Y | 60 | 60 | 9.6 | 6.25 |

| [28] | SiGe (200) | Y | 75.1 | 90 | 61.6 | 1.22 |

| This Work | SiGe (320) | N | 55 | 63.5 | 23.7 | 2.32 |

| - | (GHz) | - | GHz | GHz | mW | GHz/mW |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Centurelli, F.; Monsurrò, P.; Scotti, G.; Tommasino, P.; Trifiletti, A. A Power Efficient Frequency Divider With 55 GHz Self-Oscillating Frequency in SiGe BiCMOS. Electronics 2020, 9, 1968. https://doi.org/10.3390/electronics9111968

Centurelli F, Monsurrò P, Scotti G, Tommasino P, Trifiletti A. A Power Efficient Frequency Divider With 55 GHz Self-Oscillating Frequency in SiGe BiCMOS. Electronics. 2020; 9(11):1968. https://doi.org/10.3390/electronics9111968

Chicago/Turabian StyleCenturelli, Francesco, Pietro Monsurrò, Giuseppe Scotti, Pasquale Tommasino, and Alessandro Trifiletti. 2020. "A Power Efficient Frequency Divider With 55 GHz Self-Oscillating Frequency in SiGe BiCMOS" Electronics 9, no. 11: 1968. https://doi.org/10.3390/electronics9111968

APA StyleCenturelli, F., Monsurrò, P., Scotti, G., Tommasino, P., & Trifiletti, A. (2020). A Power Efficient Frequency Divider With 55 GHz Self-Oscillating Frequency in SiGe BiCMOS. Electronics, 9(11), 1968. https://doi.org/10.3390/electronics9111968