LFMCW radars are expansively used in automotive anti-collision, security check, imaging and presence detection applications when high range resolution is required in localization/tracking. A variety of modulation schemes are available, with a transmitted frequency signal acting as sine wave, sawtooth wave, triangular wave or square wave. In a sawtooth wave-based FMCW radar, the achievable range and velocity resolution depend on the transmitting signal bandwidth BW and the linear chirp period T

m, as seen in

Figure 2. The range resolution Δr, which refers to the minimum detectable separation distance of two targets of equal cross sections that can be differentiated as distinct targets, is proportional to

c/2/BW, where

c is the velocity of light. This means that a large modulation bandwidth

BW is needed for a fine range resolution. For a transceiver operating at 94 GHz, a modulation period in the order of 100 µs, a modulation bandwidth of higher than 500 MHz, the analog baseband bandwidth can be calculated as follows:

where

BW is the transmitting signal bandwidth,

Tm is the linear chirp period,

K is the FMCW slope,

fo is the center operating frequency,

v is the target velocity,

c is the velocity of light,

r is the distance from source to target,

fIF,static is the analog baseband frequency for static target ranging, and

fIF,moving is the analog baseband frequency for moving target ranging. After setting

BW = 500 MHz,

Tm = 100 µs,

c = 3 × 10

8 m/s,

r = 6~7 km into Equations (1)–(4), we can calculate the

fIF,static to be 20~23.4 MHz. When doppler radar effect is taken into account, the IF frequency should cover the range of 18~25 MHz. Therefore, for generally used LPFs, the analog baseband −3 dB bandwidth is set to be 18/19/20/21/22/23/24/25 MHz, with 3-bit digital control words to cover the frequency shift coming from potential target moving.

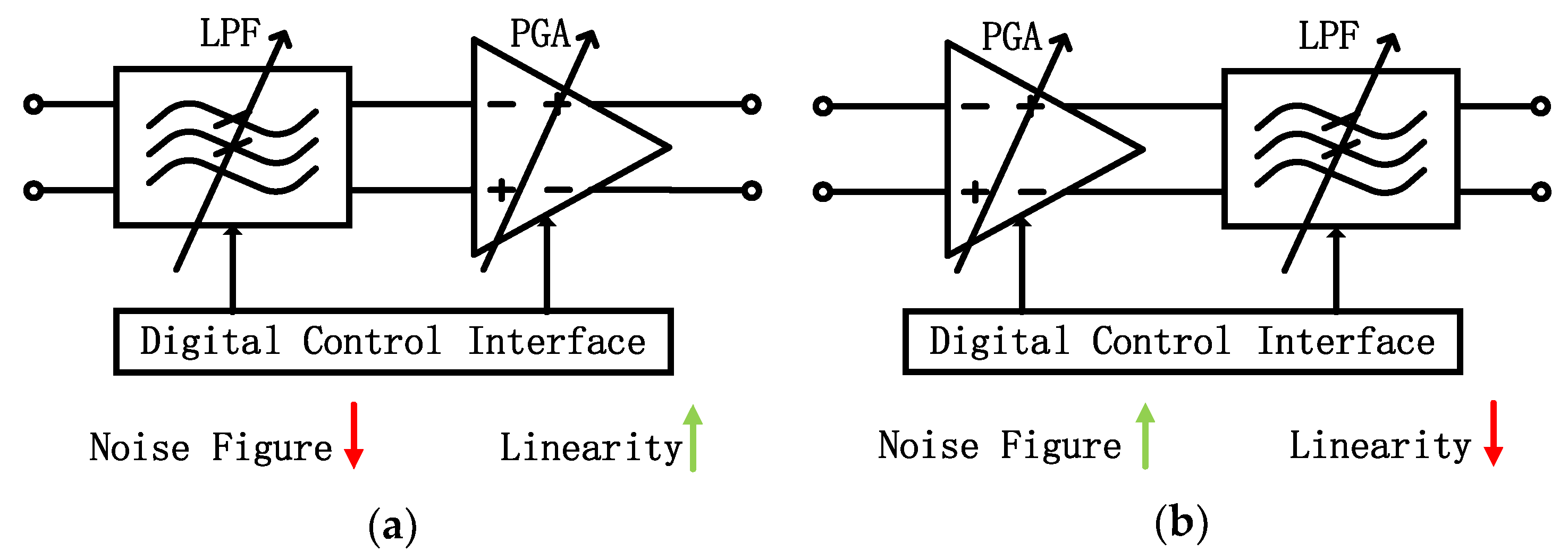

In this LFMCW radar, direct conversion architecture is adopted to evade image rejection problems and, thus, the analog baseband consumes lower power, since its bandwidth is half of that in low-IF/super heterodyne receivers. Paradoxically, typical dynamic range of direct conversion receiver is lower than that of low-IF/super heterodyne ones. Therefore, novel dynamic range optimization techniques are investigated in two directions: lower noise figure and higher linearity. Merged PGA/LPF biquads in [

9] simultaneously optimized the two specifications owing to a closed-loop topology with switchable filter orders. However, this kind of topology becomes power-hungry when the frequency rises, and its gain resolution depends on the resistor/capacitor array size. In other words, the merged analog baseband compromises power consumption and chip size for noise/linearity/gain/filter order reconfigurability. What is more, the noise figure of PGA/LPF is normally higher than 25 dB, which deteriorates the receiver noise specification, since the front-end (including a low noise amplifier and a mixer) of the linear FMCW receiver usually possesses a gain of lower than 20 dB. Thus, architectures in

Figure 1 and the merged analog baseband in [

9] cannot satisfy the noise/linearity/power consumption requirement concurrently.

This paper makes a modification to the LPF-first/PGA-first topology by adding a programmable gain pre-amplifier with course gain tuning ability to its front, as depicted in

Figure 3, which forms a PGA-LPF-PGA topology. In detail, this topology includes a pre-amplifier for noise optimization and course gain tuning, a folded Gilbert variable gain amplifier (VGA) with a symmetrical exponential voltage generator and a 10-bit R-2R DAC for fine gain tuning, a level shifter, a programmable G

m-C LPF, a DC offset cancellation (DCOC) circuit, two fixed gain amplifiers (FGA) with bandwidth extension and a novel buffer amplifier with active peaking for testing purposes. DC coupling is utilized on account of spectrally efficient modulation schemes [

12]. The architecture in

Figure 3 is open-loop and thus, frequency/power scalable. From the LPF-first viewpoint, this topology optimizes noise figure with another PGA ahead. From the PGA-first viewpoint, this topology ameliorates linearity with another PGA behind. Nonetheless, a heavy signal-processing burden is placed upon the LPF and its high linearity is a prerequisite.

In search of a high linearity LPF, researchers proposed numerous high linearity structures, such as active-R-C and class-AB G

m-C ones [

6,

13,

14,

15,

16]. Linearity is refined with a compromise of power consumption and operation frequency, which is fundamentally determined by the closed-loop LPF topology and the complex routings inside the trans-conductor. Thus, high linearity open loop LPFs, which theoretically decouples the linearity from power consumption, are urgently needed.