Optimizing Crosstalk in Optical NoC through Heuristic Fusion Mapping

Abstract

1. Introduction

2. Design of Heuristic Fusion Mapping Algorithm for Crosstalk Optimization

- (1)

- when the positions coincide, move to the right end and left end, respectively, according to the positive and negative speed until the idle topology node is found;

- (2)

- when the left and right sides are out of bounds, find the mapping position by modulus value.

3. Realization of Heuristic Fusion Mapping Algorithm for Crosstalk Optimization

| Algorithm 1. |

| Input: Iteration number: IT; Population size: NP |

| Parameter: Inertia factor: ω; Learning factor: C1, C2; Random value: R1, R2; Temperature control value: T; Individual minimum crosstalk: CP; Global minimum crosstalk: CG; Current iteration number: IC; Number of traversed particles: NC; Individual optimal mapping: MP; Global optimal mapping: MG; Current particle label: LC; Optimal particle label: LO |

| Output: Historical minimum crosstalk: CH; Historical optimal mapping: MH |

| Procedure Generate mapping solutions of initial particle swarm randomly; Calculate the crosstalk corresponding to each particle mapping; Record the initial minimum crosstalk CP and mapping mode MP; Obtain global minimum crosstalk CG and global optimal mapping MG by comparsion and label the optimal particle LO; Initialize historical minimum crosstalk CH and historical optimal mapping MH while (IC < IT) while (NC < NP ) if (LC == LO) Exchange two task mapping positions randomly and calculate the crosstalk; if (crosstalk < CP) Update CP and MP; else Update CP and MP according to the Metropolis criterion endif else Update speed and position of each particle; Calculate the crosstalk of particle and update CP, MP endif end Update CG and MG by comparsion; Update CH and MH; Change ω and T end return MH |

4. Simulation Results

4.1. Topology

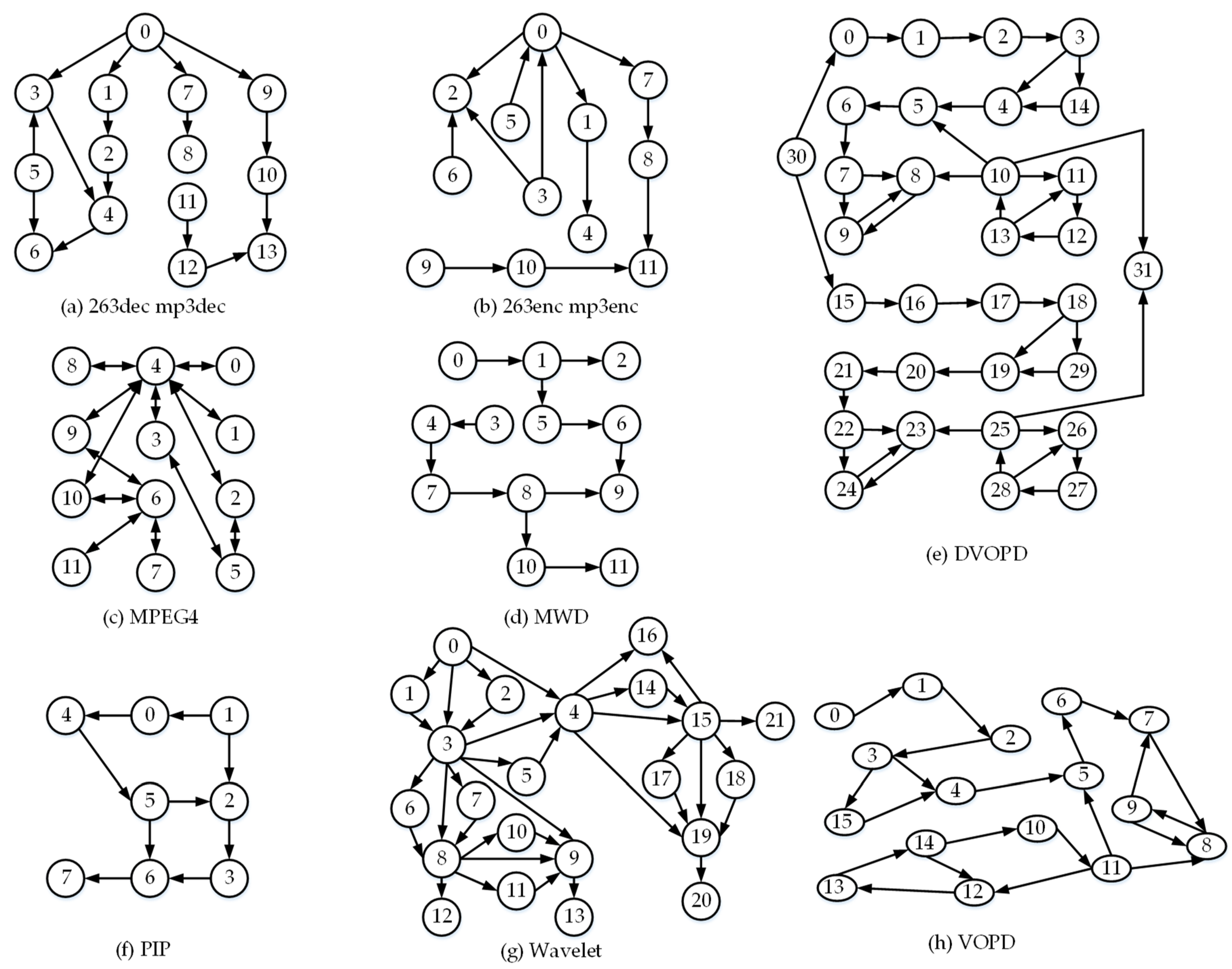

4.2. Multimedia Application

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Kogel, T.; Doerper, M.; Wieferink, A.; Leupers, R.; Ascheid, G.; Meyr, H.; Goossens, S. A modular simulation framework for architectural exploration of on-chip interconnection networks. In Proceedings of the 1st IEEE/ACM/IFIP International Conference on Hardware/Software Codesign and System Synthesis, Newport Beach, CA, USA, 1–3 October 2003; pp. 7–12. [Google Scholar]

- Benini, L.; De Micheli, G. Networks on chips: A new SoC paradigm. Computer 2002, 35, 70–78. [Google Scholar] [CrossRef]

- O’Connor, I. Optical solutions for system-level interconnect. In Proceedings of the 2004 International Workshop on System Level Interconnect Prediction, Paris, France, 14–15 February 2004. [Google Scholar] [CrossRef]

- Shacham, A.; Bergman, K.; Carloni, L.P. Photonic networks-on-chip for future generations of chip multiprocessors. IEEE Trans. Comput. 2008, 57, 1246–1260. [Google Scholar] [CrossRef]

- Sherwood-Droz, N.; Wang, H.; Chen, L.; Lee, B.G.; Biberman, A.; Bergman, K.; Lipson, M. Optical 4 × 4 hitless silicon router for optical networks-on-chip (NoC). Opt. Express 2008, 16, 15915–15922. [Google Scholar] [CrossRef] [PubMed]

- Xie, Y.Y.; Zhao, W.L.; Xu, W.H.; Huang, Y.X.; Zhang, Z.D. Performance optimization and evaluation for mesh-based optical networks-on-chip. IEEE Photonics J. 2015, 7, 1–12. [Google Scholar] [CrossRef]

- Xie, Y.; Nikdast, M.; Xu, J.; Wu, X.; Zhang, W.; Ye, Y.; Wang, X.; Wang, Z.; Liu, W. Formal worst-case analysis of crosstalk noise in mesh-based optical networks-on-chip. IEEE Trans. Very Large Scale Integr. VLSI Syst. 2012, 21, 1823–1836. [Google Scholar] [CrossRef]

- Gu, H.; Chen, K.; Yang, Y.; Chen, Z.; Zhang, B. MRONoC: A low latency and energy efficient on chip optical interconnect architecture. IEEE Photonics J. 2017, 9, 1–12. [Google Scholar] [CrossRef]

- Xia, F.; Rooks, M.; Sekaric, L.; Vlasov, Y. Ultra-compact high order ring resonator filters using submicron silicon photonic wires for on-chip optical interconnects. Opt. Express 2007, 15, 11934–11941. [Google Scholar] [CrossRef] [PubMed]

- Bogaerts, W.; Dumon, P.; Van Thourhout, D.; Baets, R. Low-loss, low-cross-talk crossings for silicon-on-insulator nanophotonic waveguides. Opt. Lett. 2007, 32, 2801–2803. [Google Scholar] [CrossRef] [PubMed]

- Chen, H.; Poon, A.W. Low-loss multimode-interference-based crossings for silicon wire waveguides. IEEE Photonics Technol. Lett. 2006, 18, 2260–2262. [Google Scholar] [CrossRef]

- Bogaerts, W.; Dumon, P.; Van Thourhout, D.; Baets, R. Compact, low-loss waveguide crossings for high-index-contrast SOI photonic wires. In Proceedings of the Optical Fiber Communication Conference, Anaheim, CA, USA, 25–29 March 2007. [Google Scholar]

- Xie, Y.; Nikdast, M.; Xu, J.; Zhang, W.; Li, Q.; Wu, X.; Ye, Y.; Wang, X.; Liu, W. Crosstalk noise and bit error rate analysis for optical network-on-chip. In Proceedings of the Design Automation Conference, Anaheim, CA, USA, 13–18 June 2010; pp. 657–660. [Google Scholar]

- Ye, Y.; Xu, J.; Wu, X.; Zhang, W.; Liu, W.; Nikdast, M. A torus-based hierarchical optical-electronic network-on-chip for multiprocessor system-on-chip. ACM J. Emerg. Technol. Comput. Syst. 2012, 8, 5. [Google Scholar] [CrossRef]

- Werner, S.; Navaridas, J.; Lujn, M. Amon: An advanced mesh-like optical noc. In Proceedings of the 2015 IEEE 23rd Annual Symposium on High-Performance Interconnects, Santa Clara, CA, USA, 26–28 August 2015; pp. 52–59. [Google Scholar]

- Sahu, P.K.; Chattopadhyay, S. A survey on application mapping strategies for network-on-chip design. J. Syst. Archit. 2013, 59, 60–76. [Google Scholar] [CrossRef]

- Kennedy, J.; Eberhart, R. Particle swarm optimization (PSO). In Proceedings of the IEEE International Conference on Neural Networks, Perth, Australia, 27 November–1 December 1995; pp. 1942–1948. [Google Scholar]

- Eberhart, R.C.; Shi, Y. Comparison between genetic algorithms and particle swarm optimization. In Proceedings of the International Conference on Evolutionary Programming, San Diego, CA, USA, 25–27 March 1998; pp. 611–616. [Google Scholar]

- Shi, Y.; Eberhart, R.C. Parameter selection in particle swarm optimization. In Proceedings of the International Conference on Evolutionary Programming, San Diego, CA, USA, 25–27 March 1998; pp. 591–600. [Google Scholar]

- Eberhart, R.C.; Shi, Y. Comparing inertia weights and constriction factors in particle swarm optimization. In Proceedings of the 2000 Congress on Evolutionary Computation, La Jolla, CA, USA, 16–19 July 2000; pp. 84–88. [Google Scholar]

- Lei, T.; Kumar, S. A two-step genetic algorithm for mapping task graphs to a network on chip architecture. In Proceedings of the Euromicro Symposium on Digital System Design, Belek-Antalya, Turkey, 1–6 September 2003; pp. 180–187. [Google Scholar]

- Wang, J.; Li, Y.; Chai, S.; Peng, Q. Bandwidth-aware application mapping for NoC-based MPSoCs. J. Comput. Inf. Syst. 2011, 7, 152–159. [Google Scholar]

- Shen, W.T.; Chao, C.H.; Lien, Y.K.; Wu, A.Y. A new binomial mapping and optimization algorithm for reduced-complexity mesh-based on-chip network. In Proceedings of the First International Symposium on Networks-on-Chip (NOCS’07), Princeton, NJ, USA, 7–9 May 2007; pp. 317–322. [Google Scholar]

- Tavanpour, M.; Khademzadeh, A.; Janidarmian, M. Chain-Mapping for mesh based Network-on-Chip architecture. IEICE Electron. Express 2009, 6, 1535–1541. [Google Scholar] [CrossRef]

- Fusella, E.; Cilardo, A. Crosstalk-aware mapping for tile-based optical network-on-chip. In Proceedings of the 2015 IEEE 17th International Conference on High Performance Computing and Communications, 2015 IEEE 7th International Symposium on Cyberspace Safety and Security, and 2015 IEEE 12th International Conference on Embedded Software and Systems, New York, NY, USA, 24–26 August 2015; pp. 1139–1142. [Google Scholar]

- Aarts, E.; Korst, J. Simulated Annealing and Boltzmann Machines; Wiley: New York, NY, USA, 1988. [Google Scholar]

- Johnson, D.S.; Aragon, C.R.; McGeoch, L.A.; Schevon, C. Optimization by simulated annealing: An experimental evaluation; part I, graph partitioning. Oper. Res. 1989, 37, 865–892. [Google Scholar] [CrossRef]

- Hwang, C.R. Simulated annealing: Theory and applications. Acta Appl. Math. 1988, 12, 108–111. [Google Scholar]

- Fusella, E.; Cilardo, A. Crosstalk-aware automated mapping for optical networks-on-chip. ACM Trans. Embed. Comput. Syst. 2016, 16, 16. [Google Scholar] [CrossRef]

- Fusella, E.; Cilardo, A. PhoNoCMap: An application mapping tool for photonic networks-on-chip. In Proceedings of the 2016 Conference on Design, Automation & Test in Europe, Dresden, Germany, 14–18 March 2016; pp. 289–292. [Google Scholar]

- Feng, K.; Ye, Y.; Xu, J. A formal study on topology and floorplan characteristics of mesh and torus-based optical networks-on-chip. Microprocess. Microsyst. 2013, 37, 941–952. [Google Scholar] [CrossRef]

- Fusella, E.; Cilardo, A. Minimizing power loss in optical networks-on-chip through application-specific mapping. Microprocess. Microsyst. 2016, 43, 4–13. [Google Scholar] [CrossRef]

| Iteration Times | 1000 |

| Population Size | 100 |

| Routing Mode | XY order routing |

| Chip Size | 400 mm2 |

| Modulation Rate | 10 Gb/s |

| Laser Source Efficiency | 30% |

| Photodetector Sensitivity | −14.2 dBm |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Shi, X.; Wu, N.; Ge, F.; Zhou, F.; Yahya, M.R. Optimizing Crosstalk in Optical NoC through Heuristic Fusion Mapping. Electronics 2020, 9, 1006. https://doi.org/10.3390/electronics9061006

Shi X, Wu N, Ge F, Zhou F, Yahya MR. Optimizing Crosstalk in Optical NoC through Heuristic Fusion Mapping. Electronics. 2020; 9(6):1006. https://doi.org/10.3390/electronics9061006

Chicago/Turabian StyleShi, Xinhao, Ning Wu, Fen Ge, Fang Zhou, and Muhammad Rehan Yahya. 2020. "Optimizing Crosstalk in Optical NoC through Heuristic Fusion Mapping" Electronics 9, no. 6: 1006. https://doi.org/10.3390/electronics9061006

APA StyleShi, X., Wu, N., Ge, F., Zhou, F., & Yahya, M. R. (2020). Optimizing Crosstalk in Optical NoC through Heuristic Fusion Mapping. Electronics, 9(6), 1006. https://doi.org/10.3390/electronics9061006