Characterization of Single Event Cell Upsets in a Radiation Hardened SRAM in a 40 nm Bulk CMOS Technology

Abstract

:1. Introduction

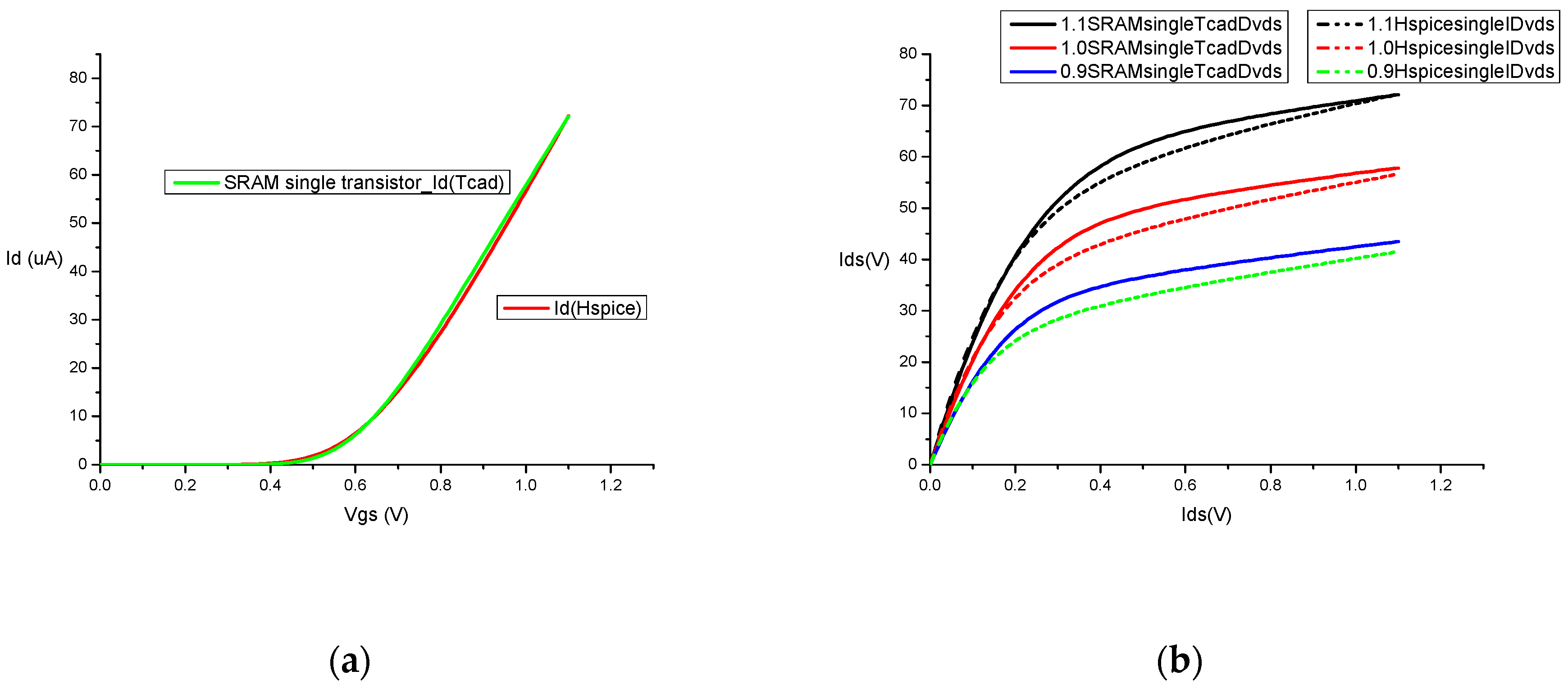

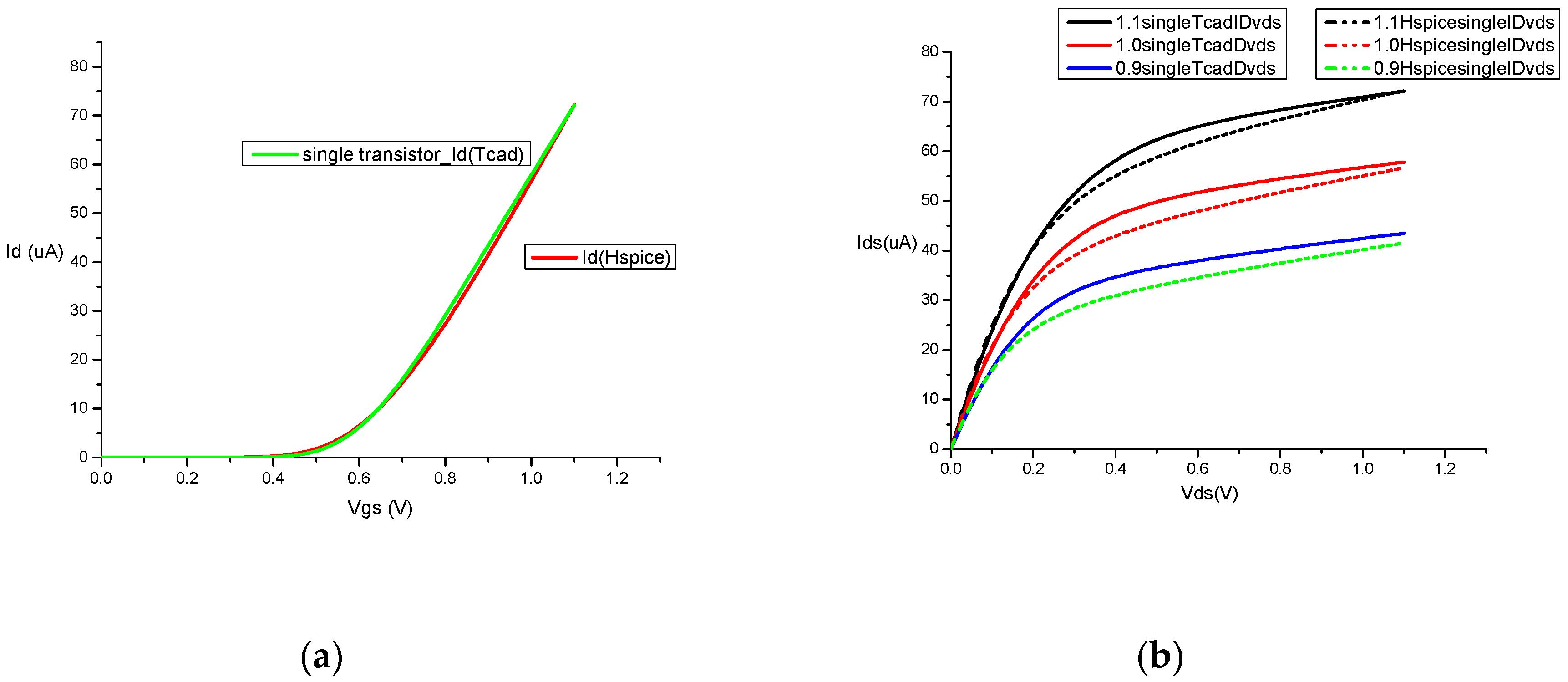

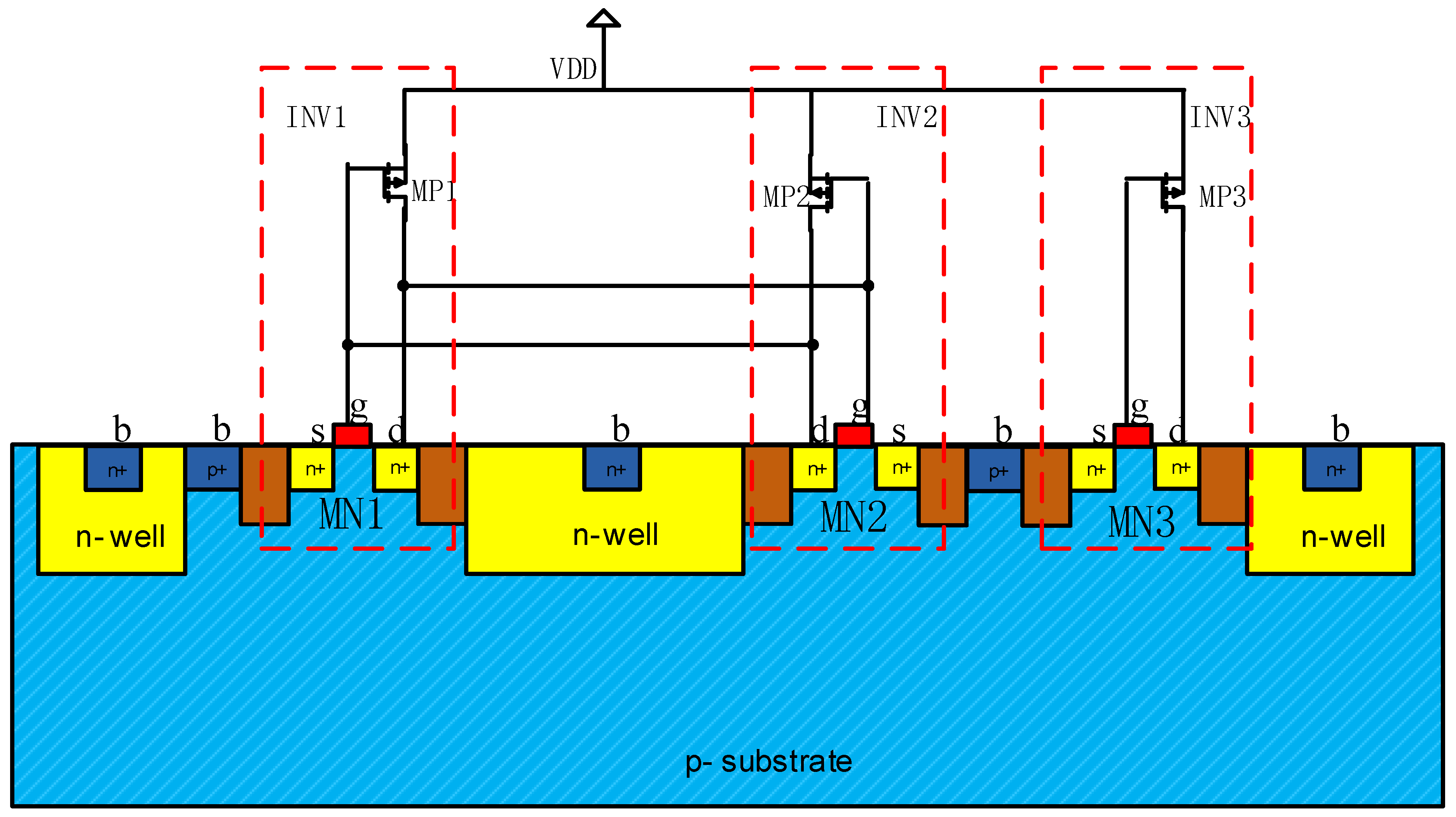

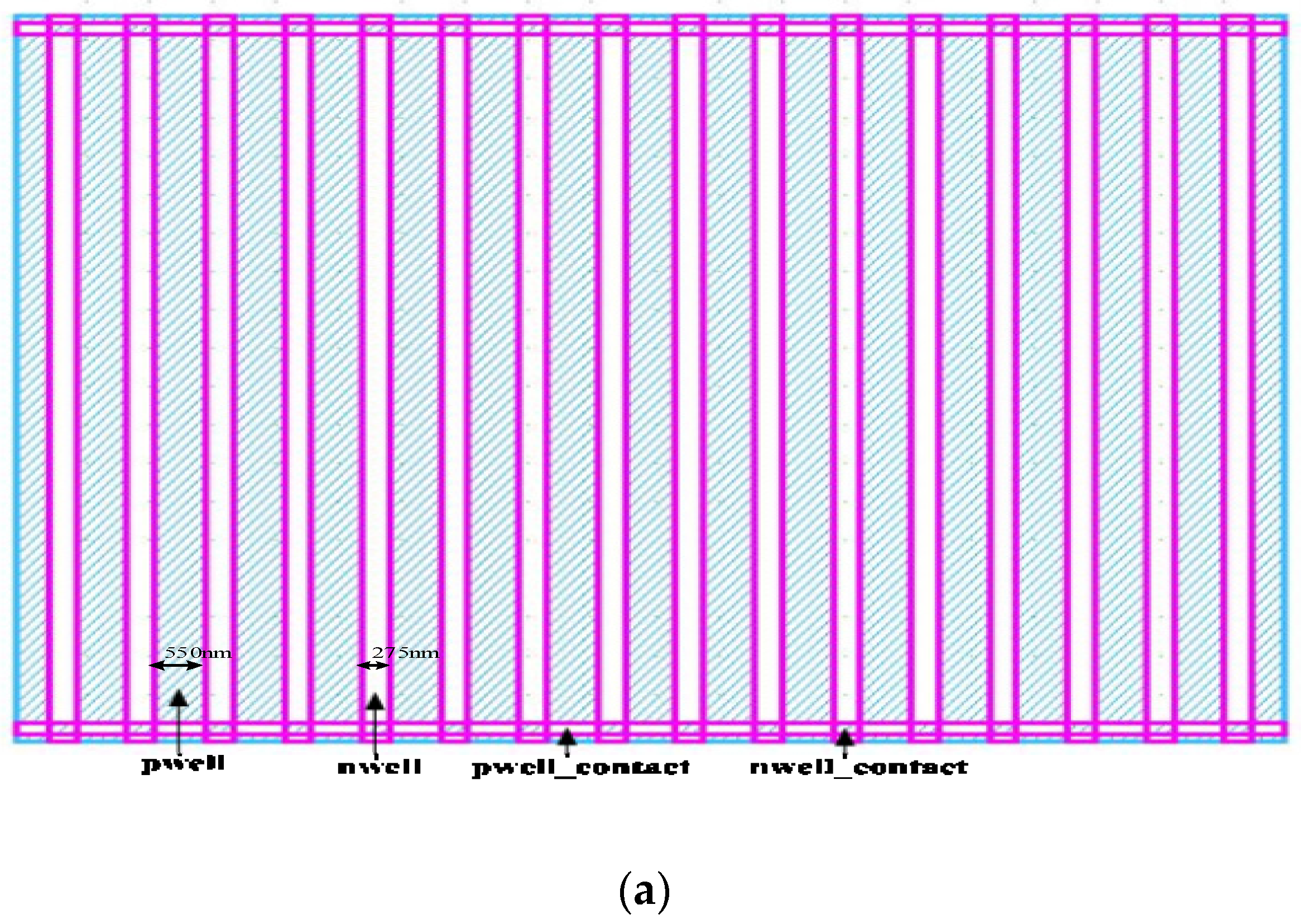

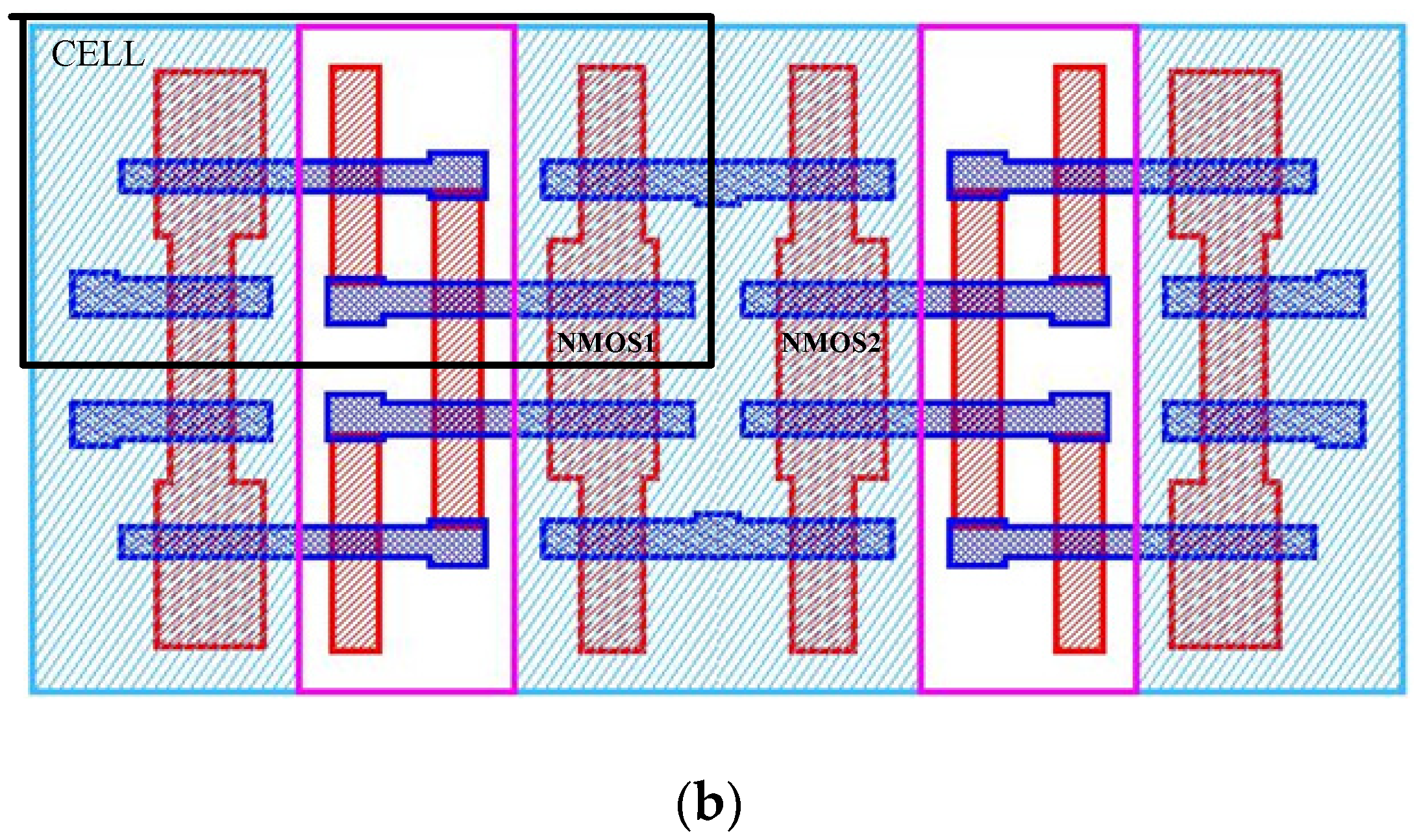

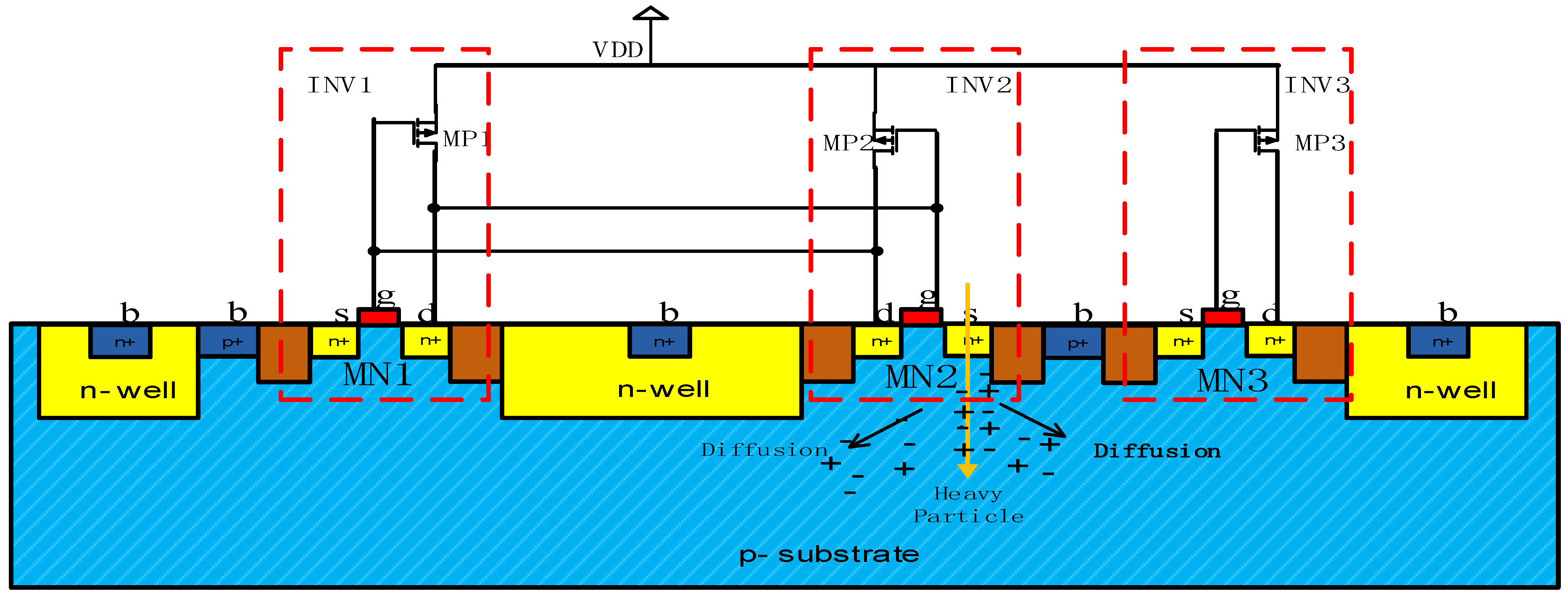

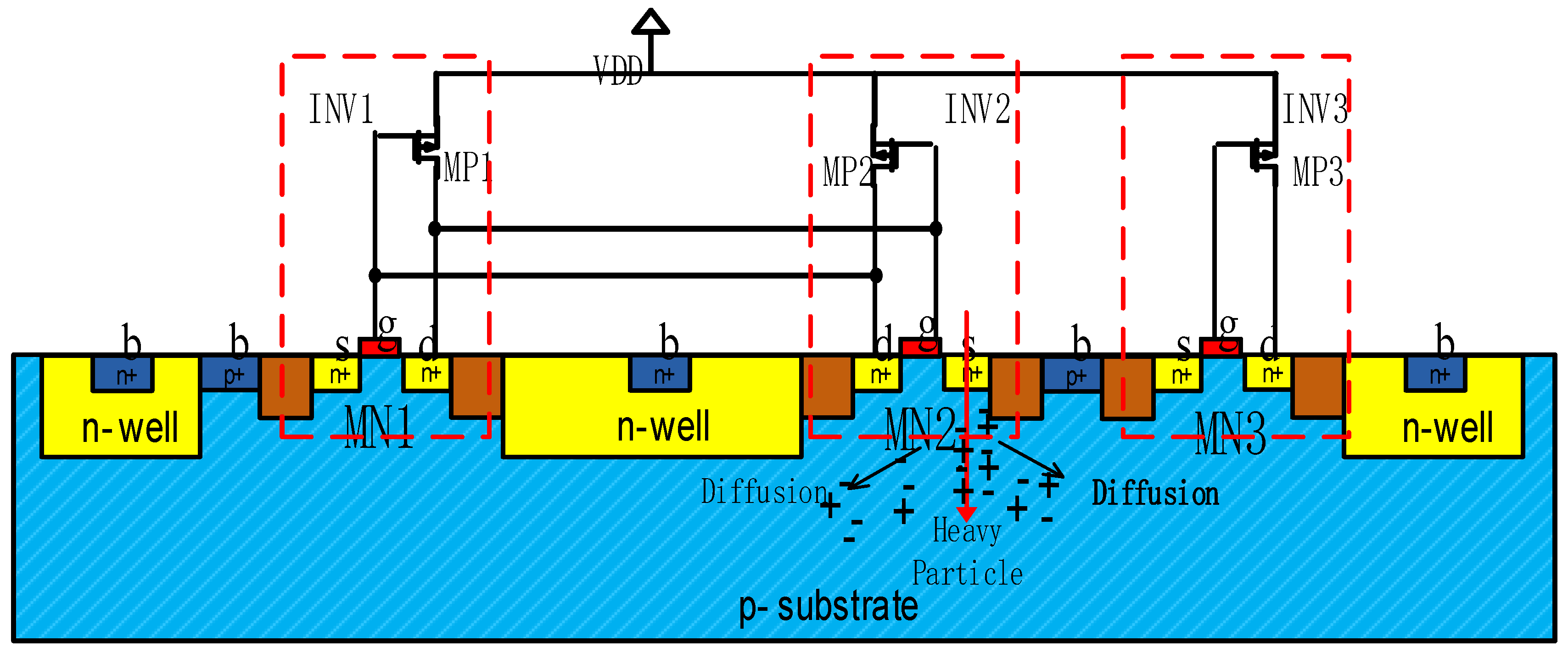

2. Device Model and I-V Curve Calibration

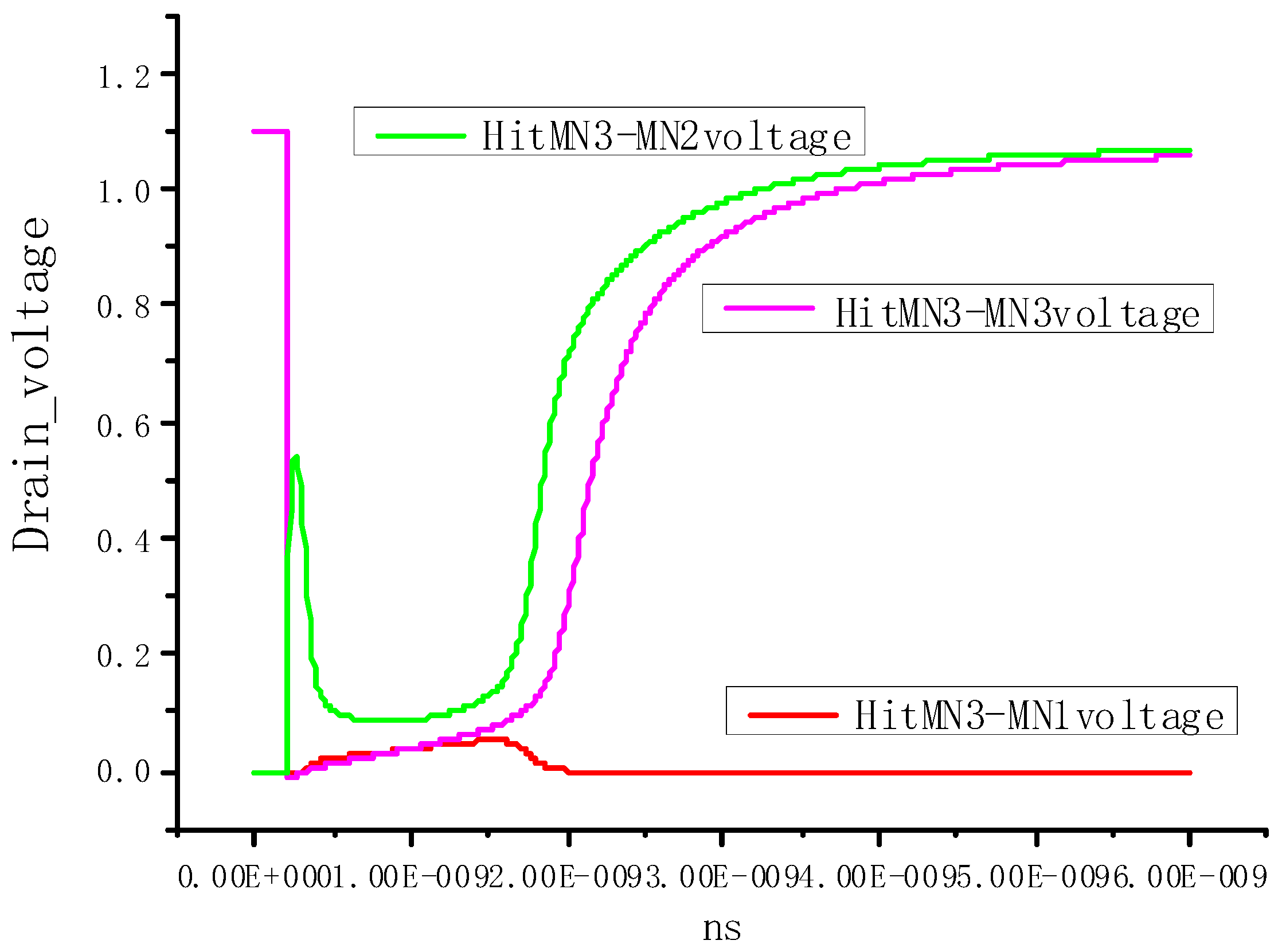

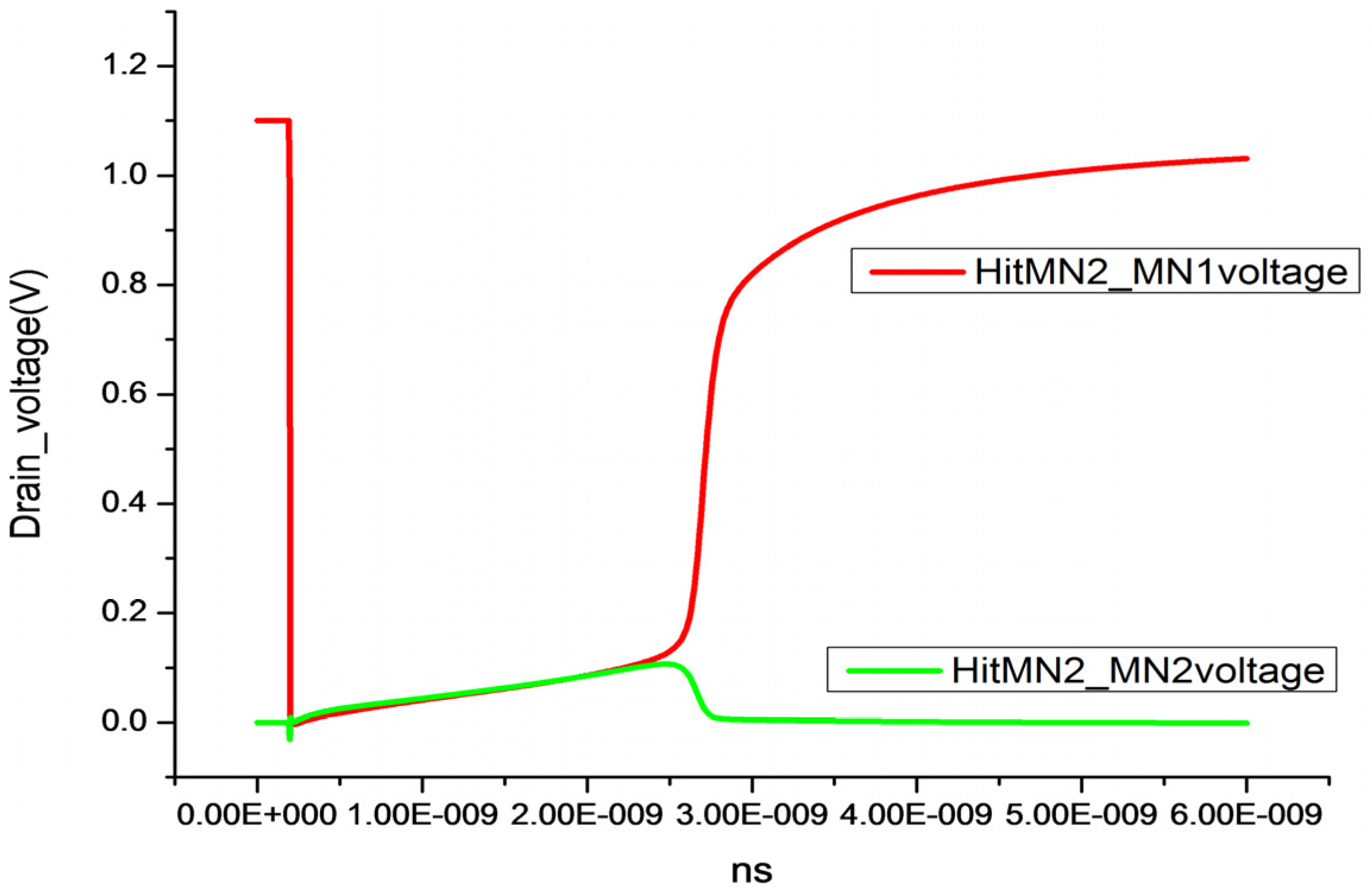

3. Emulation Voltage Waveform and Experimental Data

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Jan, M.; Chandrakasan, R.A.; Nikolic, B. Designing Memory and Array Structure. In Digital Integrated Circuits: A Design Perspective, 2nd ed.; Pearson Eeducation, Inc.: Upper Saddle River, NJ, USA, 2017; p. 625. [Google Scholar]

- Jeon, S.H.; Lee, S.; Baeg, S.; Kim, I.; Kim, G. Novel Error Detection Scheme With the Harmonious Use of Parity Codes, Well-Taps, and Interleaving Distance. IEEE Trans. Nucl. Sci. 2014, 61, 2711–2717. [Google Scholar] [CrossRef]

- Jing, G. Single Event Upsets Harden by Design Technology Research of Static Random Access Memory. Ph.D. Thesis, Harbin Institute of Technology, Harbin, China, 1 May 2015. [Google Scholar]

- Black, J.D.; Dodd, P.E.; Warren, K.M. Physics of Multiple-Node Charge Collection and Impacts on Single-Event Characterization and Soft Error Rate Prediction. IEEE Trans. Nucl. Sci. 2013, 60, 1836–1851. [Google Scholar] [CrossRef]

- Chen, J.; Liang, B.; Chi, Y. Experimental characterization of the bipolar effect on P-hit single-event transients in 65 nm twin-well and triple-well CMOS technologies. Sci. China Ser. E Technol. Sci. 2016, 59, 488–493. [Google Scholar] [CrossRef]

- Zhang, J.; Chen, J.; Huang, P.; Li, S.; Fang, L. The Effect of Deep N+ Well on Single-Event Transient in 65 nm Triple-Well NMOSFET. Symmetry 2019, 11, 154. [Google Scholar] [CrossRef] [Green Version]

- Zhang, J.; Fang, L.; Chen, J.; Hou, S.; Tong, X. Single Event Transient Study of pMOS Transistors in 65 nm Technology With and Without a Deep n+ Well Under Particle Striking. IEEE Access 2019, 7, 149255–149261. [Google Scholar] [CrossRef]

- Jagannathan, S.; Gadlage, M.J.; Bhuva, B.L.; Schrimpf, R.D.; Narasimham, B.; Chetia, J.; Ahlbin, J.R.; Massengill, L.W. Independent Measurement of SET Pulse Widths From N-Hits and P-Hits in 65-nm CMOS. IEEE Trans. Nucl. Sci. 2010, 57, 3386–3391. [Google Scholar] [CrossRef]

- Roy, T.; Witulski, A.F.; Schrimpf, R.D.; Alles, M.L.; Massengill, L.W. Single Event Mechanisms in 90 nm Triple-Well CMOS Devices. IEEE Trans. Nucl. Sci. 2008, 55, 2948–2956. [Google Scholar] [CrossRef] [Green Version]

- Chatterjee, I.; Narasimham, B.; Mahatme, N.N.; Bhuva, B.L.; Schrimpf, R.D.; Wang, J.K.; Bartz, B.; Pitta, E.; Buer, M. Single-Event Charge Collection and Upset in 40-nm Dual- and Triple-Well Bulk CMOS SRAMs. IEEE Trans. Nucl. Sci. 2011, 58, 2761–2767. [Google Scholar] [CrossRef]

- Huang, P.; Chen, S.; Chen, J.; Liu, B. Novel N-hit single event transient mitigation technique via open guard transistor in 65nm bulk CMOS process. Sci. China Ser. E Technol. Sci. 2012, 56, 271–279. [Google Scholar] [CrossRef]

- Chen, J.; Chen, S.; Liang, B.; Liu, F. Single event transient pulse attenuation effect in three-transistor inverter chain. Sci. China Ser. E Technol. Sci. 2012, 55, 867–871. [Google Scholar] [CrossRef]

- Huang, P.; Chen, S.; Liang, Z.; Chen, J.; Hu, C.; He, Y. Mirror image: Newfangled cell-level layout technique for single-event transient mitigation. Chin. Sci. Bull. 2014, 59, 2850–2858. [Google Scholar] [CrossRef]

- Wang, H.-B.; Bi, J.-S.; Li, M.-L.; Chen, L.; Liu, R.; Li, Y.-Q.; He, A.-L.; Guo, G. An Area Efficient SEU-Tolerant Latch Design. IEEE Trans. Nucl. Sci. 2014, 61, 3660–3666. [Google Scholar] [CrossRef]

- Zhang, K.; Kobayashi, K.; Kobayashi, K. Contributions of charge sharing and bipolar effects to cause or suppress MCUs on redundant latches. In Proceedings of the 2013 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 14–18 April 2013; p. 997. [Google Scholar]

- Luo, Y.H.; Zhang, F.Q.; Guo, H.X.; Zhou, H.; Zheng, L.S.; Ji, D.M.; Shen, C.; Gong, D.; Hajdas, W. Single event cluster multi-bit upsets due to localized latch-up in a90 nm COTS SRAM containing SEL mitigation design. IEEE Trans. Nucl. Sci. 2014, 61, 1918–1923. [Google Scholar]

- Chatterjee, I.; Narasimham, B.; Mahatme, N.N.; Bhuva, B.L.; Reed, R.A.; Schrimpf, R.D.; Wang, J.K.; Vedula, N.; Bartz, B.; Monzel, C. Impact of Technology Scaling on SRAM Soft Error Rates. IEEE Trans. Nucl. Sci. 2014, 61, 3512–3518. [Google Scholar] [CrossRef]

- Georgakos, G.; Huber, P.; Ostermayr, M.; Amirante, E.; Ruckerbauer, F. Investigation of Increased Multi-Bit Failure Rate Due to Neutron Induced SEU in Advanced Embedded SRAMs. In Proceedings of the 2007 IEEE Symposium on VLSI Circuits, Kyoto, Japan, 14–16 June 2007; pp. 80–81. [Google Scholar]

- Chen, H.; Chen, J.; Yao, L. Characterization of single-event multiple cell upsets in a custom SRAM in a 65 nm triple-well CMOS technology. Sci. China Ser. E: Technol. Sci. 2015, 58, 1726–1730. [Google Scholar] [CrossRef]

- Ibe, E.; Chung, S.S.; Wen, S.; Yamaguchi, H.; Yahagi, Y.; Kameyama, H.; Yamamoto, S.; Akioka, T. Spreading Diversity in Multi-cell Neutron-Induced Upsets with Device Scaling. In Proceedings of the IEEE Custom Integrated Circuits Conference, San Jose, CA, USA, 10–13 September 2006; pp. 437–444. [Google Scholar]

- Furuta, J.; Kobayashi, K.; Onodera, H.; Kobayashi, K. Impact of cell distance and well-contact density on neutron-induced Multiple Cell Upsets. In Proceedings of the 2013 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 14–18 April 2013; pp. 6C.3.1–6C.3.4. [Google Scholar]

- Zhangd, K.; Furuta, J.; Kobayashi, K.; Onodera, H.; Zhang, K. Dependence of Cell Distance and Well-Contact Density on MCU Rates by Device Simulations and Neutron Experiments in a 65-nm Bulk Process. IEEE Trans. Nucl. Sci. 2014, 61, 1583–1589. [Google Scholar] [CrossRef]

- Song, Y.; Vu, K.; Cable, J.; Witteles, A.; Kolasinski, W.; Koga, R.; Elder, J.; Osborn, J.; Martin, R.; Ghoniem, N. Experimental and analytical investigation of single event, multiple bit upsets in poly-silicon load, 64 K*1 NMOS SRAMs. IEEE Trans. Nucl. Sci. 1988, 35, 1673–1677. [Google Scholar] [CrossRef]

- Black, J.D.; Ii, D.R.B.; Robinson, W.H.; Fleetwood, D.M.; Schrimpf, R.D.; Reed, R.A.; Black, D.A.; Warren, K.M.; Tipton, A.D.; Dodd, P.E.; et al. Characterizing SRAM Single Event Upset in Terms of Single and Multiple Node Charge Collection. IEEE Trans. Nucl. Sci. 2008, 55, 2943–2947. [Google Scholar] [CrossRef]

- Gasiot, G.; Roche, P.; Flatresse, P. Comparison of multiple cell upset response of BULK and SOI 130NM technologies in the terrestrial environment. In Proceedings of the 2008 IEEE International Reliability Physics Symposium, Phoenix, AZ, USA, 27 April–1 January 2008; pp. 192–194. [Google Scholar]

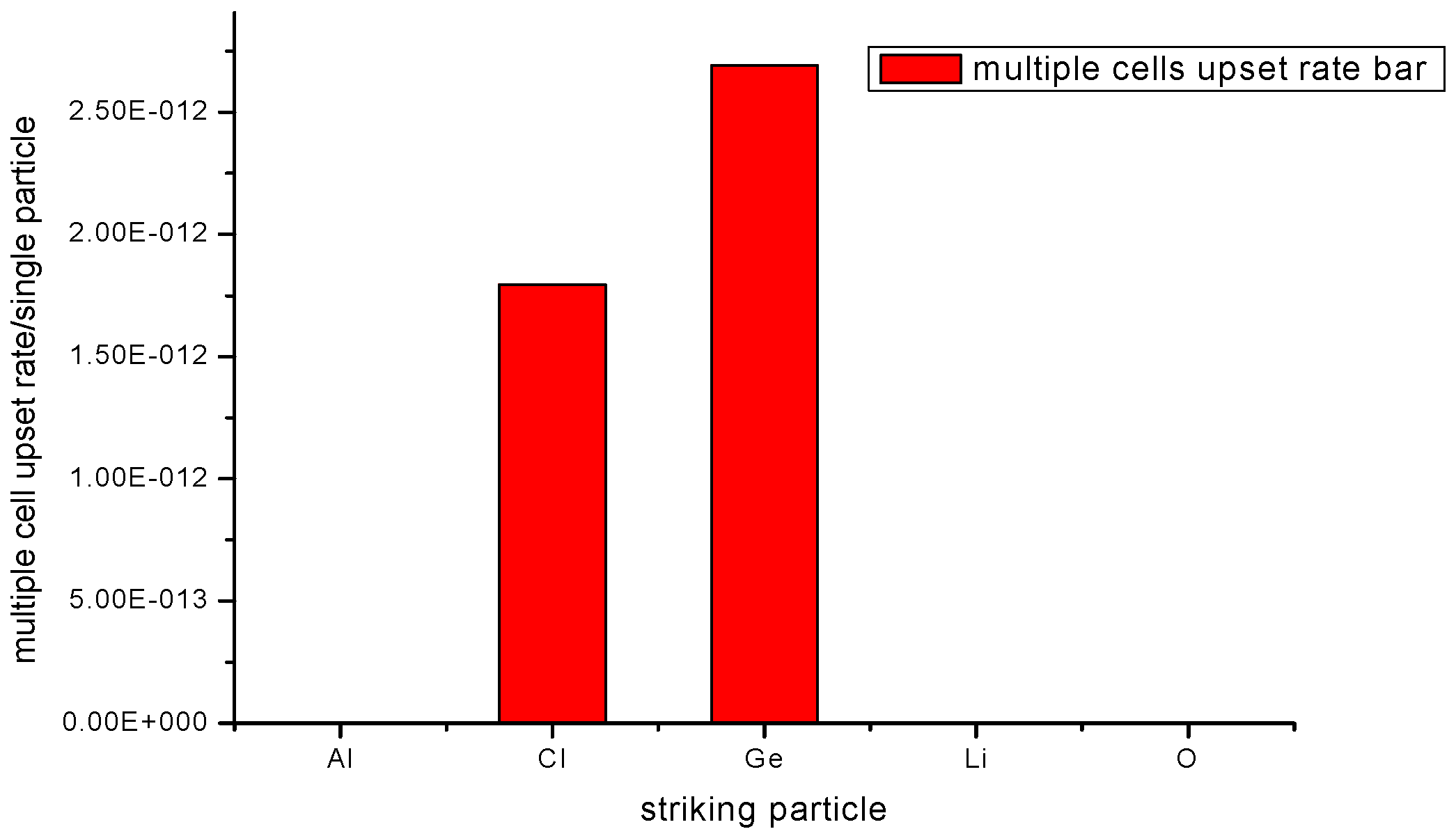

| Particle | Energy (MeV) | LET (Mev/mg/cm2) | Range (μm) | SCU (cm2/Particle) | MCU (cm2/Particle) |

|---|---|---|---|---|---|

| Ge | 210 | 37.3 | 30.5 | 8.97617E-7 | 2.69265E-12 |

| Cl | 160 | 13.1 | 46.0 | 5.04544E-7 | 1.7951E-12 |

| Al | 120 | 8.6 | 50.0 | 1.85389E-7 | 0 |

| O | 100 | 3.1 | 95.2 | 1.39709E-7 | 0 |

| Li | 44 | 0.5 | 249.9 | 2.14582E-8 | 0 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yang, G.; Yu, J.; Zhang, J.; Liu, X.; Chen, Q. Characterization of Single Event Cell Upsets in a Radiation Hardened SRAM in a 40 nm Bulk CMOS Technology. Electronics 2020, 9, 927. https://doi.org/10.3390/electronics9060927

Yang G, Yu J, Zhang J, Liu X, Chen Q. Characterization of Single Event Cell Upsets in a Radiation Hardened SRAM in a 40 nm Bulk CMOS Technology. Electronics. 2020; 9(6):927. https://doi.org/10.3390/electronics9060927

Chicago/Turabian StyleYang, Guoqing, Junting Yu, Jincheng Zhang, Xiangyuan Liu, and Qiang Chen. 2020. "Characterization of Single Event Cell Upsets in a Radiation Hardened SRAM in a 40 nm Bulk CMOS Technology" Electronics 9, no. 6: 927. https://doi.org/10.3390/electronics9060927