The Improvement Switching Technique for High Step-Up DC-DC Boost Converter

Abstract

1. Introduction

2. The Improvement Switching Technique

2.1. Principles

2.2. Power Loss Analysis

2.2.1. Power Loss in Diode:

2.2.2. Power Loss in Inductor:

2.2.3. Power Loss in the Switch:

2.2.4. Power Loss in the Output Capacitor

2.2.5. Losses in the Level Capacitor:

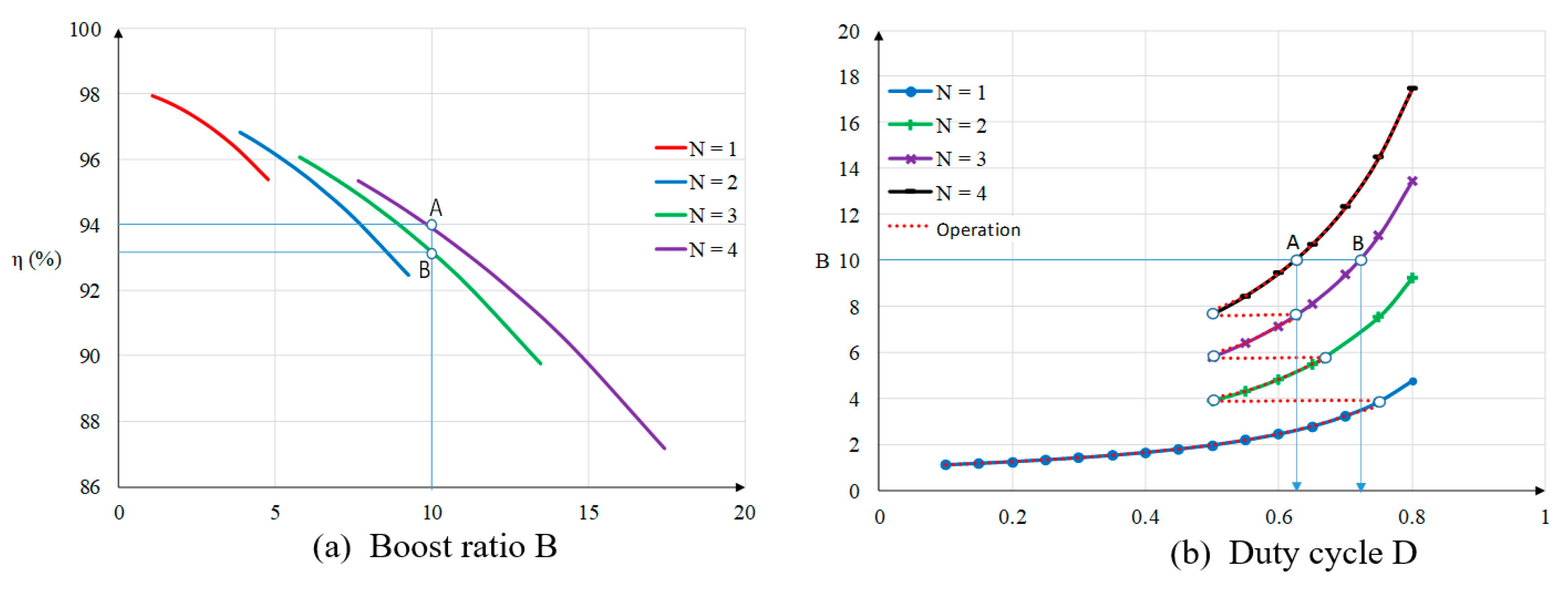

2.3. Control Technology to Minimize Power Loss

3. Simulation and Experimental Results

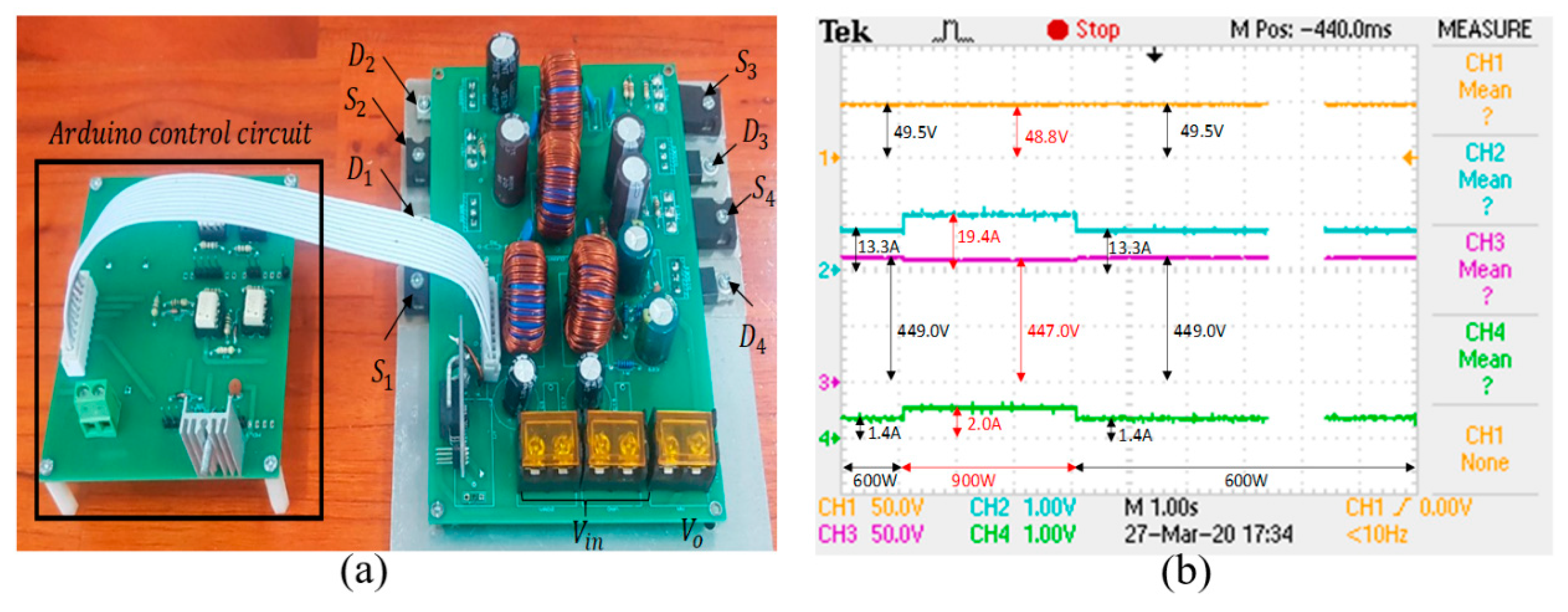

3.1. Experimental Model and Results

3.2. Analysis of the Results of Tests 1 and 2 with the Load of 500 W

3.3. Control the Proposed Converter as in the Flowchart in Figure 11

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Shrud, M.A.; Kharaz, A.; Bousbaine, A.; Faris, A. Development of Automotive DC/DC Converter based Centralised Architecture. Elev. Eur. Conf. Power Energy Syst. 2012, 179–185. [Google Scholar] [CrossRef]

- Schittler, A.C.; Pappis, D.; Campos, A.; Dalla Costa, M.A.; Alonso, J.M. Interleaved Buck Converter Applied to High-Power HID Lamps Supply: Design, Modeling and Control. IEEE Trans. Ind. Appl. 2013, 49, 1844–1853. [Google Scholar] [CrossRef]

- Zhang, Y.; Liu, H.; Li, J.; Sumner, M.; Xia, C. DC–DC Boost Converter with a Wide Input Range and High Voltage Gain for Fuel Cell Vehicles. IEEE Trans. Power Electron. 2019, 34, 4100–4111. [Google Scholar] [CrossRef]

- Aamir, M.; Kalwar, K.A.; Mekhilef, S. Review: Uninterruptible Power Supply (UPS) system. Renew. Sustain. Energy Rev. 2016, 58, 1395–1410. [Google Scholar] [CrossRef]

- Kudithi, N.; Somkun, S. Single Phase Power Generation System from Fuel Cell. Int. J. Power Electron. Drive. 2018, 9, 1676–1684. [Google Scholar] [CrossRef]

- Bi, H.; Wang, P.; Che, Y. A Capacitor Clamped H-Type Boost DC-DC Converter with Wide Voltage-Gain Range for Fuel Cell Vehicles. IEEE Trans. Veh. Technol. 2019, 68, 276–290. [Google Scholar] [CrossRef]

- Chakraborty, S.; Vu, H.N.; Hasan, M.M.; Tran, D.D.; Baghdadi, M.E.; Hegazy, O. DC-DC Converter Topologies for Electric Vehicles, Plug-in Hybrid Electric Vehicles and Fast Charging Stations: State of the Art and Future Trends. Energies 2019, 12, 1569. [Google Scholar] [CrossRef]

- Kardan, F.; Alizadeh, R.; Banaei, M.R. A New Three Input DC/DC Converter for Hybrid PV/FC/Battery Applications. IEEE J. Emerg. Sel. Top. Power Electron. 2017, 5, 1771–1778. [Google Scholar] [CrossRef]

- Torkan, A.; Ehsani, M. A Novel Nonisolated Z-Source DC–DC Converter for Photovoltaic Applications. IEEE Trans. Ind. Appl. 2018, 54, 4574–4583. [Google Scholar] [CrossRef]

- Forouzesh, M.; Siwakoti, Y.P.; Gorji, S.A.; Blaabjerg, F.; Lehman, B. Step-Up DC–DC Converters: A Comprehensive Review of Voltage-Boosting Techniques, Topologies, and Applications. IEEE Trans. Power Electron. 2017, 32, 9143–9178. [Google Scholar] [CrossRef]

- Tran, V.T.; Nguyen, M.K.; Choi, Y.O.; Cho, G.B. Switched-Capacitor-Based High Boost DC-DC Converter. Energies 2018, 11, 987. [Google Scholar] [CrossRef]

- Alassi, A.; Al-Aswad, A.; Gastli, A.; Brahim, L.B.; Massoud, A. Assessment of Isolated and Non-Isolated DC-DC Converters for Medium-Voltage PV Applications. In Proceedings of the 2017 9th IEEE-GCC Conference and Exhibition (GCCCE), Manama, Bahrain, 8–11 May 2017; pp. 1–6. [Google Scholar]

- Fu, J.; Zhang, B.; Qiu, D.; Xiao, W. A novel single-switch cascaded DC-DC converter of Boost and Buck-boost converters. In Proceedings of the 2014 16th European Conference on Power Electronics and Applications, Lappeenranta, Finland, 26–28 August 2014; pp. 1–9. [Google Scholar]

- Tofoli, F.L.; de Castro Pereira, D.; de Paula, W.J.; Júnior, D.D.S.O. Survey on non-isolated high-voltage step-up dc–dc topologies based on the boost converter. IET Power Electron. 2015, 8, 2044–2057. [Google Scholar] [CrossRef]

- Hu, X.; Gong, C. A High Gain Input-Parallel Output-Series DC/DC Converter with Dual Coupled Inductors. IEEE Trans. Power Electron. 2015, 30, 1306–1317. [Google Scholar] [CrossRef]

- Zhou, L.W.; Zhu, B.X.; Luo, Q.M.; Chen, S. Interleaved non-isolated high step-up DC/DC converter based on the diode-capacitor multiplier. IET Power Electron. 2014, 7, 390–397. [Google Scholar] [CrossRef]

- Leardpan, P.; Singthong, P. Voltage-Lift Switched Inductor DC/DC Multilevel Boost Converter. Przegląd Elektrotechniczny 2015, 91, 127–130. [Google Scholar]

- Mojtaba, F.; Yanfeng, S.; Keyvan, Y.; Yam, P.S.; Frede, B. High-Efficiency High Step-Up DC-DC Converter with Dual Coupled Inductors for Grid-Connected Photovoltaic Systems. IEEE Trans. Power Electron. 2018, 33, 5967–5982. [Google Scholar]

- Lakkas, B.G. MOSFET power losses and how they affect power-supply efficiency. Analog. Appl. J. 2016, 10, 22–26. [Google Scholar]

- Nguyen, M.; Duong, T.; Lim, Y. Switched-Capacitor-Based Dual-Switch High-Boost DC–DC Converter. IEEE Trans. Power Electron. 2018, 33, 4181–4189. [Google Scholar] [CrossRef]

- Suh, J.D.; Yun, Y.H.; Kong, B.S. High-Efficiency DC-DC Converter with Charge-Recycling Gate-Voltage Swing Control. Energies 2019, 12, 899. [Google Scholar] [CrossRef]

- Liu, D.; Deng, F.; Gong, Z.; Chen, Z. Input-Parallel Output-Parallel Three-Level DC/DC Converters with Interleaving Control Strategy for Minimizing and Balancing Capacitor Ripple Currents. IEEE J. Emerg. Sel. Top. Power Electron. 2017, 5, 1122–1132. [Google Scholar] [CrossRef]

| No. | Configuration | Switches | Capacitors | Diodes | Boost |

|---|---|---|---|---|---|

| 1 | interleaved input and coupled inductor | 2 | 4 | 4 | |

| 2 | interleaved input and multiplier cell | 2 | 5 | 5 | |

| 3 | VLC input and multiplier cell | 1 | 4 | 5 |

| Mode | 1 | 2 | 3 | 4 |

|---|---|---|---|---|

| PWM signals | S1, S2, S3, S4 | S1, S2, S3 | S1, S2 | S1 |

| Turn off switch | None | S4 | S3 to S4 | S2 to S4 |

| Stage | Switch on | Switch off | Time | Result |

|---|---|---|---|---|

| 1 | S1, S2, S3, S4 | D1, D2, D3, D4 | t1--t2 | All inductors store energy. Capacitor C4 discharges to the load |

| 2 | S2, S4, D1, D3 | S1, S3, D2, D4 | t2--t3 | Capacitors C1 and C3 charged, capacitor C2 discharged Capacitor C4 discharges to the load |

| 3 | S1, S3, D2, D4 | S2, S4, D1, D3 | t3--t4 | Capacitors C2 and C4 charged, capacitors C1 and C3 discharged |

| B | 1.1 ≤ B ≤ 4.0 | 4.0 < B ≤ 6.0 | 6.0 < B ≤ 7.9 | 7.9 < B ≤ 20 |

|---|---|---|---|---|

| Nset | 1 | 2 | 3 | 4 |

| D(N) | 0.1 ≤ D(1)< 0.75 | 0.5≤ D(2) < 0.67 | 0.5≤ D(3) < 0.62 | 0.5 ≤ D(4) ≤0.8 |

| Dset | 0.55 | 0.55 | 0.55 | 0.55 |

| Dmax | 0.75 | 0.67 | 0.62 | 0.8 |

| Elements | Type and Parameter |

|---|---|

| FET | FQP38N30 (300 V, 38 A, RS = 0.07) |

| Diode | MUR1640CT, (400 V, 16 A, VF = 0.6 V, RD = 0.08 Ω) |

| Capacitor | 2 × 22 µF, RC = 0.2 Ω |

| Inductor | L = 180 µH, RL = 0.15 Ω |

| Po (W) | Parameters | Value | Unit | Efficiency |

|---|---|---|---|---|

| 600 | Vin | 49.5 | V | 95.5% |

| Iin | 13.3 | A | ||

| Pin | 658.35 | W | ||

| Vo | 449.0 | V | ||

| Io | 1.4 | A | ||

| Po | 628.6 | W | ||

| 900 | Vin | 48.8 | V | 94.4% |

| Iin | 19.4 | A | ||

| Pin | 946.72 | W | ||

| Vo | 447 | V | ||

| Io | 2.0 | A | ||

| Po | 894 | W |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Truong, V.-A.; Luong, X.-T.; Nguyen, P.-T.; Quach, T.-H. The Improvement Switching Technique for High Step-Up DC-DC Boost Converter. Electronics 2020, 9, 981. https://doi.org/10.3390/electronics9060981

Truong V-A, Luong X-T, Nguyen P-T, Quach T-H. The Improvement Switching Technique for High Step-Up DC-DC Boost Converter. Electronics. 2020; 9(6):981. https://doi.org/10.3390/electronics9060981

Chicago/Turabian StyleTruong, Viet-Anh, Xuan-Truong Luong, Phan-Thanh Nguyen, and Thanh-Hai Quach. 2020. "The Improvement Switching Technique for High Step-Up DC-DC Boost Converter" Electronics 9, no. 6: 981. https://doi.org/10.3390/electronics9060981

APA StyleTruong, V.-A., Luong, X.-T., Nguyen, P.-T., & Quach, T.-H. (2020). The Improvement Switching Technique for High Step-Up DC-DC Boost Converter. Electronics, 9(6), 981. https://doi.org/10.3390/electronics9060981