Switch Open-Fault Detection for a Three-Phase Hybrid Active Neutral-Point-Clamped Rectifier

Abstract

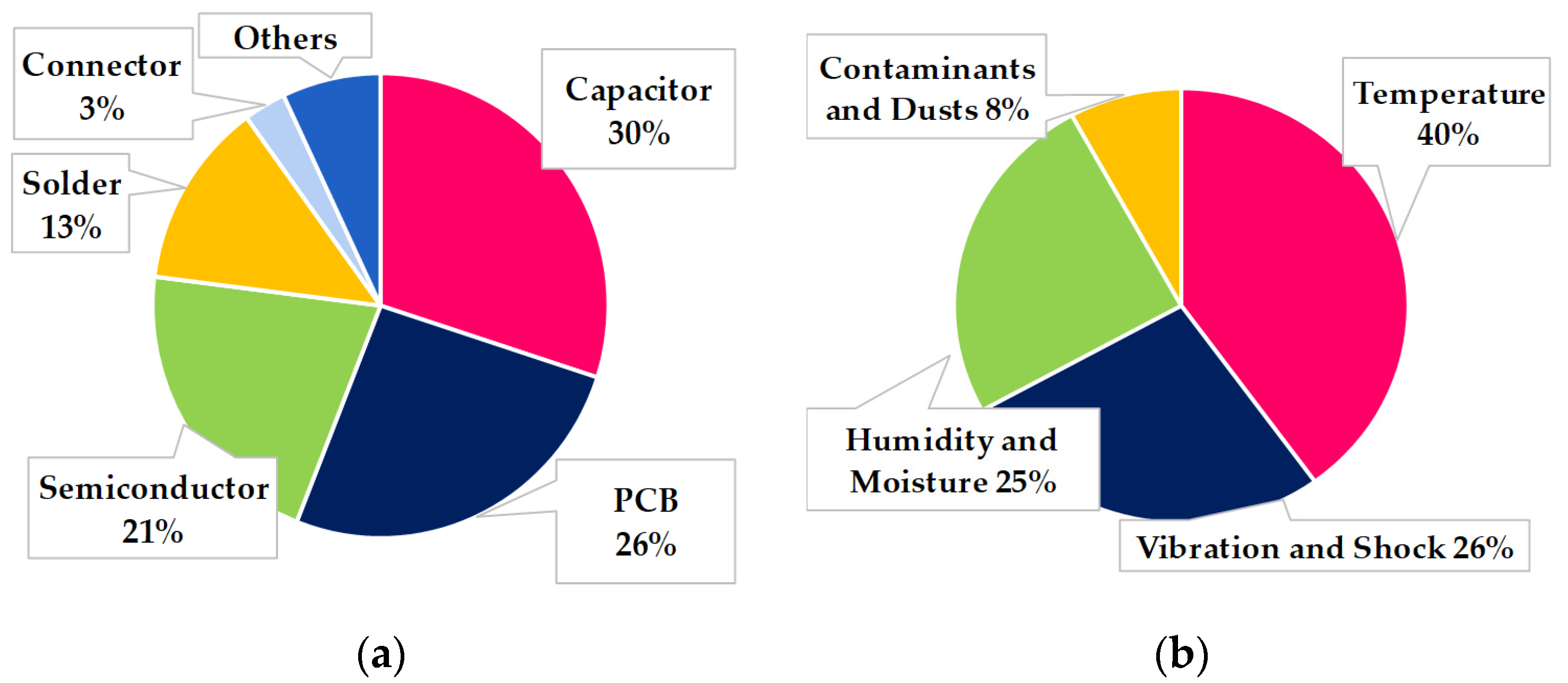

1. Introduction

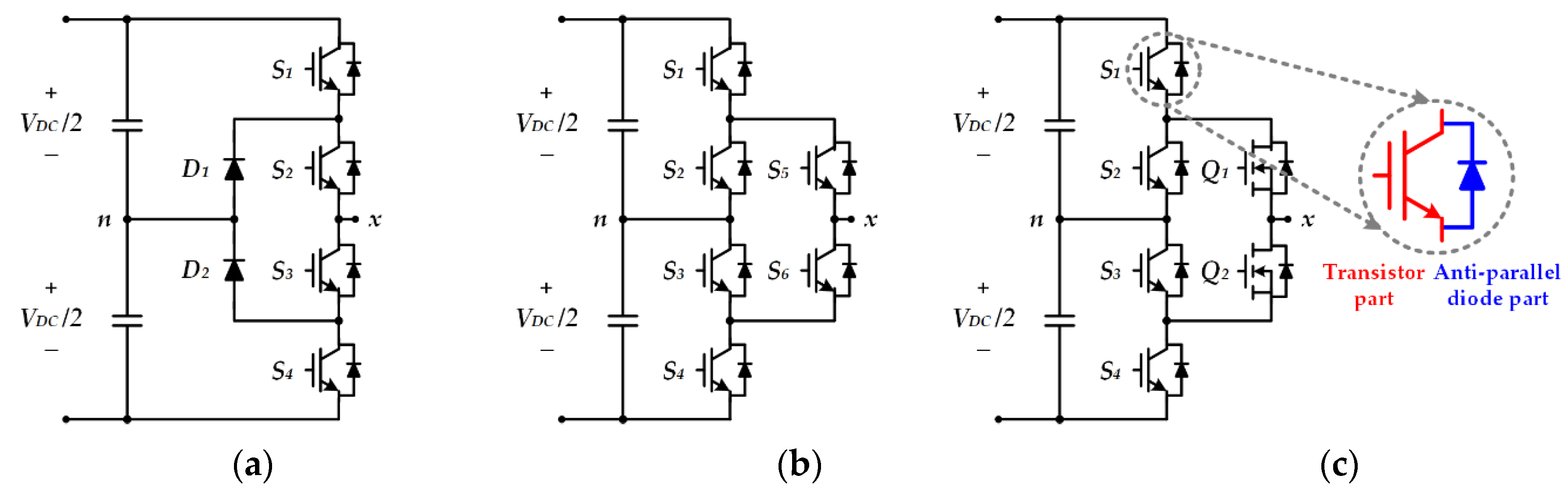

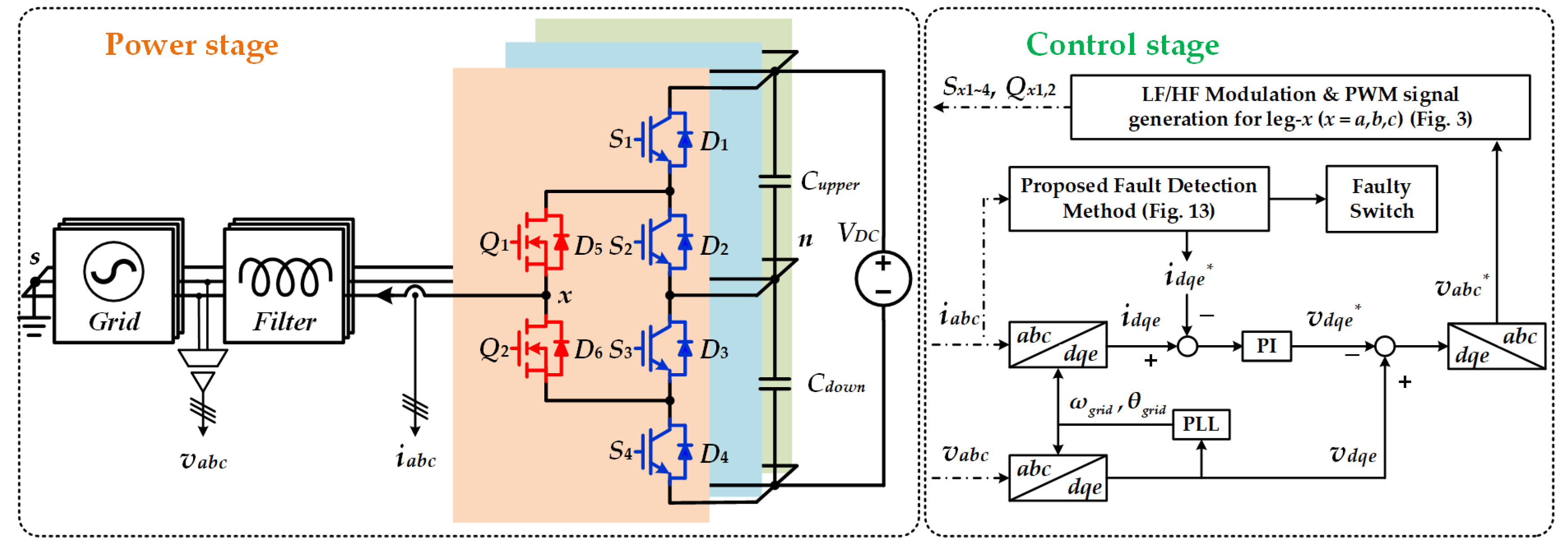

2. HANPC Rectifier Comprising Si and SiC Switches

2.1. Basic Circuit Topology

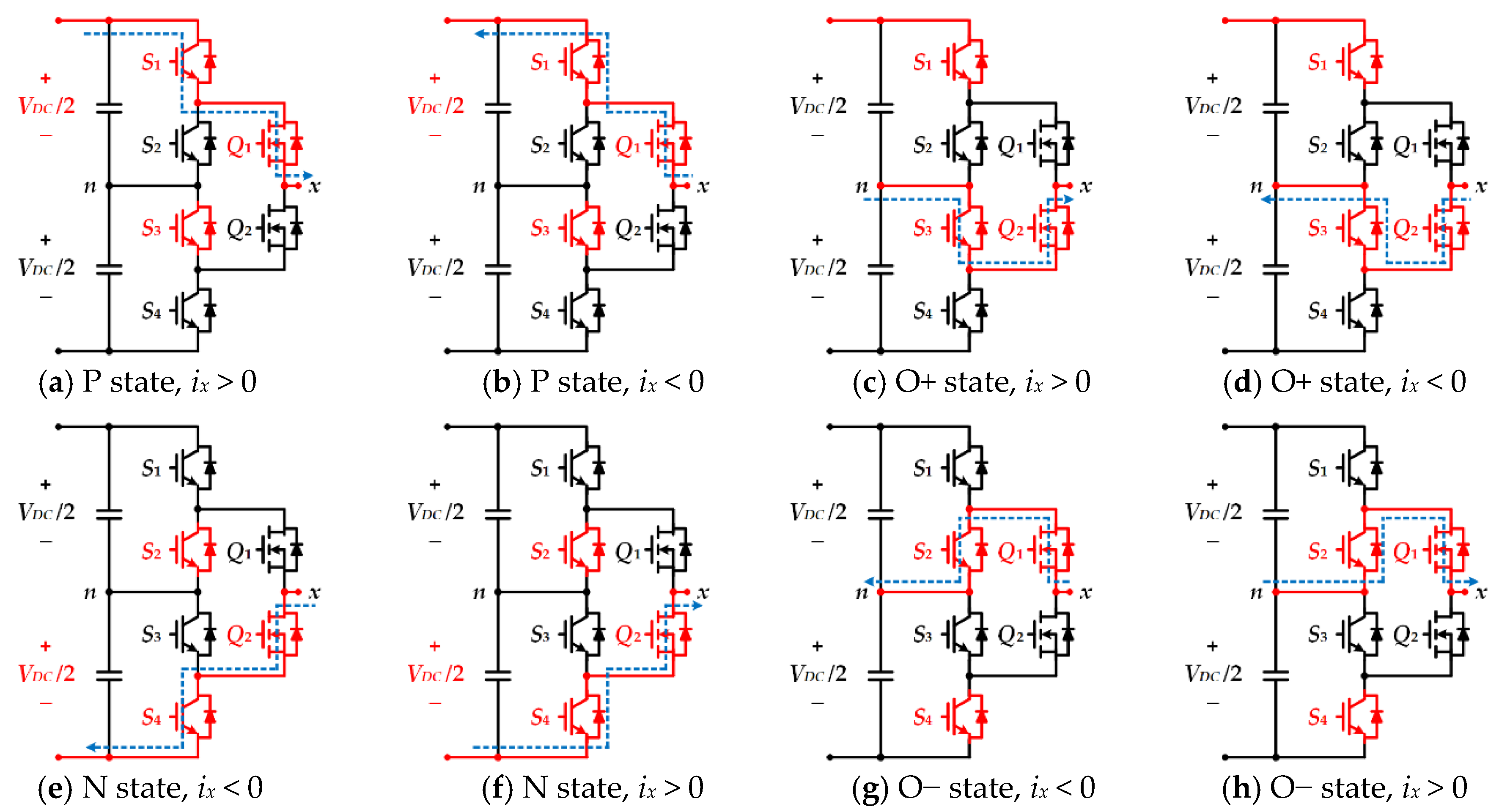

2.2. Modulation Scheme for Si and SiC Switches

3. Proposed Open-Fault Detection Method for Single Switch Failure

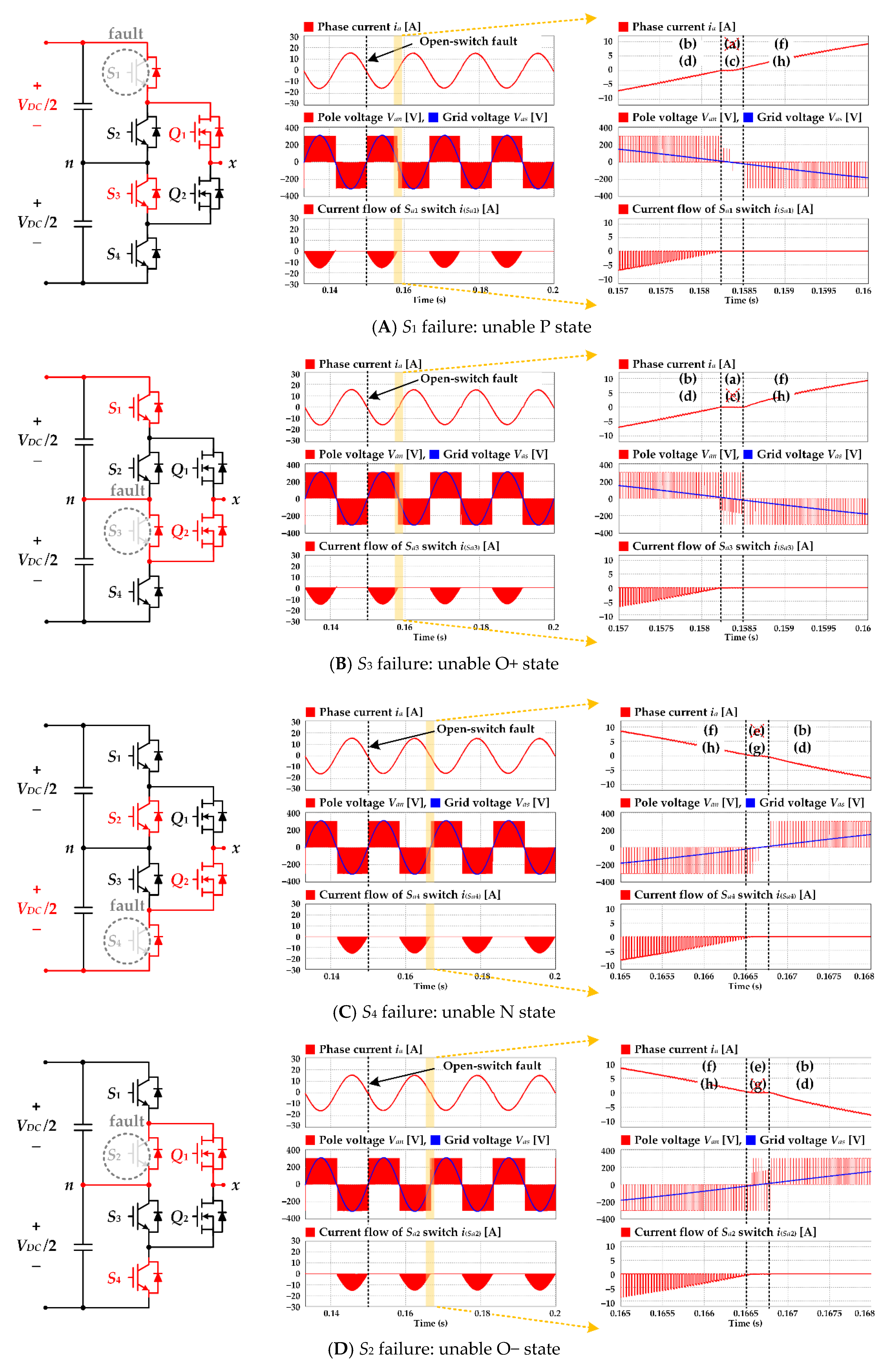

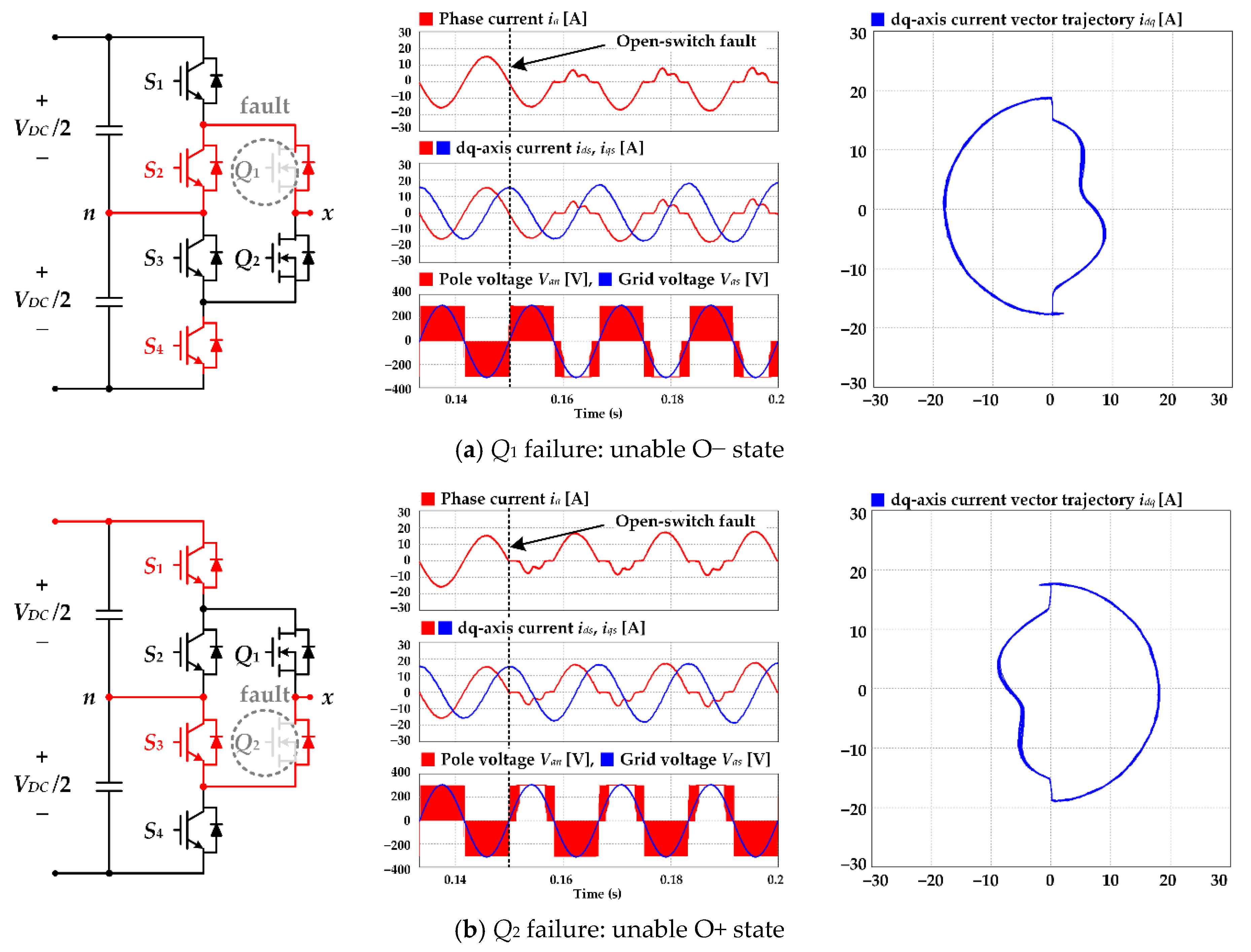

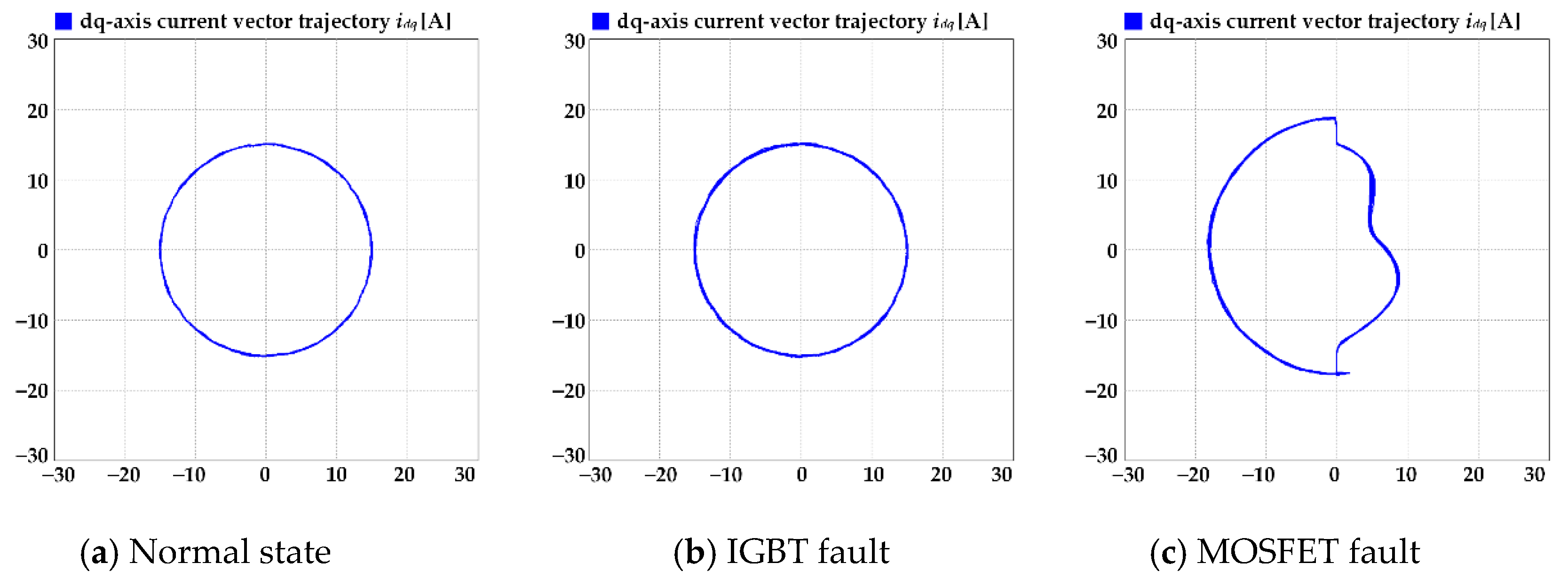

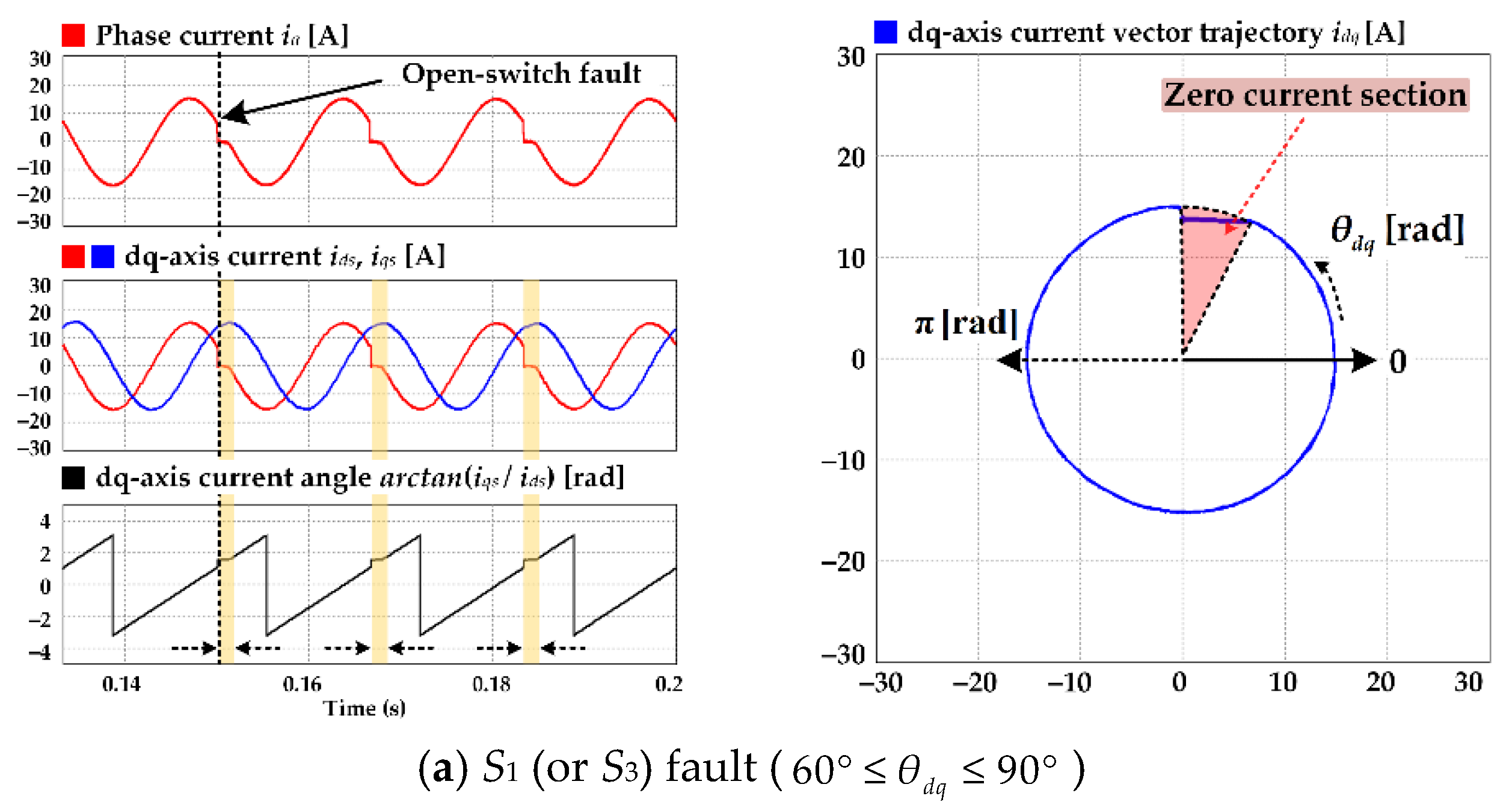

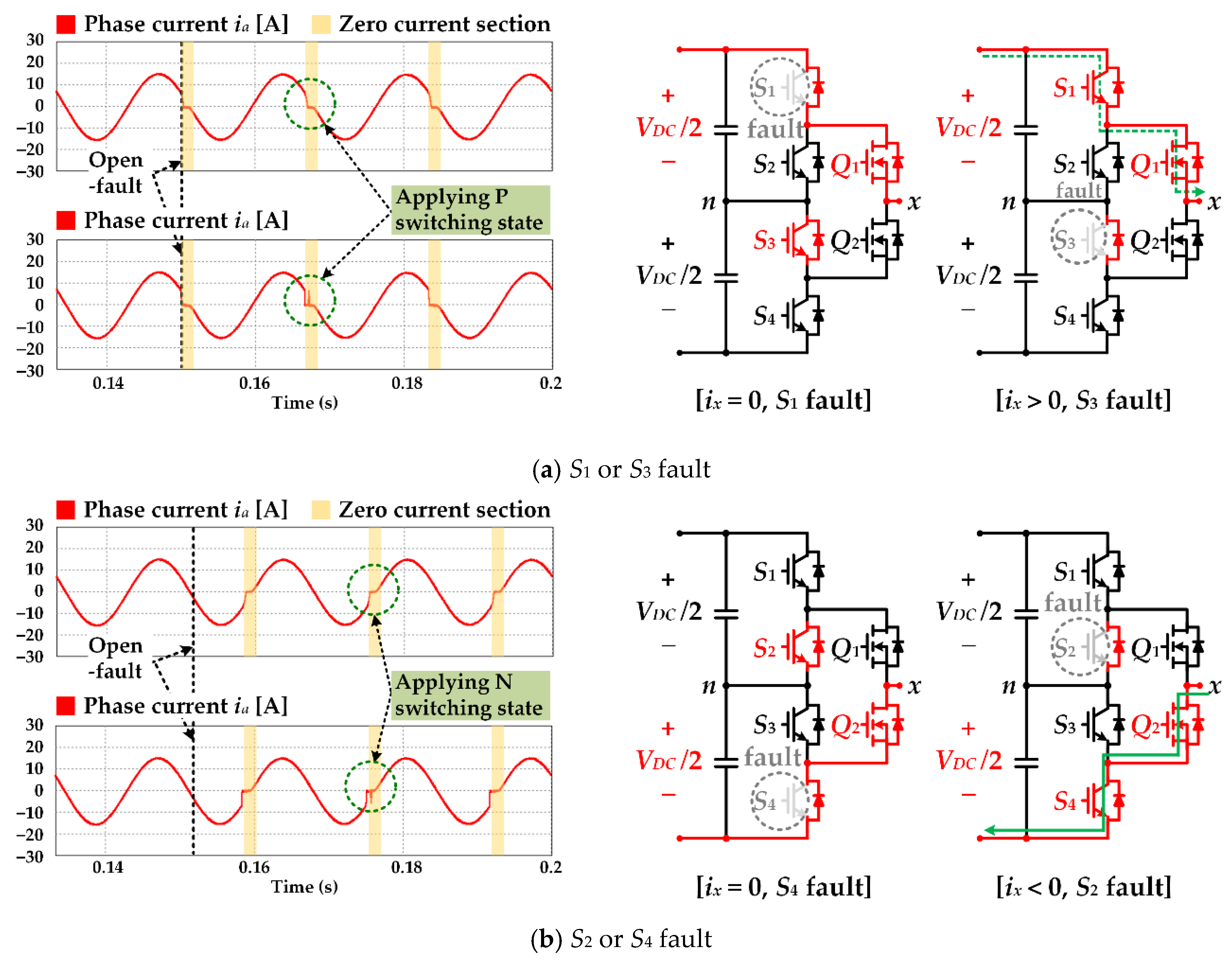

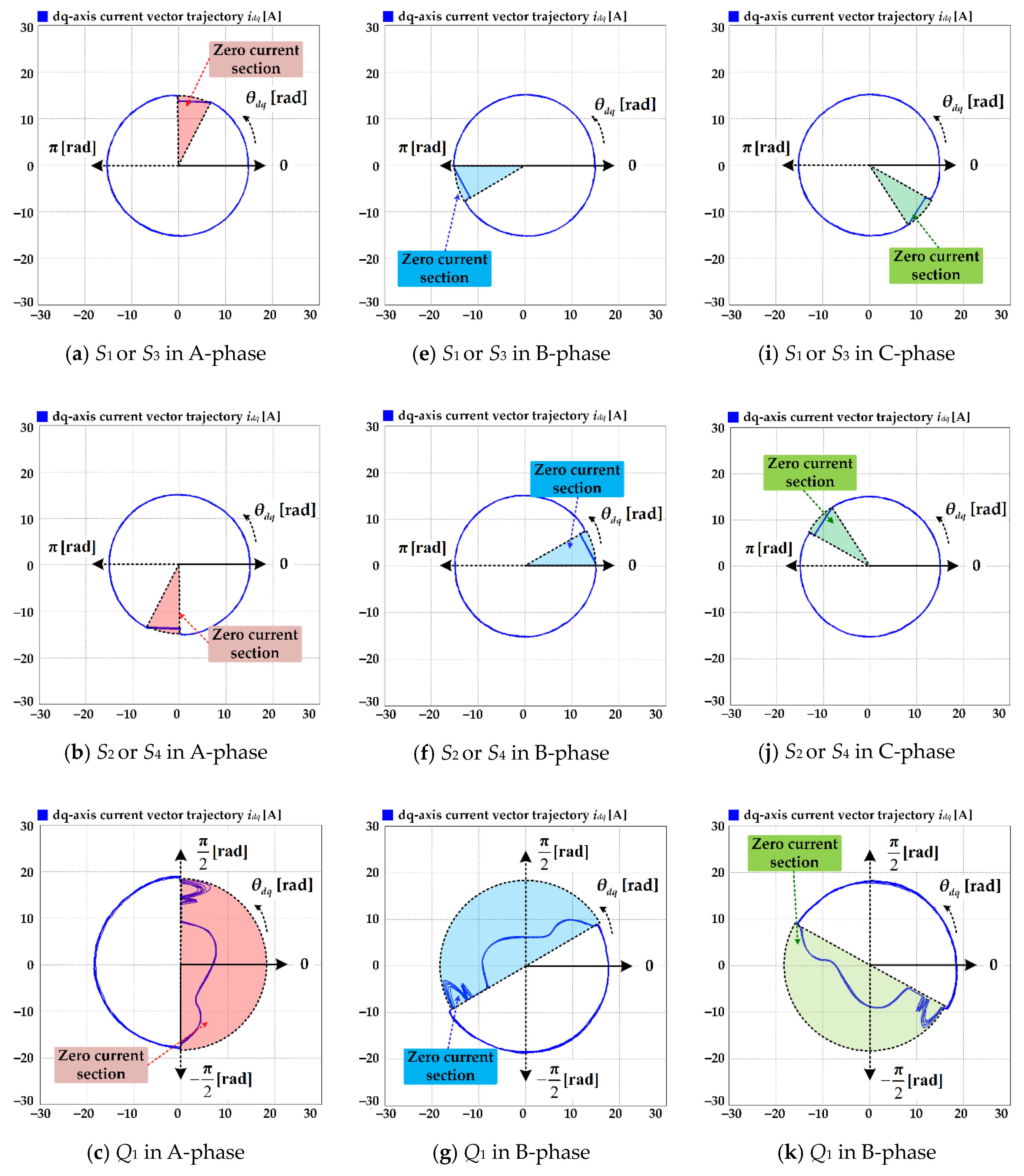

3.1. Feature Analysis of Switch Open Fault

3.2. Proposed Detection Method for Switch Open Fault

4. Simulation Results

5. Experimental Results

6. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Lee, K.B.; Lee, J.S. Reliability Improvement Technology for Power Converters, 1st ed.; Springer: Singapore, 2017; ISBN 978-981-10-4991-0. [Google Scholar]

- Bak, Y.; Lee, K.-B. Development of PCS to utilize differential pressure energy in district heating systems with reduced DC-link voltage variation. J. Power Electron. 2020, 20, 1109–1118. [Google Scholar] [CrossRef]

- Lee, S.S.; Bak, Y.; Kim, S.-M.; Joseph, A.; Lee, K.-B. New family of boost switched-capacitor seven-level inverters (BSC7LI). IEEE Trans. Power Electron. 2019, 34, 10471–10479. [Google Scholar] [CrossRef]

- Blaabjerg, F.; Chen, J.; Kjaer, S.B. Power electronics as efficient interface in dispersed power generation systems. IEEE Trans. Power. Electron. 2004, 19, 1184–1194. [Google Scholar] [CrossRef]

- Lee, C.-H.; Lee, J. An Optimal Damping Control Algorithm of Direct Two-level Inverter for Miniaturization and Weight Reduction of Auxiliary Power Supply on Railway Vehicle. J. Electr. Eng. Technol. 2018, 13, 2335–2343. [Google Scholar] [CrossRef]

- Slaman, S.; Xin, A. Droop Control based Approach for Frequency and Voltage in Hybrid AC/DC Microgrid. J. Electr. Eng. Technol. 2020, 15. [Google Scholar] [CrossRef]

- Zhang, T.; Chen, X.; Qi, C.; Lang, Z. Leg-By-Leg-Based Finite-Control-Set Model Predictive Control for Two-Level Voltage-Source Inverters. J. Power Electron. 2019, 19, 1162–1170. [Google Scholar] [CrossRef]

- Bak, Y.; Jang, Y.; Lee, K.-B. Torque Predictive Control for Permanent Magnet Synchronous Motor Drives Using Indirect Matrix Converter. J. Power Electron. 2019, 19, 1536–1543. [Google Scholar] [CrossRef]

- Rodríguez, J.; Lai, J.-S.; Peng, F.Z. Multilevel inverters: A survey of topologies, controls, and applications. IEEE Trans. Ind. Electron. 2002, 49, 724–738. [Google Scholar] [CrossRef]

- Huo, Q.; Wang, P.; Cao, G.; Zhu, J.; Yin, J.; Guo, X.; Wei, T. Novel flexible HVDC transmission converter station topology with DC fault blocking capability. J. Power Electron. 2020, 20, 884–893. [Google Scholar] [CrossRef]

- Rodríguez, J.; Bernet, S.; Wu, B.; Pontt, J.O.; Kouro, S. Multilevel voltage-source-converter topologies for industrial medium-voltage drives. IEEE Trans. Ind. Electron. 2007, 54, 2930–2945. [Google Scholar] [CrossRef]

- Rodriguez, J.; Bernet, S.; Steimer, P.K.; Lizama, I.E. A survey on neutral-point-clamped inverters. IEEE Trans. Ind. Electron. 2010, 57, 2219–2230. [Google Scholar] [CrossRef]

- Schweizer, M.; Friedli, T.; Kolar, J.W. Comparative evaluation of advanced three-phase three-level inverter/Converter topologies against two-level systems. IEEE Trans. Ind. Electron. 2013, 60, 5515–5527. [Google Scholar] [CrossRef]

- Rodríguez, J.; Dixon, J.; Espinoza, J.; Pontt, J.; Lezana, P. PWM Regenerative rectifiers: State of the art. IEEE Trans. Ind. Electron. 2005, 52, 5–22. [Google Scholar] [CrossRef]

- Nabae, A.; Takahashi, I.; Akagi, H. A new neutral-point-clamped PWM inverter. IEEE Trans. Ind. Appl. 1981, IA-17, 518–523. [Google Scholar] [CrossRef]

- Brückner, T.; Bernet, S.; Güldner, H. The active NPC converter and its loss-balancing control. IEEE Trans. Ind. Electron. 2005, 52, 855–868. [Google Scholar] [CrossRef]

- Millán, J.; Godignon, P.; Perpiñà, X.; Pérez-Tomás, A.; Rebollo, J. A survey of wide bandgap power semiconductor devices. IEEE Trans. Power Electron. 2014, 29, 2155–2163. [Google Scholar] [CrossRef]

- She, X.; Huang, A.Q.; Lucía, Ó.; Ozpineci, B. Review of Silicon Carbide Power Devices and Their Applications. IEEE Trans. Ind. Electron. 2017, 64, 8193–8205. [Google Scholar] [CrossRef]

- Wang, J.; Jiang, X. Review and analysis of SiC MOSFETs’ ruggedness and reliability. IET Power Electron. 2020, 13, 445–455. [Google Scholar] [CrossRef]

- Guan, Q.-X.; Li, C.; Zhang, Y.; Wang, S.; Xu, D.-D.; Li, W.; Ma, H. An extremely high efficient three-level active neutral-point-clamped converter comprising SiC and Si hybrid power stages. IEEE Trans. Power Electron. 2018, 33, 8341–8352. [Google Scholar] [CrossRef]

- Yang, S.; Bryant, A.; Mawby, P.; Xiang, D.; Ran, L.; Tavner, P. An industry-based survey of reliability in power electronic converters. IEEE Trans. Ind. Appl. 2011, 47, 1441–1451. [Google Scholar] [CrossRef]

- Choi, U.-M.; Blaabjerg, F.; Lee, K.-B. Study and handling methods of power IGBT module failures in power electronic converter systems. IEEE Trans. Power Electron. 2015, 30, 2517–2533. [Google Scholar] [CrossRef]

- Yang, S.; Xiang, D.; Bryant, A.; Mawby, P.; Ran, L.; Tavner, P. Condition monitoring for device reliability in power electronic converters: A review. IEEE Trans. Power Electron. 2010, 25, 2734–2752. [Google Scholar] [CrossRef]

- Liu, G.; Li, K.; Wang, Y.; Luo, H.; Luo, H. Recent advances and trend of HEV/EV-oriented power semiconductors—An overview. IET Power Electron. 2020, 13, 394–404. [Google Scholar] [CrossRef]

- Yang, H.; Zhou, Y.; Zhao, J. Current covariance analysis-based open-circuit fault diagnosis for voltage-source-inverter-fed vector-controlled induction motor drives. J. Power Electron. 2020, 20, 492–500. [Google Scholar] [CrossRef]

- Lu, B.; Sharma, S.K. A literature review of IGBT fault diagnostic and protection methods for power inverters. IEEE. Trans. Ind. Appl. 2009, 45, 1770–1777. [Google Scholar] [CrossRef]

- Mohan, M.; Vittal, K.P. DC Fault Protection in Multi-terminal VSC-Based HVDC Transmission Systems with Current Limiting Reactors. J. Electr. Eng. Technol. 2019, 14, 1–12. [Google Scholar] [CrossRef]

- Shin, H.-U.; Lee, K.-B. Fault Diagnosis Method for Switched Reluctance Machine Drive Systems Using a Switching Signal. J. Electr. Eng. Technol. 2019, 14, 663–676. [Google Scholar] [CrossRef]

- Lin, Y.; Ge, H.; Chen, S.; Pecht, M. Two-level fault diagnosis RBF networks for auto-transformer rectifier units using multi-source features. J. Power Electron. 2020, 20, 754–763. [Google Scholar] [CrossRef]

- Yin, H.; Chen, Y.; Chen, Z. Observer-based adaptive threshold diagnosis method for open-switch faults of voltage source inverters. J. Power Electron. 2020, 20. [Google Scholar] [CrossRef]

- Kim, Y.; Park, T.; Kim, S.; Kwak, N.; Kweon, D. Artificial Intelligent Fault Diagnostic Method for Power Transformers using a New Classification System of Faults. J. Electr. Eng. Technol. 2019, 14, 825–831. [Google Scholar] [CrossRef]

- Im, W.-S.; Kim, J.-M.; Lee, D.-C.; Lee, K.-B. Diagnosis and fault-tolerant control of three-phase AC–DC PWM Converter SYSTEMS. IEEE Trans. Ind. Appl. 2013, 49, 1539–1547. [Google Scholar] [CrossRef]

- Cardoso, A.M.; Saraiva, E.S. Computer-aided detection of airgap eccentricity in operating three-phase induction motors by Park’s vector approach. IEEE Trans. Ind. Appl. 1993, 29, 897–901. [Google Scholar] [CrossRef]

- Jo, S.-R.; Kim, S.-M.; Cho, S.; Lee, K.-B. Development of a hardware simulator for reliable design of modular multilevel converters based on junction-temperature of IGBT modules. Electronics 2019, 8, 1127. [Google Scholar] [CrossRef]

- Choi, U.-M.; Blaabjerg, F.; Jørgensen, S. Power cycling test methods for reliability assessment of power device modules in respect to temperature stress. IEEE Power Electron. 2018, 33, 2531–2551. [Google Scholar] [CrossRef]

- Alavi, M.; Wang, D.; Luo, M. Short-circuit fault diagnosis for three-phase inverters based on voltage-space patterns. IEEE Trans. Ind. Electron. 2014, 61, 5558–5569. [Google Scholar] [CrossRef]

- Gao, Z.; Cecati, C.; Ding, S.X. A Survey of fault diagnosis and fault-tolerant techniques—Part I: Fault diagnosis with model-based and signal-based approaches. IEEE Trans. Ind. Electron. 2015, 62, 3757–3767. [Google Scholar] [CrossRef]

- Ku, H.-K.; Jung, J.-H.; Park, J.-W.; Kim, J.-M. Fault-tolerant control strategy for open-circuit fault of two-parallel-connected three-phase AC–DC two-level PWM converter. J. Power Electron. 2020, 20, 731–742. [Google Scholar] [CrossRef]

- Lee, E.; Lee, K.-B. Fault-tolerant strategy to control a reverse matrix converter for open-switch faults in the rectifier stage. J. Power Electron. 2016, 16, 57–65. [Google Scholar] [CrossRef]

- Khomfoi, S.; Tolbert, L.M. Fault diagnostic system for a multilevel inverter using a neural network. IEEE Trans. Power Electron. 2007, 22, 1062–1069. [Google Scholar] [CrossRef]

- Qiao, H.; Wang, T.; Wang, P.; Zhang, L.; Xu, M. An adaptive weighted multiscale convolutional neural network for rotating machinery fault diagnosis under variable operating conditions. IEEE Access 2019, 7, 118954–118964. [Google Scholar] [CrossRef]

- Caseiro, L.M.A.; Mendes, A.M.S. Real-time IGBT open-circuit fault diagnosis in three-level neutral-point-clamped voltage-source rectifiers based on instant voltage error. IEEE Trans. Ind. Electron. 2015, 62, 1669–1678. [Google Scholar] [CrossRef]

- Kwon, B.H.; Kim, S.-H.; Kim, S.-M.; Lee, K.-B. Fault diagnosis of open-switch failure in a grid-connected three-level Si/SiC hybrid ANPC inverter. Electronics 2020, 9, 399. [Google Scholar] [CrossRef]

- Choi, U.-M.; Jeong, H.-G.; Lee, K.-B.; Blaabjerg, F. Method for detecting an open-switch fault in a grid-connected NPC inverter system. IEEE Trans. Power Electron. 2012, 27, 2726–2739. [Google Scholar] [CrossRef]

- Kim, T.-J.; Lee, W.-C.; Hyun, D.-S. Detection method for open-circuit fault in neutral-point-clamped inverter systems. IEEE Trans. Ind. Electron. 2009, 56, 2754–2763. [Google Scholar] [CrossRef]

- Afef, B.-B.A.; Hafedh, B.A.; Frédéric, R.; Jean-Marc, B.; Franck, M.; Ilhem, S.-B. Versatile three-level FC-npc converter with high fault-tolerance capabilities: Switch fault detection and isolation and safe postfault operation. IEEE Trans. Ind. Electron. 2019, 64, 6453–6464. [Google Scholar] [CrossRef]

- Qun-Tao, A.; Li-Zhi, S.; Ke, Z.; Li, S. Switching function model-based fast-diagnostic method of open-switch faults in inverters without sensors. IEEE Trans. Power Electron. 2011, 26, 119–126. [Google Scholar] [CrossRef]

- Jeon, S.-S.; Lee, Y.J.; Bak, Y.; Lee, K.-B. Hardware-simulator development and implementation for hydraulic turbine generation systems in a district heating system. Electronics 2020, 9, 368. [Google Scholar] [CrossRef]

- Seo, D.-W.; Bak, Y.; Lee, K.-B. An improved rotating restart method for a sensorless permanent magnet synchronous motor drive system using repetitive zero voltage vectors. IEEE Trans. Ind. Electron. 2020, 67, 3496–3504. [Google Scholar] [CrossRef]

- Lee, E.-J.; Kim, S.-M.; Lee, K.-B. Modified phase-shifted PWM scheme for reliability improvement in cascaded H-bridge multilevel inverters. IEEE Access 2020, 8, 78130–78139. [Google Scholar] [CrossRef]

- Kim, S.-M.; Jeong, M.-G.; Kim, J.; Lee, K.-B. Hybrid Modulation Scheme for Switching Loss Reduction in a Modular Multilevel High-voltage Direct Current Converter. IEEE Trans. Power Electron. 2019, 34, 3178–3191. [Google Scholar] [CrossRef]

- Kwon, B.H.; Kim, S.-H.; Bea, K.-C.; Lee, K.-B. Performance analysis on a bidirectional operation of a three-level hybrid ANPC inverter. Trans. Korean Inst. Electr. Eng. 2019, 10, 1204–1213. [Google Scholar] [CrossRef]

- Yoon, H.; Yoon, D.; Choi, D.; Cho, Y. Three-phase current balancing strategy with distributed static series compensators. J. Power Electron. 2019, 19, 803–814. [Google Scholar] [CrossRef]

- Choi, H.; Song, S.; Jeong, S.; Choi, J.; Choy, I. Design of SRF-PLL system with consideration of low-pass filter for high dynamic performance during voltage disturbance. In Proceedings of the IEEE 6th International Power Electronics and Motion Control Conference (IPEMC), Wuhan, China, 17–20 May 2009. [Google Scholar] [CrossRef]

- Xu, Y.; Li, H.; Ren, J.; Zhang, Y. Three-vector-based model predictive current control with disturbance feedforward compensation. J. Power Electron. 2020, 20, 687–697. [Google Scholar] [CrossRef]

- Feng, X.; Tao, Y.; Cui, X.; Shao, K.; Wang, Y. Sliding mode and predictive current control strategy of the three-phase Vienna rectifier. J. Power Electron. 2020, 20, 743–753. [Google Scholar] [CrossRef]

- Kazmierkowski, M.P.; Malesani, L. Current control techniques for three-phase voltage-source PWM converters: A survey. IEEE Trans. Ind. Electron. 1998, 45, 691–703. [Google Scholar] [CrossRef]

- Lee, J.-S.; Lee, K.-B.; Blaabjerg, F. Open-switch fault detection method of a back-to-back converter using NPC topology for wind turbine systems. IEEE Trans. Ind. Appl. 2015, 51, 325–335. [Google Scholar] [CrossRef]

| Switching State | Output Pole Voltage Vxn | IGBTs | MOSFETs | ||||

|---|---|---|---|---|---|---|---|

| S1 | S2 | S3 | S4 | Q1 | Q2 | ||

| Positive (P) | +VDC/2 | 1 | 0 | 1 | 0 | 1 | 0 |

| Zero (O+) | 0 | 1 | 0 | 1 | 0 | 0 | 1 |

| Zero (O−) | 0 | 0 | 1 | 0 | 1 | 1 | 0 |

| Negative (N) | −VDC/2 | 0 | 1 | 0 | 1 | 0 | 1 |

| Parameters | Value | Unit |

|---|---|---|

| Voltage of DC-link (VDC) | 600 | V |

| Voltage of grid source (line-to-line) | 380 | Vrms |

| Capacitance of DC-link (Cupper, Clow) | 4700 | μF |

| Inductance of grid filter (L) | 2 | mH |

| Switching frequency of SiC MOSFET | 20,000 | Hz |

| Frequency of grid voltage (switching frequency of Si IGBT) | 60 | Hz |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kim, S.-H.; Kim, S.-M.; Park, S.; Lee, K.-B. Switch Open-Fault Detection for a Three-Phase Hybrid Active Neutral-Point-Clamped Rectifier. Electronics 2020, 9, 1437. https://doi.org/10.3390/electronics9091437

Kim S-H, Kim S-M, Park S, Lee K-B. Switch Open-Fault Detection for a Three-Phase Hybrid Active Neutral-Point-Clamped Rectifier. Electronics. 2020; 9(9):1437. https://doi.org/10.3390/electronics9091437

Chicago/Turabian StyleKim, Sang-Hun, Seok-Min Kim, Sungmin Park, and Kyo-Beum Lee. 2020. "Switch Open-Fault Detection for a Three-Phase Hybrid Active Neutral-Point-Clamped Rectifier" Electronics 9, no. 9: 1437. https://doi.org/10.3390/electronics9091437

APA StyleKim, S.-H., Kim, S.-M., Park, S., & Lee, K.-B. (2020). Switch Open-Fault Detection for a Three-Phase Hybrid Active Neutral-Point-Clamped Rectifier. Electronics, 9(9), 1437. https://doi.org/10.3390/electronics9091437