Monolithic Integrated High Frequency GaN DC-DC Buck Converters with High Power Density Controlled by Current Mode Logic Level Signal

Abstract

:1. Introduction

2. GaN Based Switching DC-DC Converter

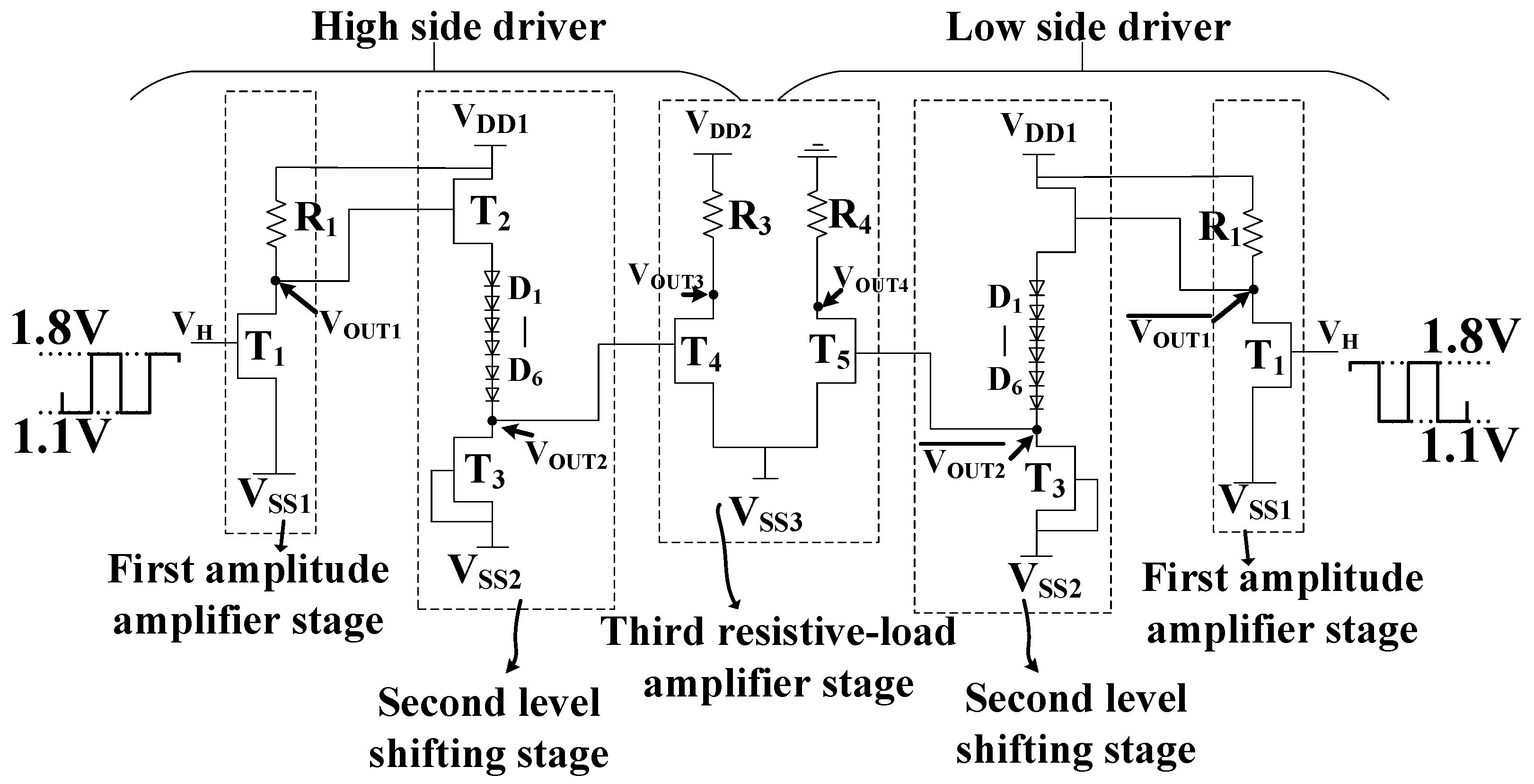

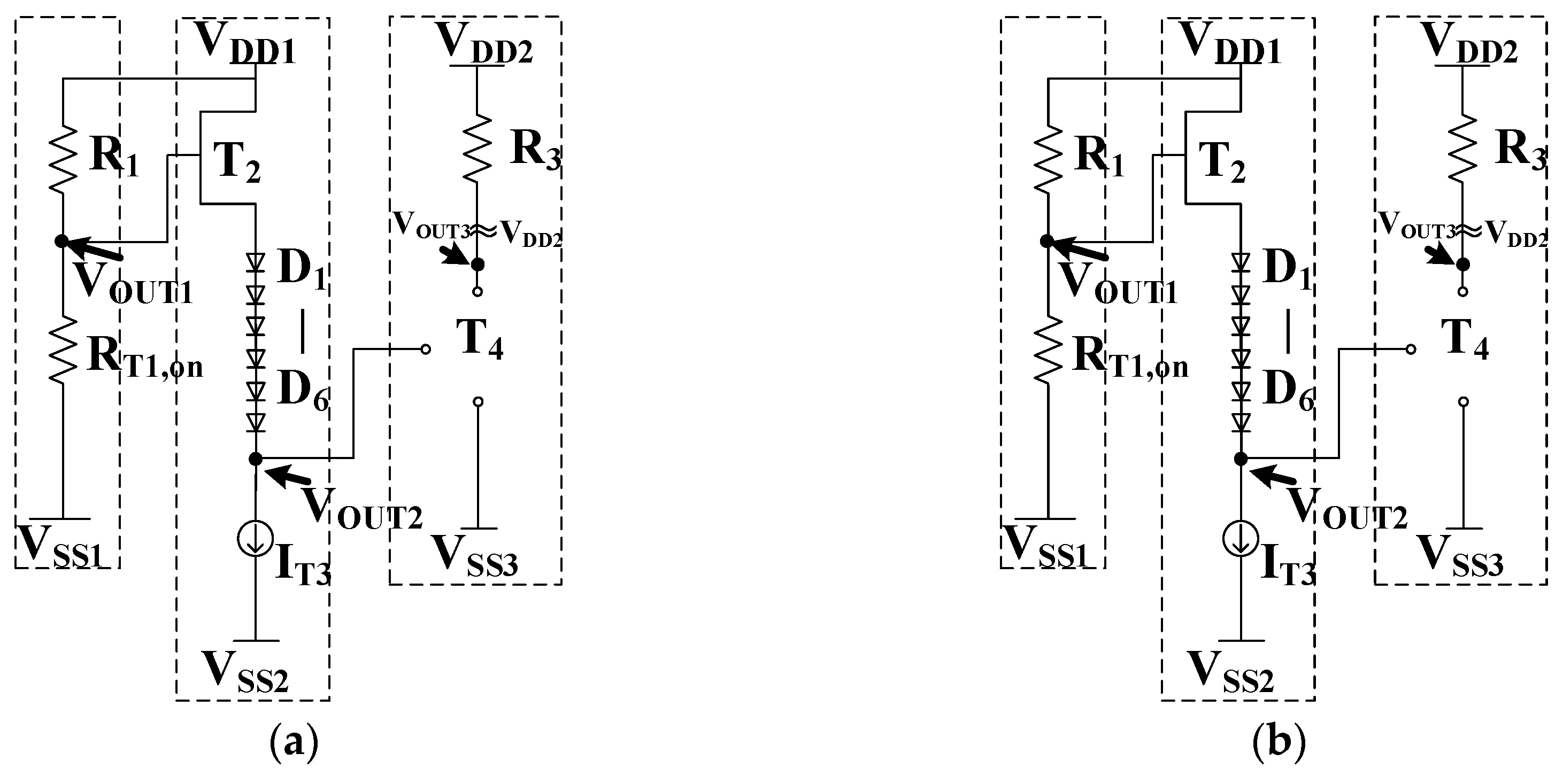

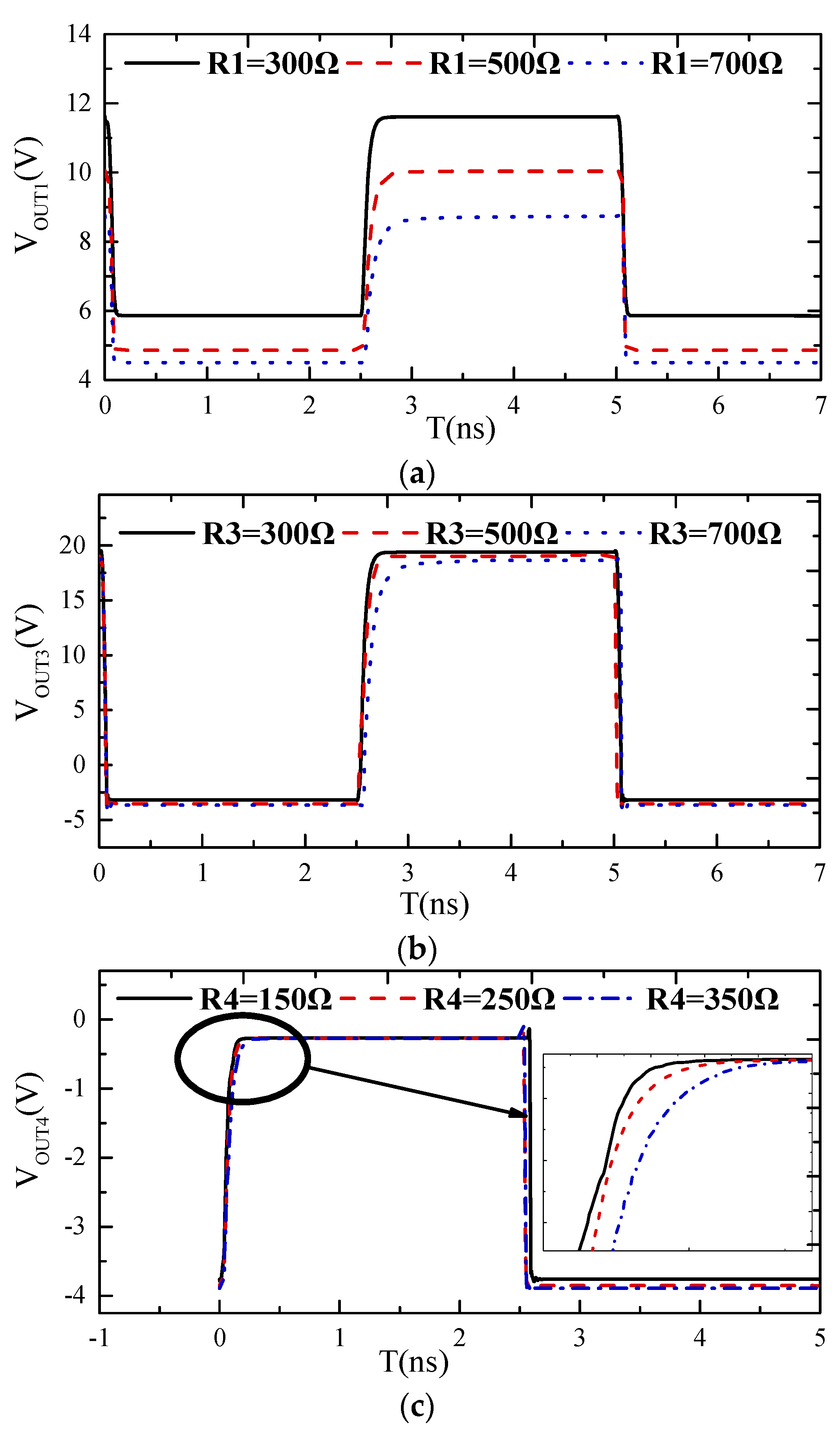

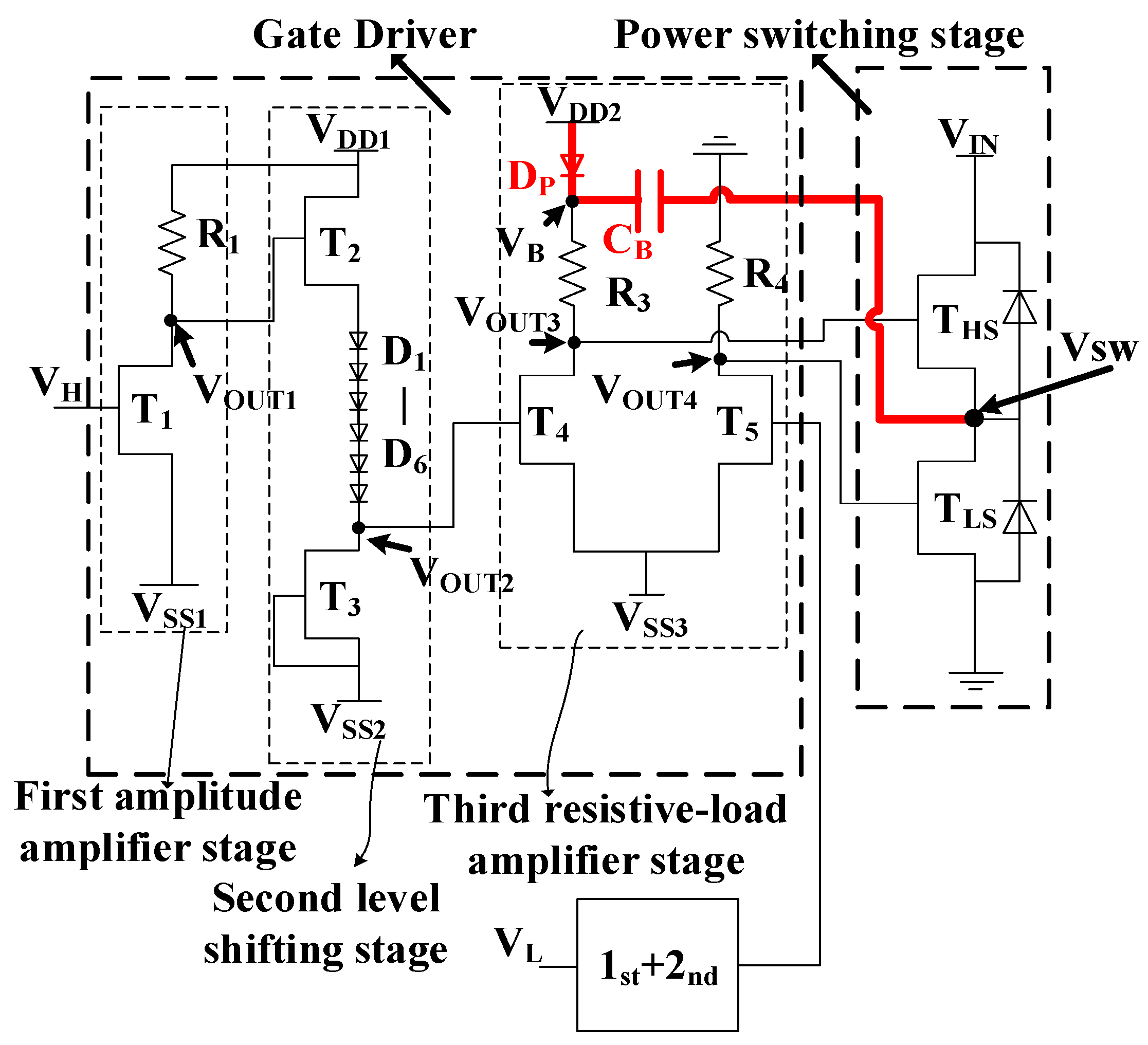

2.1. Driver Design

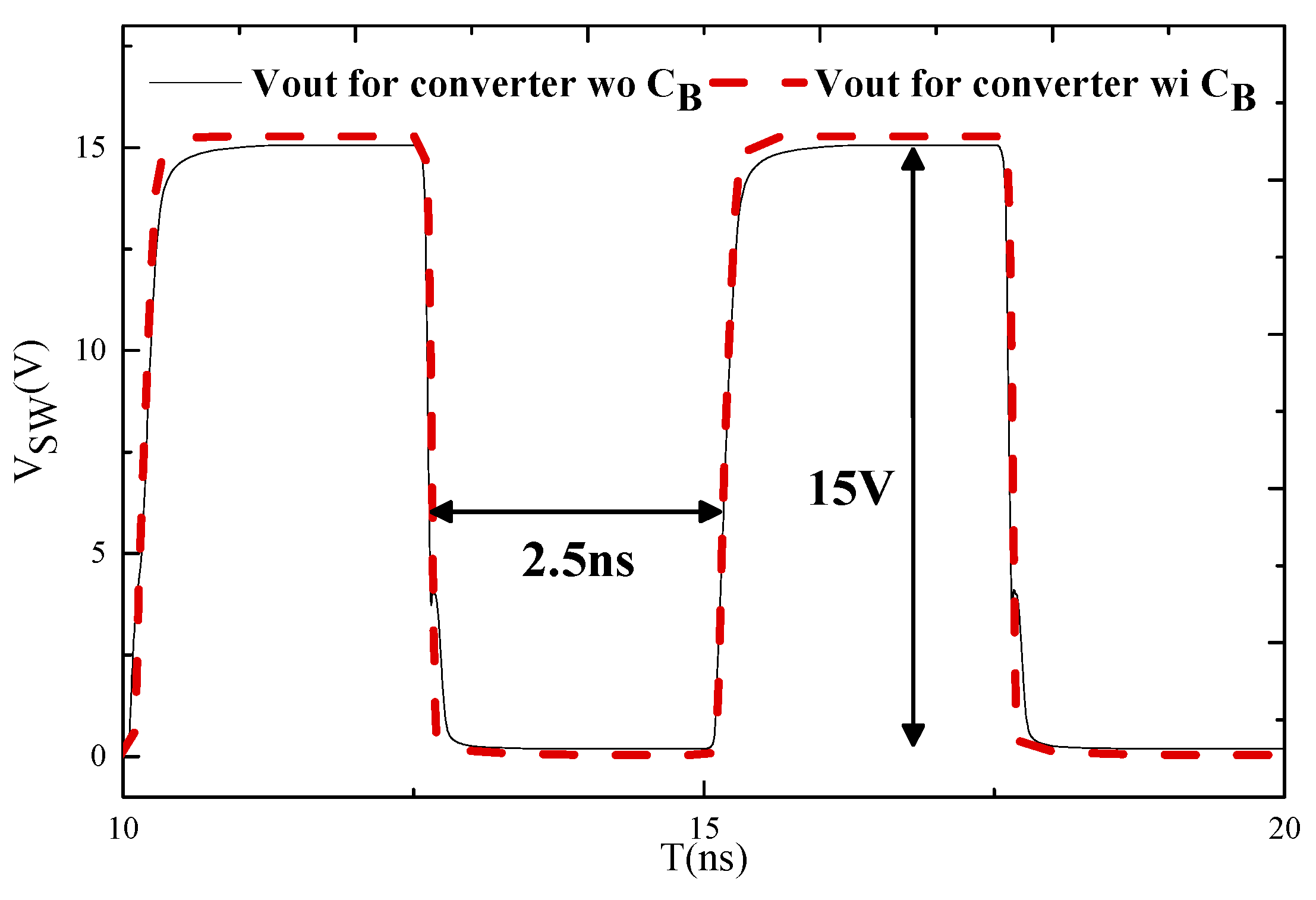

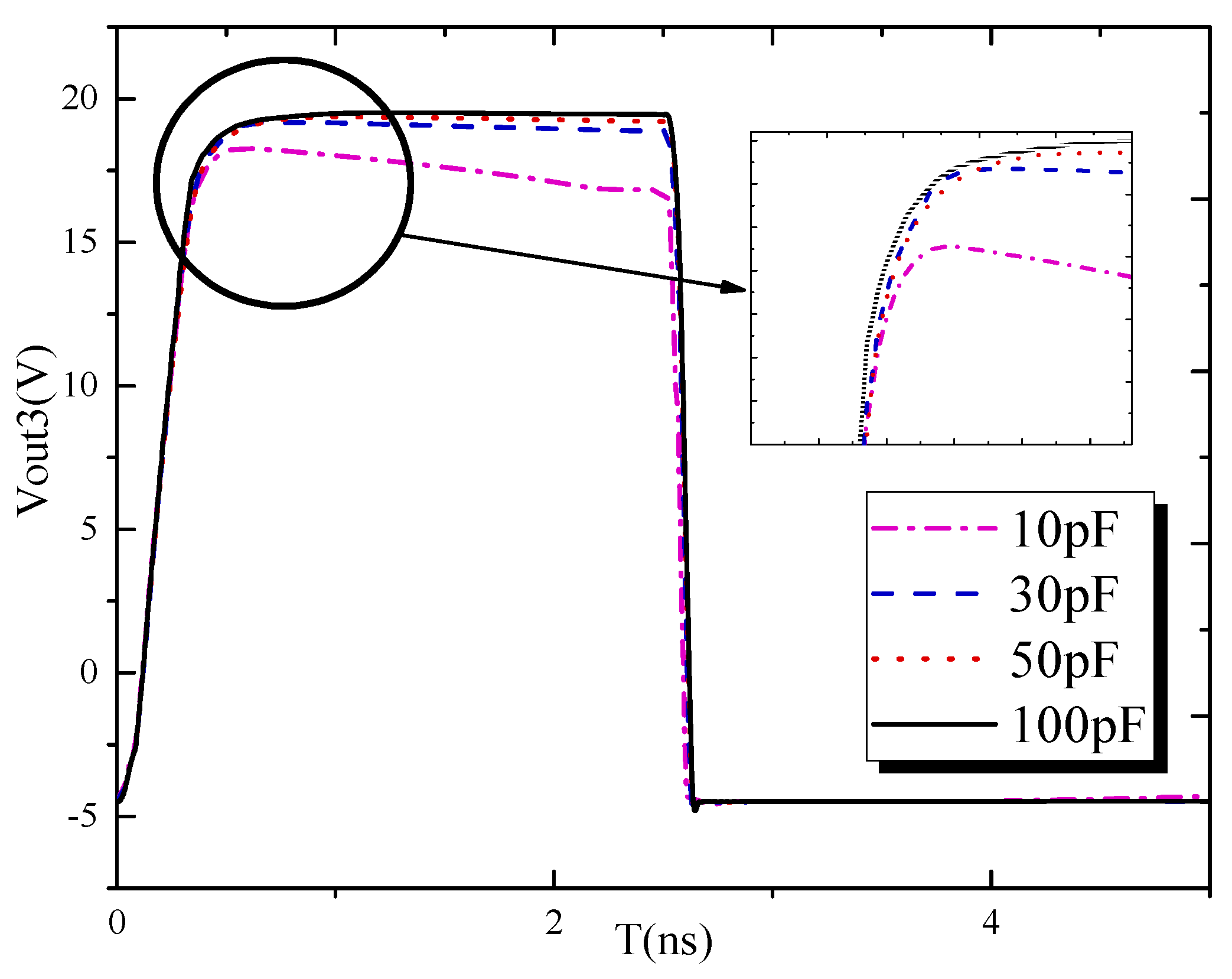

2.2. Converter Design

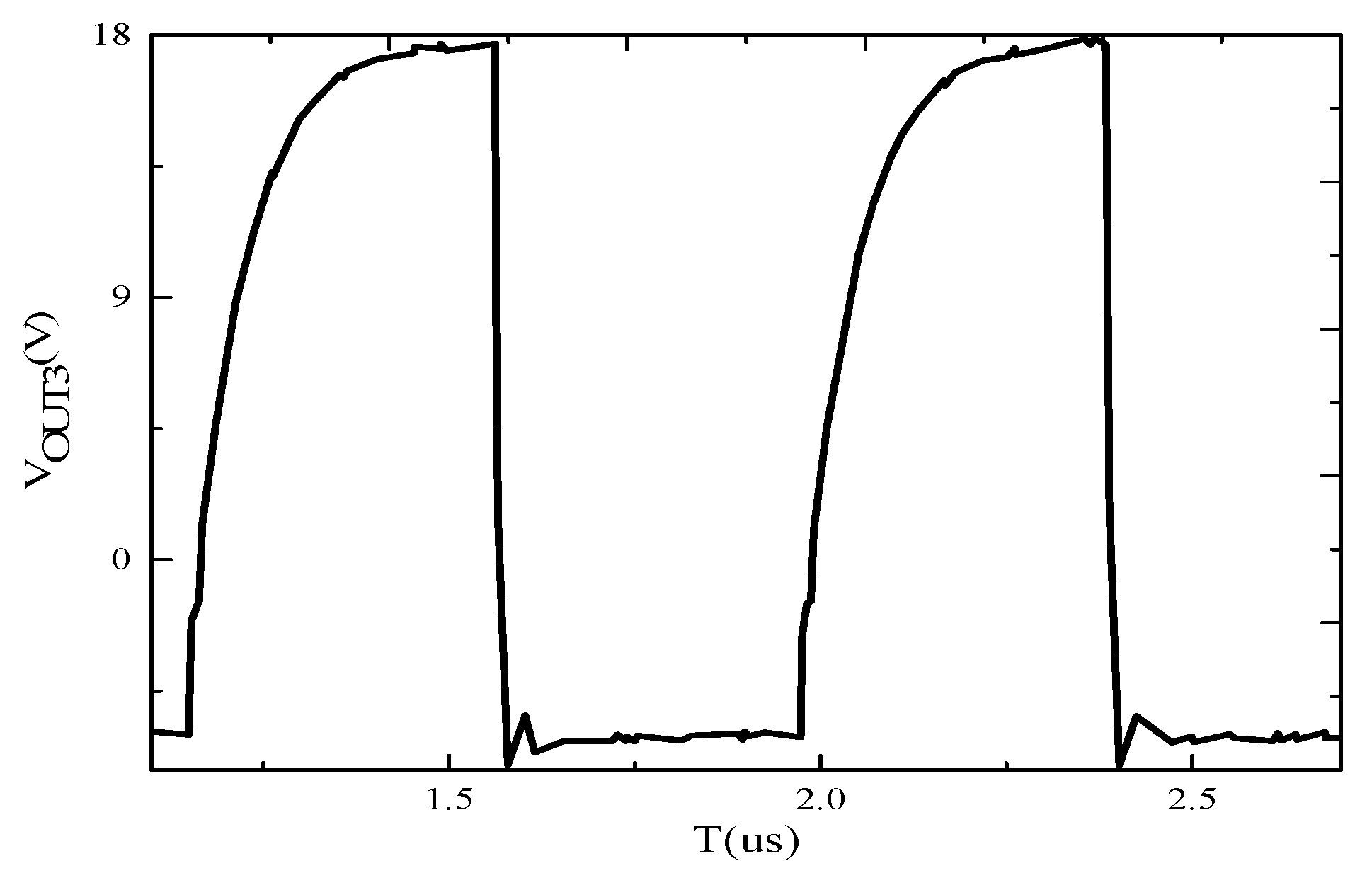

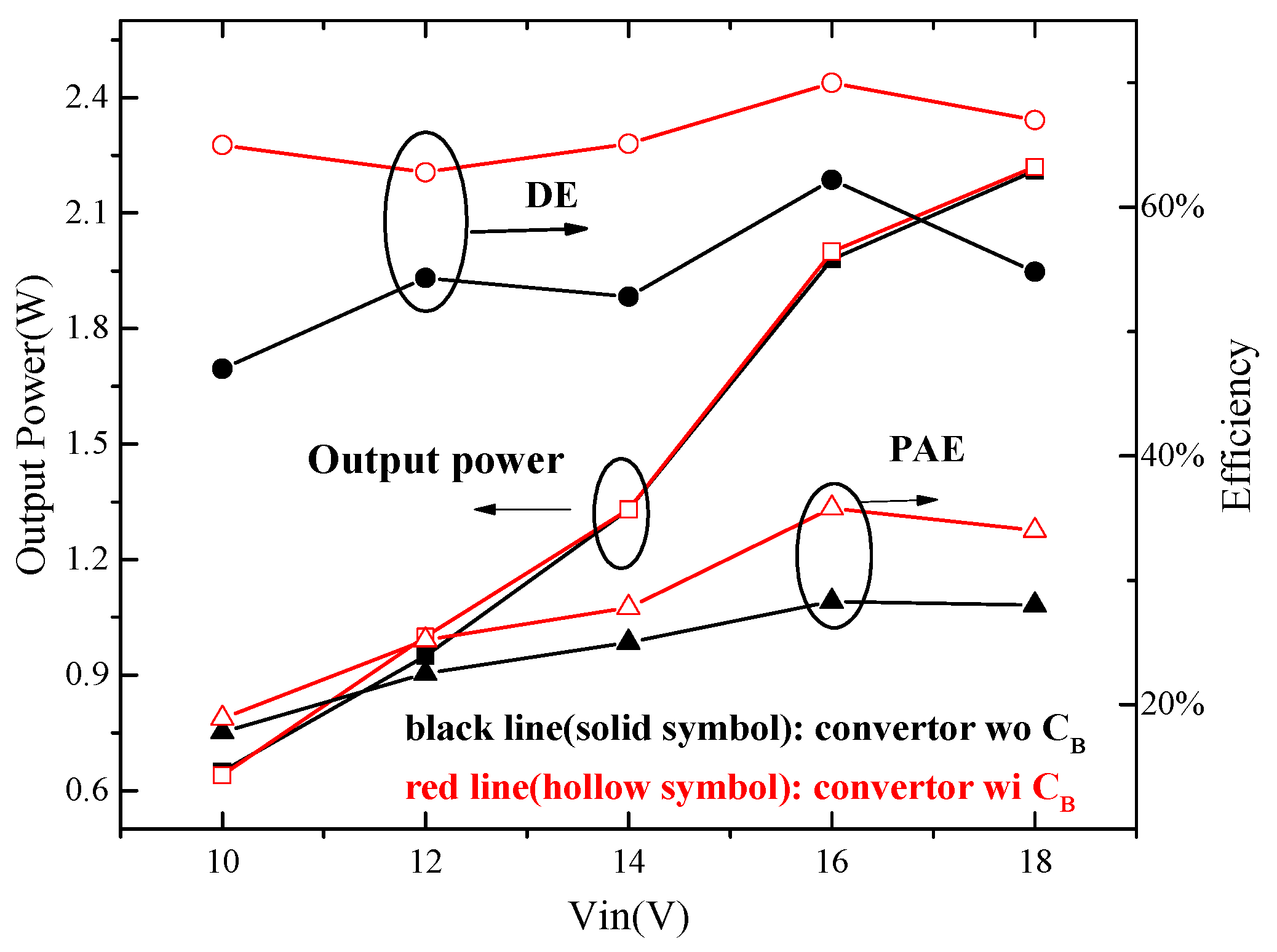

3. Experiment Results

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Jain, P.K. Power electronics for low voltage semiconductor technology: Challenges and some possible solutions. In Proceedings of the International Power Electronics & Motion Control Conference, Xi’an, China, 14–16 August 2004; pp. 20–28. [Google Scholar]

- Babazadeh, A.; Tschirhart, D.J. Adaptive dynamic voltage transitioning in switch mode DC–DC power converters. IET Power Electron. 2017, 11, 507–514. [Google Scholar] [CrossRef]

- Kumar, S.; Choi, J.; Song, H. An ultra-low power CMOS DC–DC buck converter with double-chain digital PWM technique. Analog. Integr. Circuits Signal Process. 2017, 92, 141–149. [Google Scholar] [CrossRef]

- Lin, B.R.; Hou, B.R. Analysis of a zero voltage switching DC/DC converter without output inductor. IET Power Electron. 2012, 5, 790–800. [Google Scholar] [CrossRef]

- Liu, P.-J.; Lai, Y.-M.; Lee, P.-C.; Chen, H.-S. Fast-transient DC–DC converter with hysteresis prediction voltage control. IET Power Electron. 2017, 10, 271–278. [Google Scholar] [CrossRef]

- Monfaredi, K.; Yousefi, M.; Razyani, K. A compact CMOS DC-DC buck converter based on a novel complement value leaping PWM technique. Int. J. Circuit Theory Appl. 2019, 47, 580–590. [Google Scholar] [CrossRef]

- Yuan, C.; Hanxiao, D.; Xinquan, L. Ultra-low startup voltage low output ripple high-efficiency hysteretic current mode step-up DC–DC converter. IET Power Electron. 2015, 8, 1238–1245. [Google Scholar] [CrossRef]

- Elasser, A.; Chow, T.P. Silicon carbide benefits and advantages for power electronics circuits and systems. Proc. IEEE 2014, 90, 969–986. [Google Scholar] [CrossRef]

- Rodriguez, M.; Zhang, Y.; Maksimovic, D. High-Frequency PWM Buck Converters Using GaN-on-SiC HEMTs. IEEE Trans. Power Electron. 2014, 29, 2462–2473. [Google Scholar] [CrossRef]

- Zhang, Y.; Rodriguez, M.; Maksimović, D. Very High Frequency PWM Buck Converters Using Monolithic GaN Half-Bridge Power Stages with Integrated Gate Drivers. IEEE Trans. Power Electron. 2016, 31, 7926–7942. [Google Scholar] [CrossRef]

- Huang, X.; Liu, Z.; Lee, F.C.; Li, Q. Characterization and Enhancement of High-Voltage Cascode GaN Devices. IEEE Trans. Electron Devices 2014, 62, 270–277. [Google Scholar] [CrossRef]

- Jones, E.; Wang, F.F.; Costinett, D. Review of Commercial GaN Power Devices and GaN-Based Converter Design Challenges. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 4, 707–719. [Google Scholar] [CrossRef]

- Badawi, N.; Hilt, O.; Bahat-Treidel, E.; Bocker, J.; Wurfl, J.; Dieckerhoff, S.; Boecker, J.; Wuerfl, H.-J. Investigation of the Dynamic On-State Resistance of 600 V Normally-Off and Normally-On GaN HEMTs. IEEE Trans. Ind. Appl. 2016, 52, 4955–4964. [Google Scholar] [CrossRef]

- Le Gallou, N.; Sardin, D.; Delepaut, C.; Campovecchio, M.; Rochette, S. Over 10MHz bandwidth envelope-tracking DC/DC converter for flexible high power GaN amplifiers. In 2011 IEEE MTT-S International Microwave Symposium; IEEE: Piscataway, NJ, USA, 2011; pp. 1–4. [Google Scholar]

- Liu, M.-J.; Hsu, S.S.H. A Miniature 300-MHz Resonant DC–DC Converter with GaN and CMOS Integrated in IPD Technology. IEEE Trans. Power Electron. 2018, 33, 9656–9668. [Google Scholar] [CrossRef]

- Choi, P.; Radhakrishna, U.; Boon, C.C.; Antoniadis, D.; Peh, L.-S. A Fully Integrated Inductor-Based GaN Boost Converter with Self-Generated Switching Signal for Vehicular Applications. IEEE Trans. Power Electron. 2016, 31, 5365–5368. [Google Scholar] [CrossRef]

- Luo, W.; Liu, H.; Zhang, Z.; Pengpeng, S.; Xinyu, L. High-Power X -Band 5-b GaN Phase Shifter with Monolithic Integrated E/D HEMTs Control Logic. IEEE Trans. Electron Devices 2017, 64, 3627–3633. [Google Scholar] [CrossRef]

- Zheng, Y.; Ho, M.; Guo, J.; Mak, K.-L.; Leung, K.N. A Single-Inductor Multiple-Output Auto-Buck-Boost DC–DC Converter with Autophase Allocation. IEEE Trans. Power Electron. 2016, 31, 2296–2313. [Google Scholar] [CrossRef]

- Jing, X.; Mok, P.K.T.; Lee, M.C. A Wide-Load-Range Constant-Charge-Auto-Hopping Control Single-Inductor-Dual-Output Boost Regulator with Minimized Cross-Regulation. IEEE J. Solid State Circuits 2011, 46, 2350–2362. [Google Scholar] [CrossRef]

- Kuan, C.-W.; Lin, H.-C. Near-independently regulated 5-output single-inductor DC-DC buck converter delivering 1.2 W/mm 2 in 65 nm CMOS. In Proceedings of the 2012 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 19–23 February 2012; pp. 274–276. [Google Scholar]

- Musunuri, S.; Chapman, P.L. Design of low power monolithic DC-DC buck converter with integrated inductor. In Proceedings of the 2005 IEEE 36th Power Electronics Specialists Conference, Aachen, Germany, 12 June 2005; pp. 1773–1779. [Google Scholar]

- Aklimi, E.; Piedra, D.; Tien, K.; Palacios, T.; Shepard, K.L. Hybrid CMOS/GaN 40-MHz Maximum 20-V Input DC–DC Multiphase Buck Converter. IEEE J. Solid-State Circuits 2017, 52, 1618–1627. [Google Scholar] [CrossRef] [Green Version]

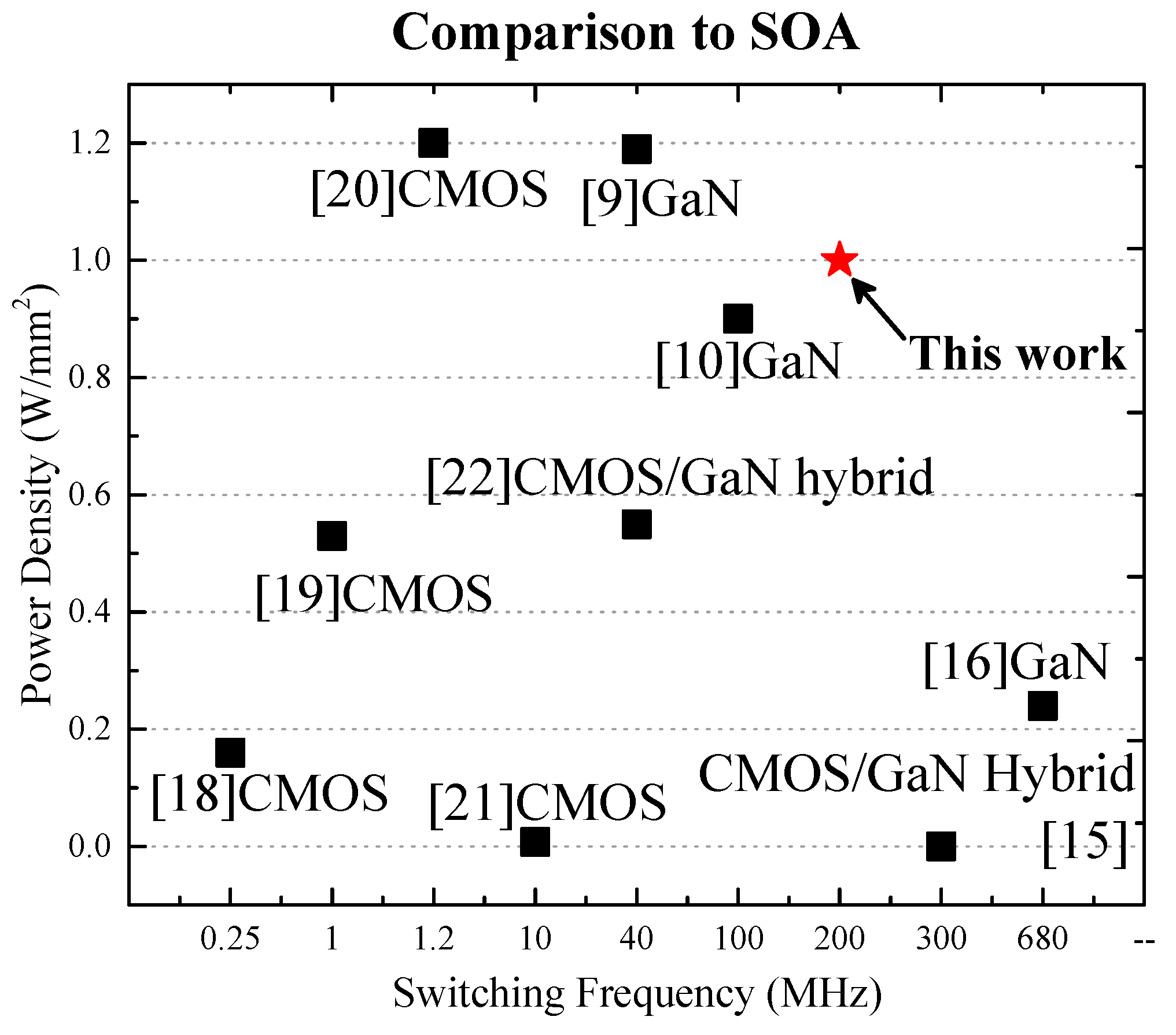

| Symbol | [10] | [14] | [15] | This Work |

|---|---|---|---|---|

| Technology | 0.15 um GaN | Discrete GaN | 0.25 um GaN | 0.25 um GaN |

| Gate driver | integrated | N/A | CMOS driver | integrated |

| Control signal swing | 5 V | 6.27 V | N/A | 0.7 V |

| Frequency | 100 MHz | 50 MHz | 300 MHz | 200 MHz |

| Max converter efficiency | 88% | 90% | 47.3% | 54.8% |

| Area | 2.4 × 2.3 mm2 | N/A | 0.94 × 0.98 cm2 | 1.7 × 1.3 mm2 |

| Power Density | 0.9 W/mm2 | N/A | 4.4 × 10−6 W/mm2 | 1 W/mm2 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lai, L.; Zhang, R.; Cheng, K.; Xia, Z.; Wei, C.; Wei, K.; Luo, W.; Liu, X. Monolithic Integrated High Frequency GaN DC-DC Buck Converters with High Power Density Controlled by Current Mode Logic Level Signal. Electronics 2020, 9, 1540. https://doi.org/10.3390/electronics9091540

Lai L, Zhang R, Cheng K, Xia Z, Wei C, Wei K, Luo W, Liu X. Monolithic Integrated High Frequency GaN DC-DC Buck Converters with High Power Density Controlled by Current Mode Logic Level Signal. Electronics. 2020; 9(9):1540. https://doi.org/10.3390/electronics9091540

Chicago/Turabian StyleLai, Longkun, Ronghua Zhang, Kui Cheng, Zhiying Xia, Chun Wei, Ke Wei, Weijun Luo, and Xinyu Liu. 2020. "Monolithic Integrated High Frequency GaN DC-DC Buck Converters with High Power Density Controlled by Current Mode Logic Level Signal" Electronics 9, no. 9: 1540. https://doi.org/10.3390/electronics9091540

APA StyleLai, L., Zhang, R., Cheng, K., Xia, Z., Wei, C., Wei, K., Luo, W., & Liu, X. (2020). Monolithic Integrated High Frequency GaN DC-DC Buck Converters with High Power Density Controlled by Current Mode Logic Level Signal. Electronics, 9(9), 1540. https://doi.org/10.3390/electronics9091540