1. Introduction

Silicon has long been the primary material for solar energy applications, largely owing to its natural abundance and low toxicity [

1,

2]. However, recent studies have highlighted certain limitations in the energy conversion efficiency of silicon-based photovoltaic cells [

3,

4], catalyzing the exploration of alternative semiconducting materials. In this vein, semiconductors such as cadmium telluride (CdTe) [

5,

6], gallium arsenide (GaAs) [

7,

8], indium phosphide (InP) [

9,

10], and complex ternary compounds like Cd

xTe

yO

z [

11,

12], Al

xGa

1−xAs [

13,

14], and CuGa

xIn

1−xSe

2 [

15,

16] have garnered significant attention. Despite the promising attributes of these materials, they are often compromised by high production costs [

17]. To ameliorate this, nanostructuring the surfaces of these semiconductors has been suggested as a method to enhance their light absorption coefficients [

18,

19,

20]. Nonetheless, the scarcity of elements like indium and gallium restricts the large-scale application of such materials to space-based solar cells [

21,

22], emphasizing the need for efficient and cost-effective materials for terrestrial use.

Emerging as a viable option is silicon carbide (SiC), a material comprising silicon and carbon, two of Earth’s most abundant elements [

23,

24,

25]. The well-characterized semiconductor properties of SiC make it conducive for industrial-scale utilization [

26,

27,

28,

29,

30,

31,

32,

33,

34,

35], akin to silicon. In addition to its robust thermal conductivity, electric breakdown voltage, and current density, SiC can operate over a broad temperature range without undergoing degradation in its monocrystalline structure or phase transitions. Through doping, the semiconductor properties of SiC can be tailored to yield both n-type and p-type materials [

36,

37]. These defects have been reported to impede the electrical and mechanical properties of the material, as corroborated by extensive studies [

38,

39]. Such defects are not just distinctive to silicon carbide but are a recurring theme across the broader category of semiconductors, each requiring its unique set of mitigative strategies.

Another formidable obstacle lies in the lattice mismatch when SiC films are grown on non-lattice-matched substrates. The repercussions of this discrepancy are often the formation of strain-induced defects that can severely compromise the crystalline quality of SiC films, thereby limiting their applicability in electronic devices [

40,

41].

To ameliorate these complexities, prior research has established the efficacy of incorporating intermediate buffer layers as a palliative measure [

42,

43]. Notably, porous domains or interstitial spaces generated on the semiconductor surface via electrochemical procedures have been shown to serve as effective buffer layers, considerably reducing defect densities and lattice mismatch-induced stresses [

44,

45,

46]. Additionally, it has been demonstrated repeatedly that the nanostructuring of silicon leads to a change in the properties of the monocrystalline counterpart, allowing for a significant improvement in the characteristics of solar cells fabricated based on it [

47,

48,

49].

The present study introduces a cost-effective approach for synthesizing high-quality β-SiC films on silicon substrates, utilizing a porous silicon (por-Si) intermediary buffer layer.

Using the electrochemical etching technique, the methodology begins by establishing a porous layer on the monocrystalline silicon surface. This method possesses distinct economic advantages such as reduced material wastage, lower energy consumption, and a minimal requirement of specialized equipment. Furthermore, the electrochemical etching process can be precisely controlled to produce uniform pores, thus reducing the need for additional post-processing or treatments. Considering these benefits, electrochemical etching can be up to 40–60% more cost-effective compared to other pore-formation methods.

The subsequent growth of SiC is facilitated by rapid thermal vacuum carbonization. Including the buffer porous layer is pivotal for attaining a pristine silicon carbide film.

Regarding material safety, both silicon and silicon carbide stand out for their benign nature. Silicon, a primary component of the Earth’s crust, is non-toxic and abundantly available. Silicon carbide, similarly, is considered environmentally friendly and non-toxic compared to other semiconductors that are frequently employed in solar cells, such as cadmium telluride or copper indium gallium selenide, which have raised environmental and health concerns. This inherent non-toxicity of the β-SiC/por-Si/mono-Si heterostructure materials emphasizes their suitability for sustainable and eco-friendly solar cell applications.

Given the economic and environmental merits, the β-SiC/por-Si/mono-Si heterostructure demonstrates significant potential as an advanced and viable material for use in solar cell applications. The novelty of our work lies in using a porous buffer layer, which not only facilitates the growth of high-quality silicon carbide films but also enhances the adhesion and structural integrity of the resulting heterostructure. Consequently, this new approach reduces production costs and yields a high-quality heterostructure with excellent electronic properties, making the β-SiC/por-Si/mono-Si heterostructure a promising material for application in solar cells.

2. Materials and Methods

2.1. Samples for the Experiment

A monocrystalline Si of n-type conductivity was utilized for the experiment, doped with phosphorus to a concentration of 1.8 × 1017 cm−1. Plates oriented as (111) with dimensions of 1 × 2 × 0.2 cm were employed.

2.2. Electrolytes, Precursors, and Equipment

For the electrochemical modification of the silicon substrate, an initial step involved the removal of the native oxide passivating layer. This procedure was accomplished through electrochemical etching using a hydrochloric acid (HCl) solution. The experimental setup included a standard three-electrode electrochemical cell. Within this configuration, a platinum electrode served as the counter electrode, while a silver–silver chloride electrode acted as the reference.

To augment the efficiency of the etching process, the electrochemical cell was equipped with two additional subsystems. Firstly, an air-blowing module was incorporated to eliminate the formation of oxygen bubbles on the sample surface that could otherwise hinder the etching process. Second, an electrolyte stirring mechanism was added to ensure uniform electrolyte distribution and consistent etching across the substrate.

After removing the oxide layer, the next phase involved the formation of a porous silicon layer. This was achieved through electrochemical etching in a hydrofluoric acid (HF) solution within the same electrochemical cell. The electrolyte was maintained at room temperature during this stage of the procedure. The etching was conducted under ambient lighting conditions and did not require specialized environmental controls.

Post-etching, the samples underwent a drying process within a SNOL 58/350 muffle furnace to remove any residual moisture and to prepare their surfaces for subsequent procedures.

Finally, the silicon carbide layer was synthesized using a Jipelec JetFirst-100 oven. A methane (CH4) gas precursor was deployed for this purpose, facilitating the formation of Si-C bonds and thereby culminating in the growth of a high-quality SiC layer.

All chemicals utilized were procured from Spetsprompostach LLC. The hydrochloric HCl and HF acids were of analytical grade (ARG, 99.8%), indicating a high purity level suitable for analytical applications and ensuring minimal interference from impurities during the electrochemical etching processes. The silicon (Si) substrate was of semiconductor grade, a designation for materials with controlled and specified impurity levels to ensure optimal electrical conductivity and functionality in semiconductor applications. Methane (CH4), which was utilized to synthesize the silicon carbide layer, was of ultra-high purity (UHP) grade with a purity level of 99.995%, ensuring the high-quality synthesis of the SiC layer.

2.3. Experiment Steps

The experiment was conducted in several stages, specifically:

Stage 1—Formation of the porous Si layer;

Stage 2—Removal of reaction products from the sample surface;

Stage 3—Formation of the SiC layer;

Stage 4—Post-processing of the samples.

Detailed experimental stages are provided below.

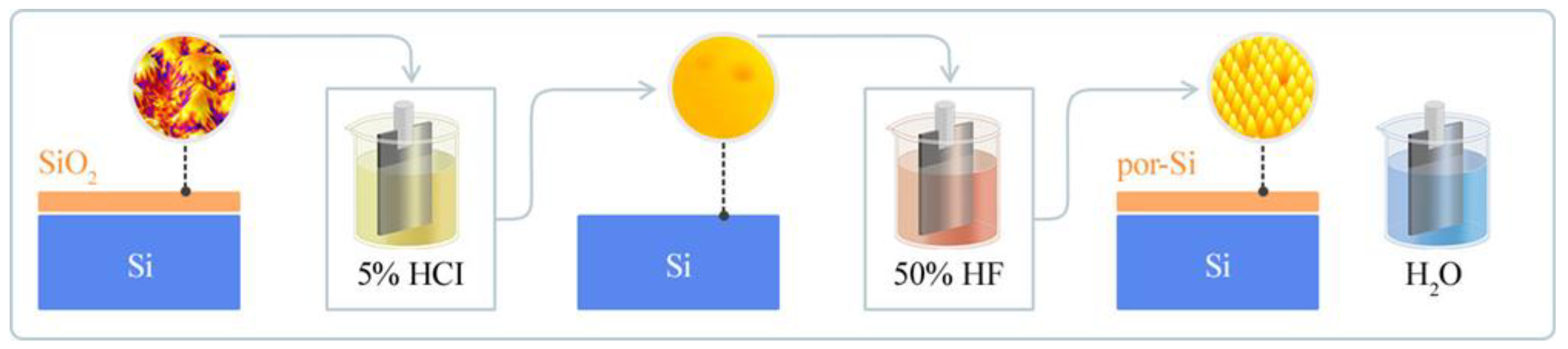

2.3.1. Stage 1. Electrochemical Etching in Acid Solutions

The preliminary phase of the experimental procedure focused on the meticulous preparation of the monocrystalline silicon (mono-Si) surface to render it amenable for silicon carbide (SiC) layer formation. A point of concern in semiconductor processing is the natural tendency of the silicon surface to oxidize following mechanical operations such as grinding and polishing. This oxidation forms a thin, amorphous oxide layer documented to expedite the device degradation rate and pose challenges in further fabrication steps [

50,

51]. Therefore, it is imperative to effectively remove this passivating oxide layer to preserve the monocrystalline silicon substrate’s intrinsic properties and facilitate subsequent process steps [

52,

53].

To further facilitate the quality of SiC films, a strategic approach involves formulating a textured or porous silicon layer on the monocrystalline silicon surface. These specially engineered buffer layers act as a soft substrate, addressing and alleviating the perennial lattice mismatch between the SiC film and the mono-Si substrate. The resulting architecture diminishes the manifestation of elastic stresses at the interface, thereby potentially enhancing the SiC films’ overall quality and reprehensive understanding and repeatability. The specific conditions under which this initial phase of the experiment was conducted are systematically documented in

Table 1, while the accompanying

Figure 1 provides a visual representation to aid interpretation.

A standard three-electrode cell ensemble was employed in the electrochemical etching process utilized for both the removal of oxide and the formation of a porous layer on the monocrystalline silicon substrate. In the initial sub-stage (1.1), a potential of 2V was applied for 3 min in a 5% HCl solution to facilitate the removal of the oxide layer. Subsequently, in the second sub-stage (1.2), the porous silicon layer was formed by applying a potential of 5V for 7 min in a 50% HF solution. This higher potential drove the electrochemical etching of the silicon substrate, inducing porosity. The specific current during these processes was not fixed but could fluctuate to maintain the set potential, ensuring that the desired electrochemical reactions occurred. The final sub-stage (1.3) involved rinsing the silicon substrate in water to remove any reaction products from the surface, setting the stage for subsequent procedures. Through this systematic electrochemical etching process, the silicon substrate was adequately prepared to synthesize the silicon carbide layer, addressing the inherent challenges associated with the lattice mismatch and the passivating oxide layer.

2.3.2. Stage 2. Removal of Moisture Residues and Reaction Products from the Sample Surface

The second stage of the experimental process was engineered to meticulously remove moisture residues and byproducts from the treated surface of the porous silicon (por-Si) sample. Such procedural steps are integral to ensure an uncontaminated substrate for subsequent silicon carbide (SiC) film formation. To achieve this, samples were subjected to a tightly controlled drying sequence in a SNOL 58/350 oven, characterized by three discrete sub-stages delineated by specific durations and temperatures as outlined in

Table 2.

Table 2 comprehensively summarizes the conditions and sub-stages: starting with a 180-min treatment at 150 °C, followed by 60 min at 300 °C and then 400 °C. The judiciously selected time and temperature parameters were optimized to remove any vestigial moisture residues without adversely affecting the integrity of the por-Si substrate.

Initiating the SiC film formation immediately after this stage was paramount to mitigate the potential of the sample oxidation processes post-drying. Thus, the transition to the SiC film formation was executed without delay to maintain a contiguous processing flow.

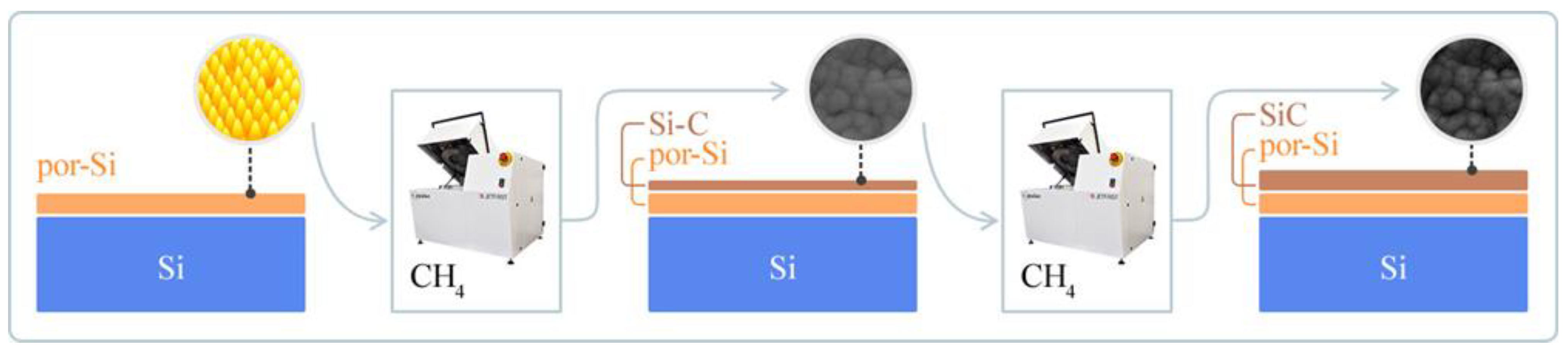

2.3.3. Stage 3. Thermal Deposition and SiC Film Formation

Employing rapid thermal vacuum carbonization as our deposition technique, we used methane (CH

4) as the precursor material (

Figure 2). The procedure was bifurcated into two temporal series, each encapsulating a duration of 60 s and punctuated by a 2-min hiatus, a design choice strategically deployed to allow for the chamber’s re-equilibration. As can be seen in

Table 3, the process underwent a rapid temperature ramp from an initial 50 °C to a final state of 900 °C, conducted under a controlled vacuum pressure of 1 × 10

−2 Pa.

The rapid thermal vacuum carbonization technique was chosen for its proven ability to produce high-fidelity SiC films with minimized defect density, offering a potential solution to inherent fabrication challenges. This process involves an instantaneous elevation in temperature, designed to expedite deposition while suppressing the possible formation of undesirable phases or defects. The constant pressure conditions in the reaction chamber also serve as a critical parameter to inhibit unwanted chemical reactions, thereby promoting stoichiometric fidelity in the resulting SiC films.

2.3.4. Stage 4. Post-Processing of the β-SiC/Por-Si/Mono-Si Heterostructure

For Stage 4, post-processing procedures were initiated to stabilize the formed β-SiC/por-Si/mono-Si heterostructures. The post-processing primarily aimed to eliminate weakly adhered atoms and extraneous byproducts of the deposition process.

Table 4 outlines the conditions: firstly, chemical etching was applied using a 2% HCl solution for 20 min at ambient temperature to remove oxides and other residual compounds. Secondly, thermal annealing was performed in a nitrogen atmosphere for 90 min at 150 °C to relieve residual stresses and improve crystallinity.

After completing the aforementioned stages, the samples were allowed to rest in an open-air environment for 90 days. This time frame was sufficient for fully assessing the samples’ long-term structural stability and integrity.

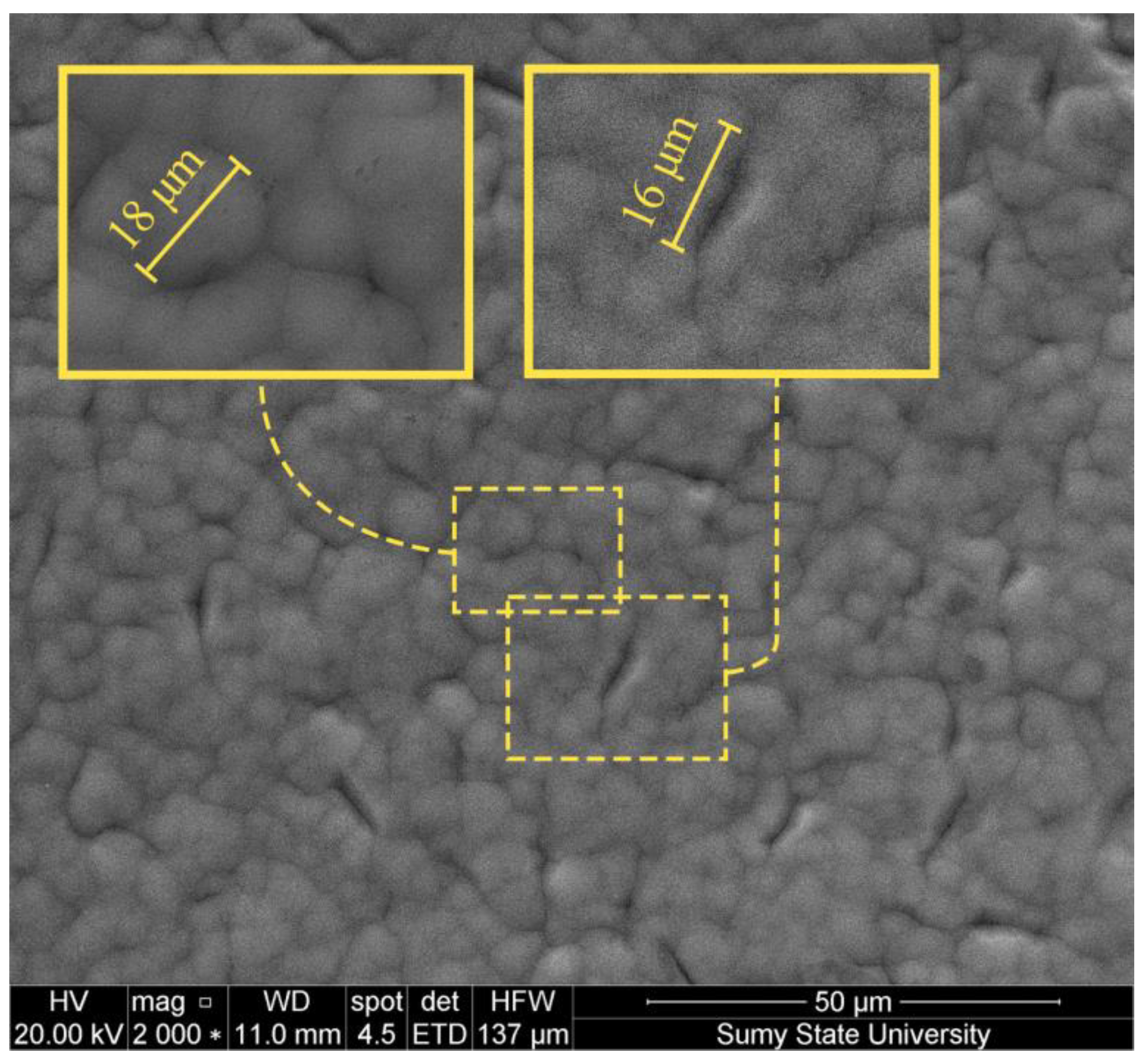

2.4. Characterization

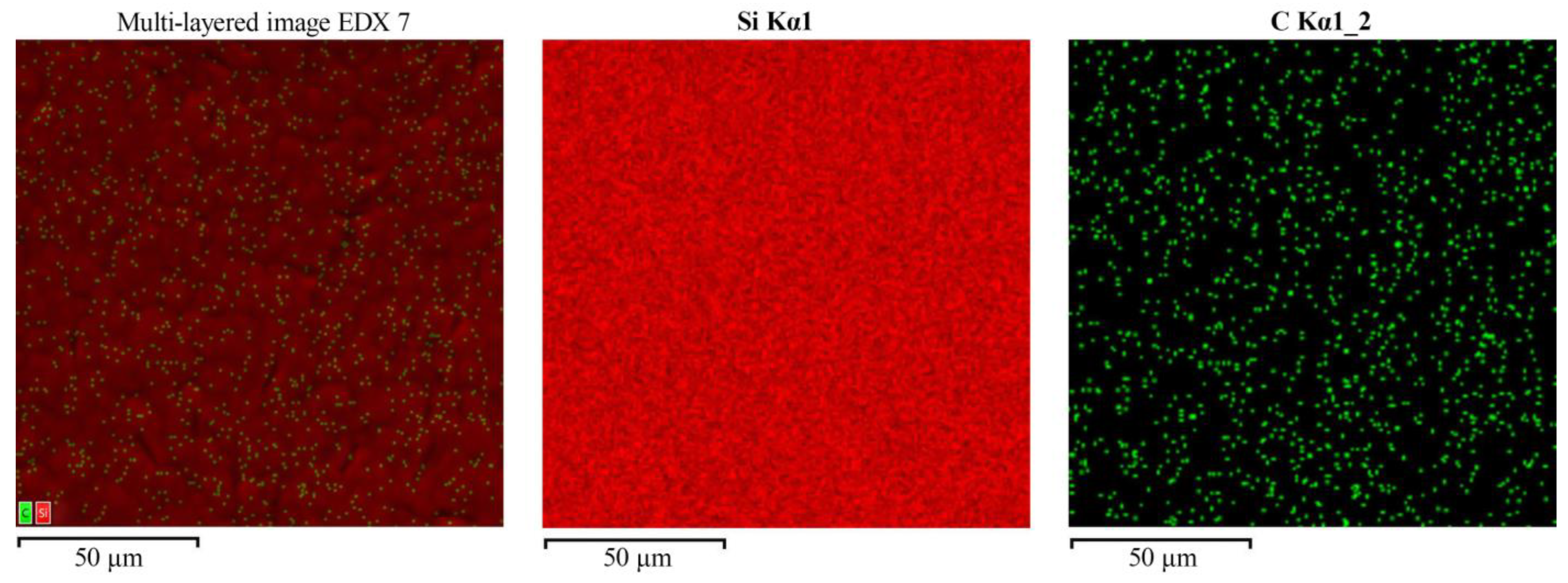

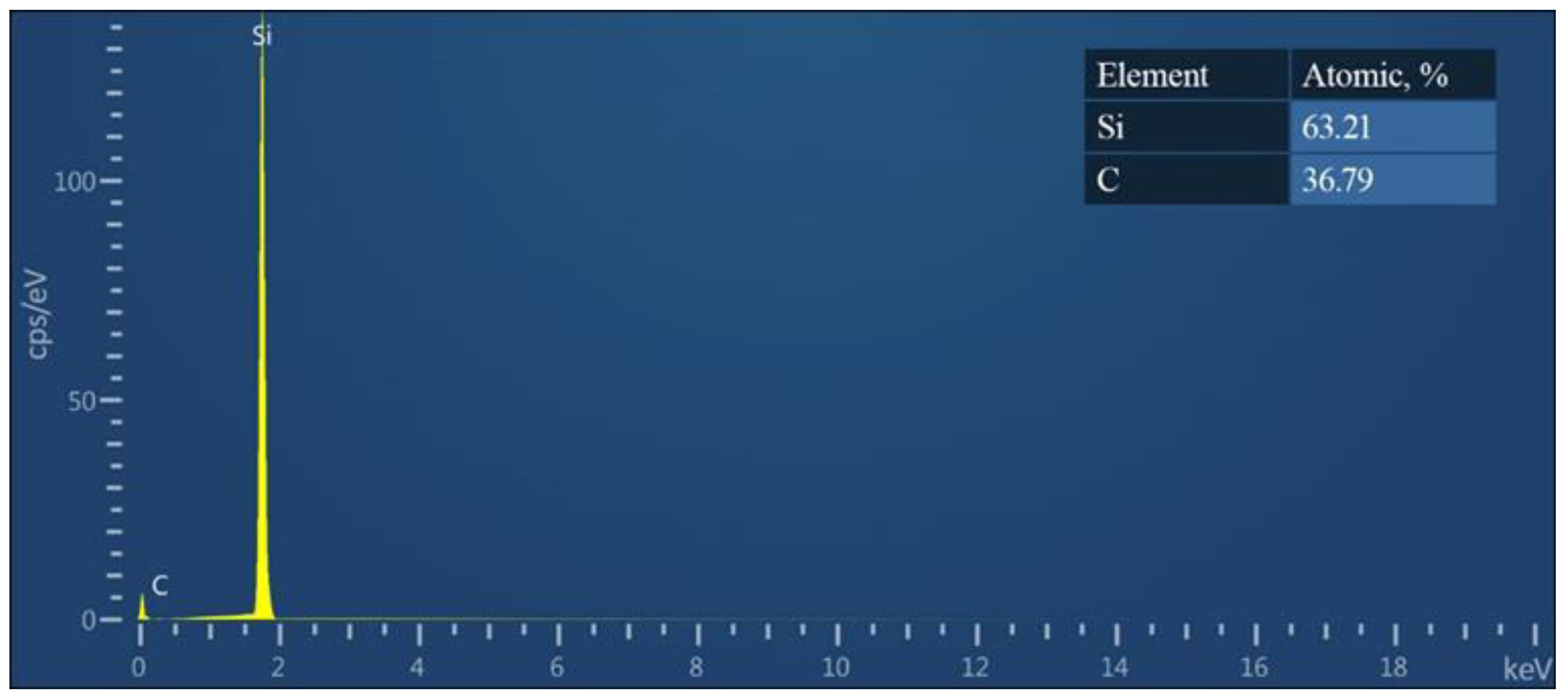

The structural features of the SiC films were comprehensively analyzed using scanning electron microscopy (SEM), carried out with an SEO-SEM Inspect S50-B microscope (Fei Company, Hillsboro, OR, USA). X-ray diffraction methods were also employed, utilizing a Dron–3M device with CuKα radiation (Sumy State University, Sumy, Ukraine). Energy dispersive spectroscopy (EDS) was executed to elucidate the elemental composition, facilitated by an AZtecOne spectrometer (Oxford Instruments, Abingdon, UK).

4. Discussion

One of the formidable challenges encountered in the epitaxial growth of silicon carbide (SiC) films on silicon (Si) substrates lies in the substantial presence of packing defects, as corroborated by the existing literature [

56,

57]. Such defects can be particularly detrimental, as they precipitate a breakdown under the application of high electric fields, thereby undermining the functional integrity of the device. The etiology of these packing defects can be primarily ascribed to the lattice mismatch between the SiC film and the silicon substrate [

58].

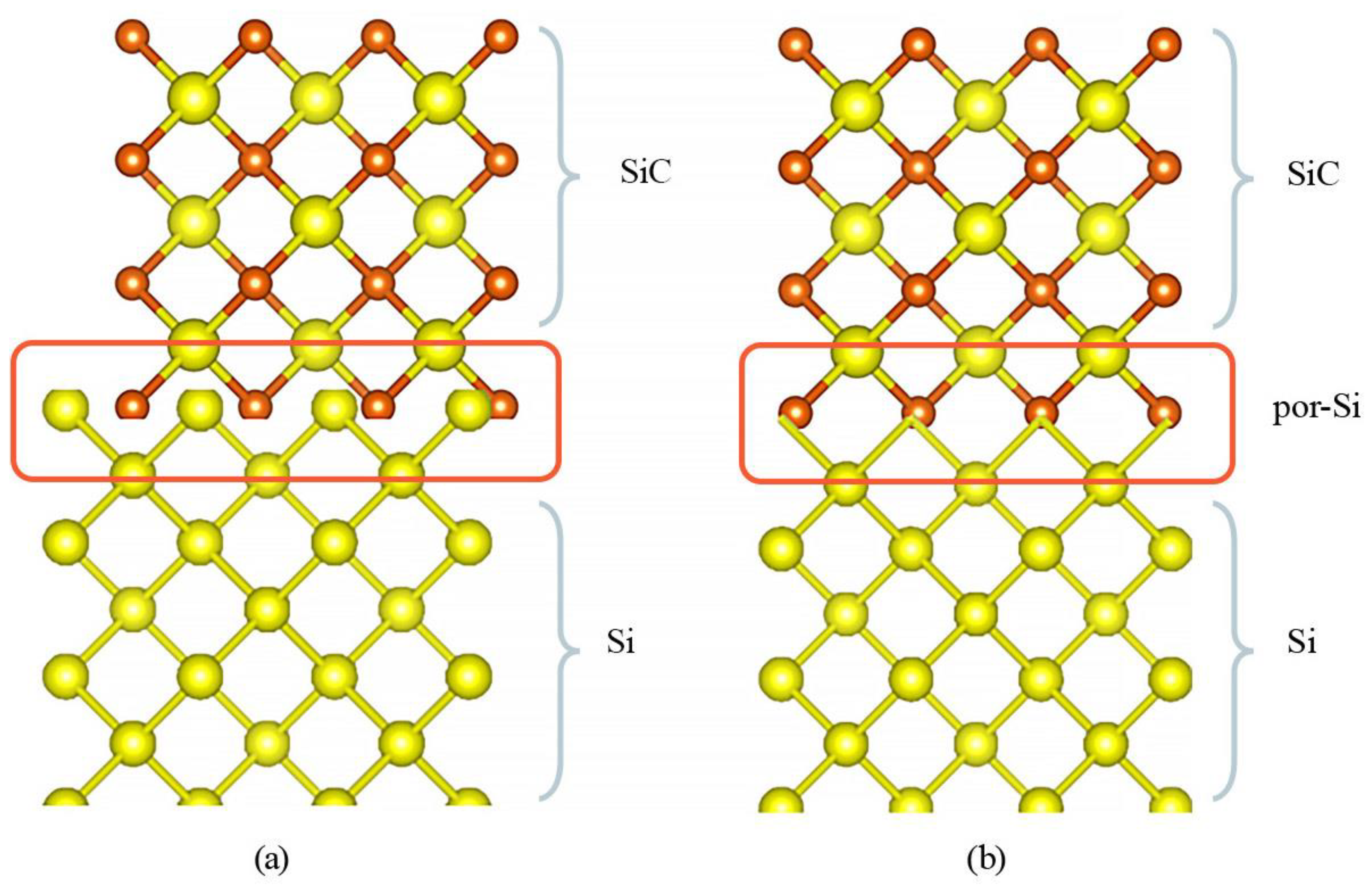

To offer a nuanced understanding of this phenomenon,

Table 6 presents the lattice parameters for both monocrystalline silicon and silicon carbide [

59]. While both of these semiconductors crystallize in the cubic crystal system, their lattice parameters and unit-cell volumes exhibit pronounced disparities. These differences, although subtle, often translate into significant mechanical stress during the growth of SiC films on monocrystalline silicon substrates. The inherent tension culminates in defect formations and compromises the film’s overall quality (as illustrated in

Figure 9a).

A promising approach to alleviate these issues involves creating a porous layer on the silicon substrate, before SiC deposition. As depicted in

Figure 9b, this porous layer can serve as a mechanical buffer, effectively mitigating the excessive elastic pressures that typically arise due to lattice mismatches. The porous architecture essentially functions as a “soft” substrate, facilitating more harmonious integration of SiC with the underlying silicon.

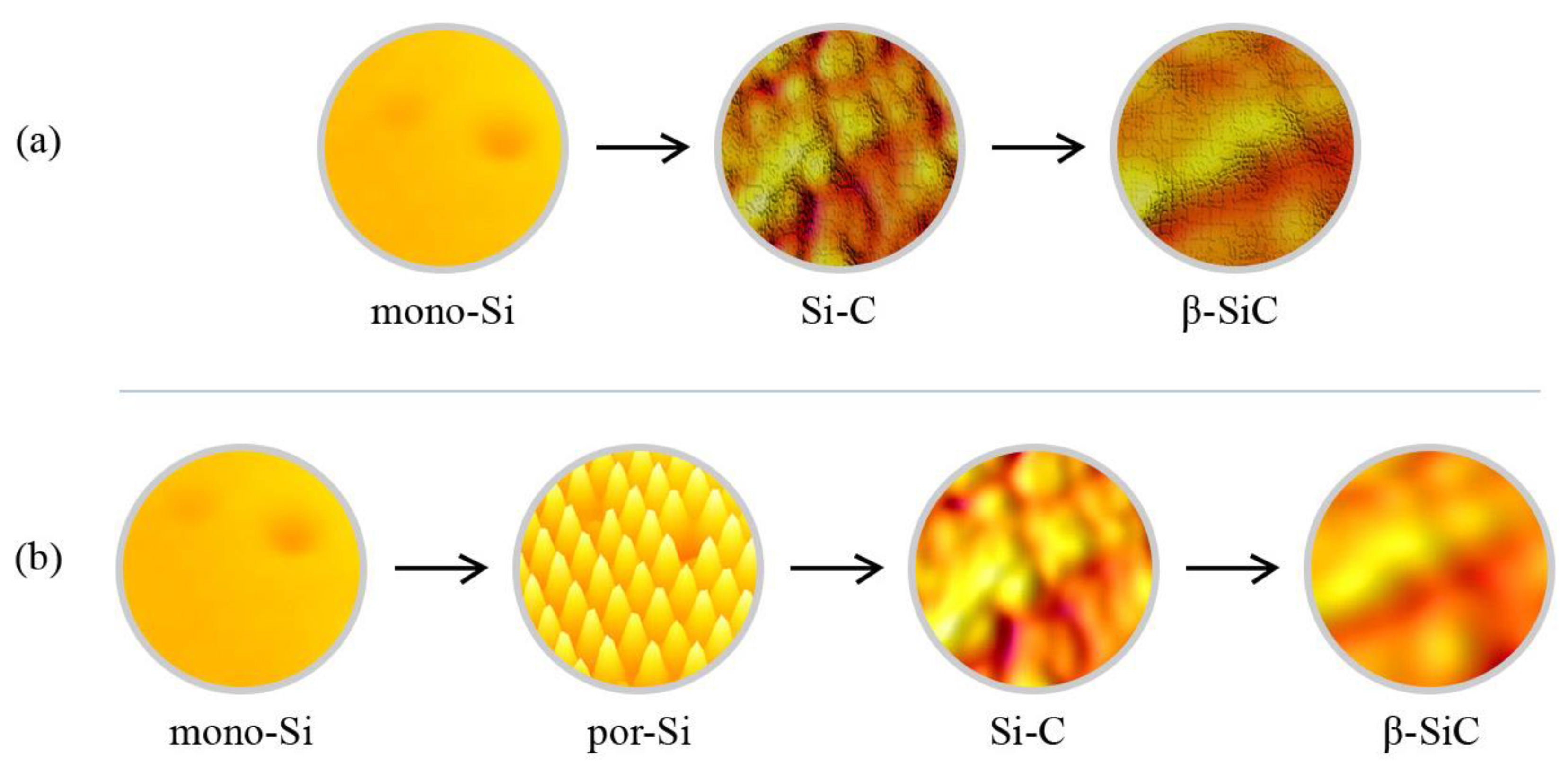

Figure 10 represents the SiC film growth on mono-Si (

Figure 10a) and por-Si (

Figure 10b) substrates. In

Figure 10a, the progression from pure mono-Si to a rougher β-SiC film signifies strain due to lattice mismatches. Conversely, in

Figure 10b, the por-Si begins with a structured porous surface, and as SiC deposition occurs, it shows a smoother β-SiC film, underscoring the stress-buffering capacity of the porous architecture. This improved consistency in

Figure 10b illustrates enhanced film–substrate adhesion and provides empirical support to the viability of the por-Si approach in addressing lattice mismatch challenges.

The lattice mismatch between SiC and Si serves as a fundamental bottleneck in achieving high-quality epitaxial films. However, incorporating a porous buffer layer presents a feasible solution to this problem, as it allows for better stress distribution and enhanced adhesion, ultimately forming superior-quality SiC films.

In conventional thermal methods for forming silicon carbide (SiC), carbon atoms are chemically bonded to silicon atoms by forming Si-C covalent bonds [

60,

61]. However, a challenge arises when considering the surface properties of monocrystalline silicon (mono-Si), which inherently possesses a smooth topology. Due to the natural occurrence of auto-passivation facilitated by silicon dioxide, monocrystalline silicon surfaces tend to have minimal atoms with dangling or broken bonds [

62]. Consequently, this surface morphology impinges upon the efficacy of most traditional techniques for the epitaxial growth of SiC films on mono-Si substrates.

The SiC films grown on such smooth mono-Si substrates are often fraught with many imperfections, both on the surface and within the bulk material. These defects manifest in various forms, including dislocations, stacking faults, and film cracking, as illustrated in

Figure 10a. The cracks compromise the mechanical and electronic properties of the material, significantly limiting its application potential.

Contrastingly, when pre-formed on the mono-Si surface, a porous silicon (por-Si) layer offers a more amenable substrate for SiC film growth. The surface of porous silicon is characterized by a rough, textured morphology, depicted in

Figure 10b. This textural variation in por-Si is crucial: it engenders micro-protrusions or elevated zones interspersed between the pores. These micro-protrusions act as localized sources of silicon atoms, which can readily bond with incoming carbon atoms during SiC film formation.

The intricate porous architecture thus plays a dual role; first, it provides a multitude of nucleation sites that better facilitate the formation of Si-C bonds, and second, it introduces a level of surface roughness that enhances the mechanical interlocking between the SiC film and the underlying silicon substrate. The result is the formation of a high-quality crystalline β-SiC film, which benefits from reduced defects and superior bond strength.

It is imperative to highlight that the properties and applications of porous silicon as a substrate have been the subject of extensive academic investigations [

63,

64,

65]. These studies underscore the porous structure’s instrumental role in mitigating challenges associated with SiC film growth on monocrystalline silicon, thereby contributing to improved SiC/mono-Si heterostructures.

In summary, while the surface characteristics of monocrystalline silicon have traditionally posed limitations on the growth of defect-free SiC films, introducing a porous silicon layer offers an effective countermeasure. This adaptability can pave the way for developing high-quality SiC films, an area of ongoing research and technological importance.

Many mechanisms have been elucidated in film formation on semiconductor substrates to govern the deposited films’ growth kinetics and morphological evolution. Among these, the paradigms established by Frank–van der Merwe [

66,

67], Volmer–Weber [

68,

69], and the Stranski–Krastanov mechanism [

70,

71] stand out as seminal frameworks.

In the context of the Frank–van der Merwe mechanism, also known as layer-by-layer growth, we observe a unique phenomenon primarily in systems where the film’s and substrate’s crystalline lattice parameters exhibit minimal discrepancy [

72,

73]. This leads to the formation of what is colloquially termed a “wetting layer,” characterized by the sequential deposition of monatomic layers on the substrate. This mechanism is typically operative when the thermodynamic factors favor minimizing surface and interfacial energies.

Conversely, the Volmer–Weber mechanism is observed in instances with pronounced lattice mismatch between the substrate and the film. Such discrepancies promote the growth of isolated islands on the substrate, negating the formation of an initial wetting layer. The Volmer–Weber mode is driven by the system’s need to minimize the strain energy, which leads to a preferential aggregation of atoms into islands rather than a uniform film.

Situated as an intermediate regime between these two is the Stranski–Krastanov mechanism. In this model, the early stages of the film growth process resemble the Frank–van der Merwe mechanism, characterized by establishing an initial wetting layer [

74]. However, owing to a slight lattice mismatch, elastic deformations begin to manifest. These deformations induce compressive stresses in the film, ultimately resulting in the nucleation and growth of three-dimensional, rounded islands atop the wetting layer.

Turning our attention to the growth of silicon carbide (SiC) on silicon (Si) substrates, it becomes evident that the porous silicon (por-Si) layer significantly eases the challenges associated with lattice mismatch, as depicted in

Figure 9b. Our findings point to the applicability of the Stranski–Krastanov mechanism in this particular heterostructure. This observation substantiates the role of por-Si as a buffer layer, serving as an effective stress-relief intermediary that accommodates the lattice discrepancies between SiC and Si.

Hence, we have presented a facile yet robust methodology for SiC film growth that deftly addresses the perennial technological constraints of lattice mismatch and the compromised crystalline quality of SiC films. Introducing a por-Si buffer layer acts as a catalyst in optimizing the epitaxial growth process of SiC on silicon substrates. The buffer layer’s role is pivotal, warranting further exploration for future refinements in the growth methodology. Subsequent research endeavors may be directed towards achieving complete carbide formation in SiC/Si structures and the potential for developing graphene layers on the surface of these heterostructures.

Through this multi-faceted analysis, we aim to contribute to the empirical knowledge pool of SiC film growth and broader efforts aimed at technological advancements in semiconductor applications.

5. Conclusions

The current study meticulously elaborates on an enhanced methodology for synthesizing β-SiC films on silicon substrates by judiciously integrating porous silicon (por-Si) as an intermediary buffer layer. Incorporating this buffer layer culminates in augmented adhesion between the SiC film and the mono-Si substrate. The resultant layered material thus manifests as a hybrid heterostructure of β-SiC/por-Si/mono-Si, with implications for advancing the state of the art in semiconductor technologies.

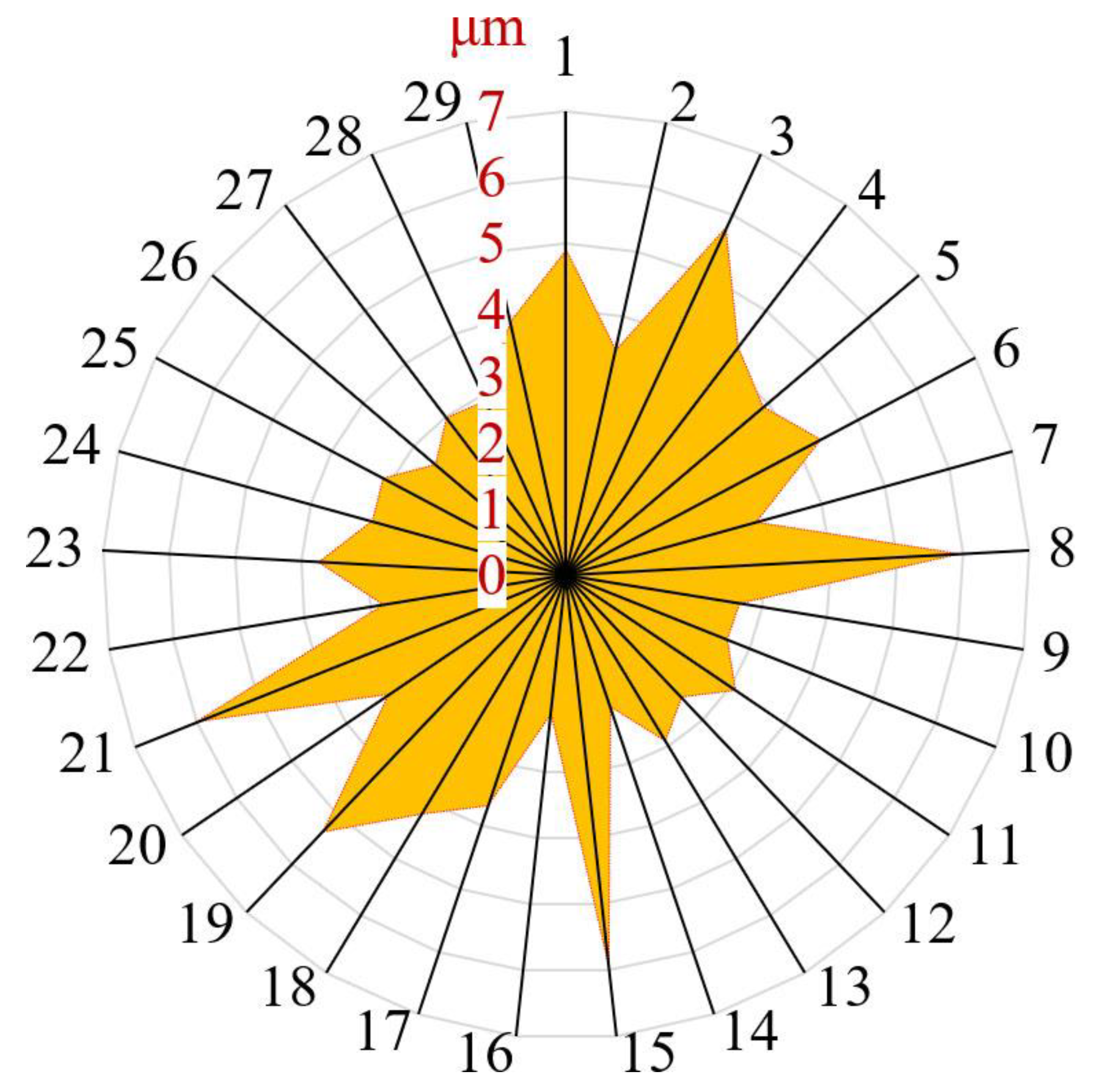

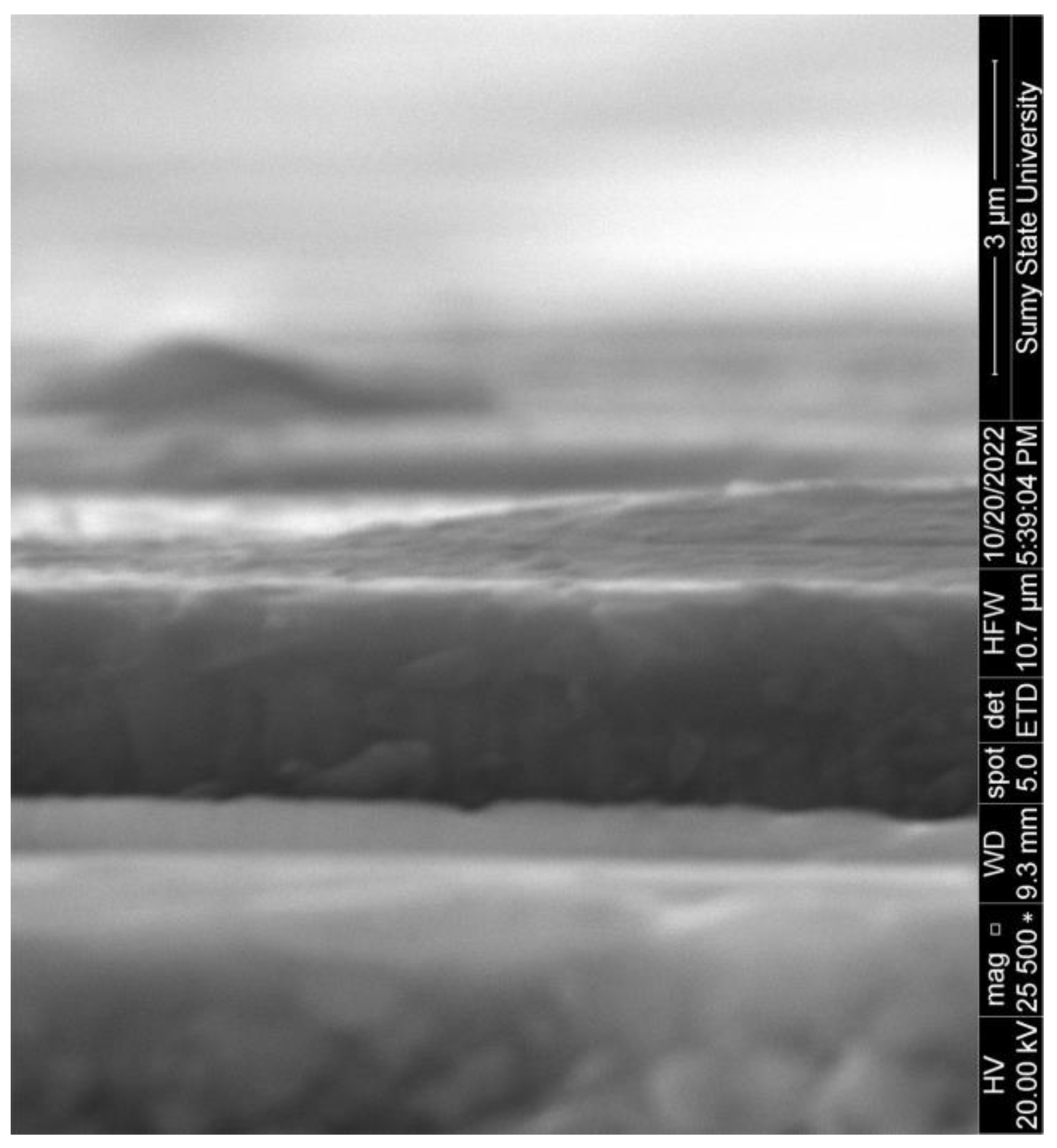

Examinations of the surface morphology via advanced imaging techniques revealed that the synthesized SiC film predominantly consists of island agglomerates with diametric dimensions ranging from 2 to 6 μm. Further intricate features, such as minuscule pores with sizes varying between 70 and 80 nm, were discerned on the islands’ surfaces. Such topological attributes point to an intricate interface interaction and might have ramifications on the mechanical and electronic properties of the resulting heterostructure.

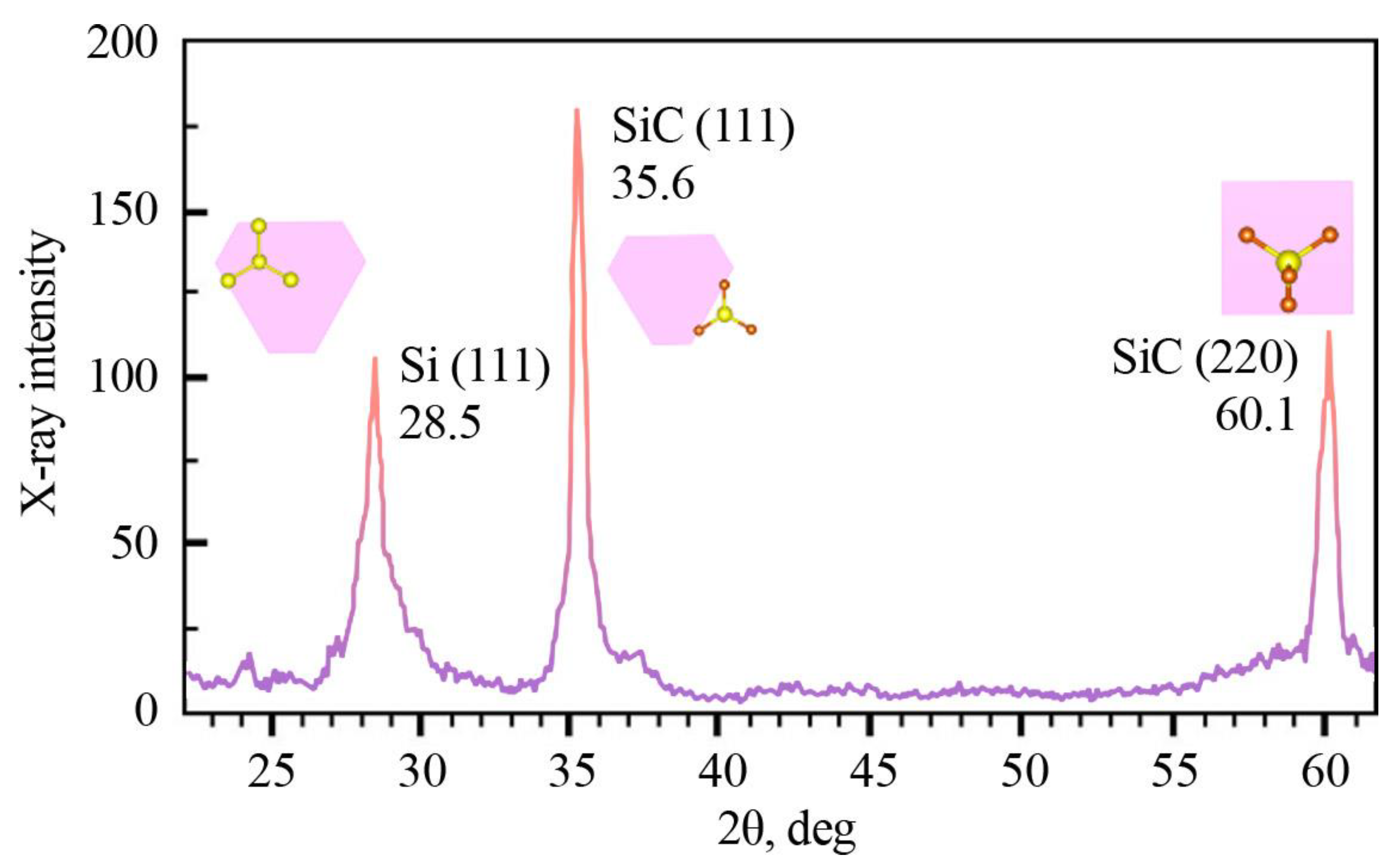

The X-ray Diffraction (XRD) analysis of the synthesized β-SiC/por-Si/mono-Si heterostructure exhibited three distinct peaks at angular positions (2θ) of 28.5°, 35.6°, and 60.1°. These peaks unequivocally correspond to the crystallographic orientations (hkl) of (111) and (220) for silicon (Si) and silicon carbide (SiC) in their cubic symmetry, respectively. This indicates the formation of high-quality crystalline structures. When juxtaposed with the standard peak positions for crystalline silicon, a noticeable shift toward lower angles was observed, particularly in the peak at 2θ = 35.6°. This shift, which represents a deviation from the typical diffraction patterns of bulk silicon, is indicative of quantum size effects. Such effects are consistent with the presence of nanometer-sized objects, as confirmed by Scanning Electron Microscopy (SEM) analyses.

Furthermore, the intensity and uniqueness of the peak at an angular position of 2θ = 35.6°, which aligns with the characteristics of β-SiC in a zinc-blende-type lattice, emphasize the impeccable crystallinity of the SiC layers. The absence of other intense peaks serves as further evidence for this claim, suggesting that the resultant heterostructure retains high structural integrity.

The prospects emerging from our research are expansive. The SiC/por-Si/mono-Si heterostructure promises to revolutionize next-generation electronic devices, given the superior electron mobility and thermal resilience of SiC. In optoelectronics, the heterostructure’s unique electronic and optical attributes could spearhead the development of advanced devices such as photodetectors and light-emitting diodes. Furthermore, the chemical robustness of SiC offers avenues for its adoption in advanced sensing technologies, especially in challenging environments. The juxtaposition of SiC’s admirable thermal conductivity with por-Si’s insulating characteristics paves the path for innovative thermal management solutions for electronic apparatuses. Additionally, the observed quantum size effects signal potential applicability in the burgeoning arena of quantum computing, wherein meticulous control over nanoscale entities is vital.

It is crucial to acknowledge that, while our methodology offers a substantial improvement in overcoming lattice mismatch and adhesion issues that plague the conventional SiC film synthesis on silicon substrates, further research endeavors are requisite. These could include optimizing porosity levels in the buffer layer, a comprehensive assessment of mechanical properties under variable thermal and electrical conditions, and investigating the potential utility of this heterostructure in electronic and optoelectronic applications.

Conclusively, the present study augments the existing body of knowledge by elucidating an efficient, scalable technique for synthesizing high-quality β-SiC films on silicon substrates. The findings portend significant technological benefits and set the stage for subsequent research to refine and expand the application scope of SiC/por-Si/mono-Si heterostructures.