Dynamic Analysis of Extendable Hybrid Voltage Lift DC–DC Converter for DC Microgrid

Abstract

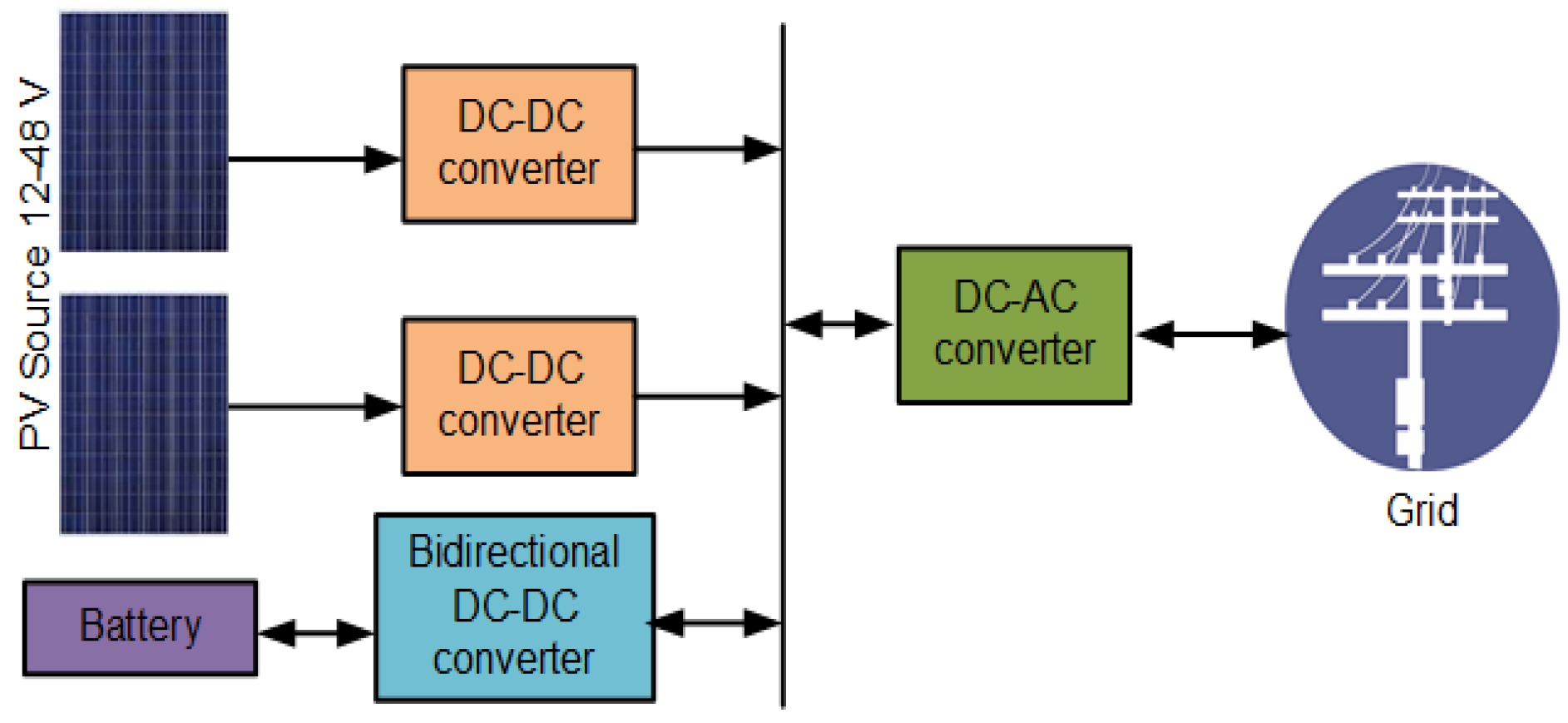

:1. Introduction

- Single switch converter with reduced complexity for controller design.

- Less number of passive components, which reduces the volume of the converter.

- Low voltage stress, which reduces the conduction loss and cost of the converter.

- Output diode voltage stress is less than the output voltage, which minimizes the cost.

- Efficiency is higher due to fewer component counts.

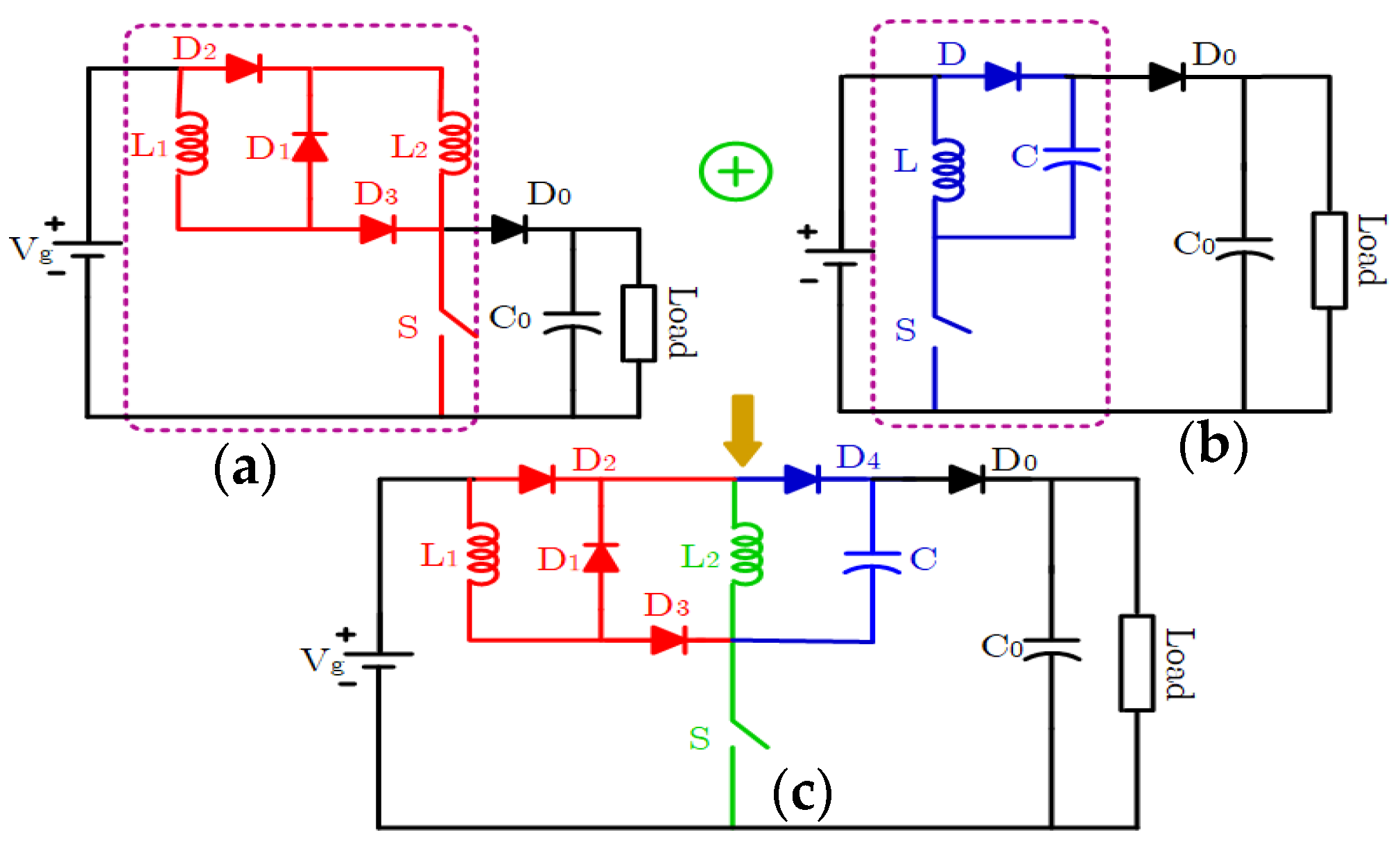

2. Proposed High Voltage DC–DC Converter

2.1. Description of Proposed HSIVL Topology

- The voltage gain is high compared to super-lift boost and elementary Luo converter.

- The switch voltage stress is not equal to the output voltage, which reduces the Rds (on) and increases the efficiency of the converter.

- Extension of the voltage gain is feasible without increasing the power switch count.

2.2. Modes and Operating Principle of the HSIVL Topology

2.2.1. Mode I

2.2.2. Mode II

2.2.3. Mode III

3. Steady-State Analysis

3.1. Continuous Conduction Mode

3.2. Stress across the Semiconductor Devices

3.3. Stress across the Passive Components across the Semiconductor Devices

4. Discussion

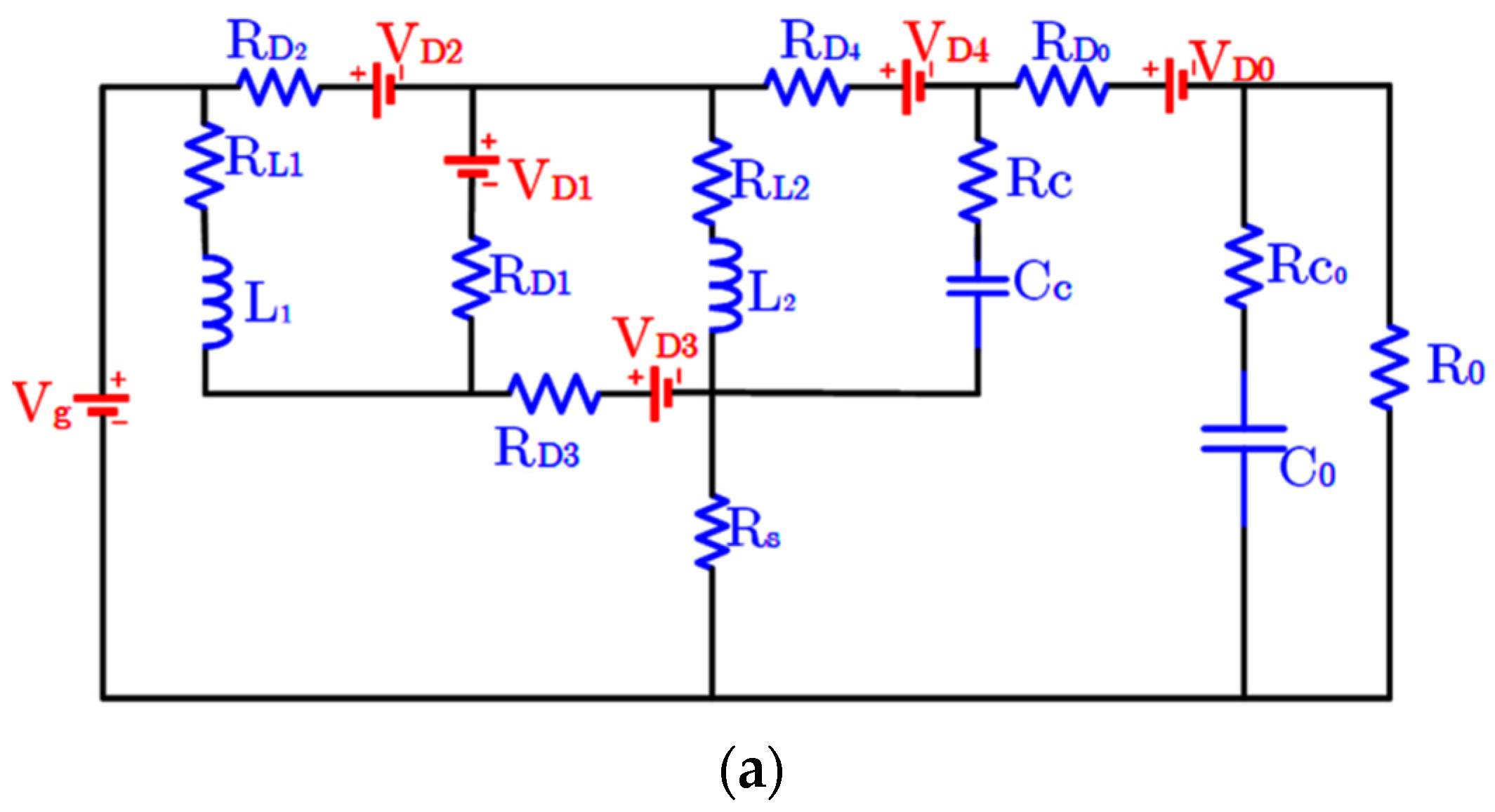

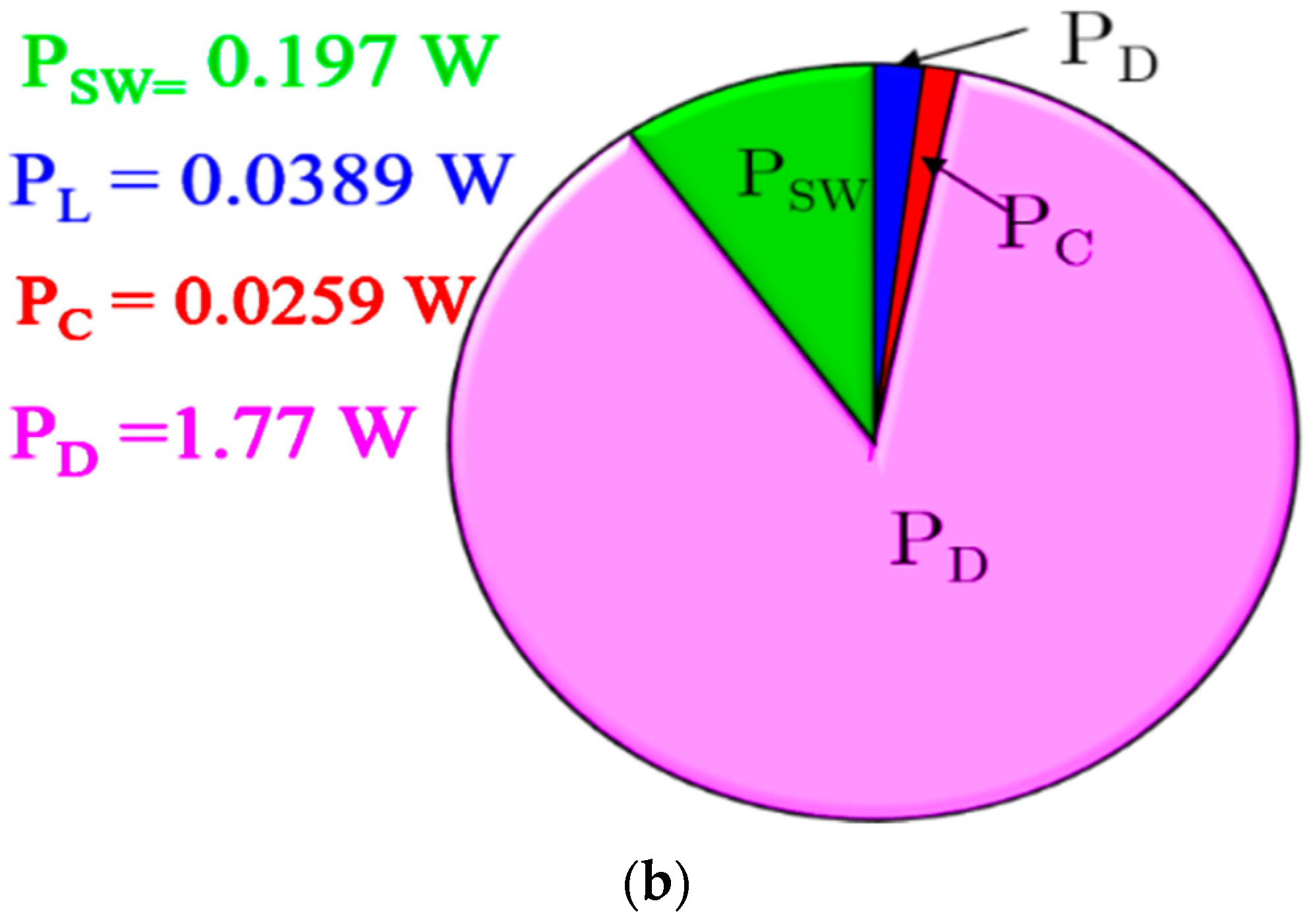

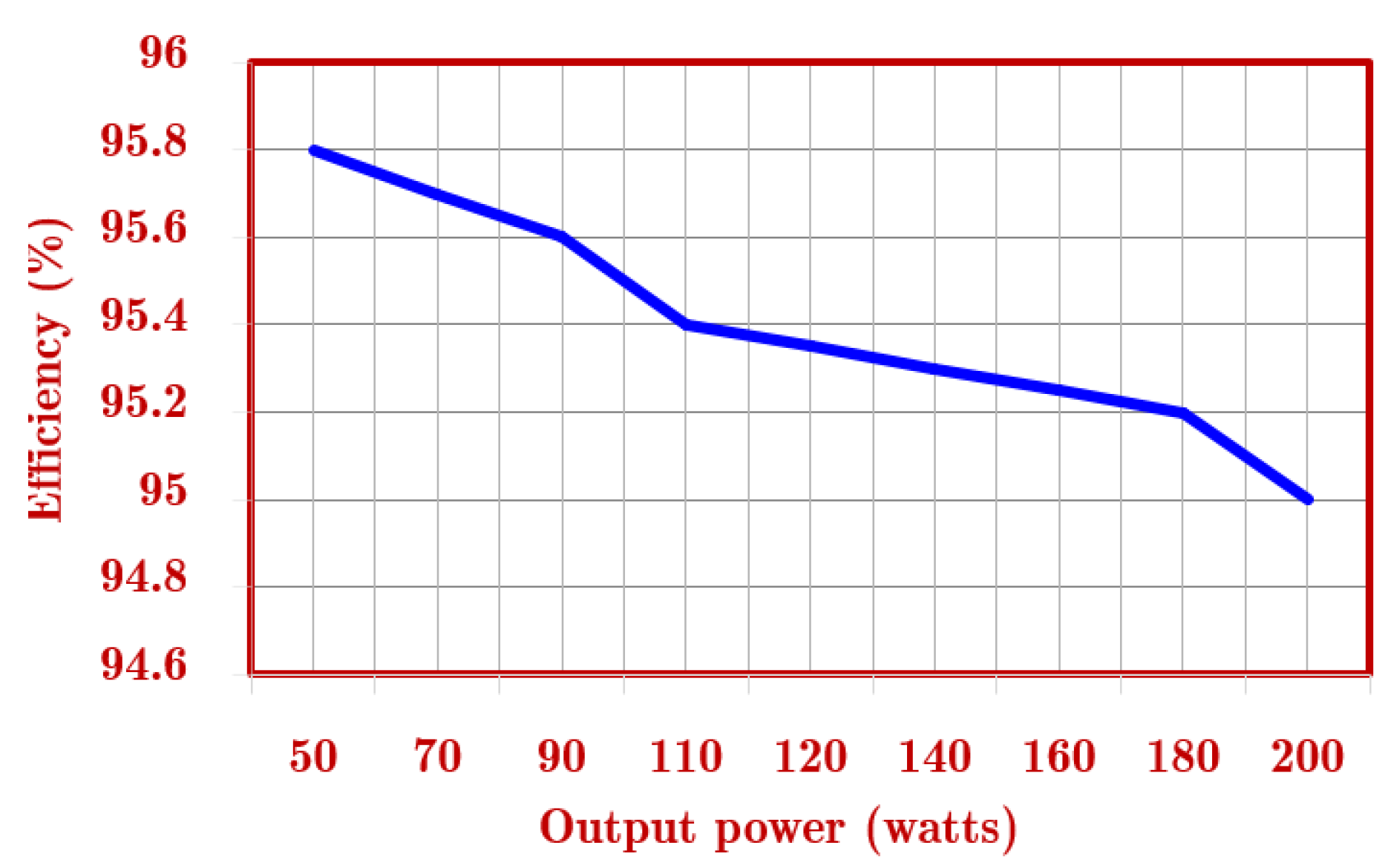

5. Efficiency Analysis

6. Dynamic Analysis of the Converter

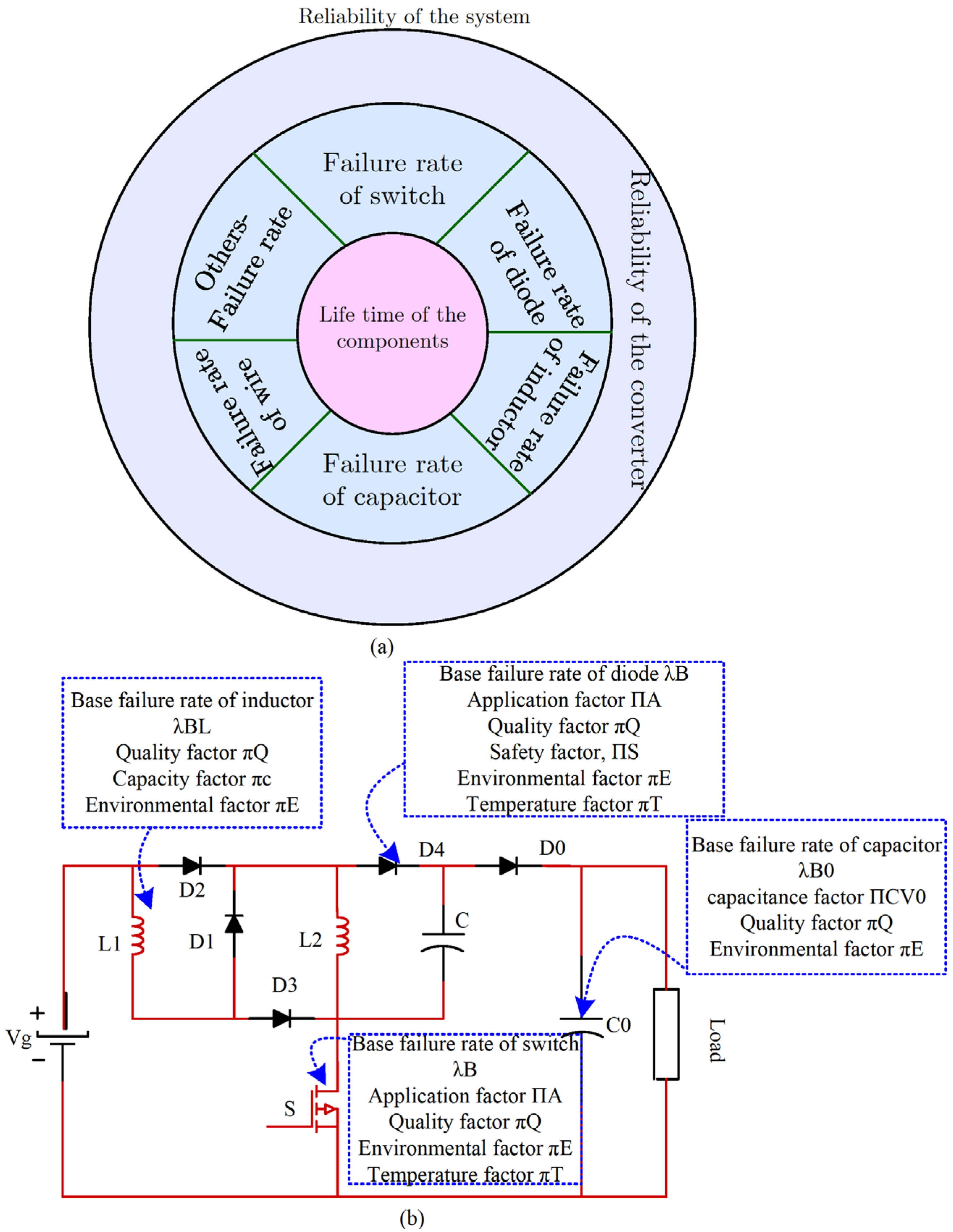

7. Reliability Analysis

7.1. Factors Affecting the Converter’s Lifetime

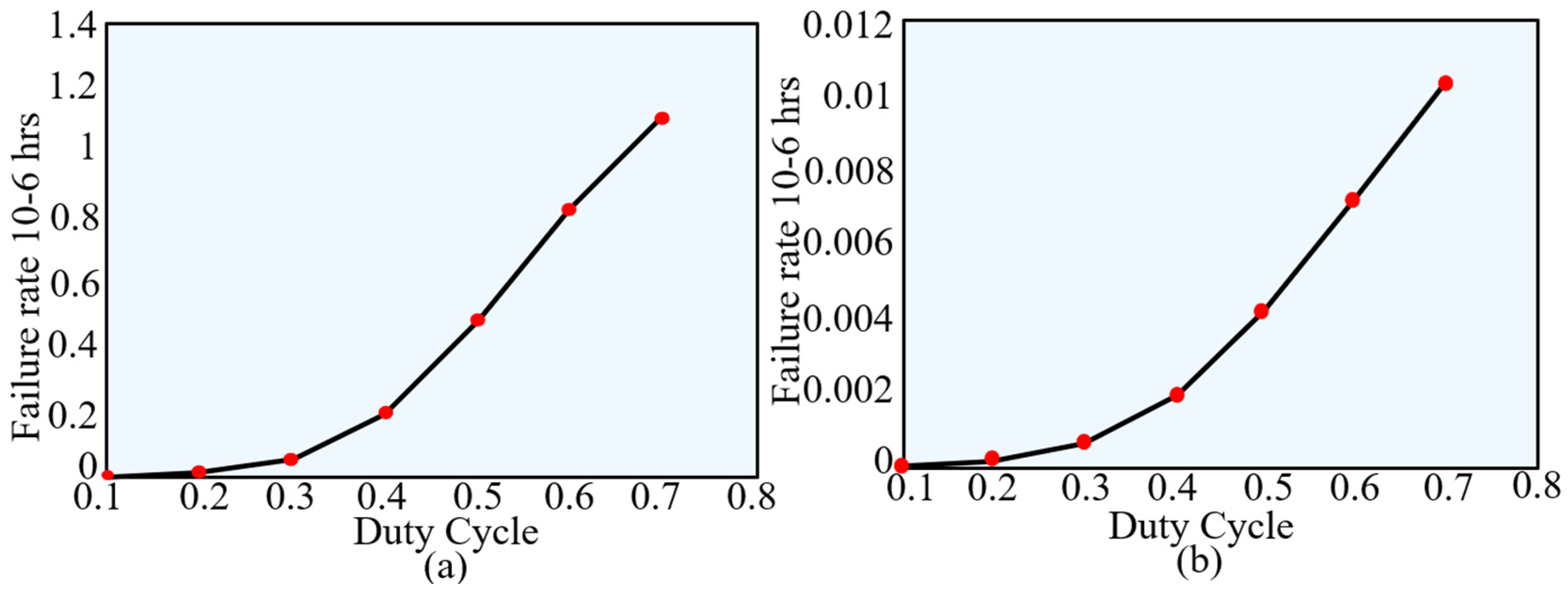

7.2. Impact of Failure Rate of Switch and Diode

8. Comparative Analysis

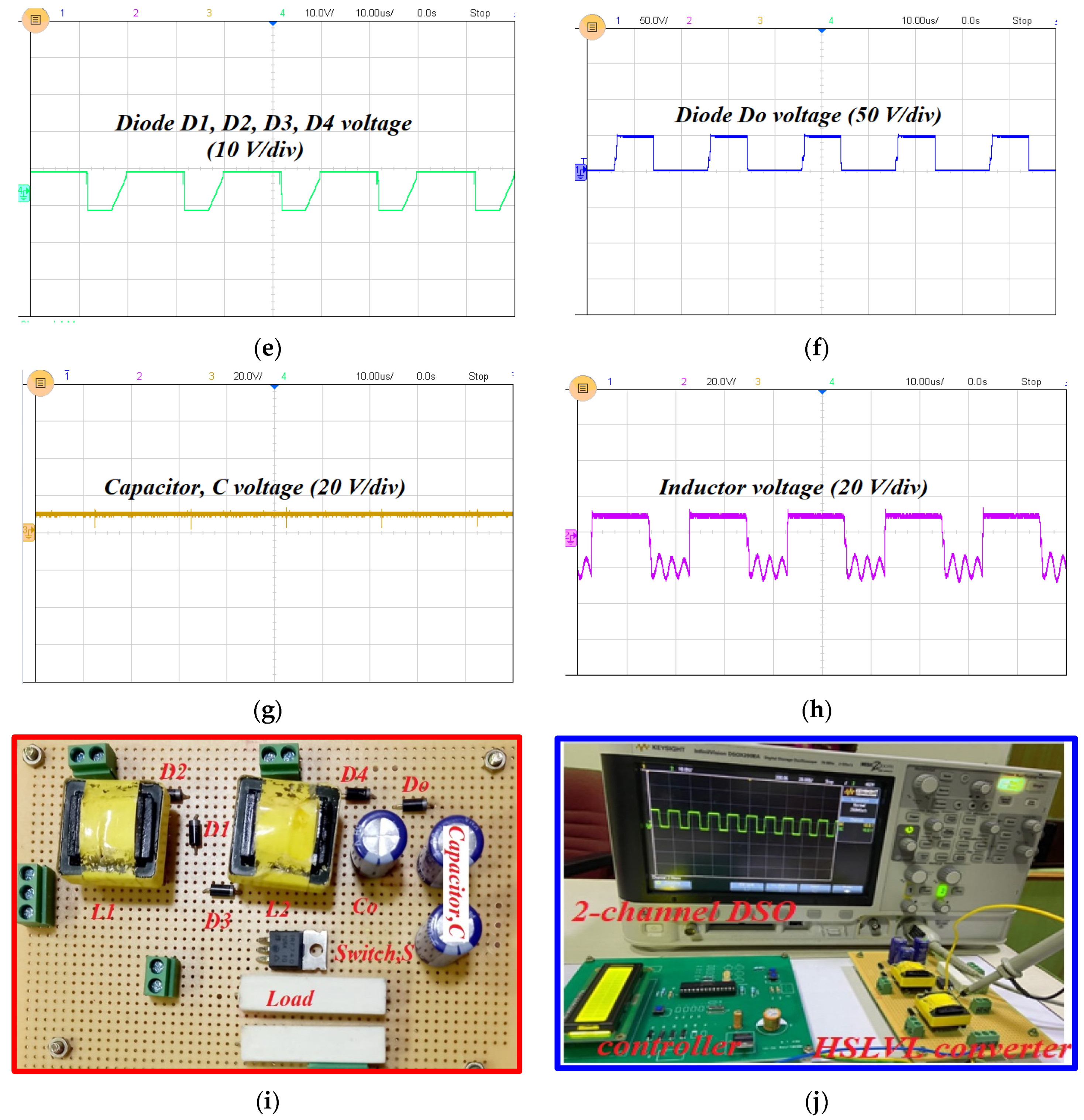

9. Simulation and Experimental Results

10. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

Nomenclature

| MPPT | Maximum power point tracking |

| PV | Photovoltaic |

| N | Number of expander cells |

| D | Duty cycle |

| Gv | Voltage gain |

| S | Stress ratio |

| CCM | Continuous Conduction Mode |

| DCM | Discontinuous Conduction Mode |

| λSW | Failure rate of the switch |

| λD | Failure rate of the diode |

| λL | Failure rate of the inductor |

| λC | Failure rate of the capacitor |

| πT | Temperature factor |

| πE | Environmental factor |

| πS | Stress factor |

| πQ | Quality factor |

| πA | Application factor |

References

- Li, W.; He, X. Review of Nonisolated High-Step-Up DC/DC Converters in Photovoltaic Grid-Connected Applications. IEEE Trans. Ind. Electron. 2010, 58, 1239–1250. [Google Scholar] [CrossRef]

- Leon-Masich, A.; Valderrama-Blavi, H.; Bosque-Moncusi, J.M.; Martinez-Salamero, L. A High-Voltage SiC-Based Boost PFC for LED Applications. IEEE Trans. Power Electron. 2015, 31, 1633–1642. [Google Scholar] [CrossRef]

- Bhaskar, M.S.; Meraj, M.; Iqbal, A.; Padmanaban, S.; Maroti, P.K.; Alammari, R. High Gain Transformer-Less Double-Duty-Triple-Mode DC/DC Converter for DC Microgrid. IEEE Access 2019, 7, 36353–36370. [Google Scholar] [CrossRef]

- Lakshmi, M.; Hemamalini, S. Nonisolated High Gain DC–DC Converter for DC Microgrids. IEEE Trans. Ind. Electron. 2017, 65, 1205–1212. [Google Scholar] [CrossRef]

- Alghaythi, M.L.; O′Connell, R.M.; Islam, N.E.; Khan, M.M.S.; Guerrero, J.M. A High Step-Up Interleaved DC–DC Converter with Voltage Multiplier and Coupled Inductors for Renewable Energy Systems. IEEE Access 2020, 8, 123165–123174. [Google Scholar] [CrossRef]

- Bhaskar, M.S.; Al-Ammari, R.; Meraj, M.; Padmanaban, S.; Iqbal, A. A New Triple-Switch-Triple-Mode High Step-Up Converter with Wide Range of Duty Cycle for DC Microgrid Applications. IEEE Trans. Ind. Appl. 2019, 55, 7425–7441. [Google Scholar] [CrossRef]

- She, X.; Huang, A.Q.; Lukic, S.; Baran, M.E. On Integration of Solid-State Transformer with Zonal DC Microgrid. IEEE Trans. Smart Grid 2012, 3, 975–985. [Google Scholar] [CrossRef]

- Chub, A.; Vinnikov, D.; Liivik, E.; Jalakas, T. Multiphase Quasi-Z-Source DC–DC Converters for Residential Distributed Generation Systems. IEEE Trans. Ind. Electron. 2018, 65, 8361–8371. [Google Scholar] [CrossRef]

- Chaudhury, T.; Kastha, D. A High Gain Multiport DC–DC Converter for Integrating Energy Storage Devices to DC Microgrid. IEEE Trans. Power Electron. 2020, 35, 10501–10514. [Google Scholar] [CrossRef]

- Hsieh, Y.-P.; Chen, J.-F.; Liang, T.-J.; Yang, L.-S. A Novel High Step-Up DC–DC Converter for a Microgrid System. IEEE Trans. Power Electron. 2011, 26, 1127–1136. [Google Scholar] [CrossRef]

- Kazimierczuk, M.K. Pulse-Width Modulated DC–DC Power Converters; Wiley: Chichester, UK, 2016. [Google Scholar]

- Prudente, M.; Pfitscher, L.L.; Emmendoerfer, G.; Romaneli, E.F.; Gules, R. Voltage Multiplier Cells Applied to Non-Isolated DC–DC Converters. IEEE Trans. Power Electron. 2008, 23, 871–887. [Google Scholar] [CrossRef]

- Tofoli, F.L.; Pereira, D.D.C.; de Paula, W.J.; Júnior, D.D.S.O. Survey on non-isolated high-voltage step-up dc–dc topologies based on the boost converter. IET Power Electron. 2015, 8, 2044–2057. [Google Scholar] [CrossRef] [Green Version]

- Shahir, F.M.; Babaei, E.; Sabahi, M.; Laali, S. A new DC–DC converter based on voltage-lift technique. Int. Trans. Electr. Energy Syst. 2016, 26, 1260–1286. [Google Scholar] [CrossRef]

- Shahir, F.M.; Babaei, E.; Farsadi, M. Voltage-Lift Technique Based Nonisolated Boost DC–DC Converter: Analysis and Design. IEEE Trans. Power Electron. 2017, 33, 5917–5926. [Google Scholar] [CrossRef]

- Babaei, E.; Maheri, H.M.; Sabahi, M.; Hosseini, S.H. Extendable Nonisolated High Gain DC–DC Converter Based on Active–Passive Inductor Cells. IEEE Trans. Ind. Electron. 2018, 65, 9478–9487. [Google Scholar] [CrossRef]

- Jalilzadeh, T.; Rostami, N.; Babaei, E.; Maalandish, M. Ultra-step-up dc–dc converter with low-voltage stress on devices. IET Power Electron. 2019, 12, 345–357. [Google Scholar] [CrossRef]

- Luo, F.L.; Ye, H. Super-lift boost converters. IET Power Electron. 2014, 7, 1655–1664. [Google Scholar] [CrossRef]

- Maheri, H.M.; Babaei, E.; Sabahi, M.; Hosseini, S.H. High Step-Up DC–DC Converter with Minimum Output Voltage Ripple. IEEE Trans. Ind. Electron. 2017, 64, 3568–3575. [Google Scholar] [CrossRef]

- Tang, Y.; Fu, D.; Wang, T.; Xu, Z. Hybrid Switched-Inductor Converters for High Step-Up Conversion. IEEE Trans. Ind. Electron. 2014, 62, 1480–1490. [Google Scholar] [CrossRef]

- Axelrod, B.; Berkovich, Y.; Ioinovici, A. Switched-Capacitor/Switched-Inductor Structures for Getting Transformerless Hybrid DC–DC PWM Converters. IEEE Trans. Circuits Syst. I Regul. Pap. 2008, 55, 687–696. [Google Scholar] [CrossRef]

- Sadaf, S.; Bhaskar, M.S.; Meraj, M.; Iqbal, A.; Al-Emadi, N. A Novel Modified Switched Inductor Boost Converter with Reduced Switch Voltage Stress. IEEE Trans. Ind. Electron. 2020, 68, 1275–1289. [Google Scholar] [CrossRef]

- Yang, L.-S.; Liang, T.-J.; Chen, J.-F. Transformerless DC–DC Converters with High Step-Up Voltage Gain. IEEE Trans. Ind. Electron. 2009, 56, 3144–3152. [Google Scholar] [CrossRef]

- Luo, F. Positive output Luo converters: Voltage lift technique. IEE Proc.-Electr. Power Appl. 1999, 146, 415–432. [Google Scholar] [CrossRef]

- Luo, F.; Ye, H. Positive output cascade boost converters. IEE Proc.-Electr. Power Appl. 2004, 151, 590–606. [Google Scholar] [CrossRef]

- Mohan, N.; Undeland, T.M.; Robbins, W.P. Power Electronics-Converters, Applications and Design, 3rd ed.; Wiley: New York, NY, USA, 2003. [Google Scholar]

- Wu, G.; Xinbo, R.; Ye, Z. Non isolated high step-up dc–dc converters adopting switched-capacitor cell. IEEE Trans. Ind. Electron. 2015, 62, 383–393. [Google Scholar] [CrossRef]

- Divya Navamani, J.; Vijayakumar, K.; Lavanya, A. Design and Component Analysis of High Gain Quadratic Boost Converters with fault diagnosis and remedial measure. J. Electr. Syst. 2019, 15, 539–552. [Google Scholar]

- Navamani, J.D.; Vijayakumar, K.; Jegatheesan, R.; Lavanya, A. High Step-up DC–DC Converter by Switched Inductor and Voltage Multiplier Cell for Automotive Applications. J. Electr. Eng. Technol. 2017, 12, 189–197. [Google Scholar] [CrossRef] [Green Version]

- Maroti, P.K.; Ranjana, M.S.B.; Revathi, B.S. A high gain DC–DC converter using voltage multiplier. In Proceedings of the 2014 International Conference on Advances in Electrical Engineering (ICAEE), Vellore, India, 9–11 January 2014; pp. 1–4. [Google Scholar] [CrossRef]

- Maalandish, M.; Hosseini, S.H.; Ghasemzadeh, S.; Babaei, E.; Jalilzadeh, T. A Novel Multiphase High Step-Up DC/DC Boost Converter with Lower Losses on Semiconductors. IEEE J. Emerg. Sel. Top. Power Electron. 2018, 7, 541–554. [Google Scholar] [CrossRef]

- Bhaskar, M.S.; Gupta, N.; Selvam, S.; Almakhles, D.J.; Sanjeevikumar, P.; Ali, J.S.M.; Umashankar, S. A New Hybrid Zeta-Boost Converter with Active Quad Switched Inductor for High Voltage Gain. IEEE Access 2021, 9, 20022–20034. [Google Scholar] [CrossRef]

- Bhaskar, M.S.; Ramachandaramurthy, V.K.; Padmanaban, S.; Blaabjerg, F.; Ionel, D.M.; Mitolo, M.; Almakhles, D. Survey of DC–DC Non-Isolated Topologies for Unidirectional Power Flow in Fuel Cell Vehicles. IEEE Access 2020, 8, 178130–178166. [Google Scholar] [CrossRef]

- DivyaNavamani, J.; Lavanya, A.; Sathik, M.J.; Vijayakumar, K. Expandable transformer-less high-gain dc–dc converter based on quasi-Z source and multiplier cells. Sādhanā 2021, 46, 22. [Google Scholar] [CrossRef]

- Babalou, M.; Dezhbord, M.; Alishah, R.S.; Hosseini, S.H. A Soft-Switched Ultra High Gain DC–DC Converter with Reduced Stress voltage on Semiconductors. In Proceedings of the 2019 10th International Power Electronics, Drive Systems and Technologies Conference (PEDSTC), Shiraz, Iran, 12–14 February 2019; pp. 677–682. [Google Scholar] [CrossRef]

- Alishah, R.S.; Hassani, M.Y.; Hosseini, S.H.; Bertilsson, K.; Babalou, M. Analysis and Design of a New Extendable SEPIC Converter with High Voltage Gain and Reduced Components for Photovoltaic Applications. In Proceedings of the 2019 10th International Power Electronics, Drive Systems and Technologies Conference (PEDSTC), Shiraz, Iran, 12–14 February 2019; pp. 492–497. [Google Scholar] [CrossRef] [Green Version]

- Reddy, K.J.; Sudhakar, N. High Voltage Gain Interleaved Boost Converter with Neural Network Based MPPT Controller for Fuel Cell Based Electric Vehicle Applications. IEEE Access 2018, 6, 3899–3908. [Google Scholar] [CrossRef]

- Wang, Y.-F.; Xue, L.-K.; Wang, C.-S.; Wang, P.; Li, W. Interleaved high conversion-ratio bidirectional DC–DC converter for distributed energy storage systems—Circuit generation, analysis, and design. IEEE Trans. Power Electron. 2016, 31, 5547–5561. [Google Scholar] [CrossRef]

- Naseri, F.; Farjah, E.; Ghanbari, T. An efficient regenerative braking system based on battery/supercapacitor for electric, hybrid, and plug-in hybrid electric vehicles with BLDC motor. IEEE Trans. Veh. Technol. 2017, 66, 3724–3738. [Google Scholar] [CrossRef]

- Chen, S.-M.; Liang, T.-J.; Yang, L.-S.; Chen, J.-F. A Boost Converter with Capacitor Multiplier and Coupled Inductor for AC Module Applications. IEEE Trans. Ind. Electron. 2013, 60, 1503–1511. [Google Scholar] [CrossRef]

- Andrade, A.M.S.S.; Guisso, R.A. Quasi-Z-source network DC–DC converter with different techniques to achieve a high voltage gain. Electron. Lett. 2018, 54, 710–712. [Google Scholar] [CrossRef]

- Sadaf, S.; Al-Emadi, N.; Maroti, P.K.; Iqbal, A. A New High Gain Active Switched Network-Based Boost Converter for DC Microgrid Application. IEEE Access 2021, 9, 68253–68265. [Google Scholar] [CrossRef]

- Rahimi, R.; Habibi, S.; Ferdowsi, M.; Shamsi, P. Z-source-based high step-up DC–DC converters for photovoltaic applications. IEEE J Emerg. Sel. Topics Power Electron. 2021. early access. [Google Scholar] [CrossRef]

- Faridpak, B.; Bayat, M.; Nasiri, M.; Samanbakhsh, R.; Farrokhifar, M. Improved Hybrid Switched Inductor/Switched Capacitor DC–DC Converters. IEEE Trans. Power Electron. 2020, 36, 3053–3062. [Google Scholar] [CrossRef]

- Navamani, J.D.; Geetha, A.; Almakhles, D.; Lavanya, A.; Ali, J.S.M. Modified LUO High Gain DC–DC Converter with Minimal Capacitor Stress for Electric Vehicle Application. IEEE Access 2021, 9, 122335–122350. [Google Scholar] [CrossRef]

- Andrade, A.M.S.S.; Faistel, T.M.K.; Guisso, R.A.; Toebe, A. Hybrid High Voltage Gain Transformerless DC–DC Converter. IEEE Trans. Ind. Electron. 2021, 69, 2470–2479. [Google Scholar] [CrossRef]

- Shanthi, T.; Prabha, S.U.; Sundaramoorthy, K. Non-Isolated n-Stage High Step-up DC–DC Converter for Low Voltage DC Source Integration. IEEE Trans. Energy Convers. 2021, 36, 1625–16341. [Google Scholar] [CrossRef]

- Zaid, M.; Khan, S.; Siddique, M.D.; Sarwar, A.; Ahmad, J.; Sarwer, Z.; Iqbal, A. A transformerless high gain dc–dc boost converter with reduced voltage stress. Int. Trans. Electr. Energy Syst. 2021, 31, e12877. [Google Scholar] [CrossRef]

| Ref | Number of Components |

|---|---|

| Remarks | |

| Proposed topology |

|

| Super-lift [18] |

|

| Active–passive SL [19] |

|

| AH-SLC [20] |

|

| Number of Expander Cell | Voltage Gain | Voltage Stress on Switch | Voltage Stress on Output Diode | Voltage Stress on Other Diodes (D1–D4) |

|---|---|---|---|---|

| 1 | Vg | |||

| 2 | ||||

| 3 | ||||

| 4 | ||||

| N | N | |||

| Parameters | Power Loss Equations |

|---|---|

| Inductor loss, PL | |

| Capacitor loss, PC | |

| Diode Loss, PD | |

| Switch Loss, PSW |

| Ref | Number of Components | Voltage Gain | Switch Voltage Stress | Voltage Gain Expansion | |||

|---|---|---|---|---|---|---|---|

| Diode | Switch | Capacitor | Inductor | ||||

| Proposed topology | 2 + 3N | 1 | 2 | 1 + N | Yes | ||

| Super-lift | 1 + 3N | 1 | 1 | 1 + N | Yes | ||

| Active–passive SL | 2N | N + 2 | 1 | 2 + N | Yes | ||

| AH-SLC | 4 | 2 | 1 | 3 | No | ||

| PSL converter | 4 | 1 | 1 | 2 | Yes | ||

| Modified SL Boost | 3 | 2 | 1 | 2 | Yes | ||

| Hybrid SL | 4 | 2 | 1 | 3 | Yes | ||

| Active SL | 2 | 2 | 2 | 2 | Yes | ||

| Components | Specifications |

|---|---|

| Vg (input voltage) | 12 V |

| VO (output voltage) | 66 V |

| PO (power rating) | 50 W |

| Duty cycle, D | 0.6 |

| fS (switching frequency) | 50 kHz |

| Inductors (L1 and L2) | 100 uH, Torroidal core |

| Capacitors (C and CO) | 100 µF/200 µF, Electrolytic |

| MOSFET | IRF460P |

| Diode | VS-30PT100 |

| Microprocessor | dsPIC 30F2010 |

| Driver Circuit | TLP250 |

| Parameters | Theoretical (V) | Simulated Values (V) | Experimental Values (V) |

|---|---|---|---|

| PO = 50 W, Vg = 12 V, D = 0.6, fs = 50 kHz | |||

| Output voltage, VO | 66 | 65.5 | 65 |

| Switch voltage stress, VSW | 48 | 47.5 | 46 |

| Diode voltage stress, VD1 | 12 | 12 | 11.5 |

| Diode voltage stress, VDO | 54 | 53.5 | 52 |

| Efficiency | 96.2% | 96.0% | 95.0% |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Almakhles, D.; Jayachandran, D.N.; Anbazhagan, L.; Hannachi, M.; Mohamed Ali, J.S. Dynamic Analysis of Extendable Hybrid Voltage Lift DC–DC Converter for DC Microgrid. Processes 2022, 10, 2652. https://doi.org/10.3390/pr10122652

Almakhles D, Jayachandran DN, Anbazhagan L, Hannachi M, Mohamed Ali JS. Dynamic Analysis of Extendable Hybrid Voltage Lift DC–DC Converter for DC Microgrid. Processes. 2022; 10(12):2652. https://doi.org/10.3390/pr10122652

Chicago/Turabian StyleAlmakhles, Dhafer, Divya Navamani Jayachandran, Lavanya Anbazhagan, Marwa Hannachi, and Jagabar Sathik Mohamed Ali. 2022. "Dynamic Analysis of Extendable Hybrid Voltage Lift DC–DC Converter for DC Microgrid" Processes 10, no. 12: 2652. https://doi.org/10.3390/pr10122652