Abstract

The current work presents a new structure based on Au/PVA/SiO2/p-Si/Al that has not been studied before. An aqueous solution of polyvinyl alcohol (PVA) polymer gel was deposited on the surface of SiO2/Si using the spin-coating technique. The silicon wafer was left to be oxidized in a furnace at 1170 k for thirty minutes, creating an interdiffusion layer of SiO2. The variations in the dielectric constant (Є′), dielectric loss (Є″), and dielectric tangent (tanδ) with the change in the frequency, voltage, and temperature were analyzed. The results showed an increase in the dielectric constant (Є′) and a decrease in the dielectric loss (Є″) and tangent (tanδ); thus, the Au/PVA/SiO2/p-Si/Al heterostructure has opened up new frontiers for the semiconductor industry, especially for capacitor manufacturing. The Cole–Cole diagrams of the Є″ and Є′ have been investigated at different temperatures and voltages. The ideality factor (n), barrier height (Φb), series resistance (Rs), shunt resistance (Rsh), and rectification ratio (RR) were also measured at different temperatures.

1. Introduction

In recent years, there has been significant progress in developing materials and techniques for sensor applications, particularly those involving thin films and nanostructures [1,2]. Polymer oxide semiconductor (POS) structures consist of a thin oxide film between a polymer and a semiconductor [3]. The oxide layer prevents inter-diffusion between the polymer and semiconductor substrate and improves the electric field reduction inside the structures [4,5,6]. It enhances the electrical and dielectric properties of devices such as capacitors [7,8,9], which increases the electric charge’s storage capacity. The creation of oxide thin films on Si substrates using traditional methods of oxidation or deposition cannot passivate the active hanging bonds on the surface of semiconductors [10,11]. The carrier lifetime remains more prolonged at high angular frequencies than the period (T = 1/x). Thus, the charges at the border states cannot track an AC sign [12]. Contrarily, the charges at minor frequencies could follow the AC signal, and thus, the effect of these charges on the capacitance of devices increases with decreasing frequency [13].

Consequently, the electrical and dielectric characteristics depend on the frequency, making accuracy and trust results very significant. The interface states at the Si/SiO2, PVA/SiO2 interfaces, and device contacts cause deviation from the perfect case [14,15]. These interfaces commonly cause a bias change and frequency dispersal of the C–V and G–V curves [16]. Thus, it is noteworthy to incorporate the effect of the frequency and thoroughly inspect the frequency dispersal of the dielectric properties. The frequency dependence of the dielectric constant (Є′), dielectric loss (Є″), and dielectric tangent (tanδ) is dominated by a small frequency dispersal, whose physical origin has long been in question. The innovation in this paper is that we have synthesized the Au/PVA/SiO2/p-Si/Al structure, which has not been investigated before. We present a whole study of the dielectric constant (Є′), dielectric loss (Є″), and dielectric tangent (tanδ) with the variation of the frequency, voltage, and temperature. We also succeeded in improving the dielectric constant (Є′) and reducing the dielectric loss (Є″) and the tangential component (tanδ); thus, the current structure is considered a promising material for the development of capacitors. The Cole–Cole diagrams of the Є″ and Є′ at different voltages and temperatures have been examined. In addition to that, the I–V measurements were performed to retrieve information about its electrical properties, such as the ideality factor (n), barrier height (Φb), series resistance (Rs), shunt resistance (Rsh), and rectification ratio (RR) over different temperatures.

2. Results and Discussion

2.1. Scanning Electron Microscope and X-ray Diffraction Pattern

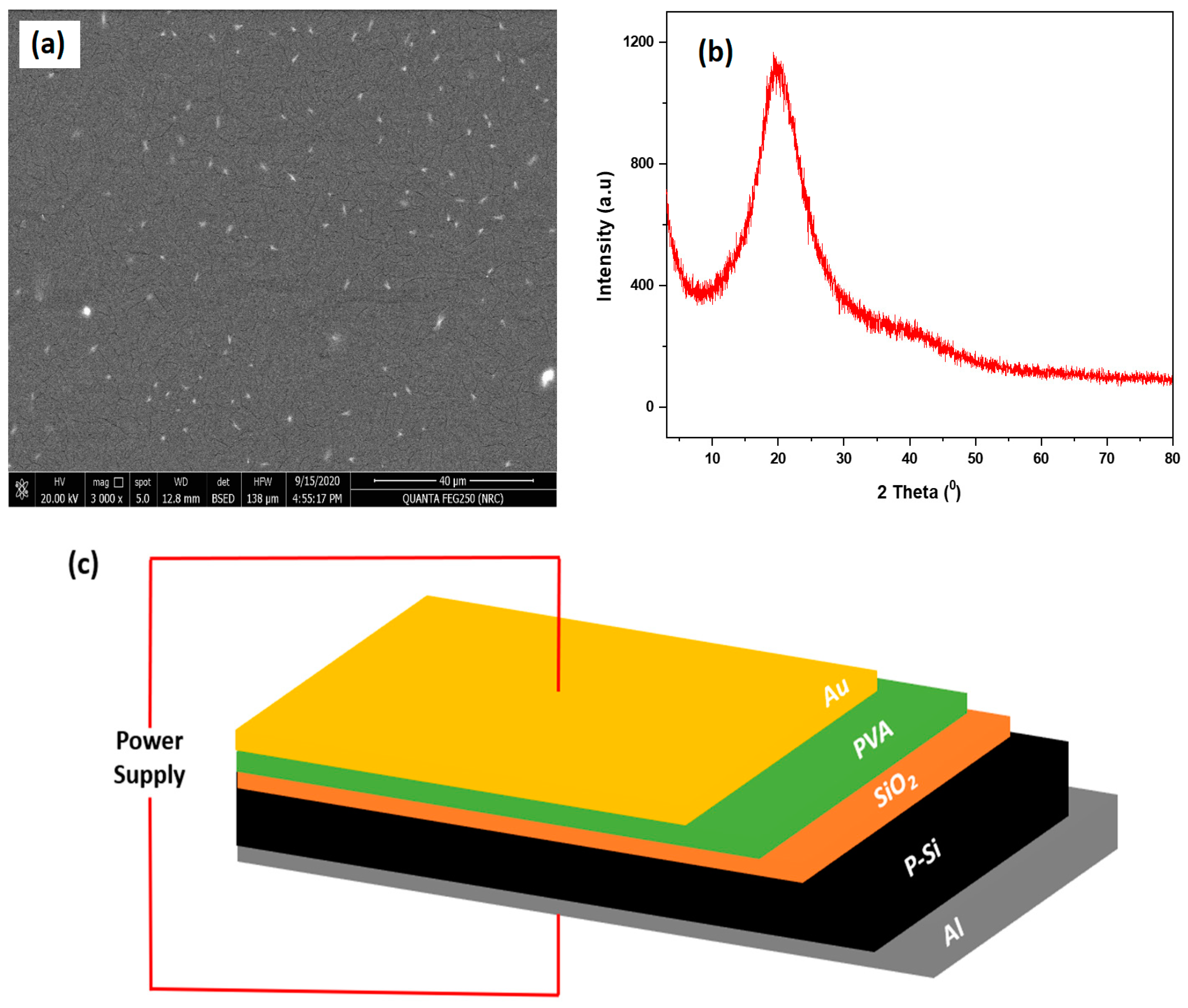

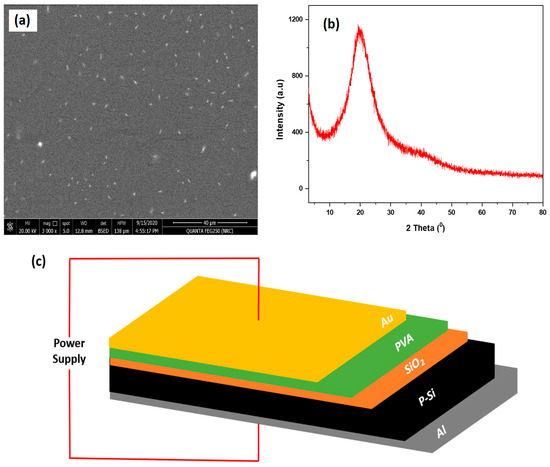

SEM Analysis: Figure 1 shows the surface topography of the PVA layer on the SiO2/Si substrate. The SEM micrograph reveals a uniform distribution across the surface, with some cracks visible. These cracks are assumed to have originated from the drying process of the PVA film as the solvent evaporated, causing shrinkage and resulting in stress-induced cracks. The surface morphology of the PVA is relatively smooth, with minimal porosity, indicating a dense film formation.

Figure 1.

(a) SEM of the Au/PVA/SiO2/p-Si/Al structure, (b) XRD of the Au/PVA/SiO2/p-Si/Al structure, and (c) Au/PVA/SiO2/p-Si/Al structure.

XRD Analysis: Figure 2 presents the XRD pattern of the PVA/SiO2/Si thin film. The XRD spectrum exhibits a prominent peak at 2θ = 19.7°, which is characteristic of the semi-crystalline nature of the PVA film. The broadening of the halo and the absence of sharp diffraction peaks confirm the semi-crystalline structure of the PVA, suggesting that the material has both amorphous and crystalline regions [17].

Figure 2.

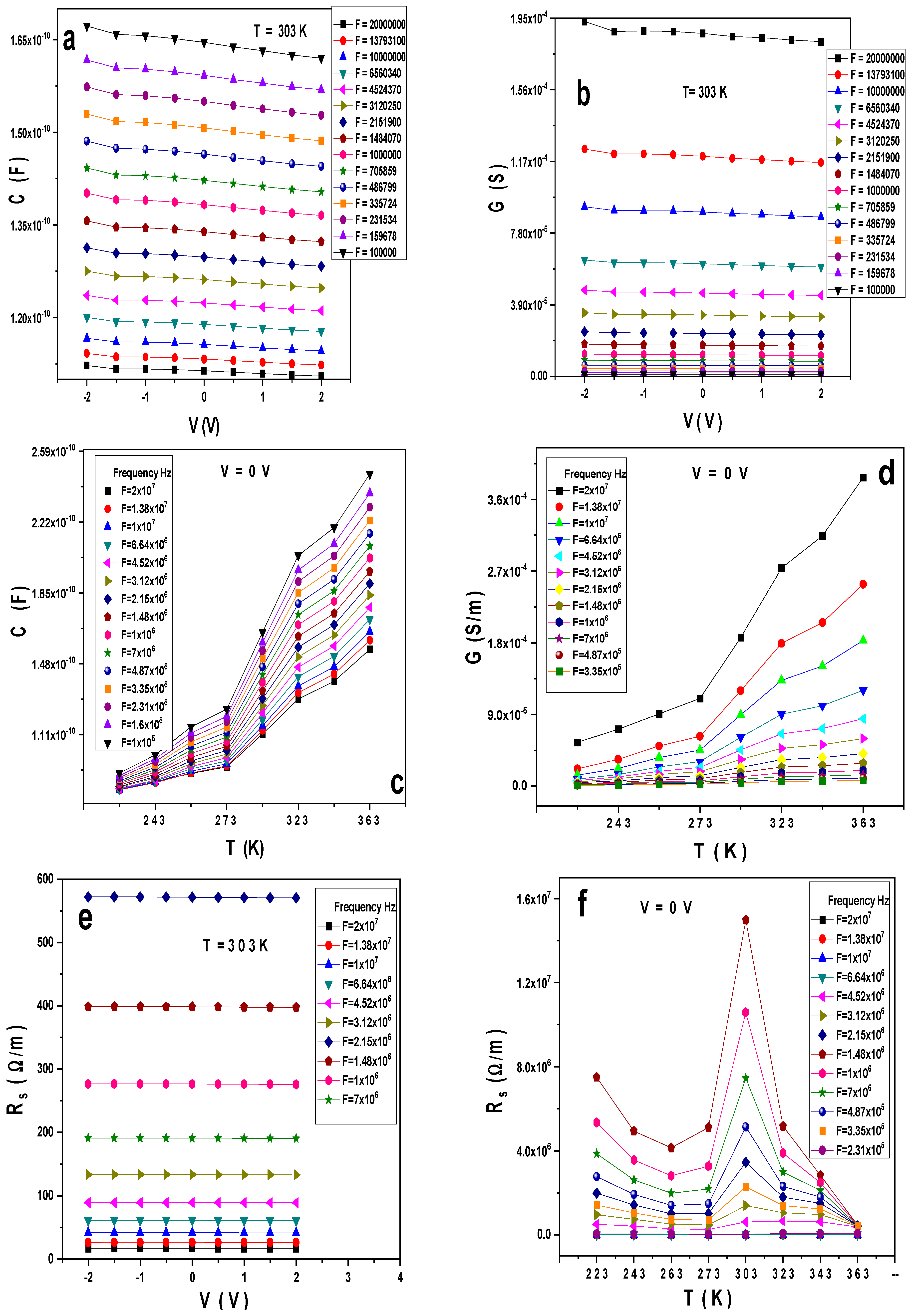

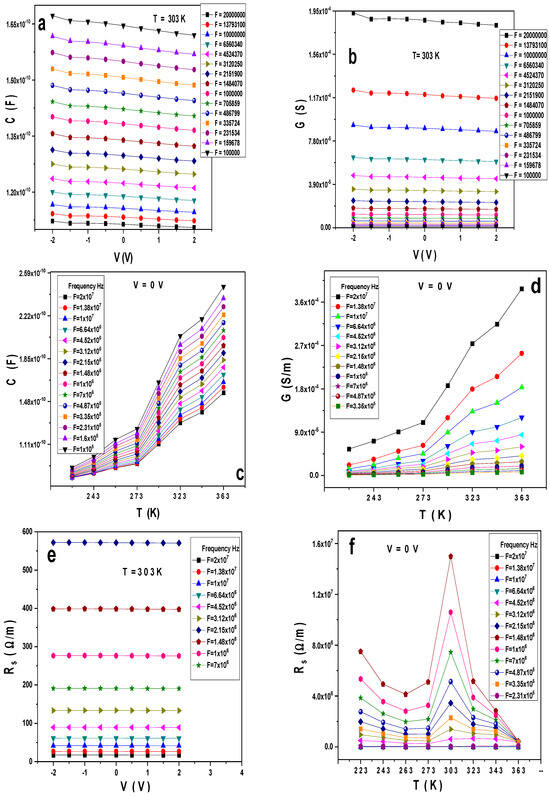

(a–f) The experimental (a) C–V, (b) G–V, (c) C–T, (d) G–T, (e) Rs–V, and (f) Rs–T for the Au/PVA/SiO2/p-Si/Al structure.

Additionally, the I–V and C–V characteristics were measured using a Keysight model B2901A and a Novocontrol high-resolution alpha analyzer. These measurements were supported by a Quatro temperature controller, which maintained the temperature stability to within 0.2 K using clean nitrogen as a heating agent.

2.2. Dielectric Characterization

Figure 2a,b display the variation of the capacitance (C) and conductance (G) with the voltages and frequencies at a temperature of 303 K for the Au/PVA/SiO2/p-Si/Al structure. As observed in Figure 2a, the capacitance decreases with the frequency, while the conductance increases. C and G are still independent of the voltage changes. At the same time, the conductance might be attributed to the spreading profile of the interface density of states at the PVA/p-Si and PVA/SiO2 interface and series resistance (Rs) [18,19]. Figure 2c,d display the variation of C and G with the temperature at different frequencies and a constant voltage V = 0 V; both rise with the temperature. The variation of the series resistance (Rs) with the voltage at different frequencies at room temperature is seen in Figure 2e; it decreases with the frequencies, while Rs shows peaks at room temperature, as displayed in Figure 2f, and then decreases at high temperatures.

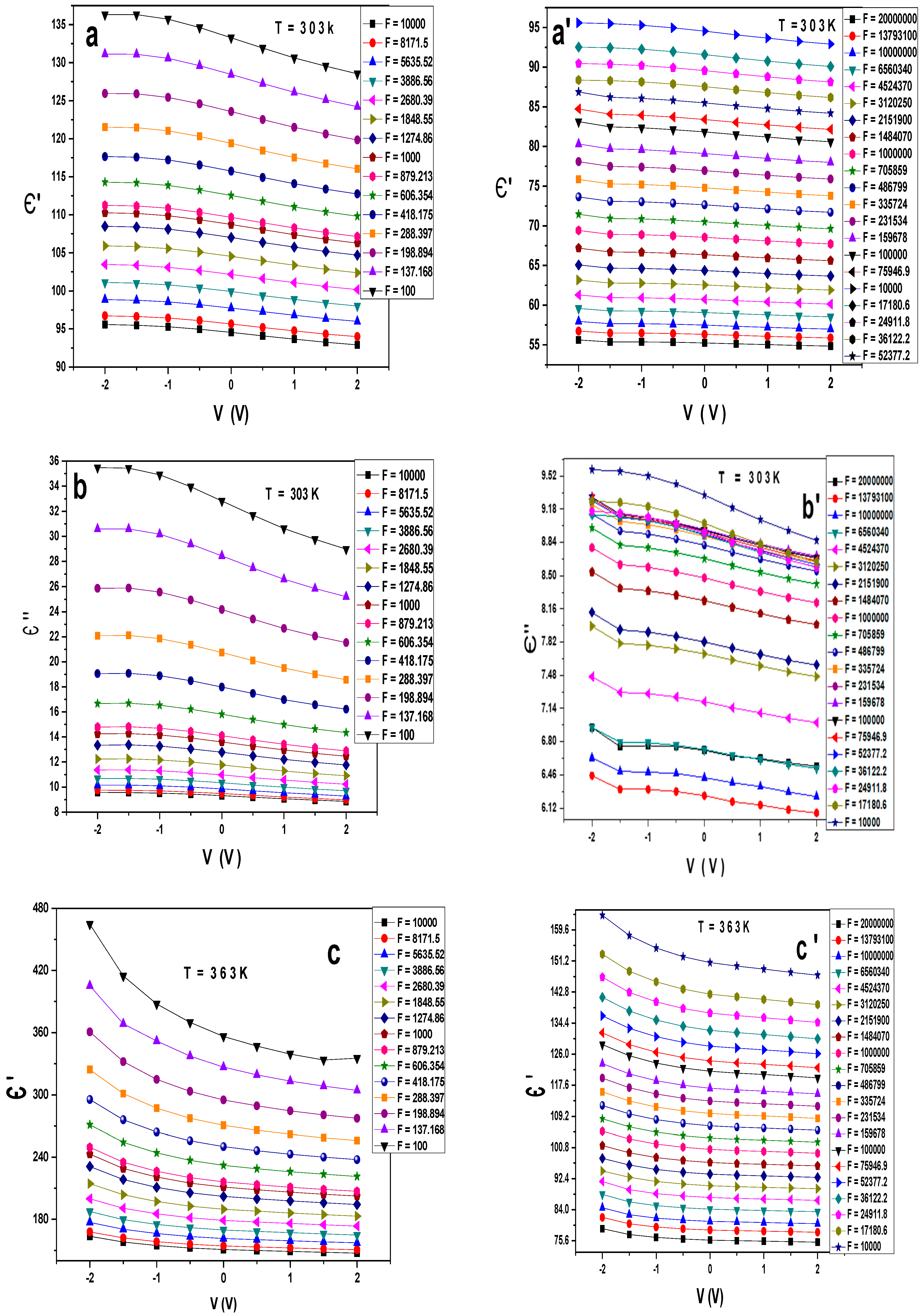

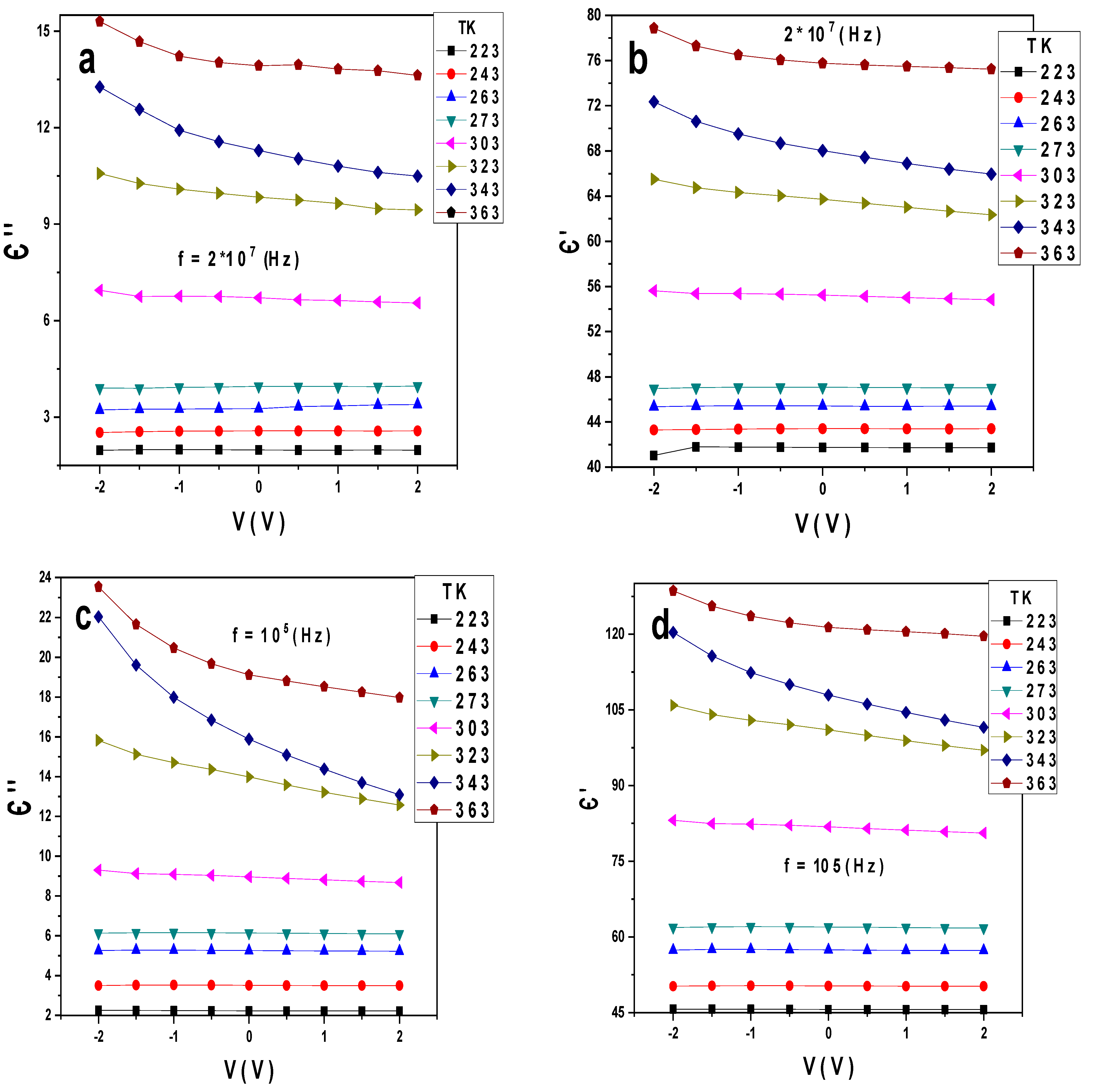

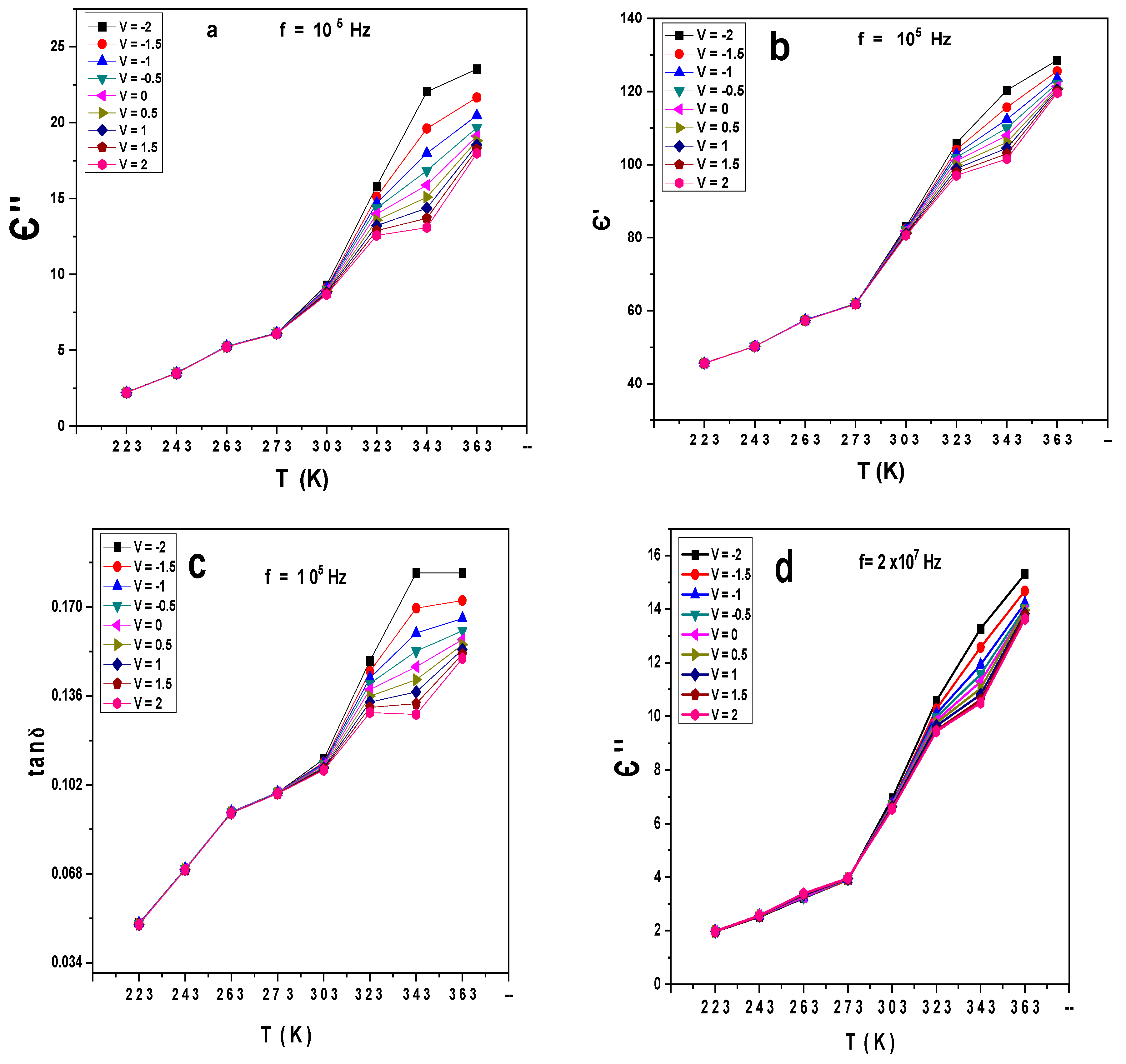

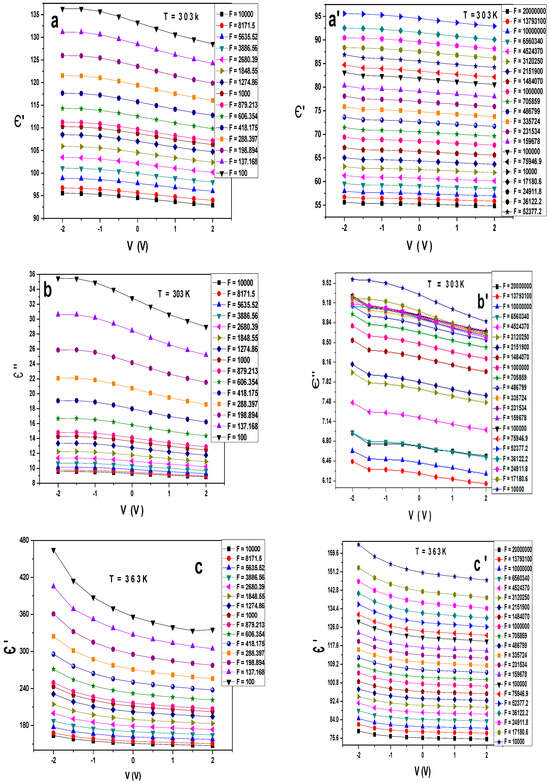

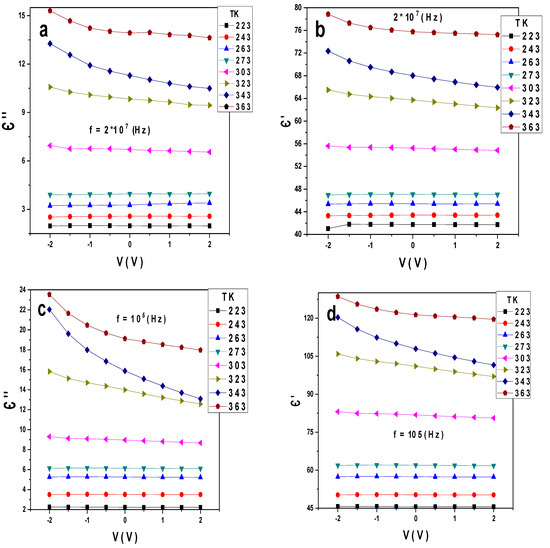

Figure 3a–b’ display the variation of the dielectric constant Є′ and Є″ at different frequencies and room temperature for Au/PVA/SiO2/p-Si/Al. It is seen that Є′ decreases with the frequencies, and its value ranges from 56 to 135, while the dielectric loss Є″ decreases with the frequency, taking values from 6 to 36. Here, we enhanced the values of Є′ and reduced the values of Є″, as shown in Figure 3b,b’. At a temperature of 363 K, Є′ increases from 75 to 480 while Є″ reduces from 13 to 380, as illustrated in Figure 4c,d. On the other hand, working at a low temperature equal to 223 k, the values of Є′ and Є″ range from 41 to 60 and from 1 to 4.4, respectively, as illustrated in Figure 3e–f’. As described above, we can increase the dielectric constant’s value and reduce the dielectric loss’s value with varying temperatures and frequencies. Still, their values are independent of the change in the voltage. It is stated that the values of Є′ and Є″ depend on several factors related to the interface state density, interfacial layer thickness, series resistance, doping concentration, etc. [17,20].

Figure 3.

(a–f’) Є′, Є″ versus V at different frequencies and different constant temperatures for the Au/PVA/SiO2/p-Si/Al structure.

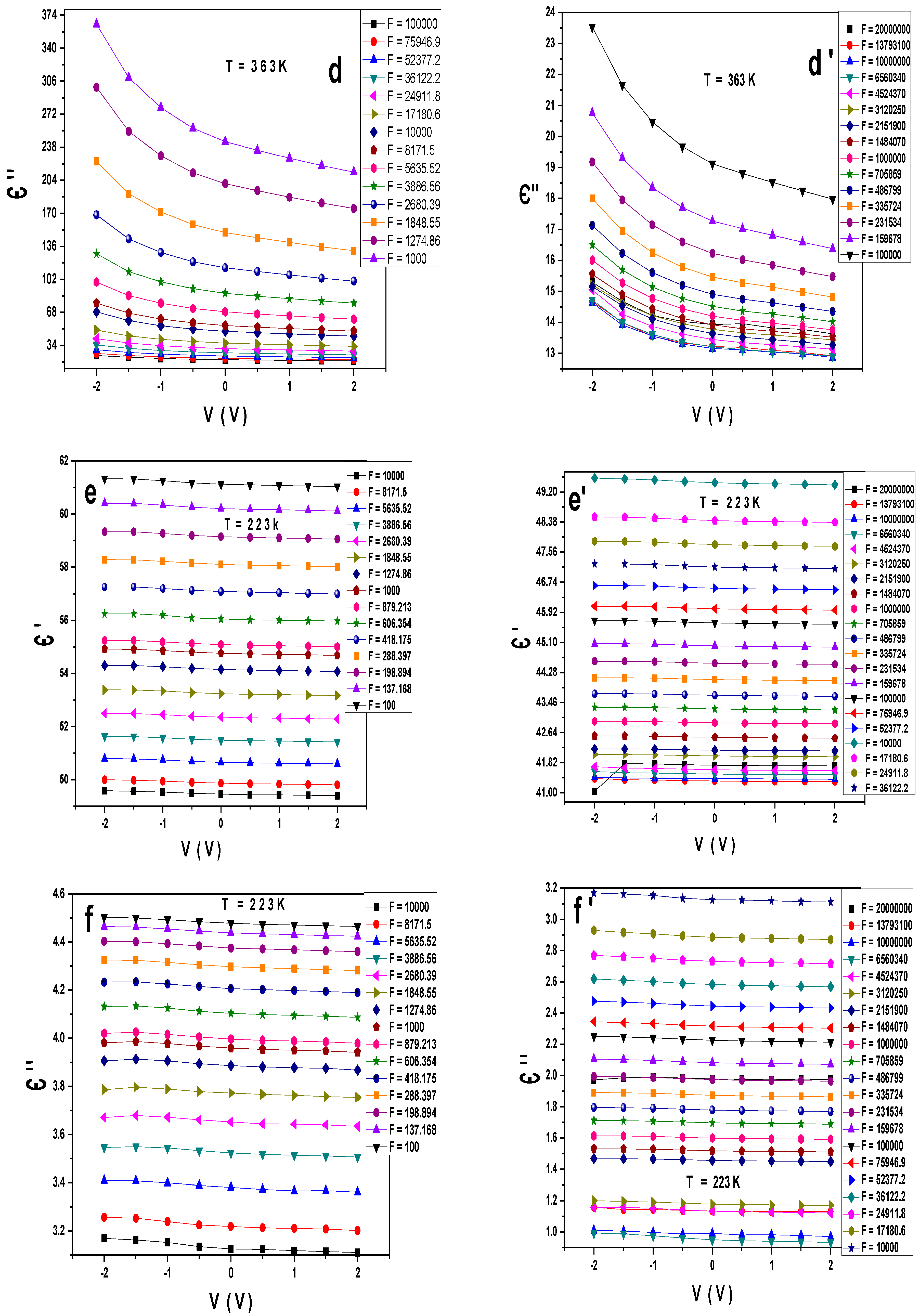

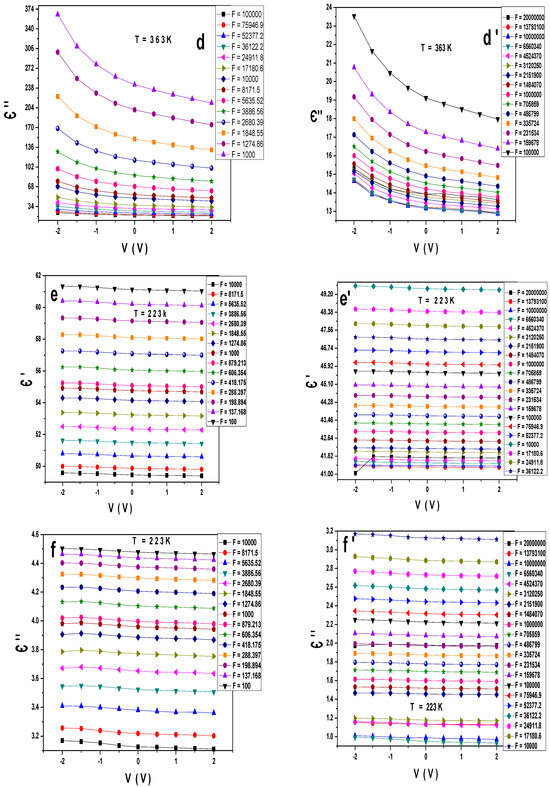

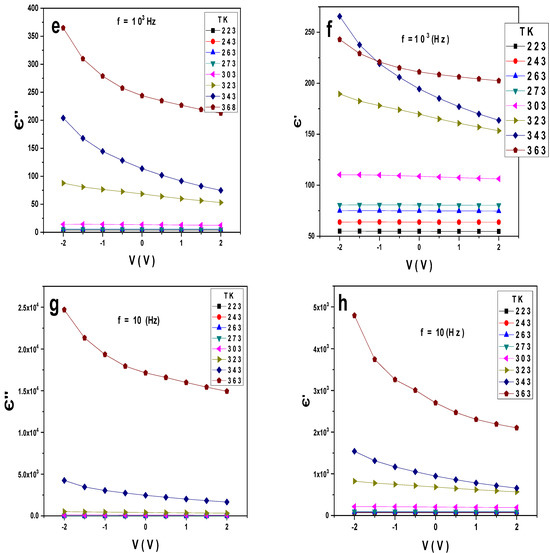

Figure 4.

(a–h) Є′, Є″ versus V at different temperatures and constant frequencies for the Au/PVA/SiO2/p-Si/Al structure.

Figure 4a–h illustrate the variation of Є′ and Є″ with the voltages at different temperatures and constant different frequencies for Au/PVA/SiO2/p-Si/Al. At the frequency 2 × 107 Hz, Є′ and Є″ increase with the temperatures and their values range from 40 to 80 and 3 to 15, respectively. The dielectric constant and dielectric loss dependence on the voltage is almost low, as shown in Figure 4a,b. At the frequency 105 Hz, the values of Є′ and Є″ range from 45 to 120 and 2 to 24, respectively, as displayed in Figure 4c,d, while at the frequencies 103 and 10 Hz, Є″ increases to large undesirable values, as shown in Figure 4e–h. These variations in the conductance of Є′ and Є″ can also be due to polarization mechanisms such as Maxwell–Wagner [21] and space charge [22,23]. Through the above, it can be concluded that at high frequencies, the value of the dielectric loss is minimal. The industry needs to reduce the value of the heat loss at medium and low frequencies as the value of constant loss rises, which is undesirable.

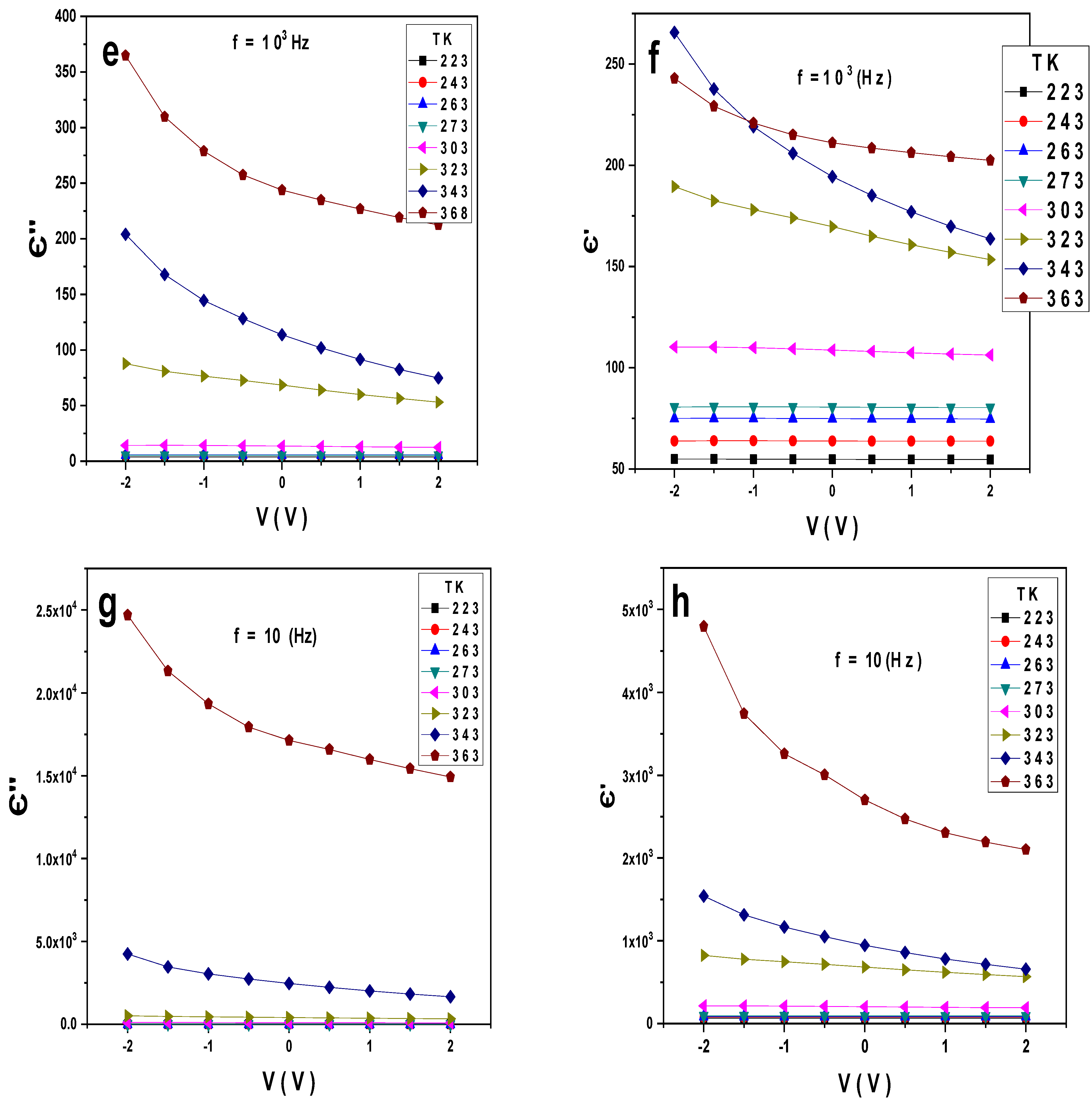

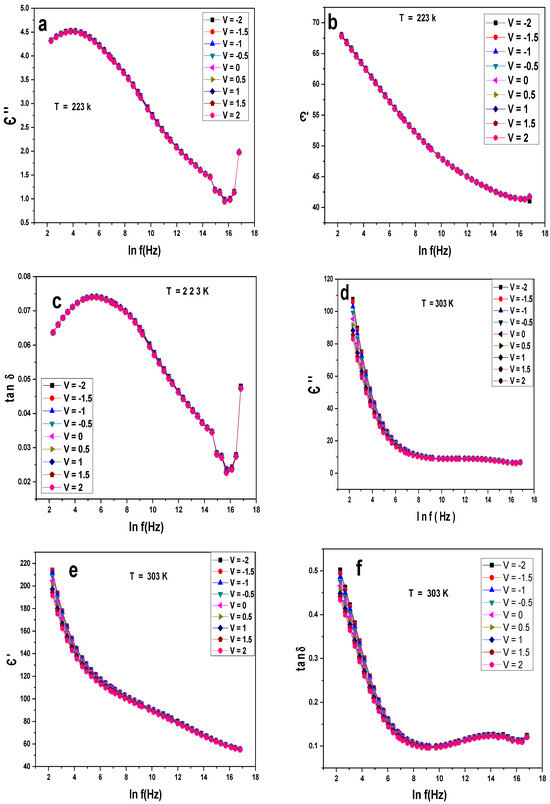

Figure 5a–f illustrate the variation of Є′, Є″, and tanδ with the frequency at different voltages and fixed temperatures for Au/PVA/SiO2/p-Si/Al. At a low temperature of 223 k, the behavior is the same for all the Є′, Є″, and tanδ, and the difference is that Є″ and tanδ have two peaks at low and high frequencies. The most significant finding here was the enhancement of the value of Є′ in the range of 40–70 and the decrease in the values of Є″ in the range of 0.5–5 and 0.02–0.08, respectively, as seen in Figure 5a–c. At room temperature, Є″ and tanδ exhibit the same standard behavior, while Є′ decreases with all the frequencies. However, the values of Є′ increase compared to Figure 5a, while Є″ and tanδ decrease, as shown in Figure 5d–f. The robust reduction in Є′ and Є″ with the frequency can be described by the Debye relaxation in terms of the polarity alignment and interface effect [8]. Though a great Є is significant for high-capacity energy storage dielectrics, the balance between a high dielectric constant and a low dielectric loss is more critical [24].

Figure 5.

(a–f) Є′, Є″, tanδ versus lnf at different voltages and constant temperatures for the Au/PVA/SiO2/p-Si/Al structure.

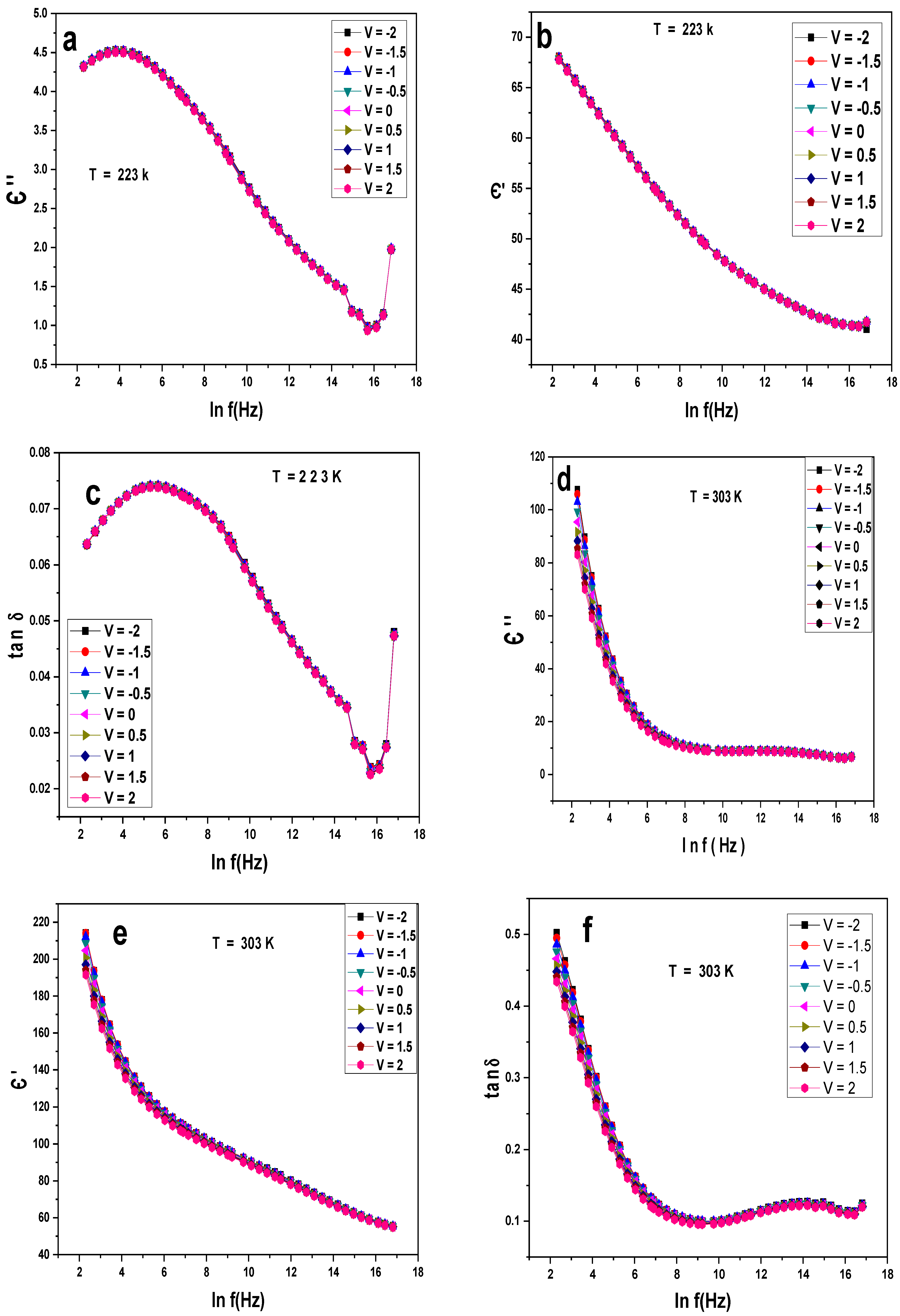

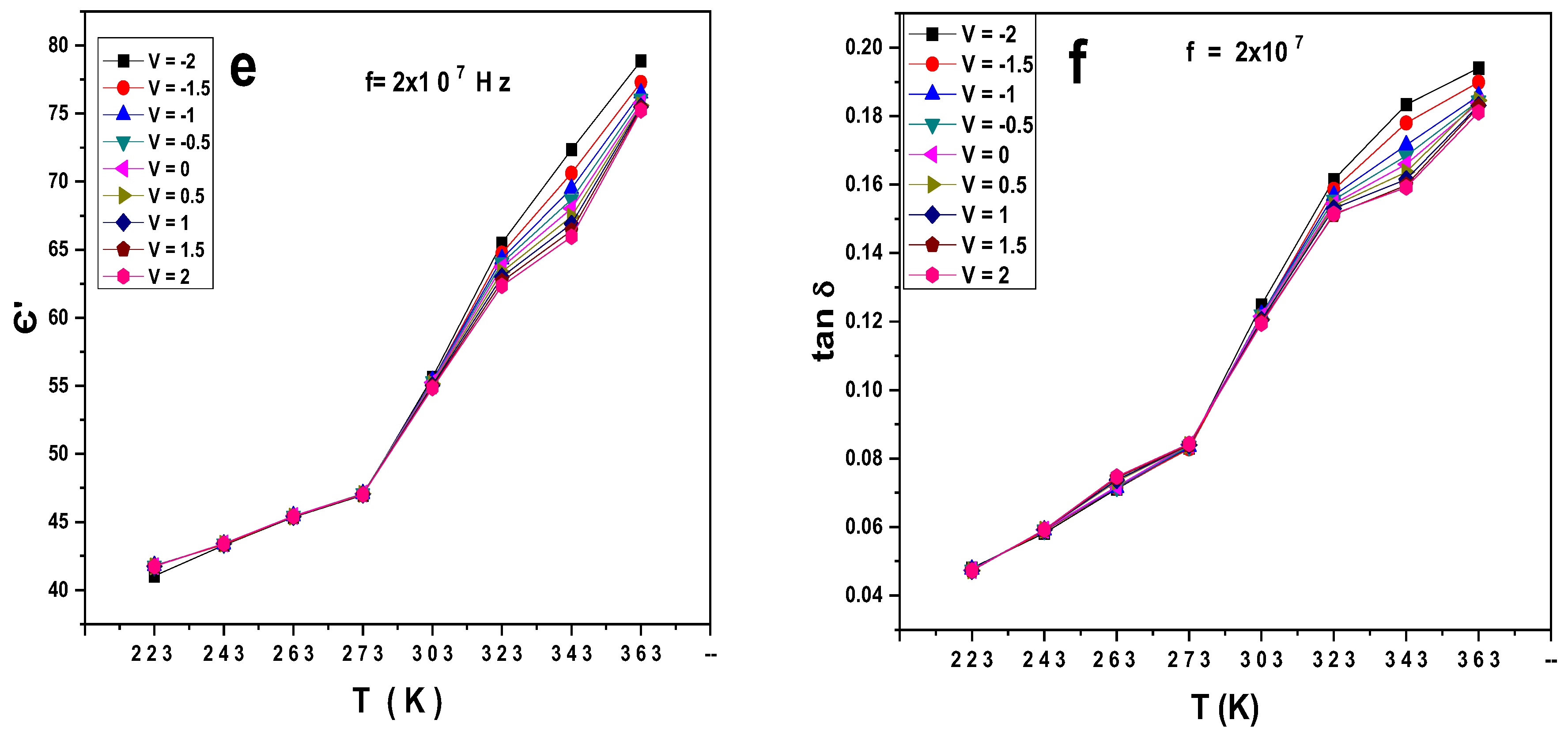

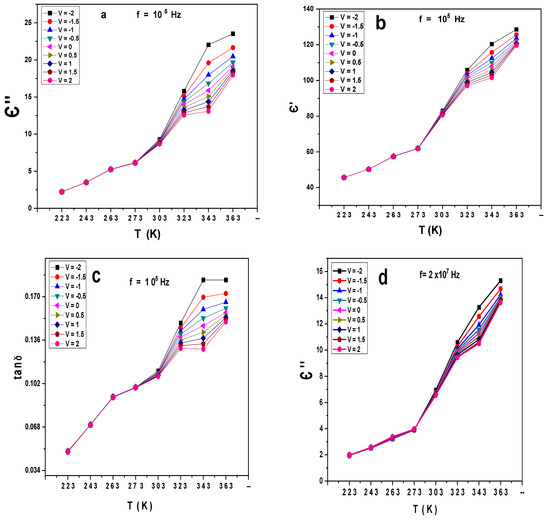

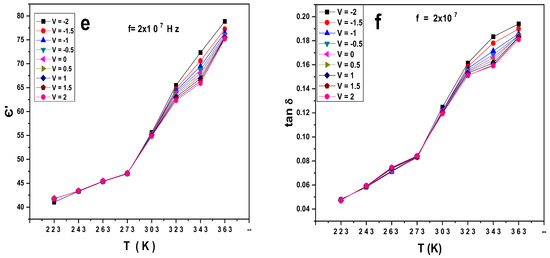

Figure 6a–f illustrate the variation of Є′, Є″, and tanδ with the temperature at different voltages and frequencies for the Au/PVA/SiO2/p-Si/Al structure. Є′, Є″, and tanδ increase with the temperature. All the curves overlap at low temperatures, while at room and high temperatures, the Є′, Є″, and tanδ curves split at each voltage. At the frequency 105 Hz, the values of Є′ increase from 40 to 140, while Є″ and tanδ reduce from 0 to 25 and 0.04 to 0.2, respectively, as displayed in Figure 6a–c. As the frequency increases to 2 × 107 Hz, the values of Є′, Є″ and tanδ range from 40 to 80, 0 to 16, and 0.04 to 0.2, respectively, as shown in Figure 6e,f. The impurities, disorders, or additional phases might be clarified in the construction. With an increase in temperature, the joint effect leads to a rise in the values of Є′ and Є″. This may be attributed to the ion jump and space charge effects induced by rising concentrations of the charge carriers. Also, the rising temperature enhances the growth of molecules. It can be supposed that this structure enhanced the dielectric properties Є′, Є″, and tanδ with annealing [25,26]. It is clear that with increasing frequency, Є′ has shown significant improvements, while Є″ and tanδ are decreased, increasing capacitors’ ability to store energy and reduce heating loss.

Figure 6.

(a–f) Є′, Є″, tanδ versus Tk at different voltages and constant different frequencies (105, 2 × 107 Hz, respectively) for the Au/PVA/SiO2/p-Si/Al structure.

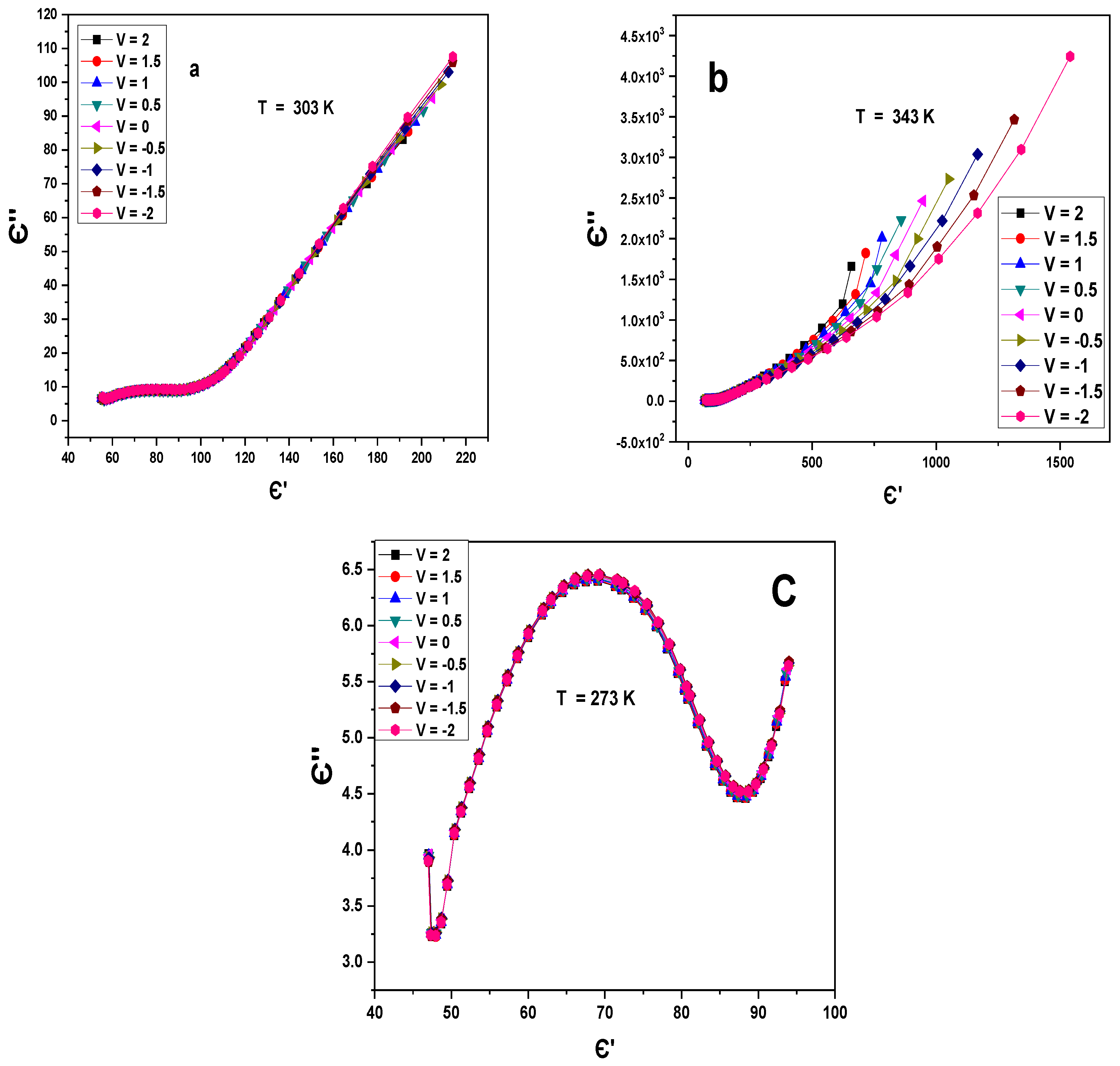

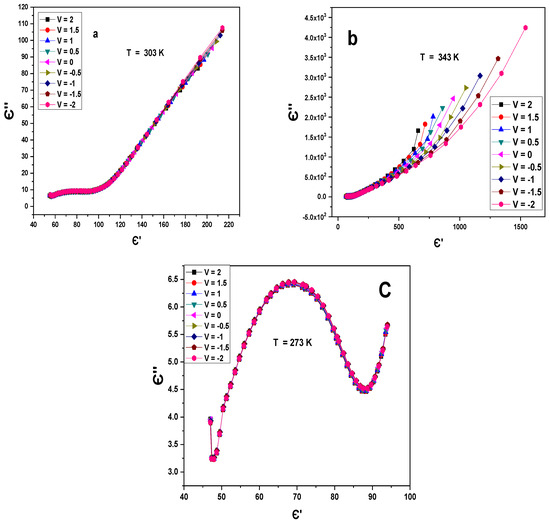

Figure 7 displays the variation of the dielectric loss (Є″) with a dielectric constant (Є′) of impedance at different voltages and constant temperatures for Au/PVA/SiO2/p-Si/Al. Entirely, the figures display a reduction in the radius of the partly shaped semicircles and shrinkage near the origin due to the rising ionic conductivity and declining resistance of the films [27,28].

Figure 7.

(a–c) Є″-Є′ at different voltages and constant temperatures for the Au/PVA/SiO2/p-Si/Al structure.

2.3. The Current–Voltage (I–V) Characteristic

The current–voltage characteristics of the diode were explained according to the thermionic emission model [29,30,31]:

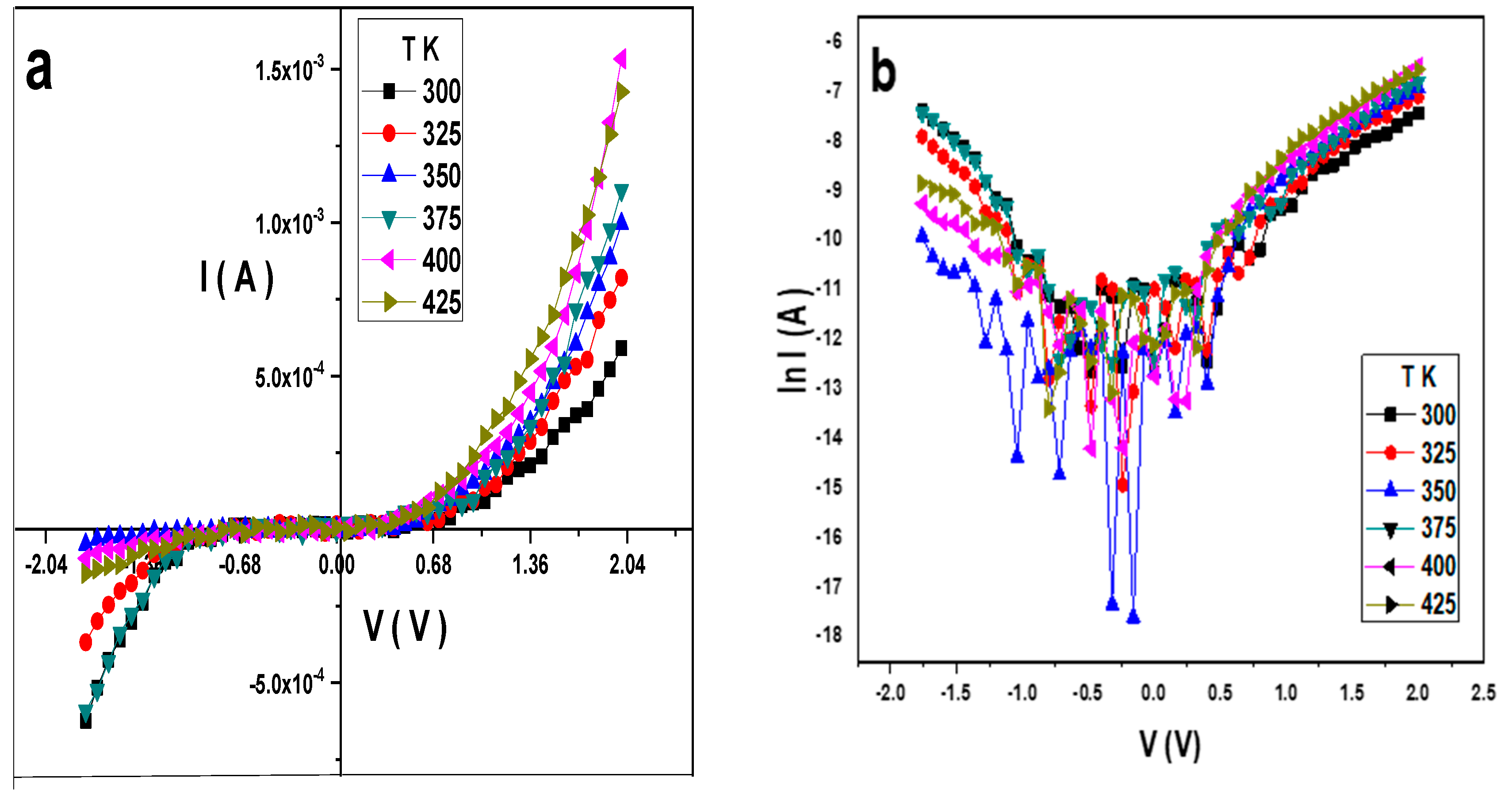

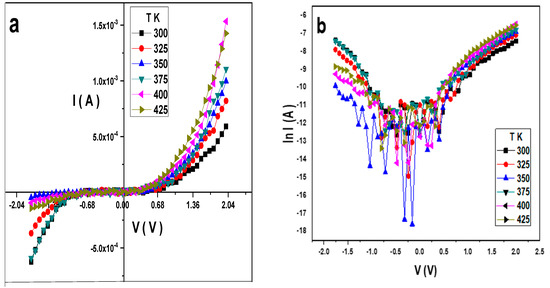

Figure 8a illustrates the I–V characteristic for the Au/PVA/SiO2/p-Si/Al heterostructure diode at different temperatures, while Figure 8b displays the diode’s lnI–V semilogarithmic behavior.

Figure 8.

(a) I–V, and (b) lnI–V at different temperatures for the Au/PVA/SiO2/p-Si/Al structure.

The barrier height can be expressed by [32,33]:

where I0 is the saturation current, V is the applied voltage, Rs is the series resistance, n is the ideality factor, T is the temperature in Kelvin, q is the electronic charge, k is the Boltzmann constant, φb is the Schottky barrier height, A* is the Richardson constant, and A is the contact area of the diode. The intersection of the inserted straight lines of the linear part with the current axis obtained the I0. The ideality factor (n) can be determined using Equation (1) as [33,34]:

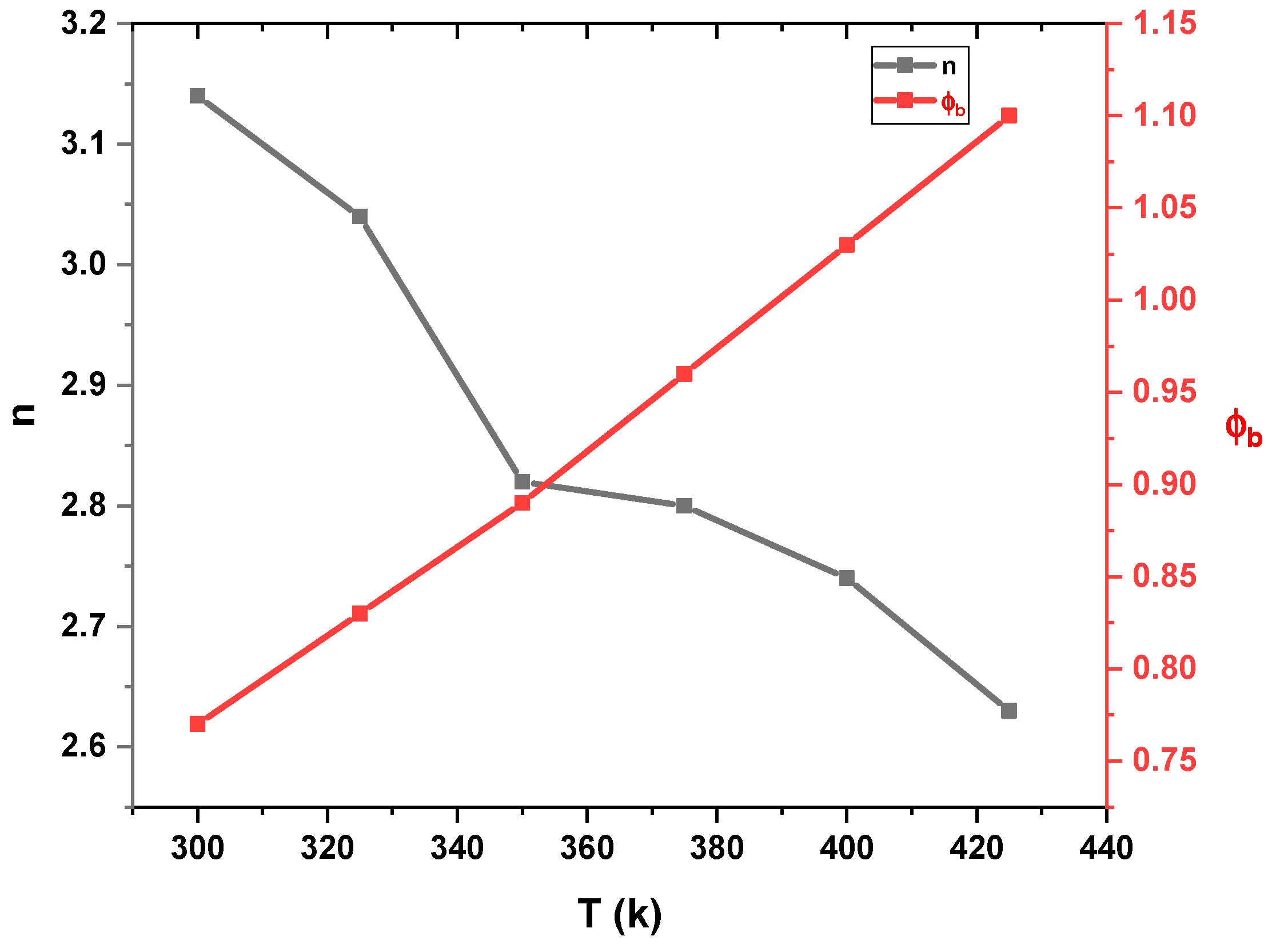

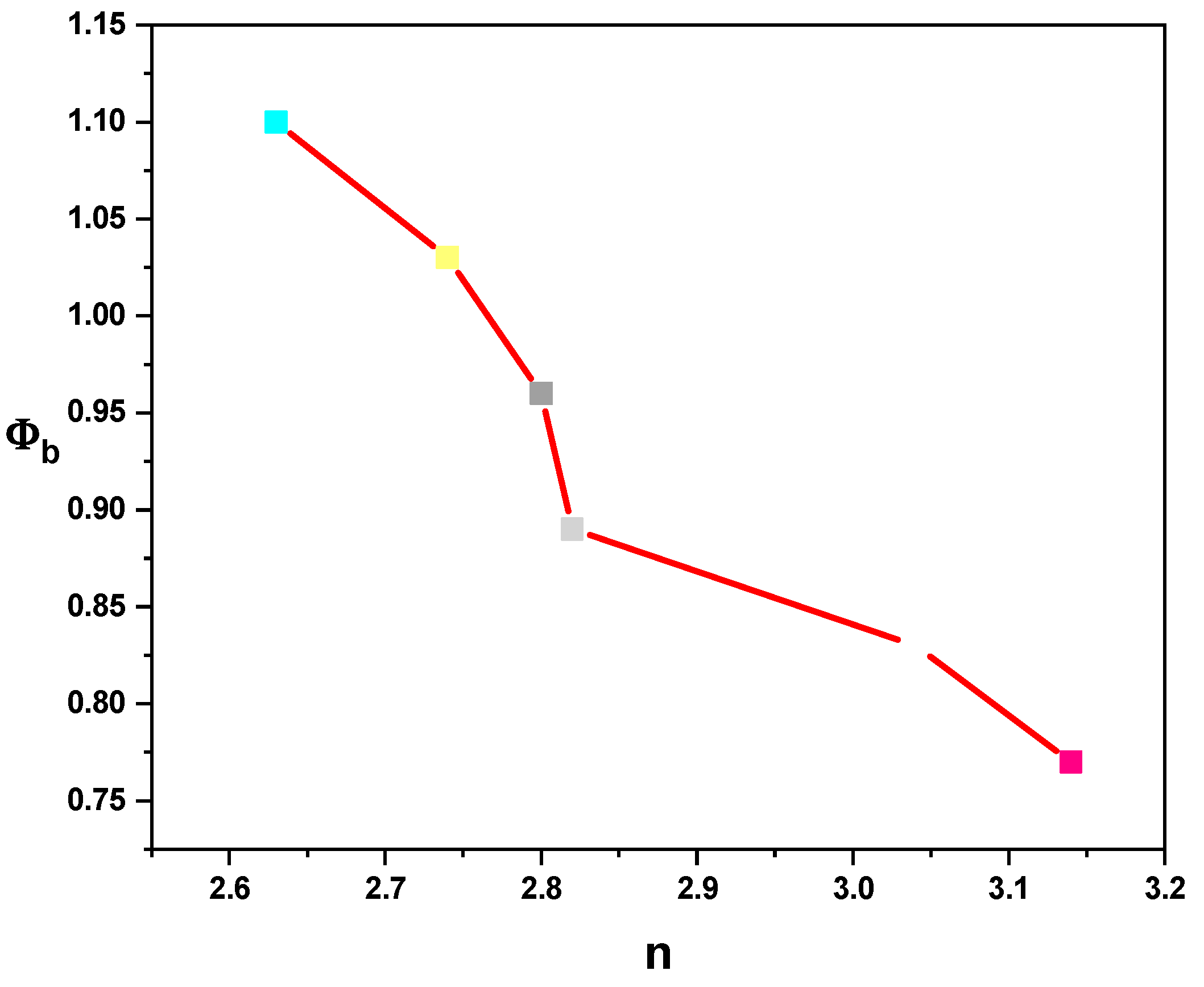

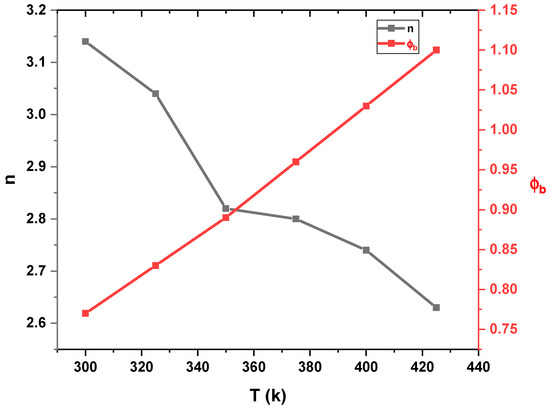

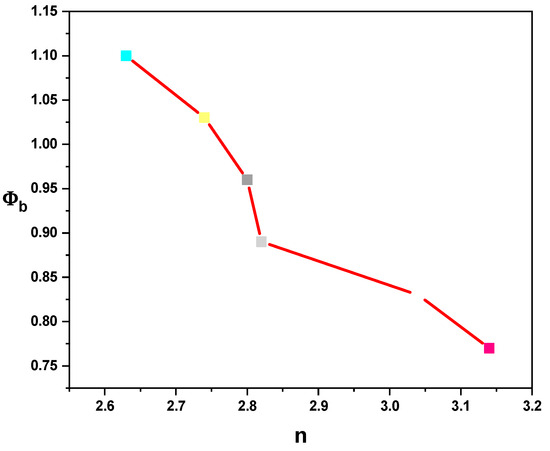

From Equations (1) and (2), ɸb increases with the temperature, while n decreases, as illustrated in Figure 9, and their values are listed in Table 1. Based on Equation (3), the high value of the ideality factor was attributed to the presence of a thin oxide layer and series resistance [23]. Since the non-homogeneous barrier height contributes to the higher value of the ideality factor [35,36], the higher value of n can be explained in terms of secondary mechanisms such as border dips and interfacial imperfections, which are produced by an organic interlayer or a specific border structure [37]. The variation of the barrier height with the ideality factor is illustrated in Figure 10.

Figure 9.

n and ɸb versus T for the Au/PVA/SiO2/p-Si/Al structure.

Table 1.

Calculated ideality factor, series resistance, shunt resistance, and Au/PVA/SiO2/p-Si/Al barrier height at different temperatures.

Figure 10.

ɸb versus n for the Au/PVA/SiO2/p-Si/Al structure.

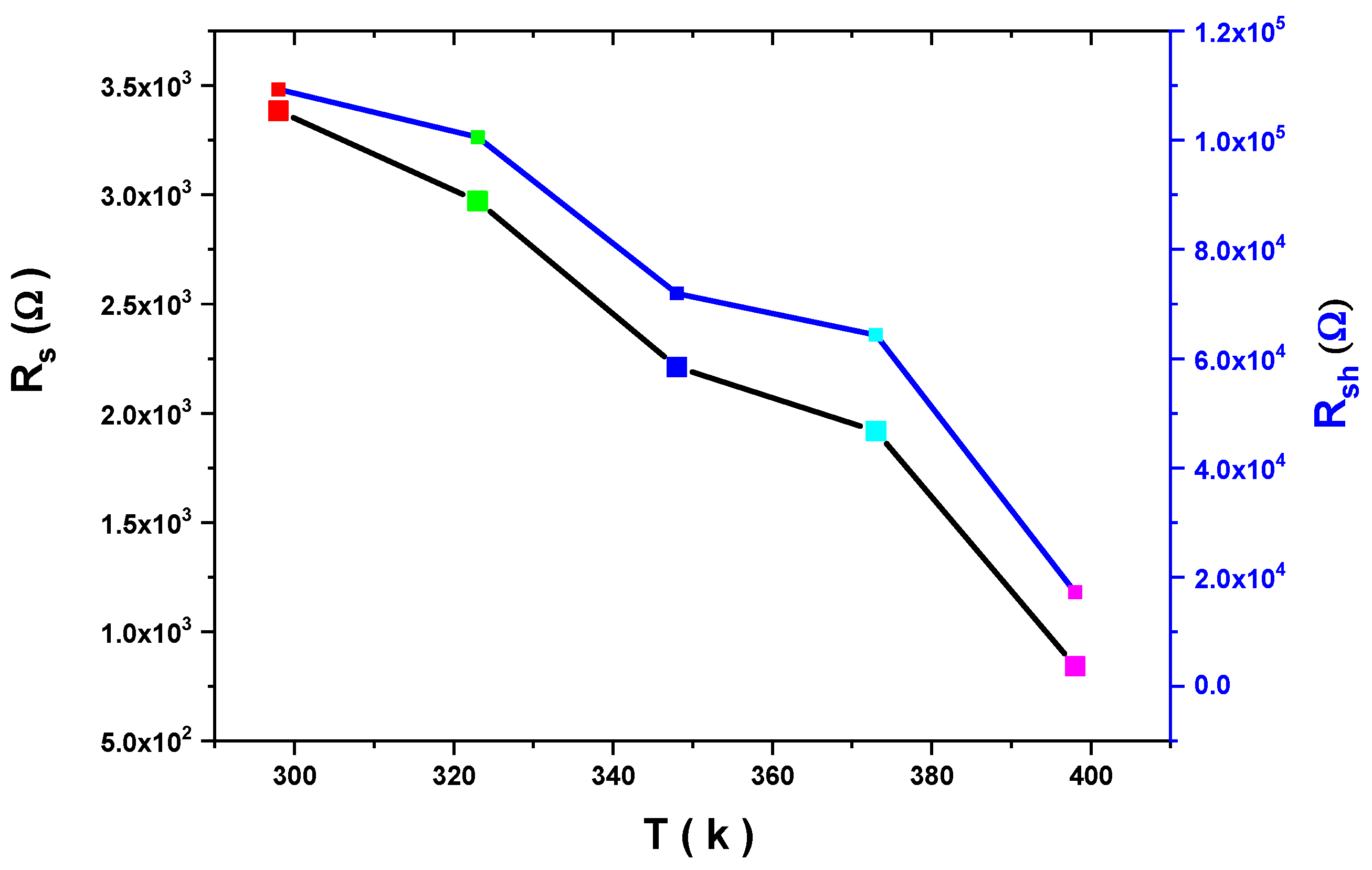

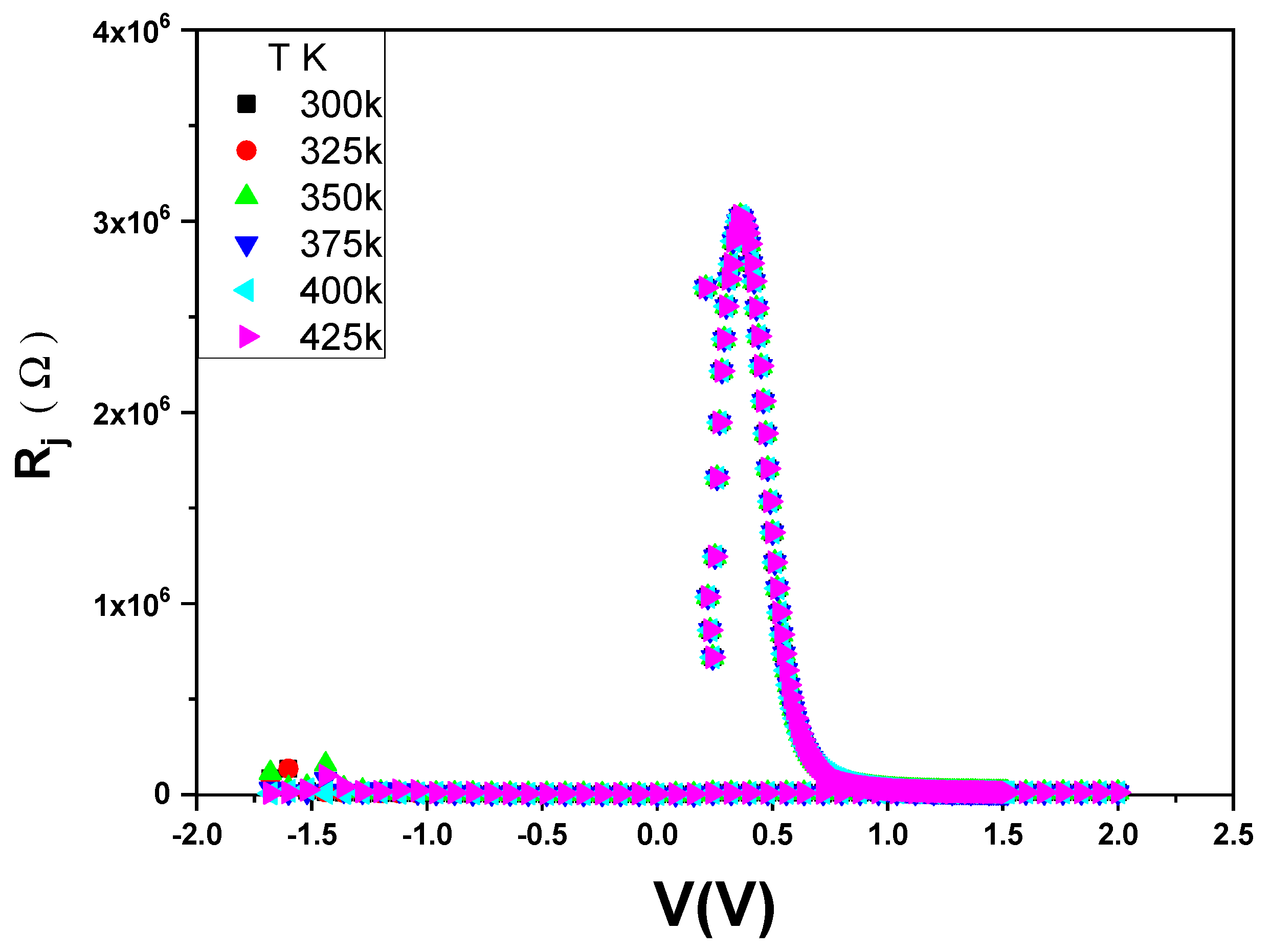

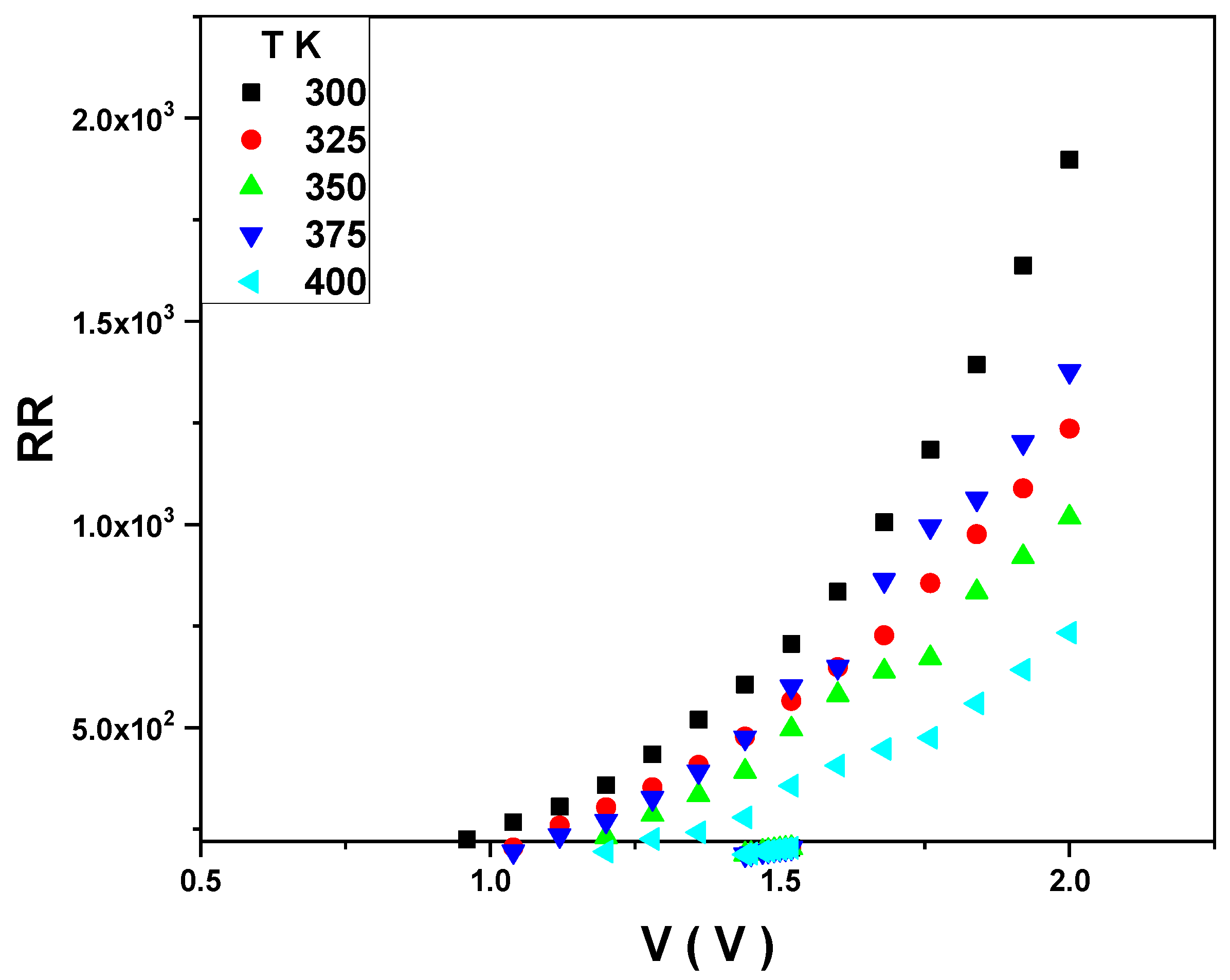

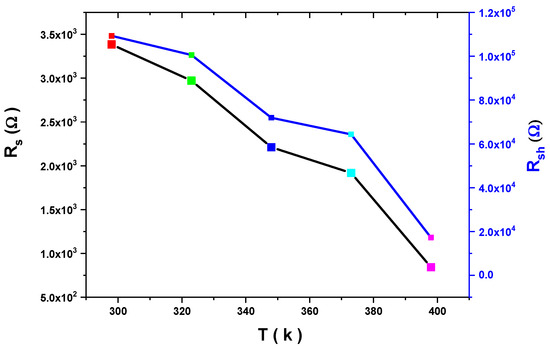

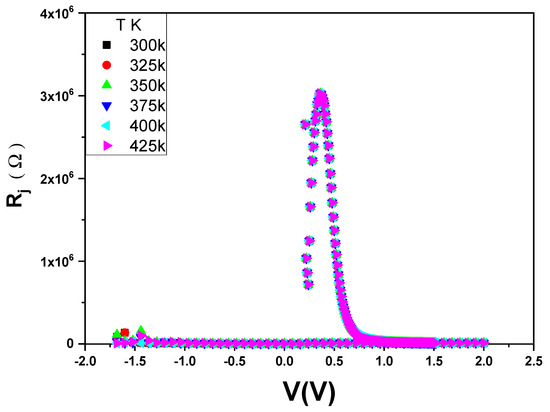

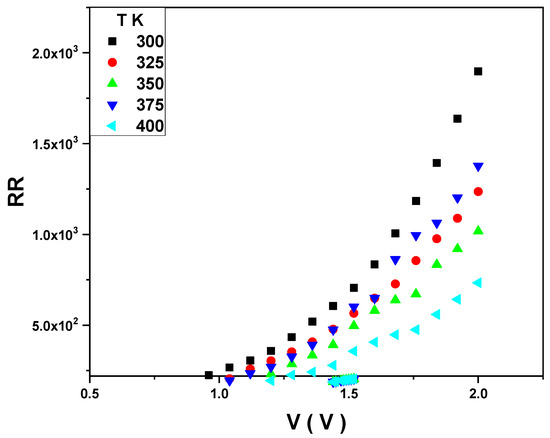

In addition to that, Rs and Rsh decrease with an increasing temperature. As illustrated in Figure 11, Rs and Rsh have a significant value due to the thin SiO2 layer between the PVA and Si layers. The variation of the junction resistance (Rj) with the applied voltage is shown in Figure 12. In contrast, the rectification ratio with a voltage at different temperatures is illustrated in Figure 13. The RR has good values at any temperature, confirming that the diode has a reasonable rectification.

Figure 11.

Rs and Rsh versus T for the Au/PVA/SiO2/p-Si/Al structure.

Figure 12.

Rj versus V at different temperatures for the Au/PVA/SiO2/p-Si/Al structure.

Figure 13.

RR versus V at different temperatures for the Au/PVA/SiO2/p-Si/Al structure.

3. Conclusions

In this study, we successfully fabricated an Au/PVA/SiO2/p-Si/Al structure, which was not previously reported. We investigated the variation of the dielectric constant (Є′), dielectric loss (Є″), and dielectric tangent (tanδ) across different frequencies, voltages, and temperatures. Our findings demonstrate an increase in the dielectric constant (Є′) and a reduction in both the dielectric loss (Є″) and tangent (tanδ). These results suggest that the Au/PVA/SiO2/p-Si/Al structure presents new opportunities for advancements in the semiconductor industry, particularly in capacitor manufacturing. Additionally, we systematically analyzed previous studies, examining the undesirable behaviors of Є′ and Є″. Cole–Cole diagrams of Є″ and Є′ under various voltages and temperatures were analyzed. We also performed I–V measurements and assessed electrical parameters such as the ideality factor, series resistance, shunt resistance, rectification ratio, and barrier height at different temperatures.

4. Materials and Methods

The Au/PVA/SiO2/p-Si/Al was synthesized by cleaning a single crystal wafer of silicon to eliminate all the contamination that exists on the surface. The silicon wafer was left to be oxidized in a furnace at 1170 k for thirty minutes, creating an oxide layer (SiO2). An aqueous gel solution of PVA was deposited on the surface of the SiO2/Si using the spin-coating technique. The Au/PVA/SiO2/p-Si/Al heterostructure was left to dry at a temperature of 223 k, and then a gold electrode was deposited on the top and aluminum as a lower electrode of the structure of the Au/PVA/SiO2/p-Si/Al using thermal evaporation.

Author Contributions

Conceptualization, A.A. and A.E.H.G.; Validation, A.A., A.E.H.G. and M.A.B.-M.K.; Formal analysis, A.E.H.G.; Investigation, G.M.T. and M.A.B.-M.K.; Resources, G.M.T.; Writing—original draft, A.E.H.G., G.M.T. and M.A.B.-M.K.; Writing—review & editing, A.A. and M.A.B.-M.K.; Visualization, A.A., A.E.H.G., G.M.T. and M.A.B.-M.K. All authors have read and agreed to the published version of the manuscript.

Funding

This research received no external funding.

Institutional Review Board Statement

Not applicable.

Informed Consent Statement

Not applicable.

Data Availability Statement

The original contributions presented in the study are included in the article, further inquiries can be directed to the corresponding author.

Conflicts of Interest

The authors declare no conflicts of interest.

References

- Tian, M.; Qiao, M.; Shen, C.; Meng, F.; Frank, L.A.; Krasitskaya, V.V.; Wang, T.; Zhang, X.; Song, R.; Li, Y.; et al. Highly-Sensitive Graphene Field Effect Transistor Biosensor Using PNA and DNA Probes for RNA Detection. Appl. Surf. Sci. 2020, 527, 146839. [Google Scholar] [CrossRef]

- Li, W.; Zhou, S.; Zhang, L.; Yang, Z.; Chen, H.; Chen, W.; Qin, J.; Shen, X.; Zhao, S. A Red Emitting Fluorescent Probe for Sensitively Monitoring Hydrogen Polysulfides in Living Cells and Zebrafish. Sens. Actuators B Chem. 2019, 284, 30–35. [Google Scholar] [CrossRef]

- Nicollian, E.H.; Brews, J.R. MOS (Metal Oxide Semiconductor) Physics and Technology; Wiley: New York, NY, USA, 1982. [Google Scholar]

- Karataş, Ş. Studies on Electrical and the Dielectric Properties in MS Structures. J. Non-Cryst. Solids 2008, 354, 3606–3611. [Google Scholar] [CrossRef]

- Deuling, H.; Klausmann, E.; Goetzberger, A. Interface States in Si-SiO2 Interfaces. Solid State Electron. 1972, 15, 559–571. [Google Scholar] [CrossRef]

- Yıldız, D.E.; Dökme, I.İ.; Yildiz, D.E.; Dökme, I.İ. Frequency and Gate Voltage Effects on the Dielectric Properties and Electrical Conductivity of Al/SiO2/p-Si Metal-Insulator-Semiconductor Schottky Diodes. J. Appl. Phys. 2011, 110, 14507. [Google Scholar] [CrossRef]

- Demirezen, S.; Tanrıkulu, E.E.; Altındal, Ş. The Study on Negative Dielectric Properties of Al/PVA (Zn-Doped)/p-Si (MPS) Capacitors. Indian J. Phys. 2019, 93, 739–747. [Google Scholar] [CrossRef]

- Yildiz, D.E.; Apaydın, D.H.; Toppare, L.; Cirpan, A. Dielectric and Electrical Properties of an Organic Device Containing Benzotriazole and Fluorene Bearing Copolymer. J. Appl. Polym. Sci. 2013, 128, 1659–1664. [Google Scholar] [CrossRef]

- Ersöz Demir, G.; Yücedağ, İ.; Azizian-Kalandaragh, Y.; Altındal, Ş. Temperature and Interfacial Layer Effects on the Electrical and Dielectric Properties of Al/(CdS-PVA)/p-Si (MPS) Structures. J. Electron. Mater. 2018, 47, 6600–6606. [Google Scholar] [CrossRef]

- Kar, S.; Varma, S. Determination of Silicon-silicon Dioxide Interface State Properties from Admittance Measurements under Illumination. J. Appl. Phys. 1985, 58, 4256–4266. [Google Scholar] [CrossRef]

- Kar, S.; Narasimhan, R.L. Characteristics of the Si-SiO2 Interface States in Thin (70–230 Å) Oxide Structures. J. Appl. Phys. 1987, 61, 5353–5359. [Google Scholar] [CrossRef]

- Demirezen, S.; Kaya, A.; Yerişkin, S.A.; Balbaşı, M.; Uslu, İ. Frequency and Voltage Dependent Profile of Dielectric Properties, Electric Modulus and Ac Electrical Conductivity in the PrBaCoO Nanofiber Capacitors. Results Phys. 2016, 6, 180–185. [Google Scholar] [CrossRef]

- Dökme, İ.; Altındal, Ş.; Gökçen, M. Frequency and Gate Voltage Effects on the Dielectric Properties of Au/SiO2/n-Si Structures. Microelectron. Eng. 2008, 85, 1910–1914. [Google Scholar] [CrossRef]

- Kar, S.; Dahlke, W.E. Interface States in MOS Structures with 20–40 Å Thick SiO2 Films on Nondegenerate Si. Solid State Electron. 1972, 15, 221–237. [Google Scholar] [CrossRef]

- Kanbur, H.; Altındal, Ş.; Tataroğlu, A. The Effect of Interface States, Excess Capacitance and Series Resistance in the Al/SiO2/p-Si Schottky Diodes. Appl. Surf. Sci. 2005, 252, 1732–1738. [Google Scholar] [CrossRef]

- Hill, W.A.; Coleman, C.C. A Single-Frequency Approximation for Interface-State Density Determination. Solid State Electron. 1980, 23, 987–993. [Google Scholar] [CrossRef]

- Nangia, R.; Shukla, N.K.; Sharma, A. Dielectric Properties of Al/PVA/p-Si (MPS) Structure as a Function of Frequency and Voltage. Mater. Today Proc. 2019, 17, 254–260. [Google Scholar] [CrossRef]

- Ashery, A.; Elnasharty, M.M.M.; Khalil, A.A.I.; Azab, A.A. Negative Resistance, Capacitance in Mn/SiO2/p-Si MOS Structure. Mater. Res. Express 2020, 7, 85901. [Google Scholar] [CrossRef]

- Arslan, E.; Şafak, Y.; Taşçioǧlu, I.; Uslu, H.; Özbay, E. Frequency and Temperature Dependence of the Dielectric and AC Electrical Conductivity in (Ni/Au)/AlGaN/AlN/GaN Heterostructures. Microelectron. Eng. 2010, 87, 1997–2001. [Google Scholar] [CrossRef]

- Aydin, M.; Al-ghamdi, A.; Al-Hartomy, O.; El-Tantawy, F.; Yakuphanoglu, F. Improved Electrical and Photosensing Properties of CuPc Phtalocyanine/p-Silicon Diode by Nanostructure. J. Optoelectron. Adv. Mater. 2012, 14, 798–803. [Google Scholar]

- Uslu, H.; Altındal, Ş.; Tunç, T.; Uslu, İ.; Mammadov, T.S. The Illumination Intensity and Applied Bias Voltage on Dielectric Properties of Au/Polyvinyl Alcohol (Co, Zn-Doped)/n-Si Schottky Barrier Diodes. J. Appl. Polym. Sci. 2011, 120, 322–328. [Google Scholar] [CrossRef]

- Kyritsis, A.; Pissis, P.; Grammatikakis, J. Dielectric Relaxation Spectroscopy in Poly(Hydroxyethyl Acrylates)/Water Hydrogels. J. Polym. Sci. Part B Polym. Phys. 1995, 33, 1737–1750. [Google Scholar] [CrossRef]

- Yücedağ, İ.; Altındal, Ş.; Tataroğlu, A. On the Profile of Frequency Dependent Series Resistance and Dielectric Constant in MIS Structure. Microelectron. Eng. 2007, 84, 180–186. [Google Scholar] [CrossRef]

- Thakur, Y.; Dong, R.; Lin, M.; Wu, S.; Cheng, Z.; Hou, Y.; Bernholc, J.; Zhang, Q.M. Optimizing Nanostructure to Achieve High Dielectric Response with Low Loss in Strongly Dipolar Polymers. Nano Energy 2015, 16, 227–234. [Google Scholar] [CrossRef]

- Fiat, S.; Polat, İ.; Bacaksiz, E.; Kompitsas, M.; Çankaya, G. The Influence of Annealing Temperature and Tellurium (Te) on Electrical and Dielectrical Properties of Al/p-CIGSeTe/Mo Schottky Diodes. Curr. Appl. Phys. 2013, 13, 1112–1118. [Google Scholar] [CrossRef]

- Ashery, A.; Elnasharty, M.M.M.; Farag, A.A.M.; Salem, M.A.; Nasralla, N. Electrical Performance and Photosensitive Properties of Cu/SiO2/Si –MOS Based Junction Prepared by Liquid Phase Epitaxy. Superlattices Microstruct. 2017, 109, 662–674. [Google Scholar] [CrossRef]

- Rhimi, T.; Leroy, G.; Duponchel, B.; Khirouni, K.; Guermazi, S.; Toumi, M. AC and DC Conductivity Study of LiH2PO4 Compound Using Impedance Spectroscopy. Ionics 2018, 24, 1305–1312. [Google Scholar] [CrossRef]

- Ashery, A.; Elnasharty, M.M.M.; Hameed, T.A. Investigation of Electrical and Dielectric Properties of Epitaxially Grown Au/n-GaAs/p-Si/Al Heterojunction. Opt. Quantum Electron. 2020, 52, 490. [Google Scholar] [CrossRef]

- Tuan, T.T.A.; Kuo, D.-H.; Li, C.-C.; Yen, W.-C. Schottky Barrier Characteristics of Pt Contacts to All Sputtering-Made n-Type GaN and MOS Diodes. J. Mater. Sci. Mater. Electron. 2014, 25, 3264–3270. [Google Scholar] [CrossRef]

- Anh Tuan, T.T.; Kuo, D.-H. Characteristics of RF Reactive Sputter-Deposited Pt/SiO2/n-InGaN MOS Schottky Diodes. Mater. Sci. Semicond. Process. 2015, 30, 314–320. [Google Scholar] [CrossRef]

- Ramesh, C.K.; Reddy, V.R.; Choi, C.-J. Electrical Characteristics of Molybdenum Schottky Contacts on N-Type GaN. Mater. Sci. Eng. B 2004, 112, 30–33. [Google Scholar] [CrossRef]

- Rajagopal Reddy, V.; Koteswara Rao, P. Annealing Temperature Effect on Electrical and Structural Properties of Cu/Au Schottky Contacts to n-Type GaN. Microelectron. Eng. 2008, 85, 470–476. [Google Scholar] [CrossRef]

- Tuan, T.T.A.; Kuo, D.-H.; Li, C.-C.; Li, G.-Z. Effect of Temperature Dependence on Electrical Characterization of P-n GaN Diode Fabricated by RF Magnetron Sputtering. Mater. Sci. Appl. 2015, 06, 809–817. [Google Scholar] [CrossRef][Green Version]

- Barış, B. Analysis of Device Parameters for Au/Tin Oxide/n-Si(100) Metal–Oxide–Semiconductor (MOS) Diodes. Phys. B Condens. Matter 2014, 438, 65–69. [Google Scholar] [CrossRef]

- Çınar, K.; Çaldıran, Z.; Coşkun, C.; Aydoğan, Ş. Electrochemical Growth of GaTe onto the P-Type Si Substrate and the Characterization of the Sn/GaTe Schottky Diode as a Function of Temperature. Thin Solid Film. 2014, 550, 40–45. [Google Scholar] [CrossRef]

- Ashery, A.; Farag, A.A.M.; Moussa, M.A.; Turky, G.M. Electrical Performance of Nanocrystalline Graphene Oxide/SiO2-Based Hybrid Heterojunction Device. Mater. Sci. Semicond. Process. 2021, 121, 105415. [Google Scholar] [CrossRef]

- Reddy, V.R. Electrical Properties of Au/Polyvinylidene Fluoride/n-InP Schottky Diode with Polymer Interlayer. Thin Solid Film. 2014, 556, 300–306. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).