DSP Processer-in-the-Loop Tests Based on Automatic Code Generation

Abstract

:1. Introduction

2. Materials and Methods

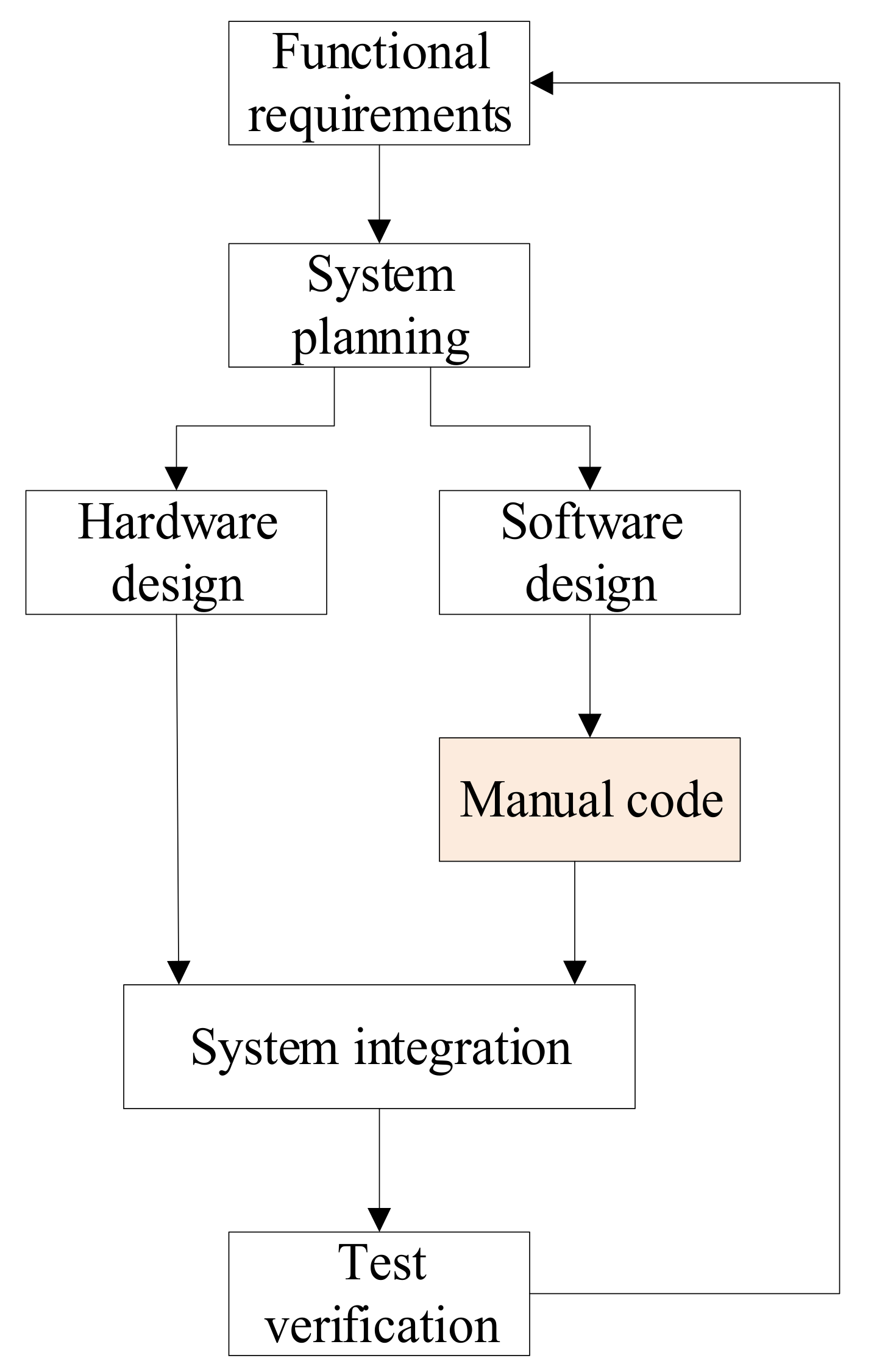

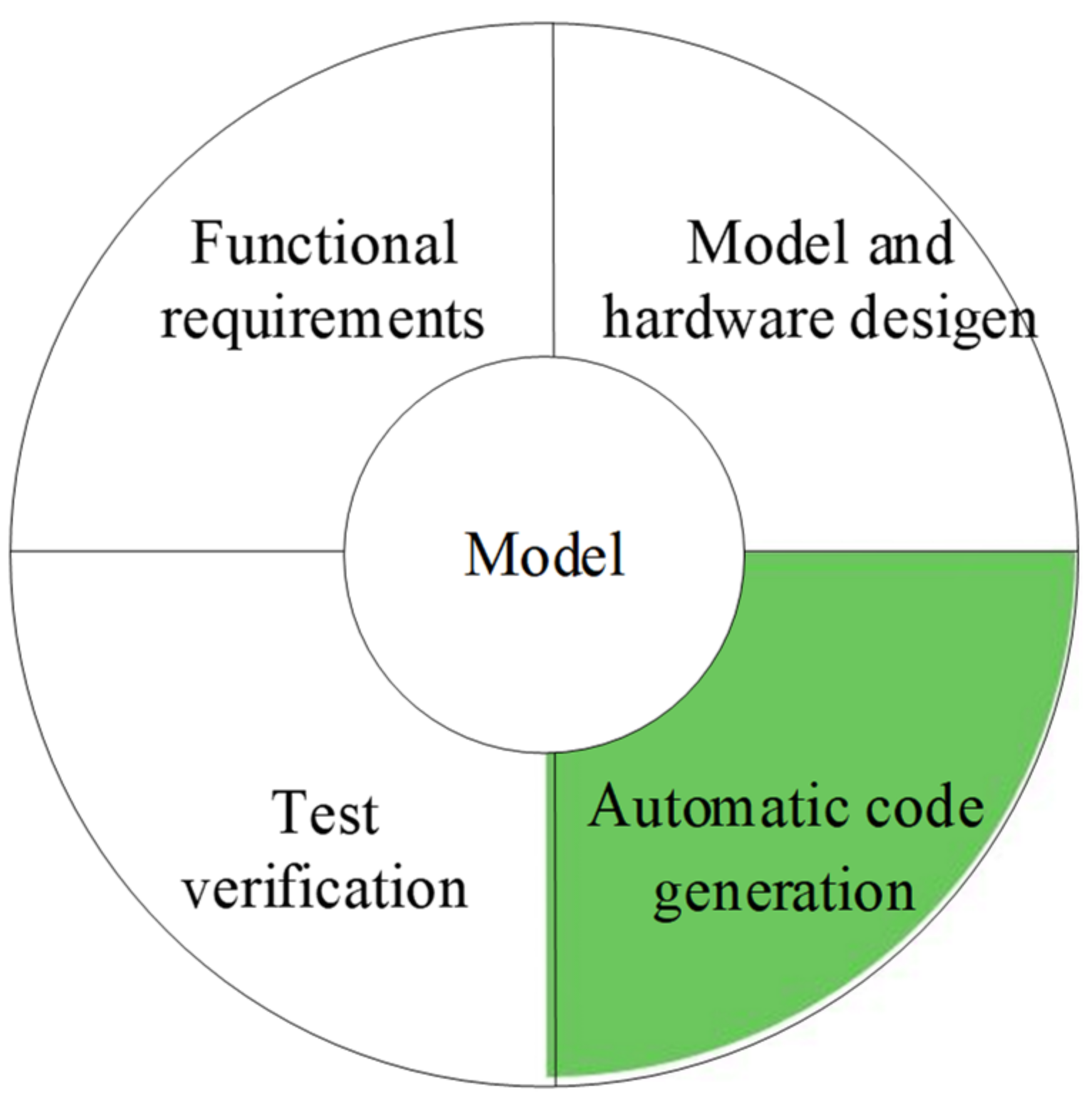

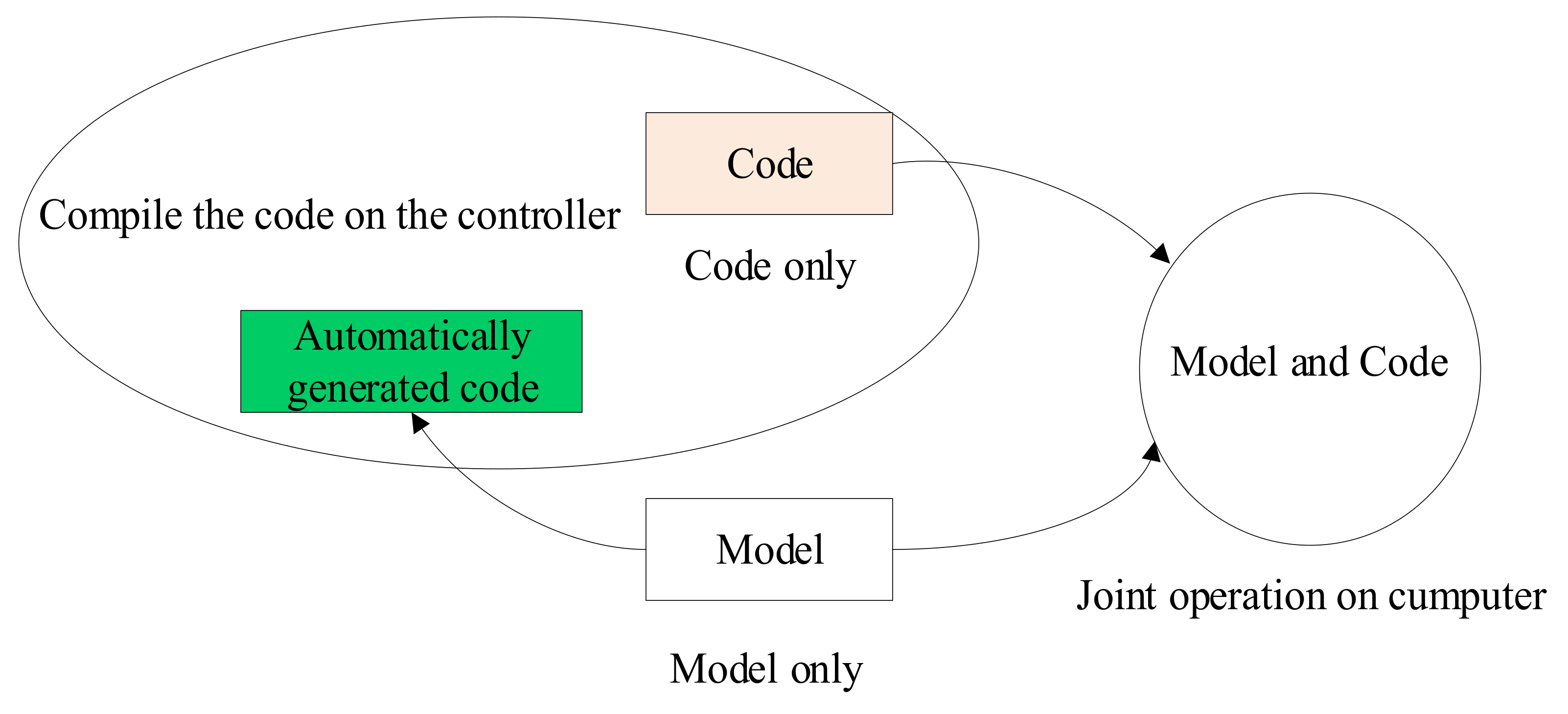

2.1. Model-Based Design and Development Mode

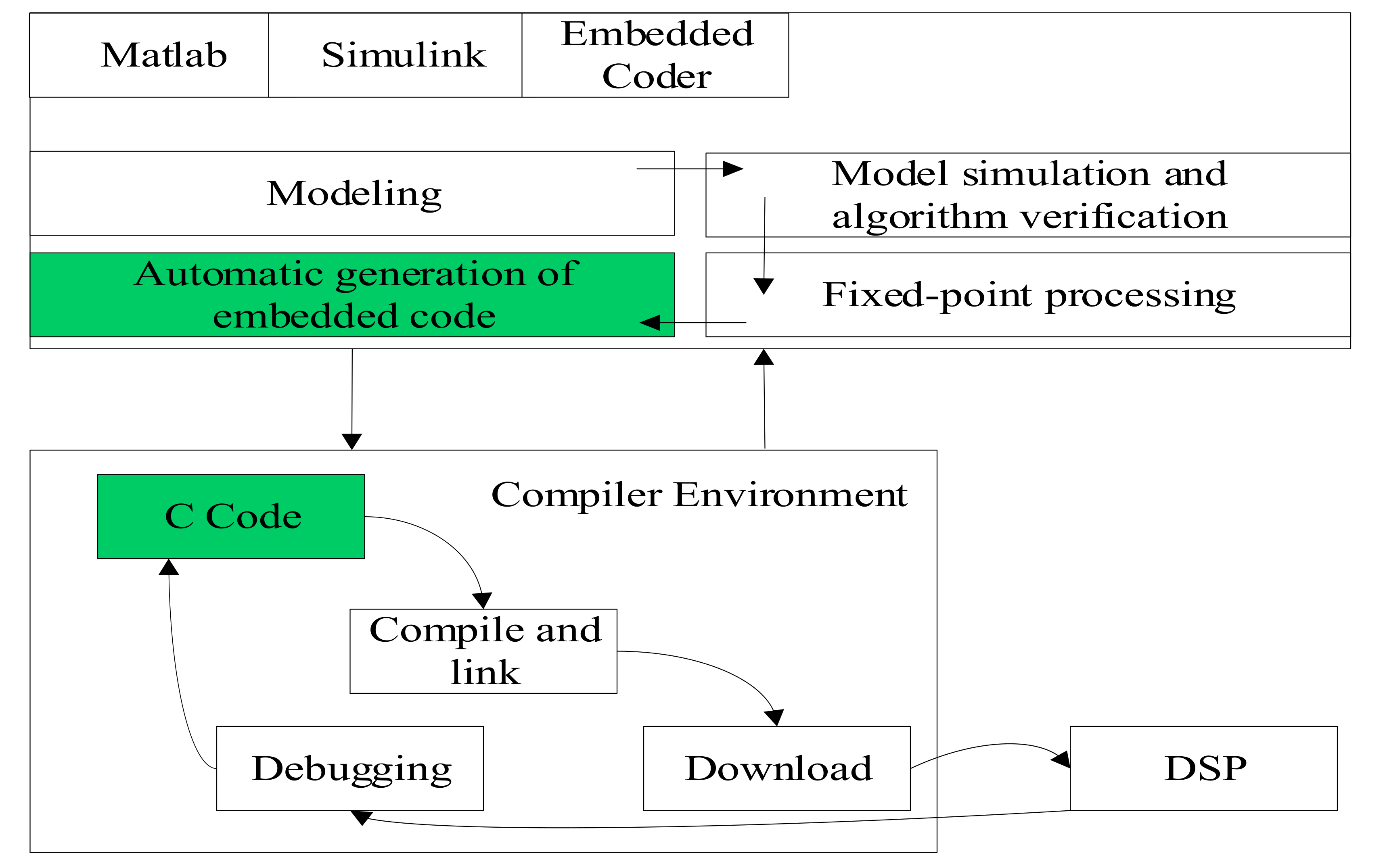

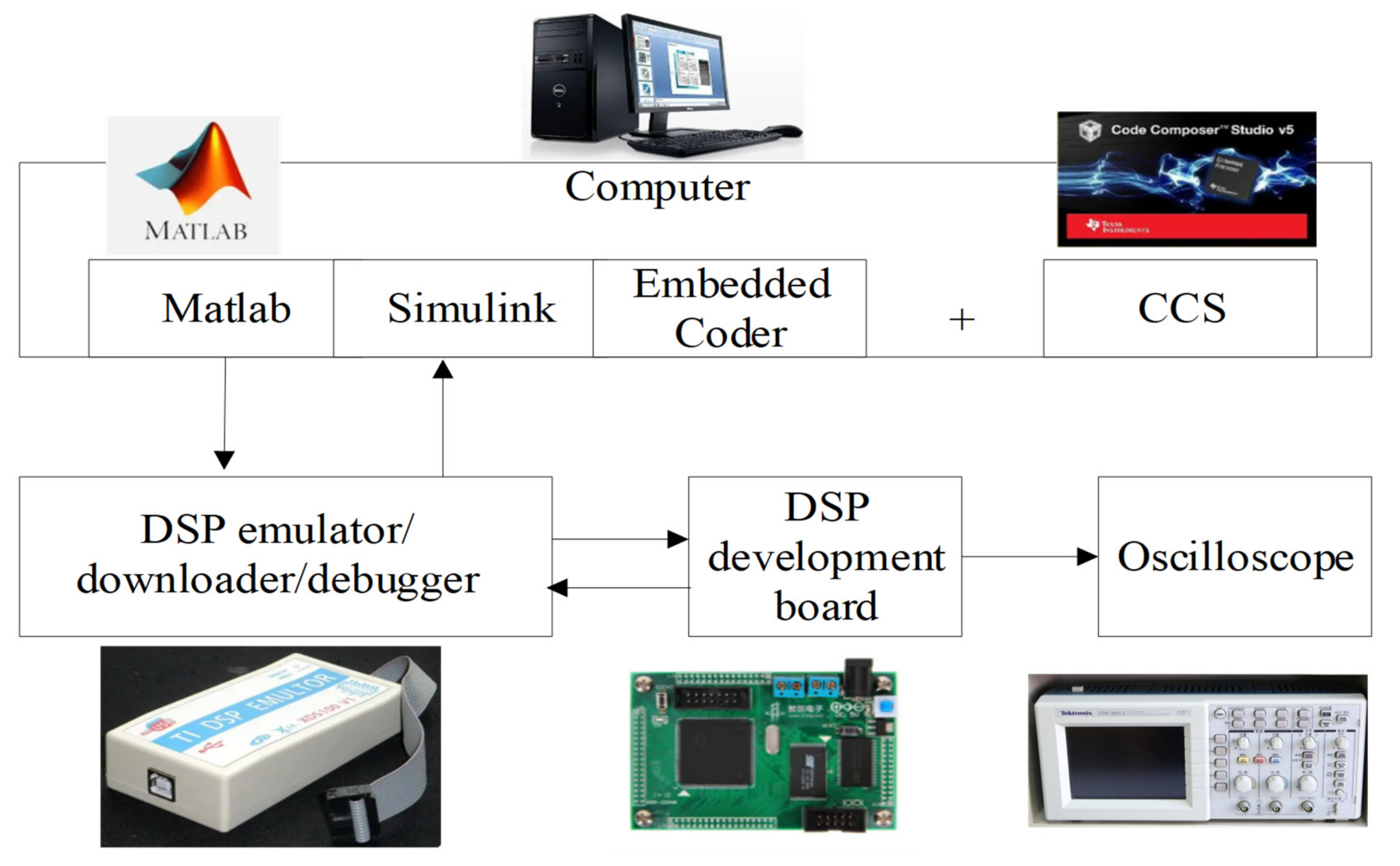

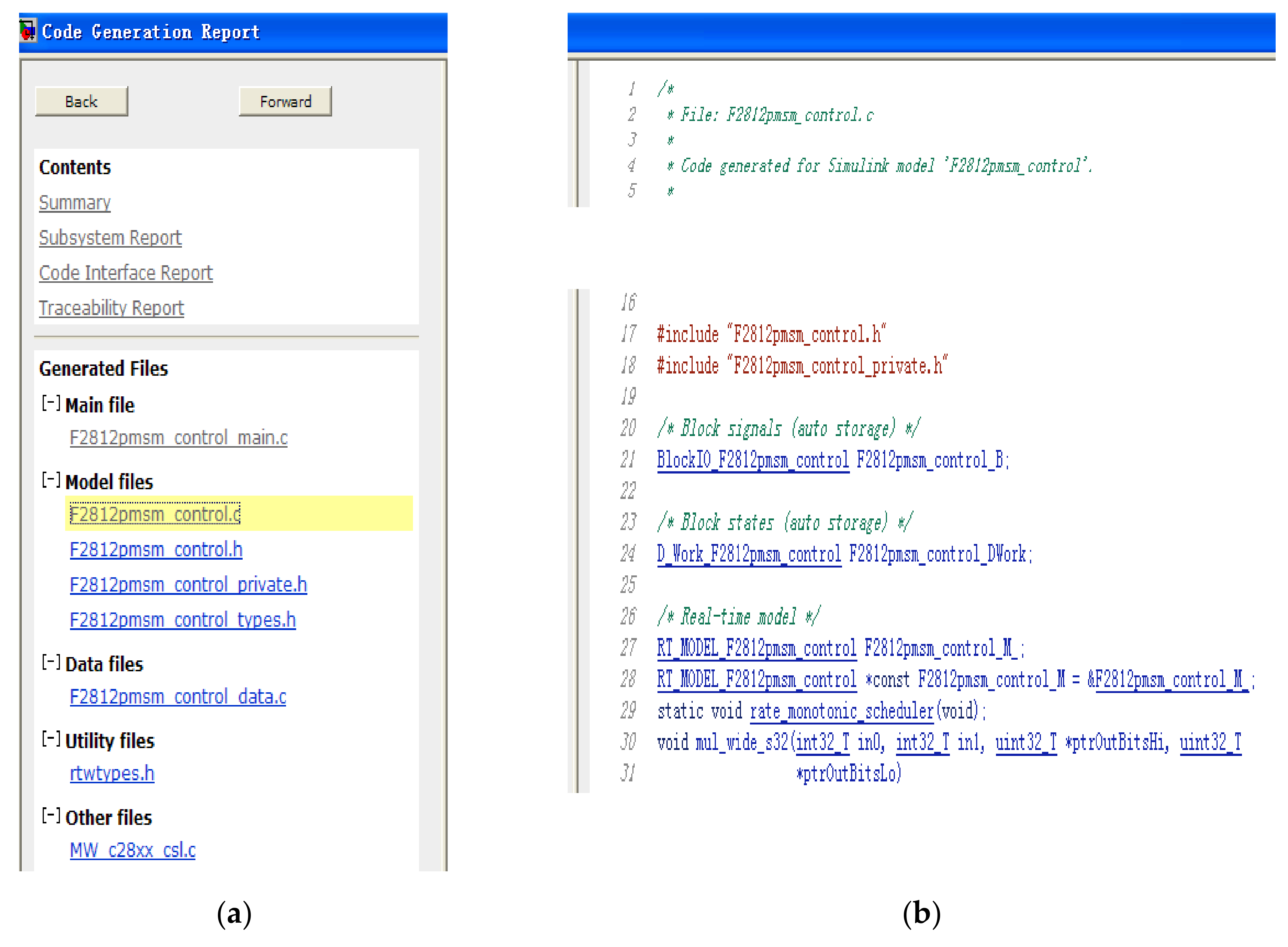

2.2. DSP Code Automatic Generation Based on MATLAB/Simulink

3. Results and Discussion

3.1. Experimental Platform

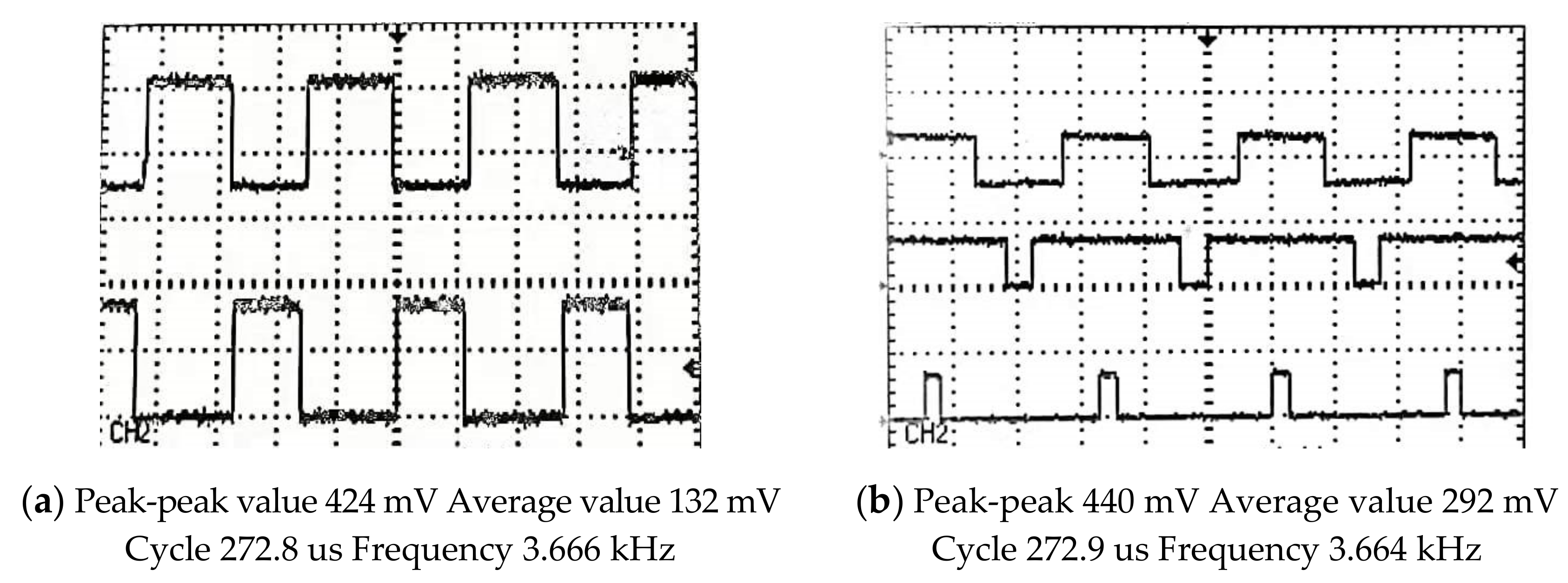

3.2. Experimental Results

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

Abbreviations

| AI | artificial intelligence |

| DMA | direct memory access |

| DSP | digital signal processing |

| FPGA | Field Programmable Gate Array |

| FPU | floating-point unit |

| HIL | hardware-in-the-loop |

| MBD | model-based design |

| MIL | model-in-the-loop |

| OTA | over-the-air technology |

| PIL | processer-in-the-loop |

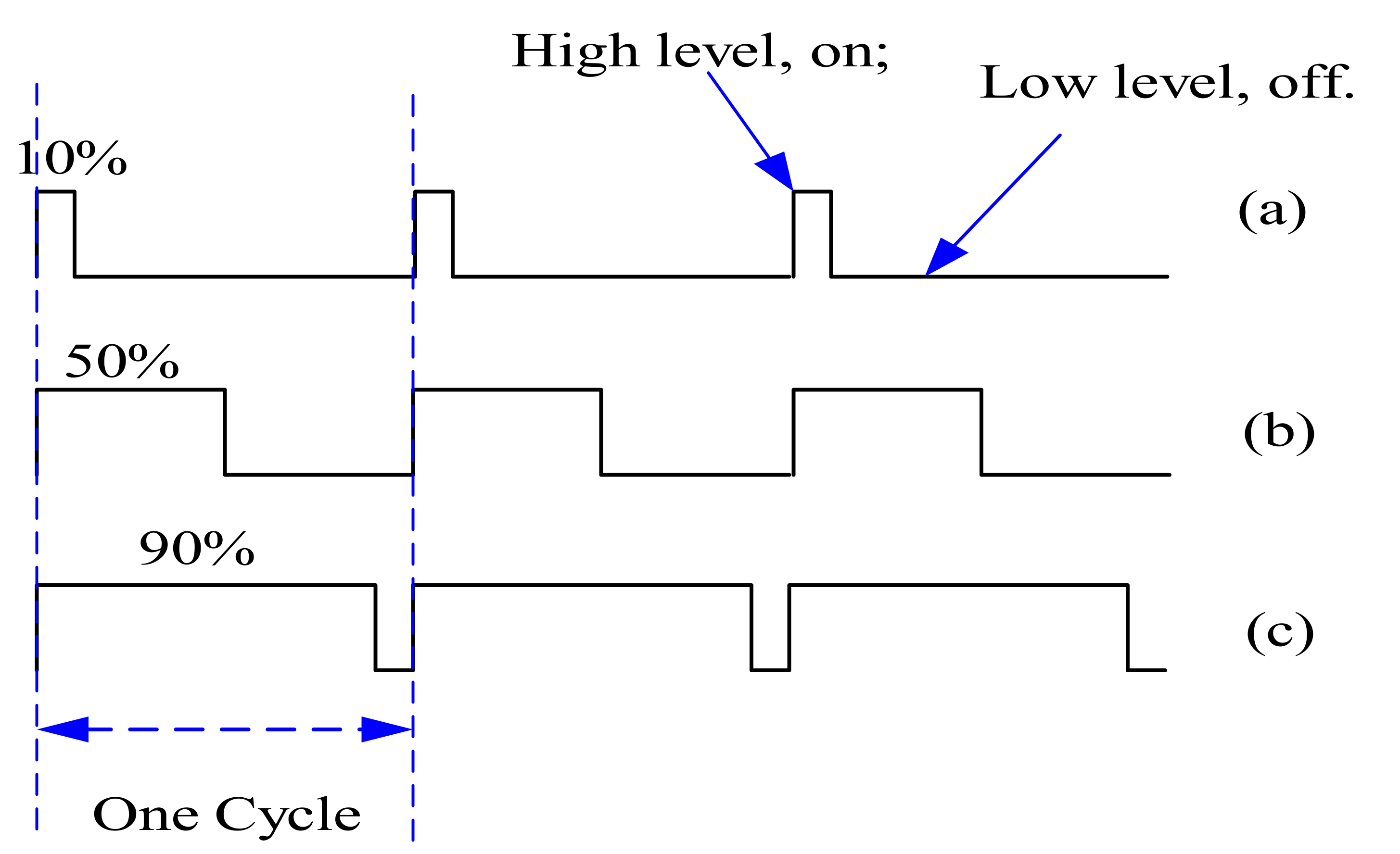

| PWM | pulse width modulation |

| SIL | software-in-the-loop |

References

- Qi, Z. Motor Controller Design Using dSPACE and Based on V-Mode Development. Res. Explor. Lab. 2014, 33, 141–144. [Google Scholar]

- Qi, Z.; Xiaoling, F.; Guojing, X. Implementation of a Rapid Prototyping Controller for asynchronous Motor. In Proceedings of the Chinese Automation Congress, Beijing, China, 22–24 October 2021. [Google Scholar]

- Shanghai Three Drivers Culture Media Co., Ltd. Where Is the Sale of Cars, Obviously It Is the Sale of Software, What Are the Models with 100 Million Lines of Software Code Written? 19 August 2020. Available online: http://k.sina.com.cn/article_6347788417_17a5b908100100pwm0.html (accessed on 2 January 2022).

- Jia, R. It May Introduce 4–6 Security Flaws per Thousand Lines of Code in Smart Vehicles. 27 May 2021. Available online: https://auto.sina.com.cn/news/2021-05-27/detail-ikmxzfmm5018318.shtml (accessed on 2 January 2022).

- Jie, L. Model-Based Design and Embedded Implementation; Beihang University Press: Beijing, China, 2010. [Google Scholar]

- Jie, L.; Gongyu, W.; Yubo, Z. Model-Based Design for MCU; Beihang University Press: Beijing, China, 2011. [Google Scholar]

- Tulpule, P.; Rezaeian, A.; Karumanchi, A.; Midlam-Mohler, S. Model Based Design (MBD) and Hardware In the Loop (HIL) validation: Curriculum development. In Proceedings of the American Control Conference, Seattle, WA, USA, 24–26 May 2017; pp. 5361–5366. [Google Scholar] [CrossRef]

- Xiangzhong, Y.; Jinwen, A.; Wenge, C. The Research on Application of Embedded Auto Code Generation. J. Proj. Rocket. Missiles Guid. 2008, 28, 250–257. [Google Scholar]

- Baxter, M. Task-processor mapping for real-time parallel systems using genetic algorithms with hardware-in-the-loop. In Proceedings of the First International Conference on Genetic Algorithms in Engineering Systems: Innovations and Applications, Sheffield, UK, 12–14 September 1995; pp. 158–163. [Google Scholar] [CrossRef]

- Kuznyetsov, O. Understanding the Basics of the Model-Based Techniques for Control Engineers with Simulink and BeagleBone Black: Processor-in-the-Loop Simulation of a DC Motor Speed Control. In Proceedings of the XIth International Scientific and Practical Conference on Electronics and Information Technologies (ELIT), Lviv, Ukraine, 16–18 September 2019; pp. 67–71. [Google Scholar] [CrossRef]

- Hu, M.; Zeng, G.; Yao, H.; Tang, Y. Processor-in-the-loop demonstration of coordination control algorithms for distributed spacecraft. In Proceedings of the 2010 IEEE International Conference on Information and Automation, Harbin, China, 20–23 June 2010; pp. 1008–1011. [Google Scholar] [CrossRef]

- Ruba, M.; Hunor, N.; Hedesiu, H.; Martis, C. FPGA based processor in the loop analysis of variable reluctance machine with speed control. In Proceedings of the IEEE International Conference on Automation, Quality and Testing, Robotics (AQTR), Los Angeles, CA, USA, 23–25 January 2016; pp. 1–6. [Google Scholar] [CrossRef]

- Mina, J.; Flores, Z.; Lopez, E.; Perez, A.; Calleja, J.-H. Processor-in-the-loop and hardware-in-the-loop simulation of electric systems based in FPGA. In Proceedings of the 13th International Conference on Power Electronics (CIEP), Chengdu, China, 24–27 October 2016; pp. 172–177. [Google Scholar] [CrossRef]

- Galarza, J. Software and Processor-in-the-Loop Execution for a Grid Connected Modular Multi-Level Converter. In Proceedings of the 2019 IEEE XXVI International Conference on Electronics, Electrical Engineering and Computing (INTERCON), Lima, Peru, 12–14 August 2019; pp. 1–4. [Google Scholar] [CrossRef]

- Liu, J.; Zhou, Y. Model-Based Design for DSP; National Defense Industry Press: Beijing, China, 2011. [Google Scholar]

- Lugang, W. PWM Inverter Based on New Space Vector Selection Model. Electr. Mach. Control Appl. 2001, 28, 27–30. [Google Scholar]

- Hu, H.; Yao, W.; Lu, Z. Design and Implementation of Three-Level Space Vector PWM IP Core for FPGAs. IEEE Trans. Power Electron. 2007, 22, 2234–2244. [Google Scholar] [CrossRef]

- Liu, X.; Zhang, Q. Robust Current Predictive Control-Based Equivalent Input Disturbance Approach for PMSM Drive. Electronics 2019, 8, 1034. [Google Scholar] [CrossRef] [Green Version]

- Zhao, Y.; Liu, X.; Zhang, Q. Predictive Speed-Control Algorithm Based on a Novel Extended-State Observer for PMSM Drives. Appl. Sci. 2019, 9, 2575. [Google Scholar] [CrossRef] [Green Version]

- Chen, P.; Zheng, J. PMLSM Servo System Design and Implement Based on DSP28335. Modul. Mach. Tool Autom. Manuf. Tech. 2013, 1, 80–83. [Google Scholar]

- Wei, T.; Renze, L.; Wengang, G.; Huiqi, Z. Design of DSP Minimum System Based on TMS320F28335. Ind. Control Comput. 2012, 4, 98–99. [Google Scholar]

| Abbreviation | Full Name | Meaning of Definition |

|---|---|---|

| MIL | Model-in-the-Loop | In the Simulink model, the control algorithm model and the controlled object model are connected to form a closed loop for simulation (a purely mathematical model). |

| SIL | Software-in-the-Loop | To verify that the automatically generated code and the original model used for code generation are consistent in function and behavior (a mathematical model and code). |

| PIL | Processer-In-the-Loop | The code generated runs on the actual controller in the PIL tests, so, in addition to verifying whether the code and the model are consistent, the longest running time of the algorithm on the actual controller can also be obtained (a mathematical model and actual controller). |

| HIL | Hardware-in-the-Loop | Different from PIL, HIL is used to test the controller system. The control system includes hardware, low-level software, and application-level software (real controller system and virtual real object). |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, Q.; Pei, W. DSP Processer-in-the-Loop Tests Based on Automatic Code Generation. Inventions 2022, 7, 12. https://doi.org/10.3390/inventions7010012

Zhang Q, Pei W. DSP Processer-in-the-Loop Tests Based on Automatic Code Generation. Inventions. 2022; 7(1):12. https://doi.org/10.3390/inventions7010012

Chicago/Turabian StyleZhang, Qi, and Wenhui Pei. 2022. "DSP Processer-in-the-Loop Tests Based on Automatic Code Generation" Inventions 7, no. 1: 12. https://doi.org/10.3390/inventions7010012

APA StyleZhang, Q., & Pei, W. (2022). DSP Processer-in-the-Loop Tests Based on Automatic Code Generation. Inventions, 7(1), 12. https://doi.org/10.3390/inventions7010012