Continuum Logic of Control Signals in Analog Cyber–Physical Nets

Abstract

:1. Introduction

2. Materials and Methods

2.1. Setting Goals and Objectives

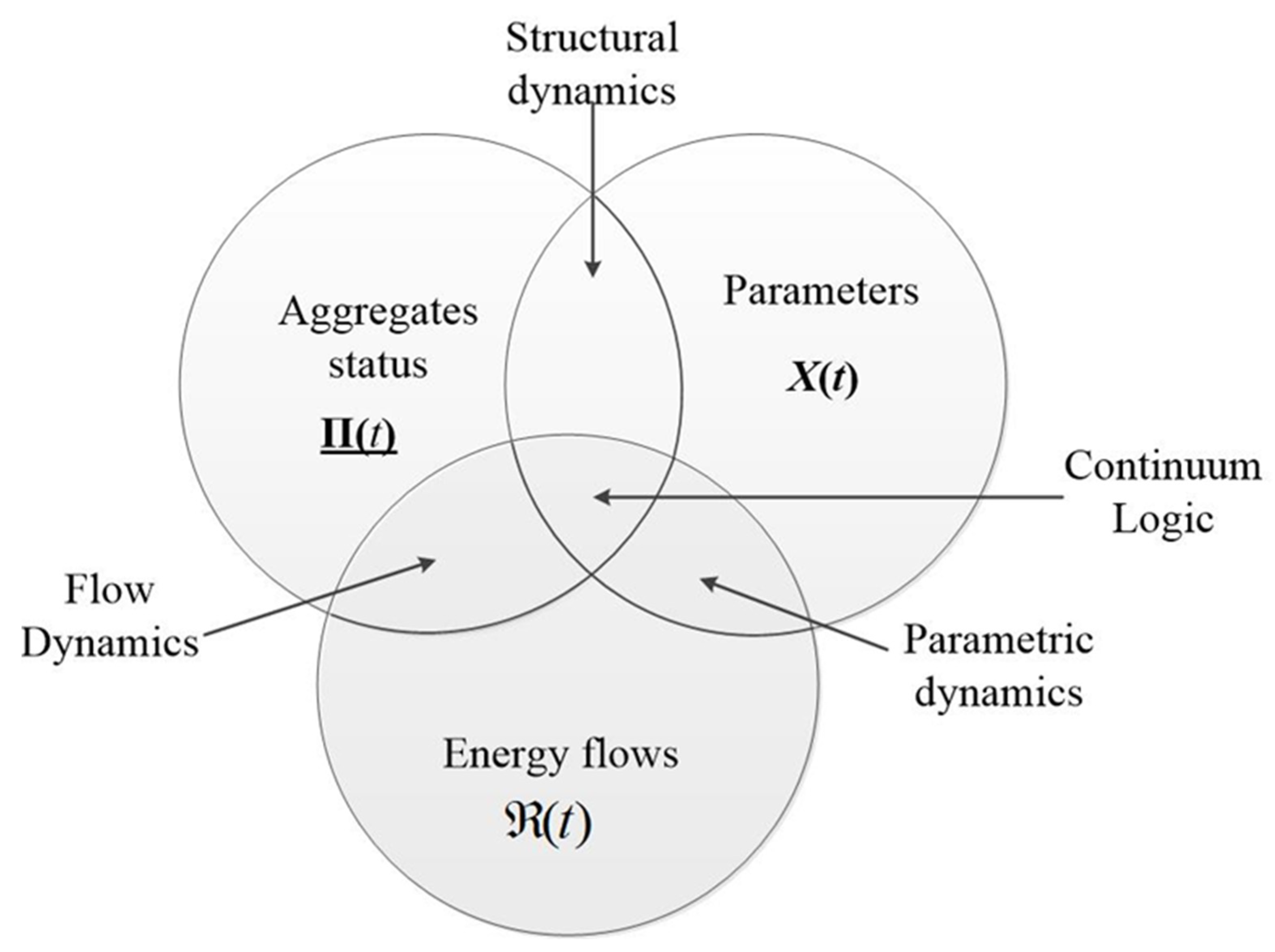

- a set of working aggregates Π(t) of the technical system;

- the set of energy flows (EF) synthesized by the aggregates ;

- a set of EF parameters X(t).

- parametric dynamics continuously captures the change in time of the parameters of the technical system δX(t);

- structural dynamics determines the change in time of the composition of the PhPr δP(t) with connected aggregates;

- flow dynamics determine the change in time of the set of EF transmitted over the network.

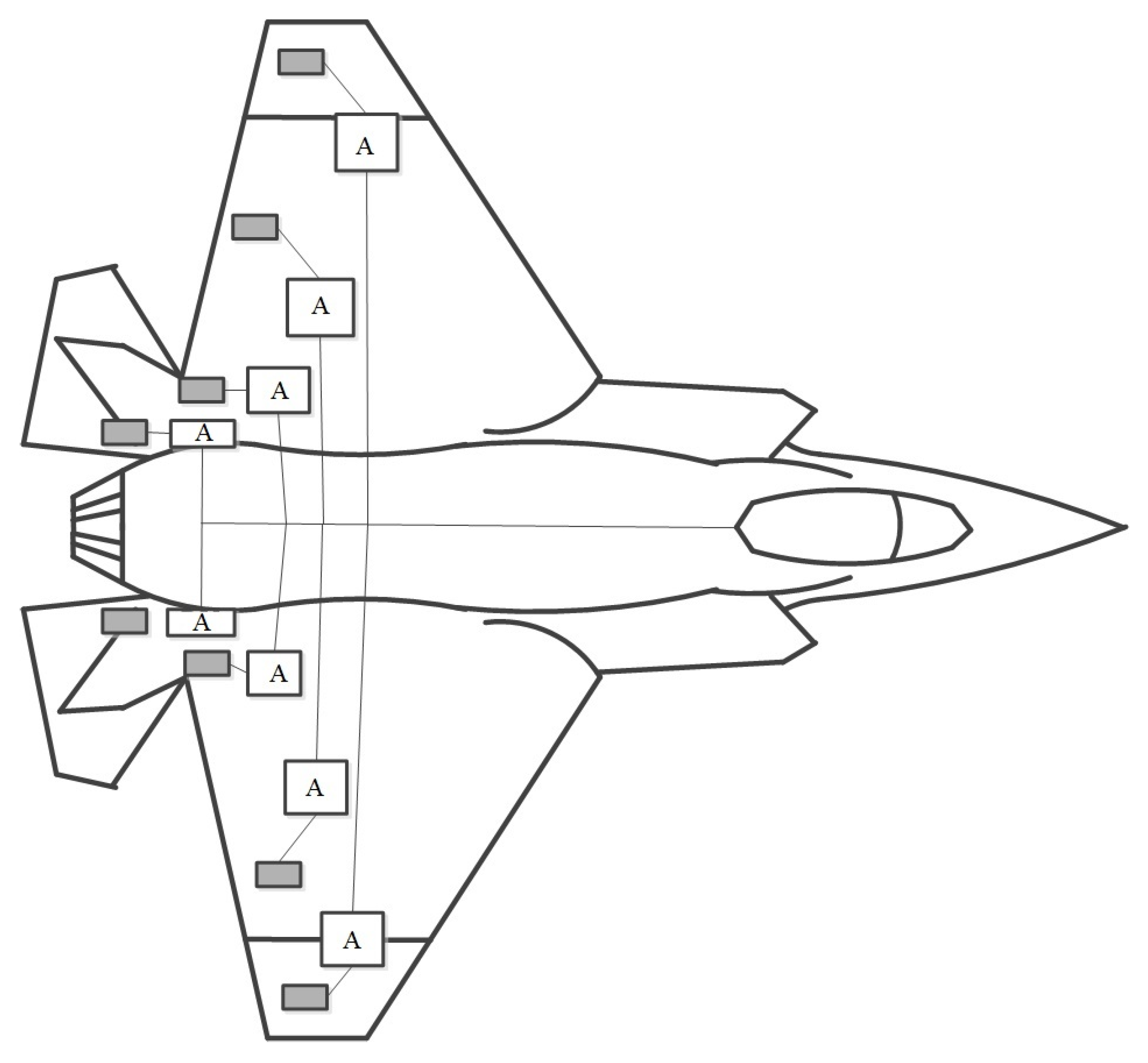

2.2. Analogue Cyber–Physical Networks

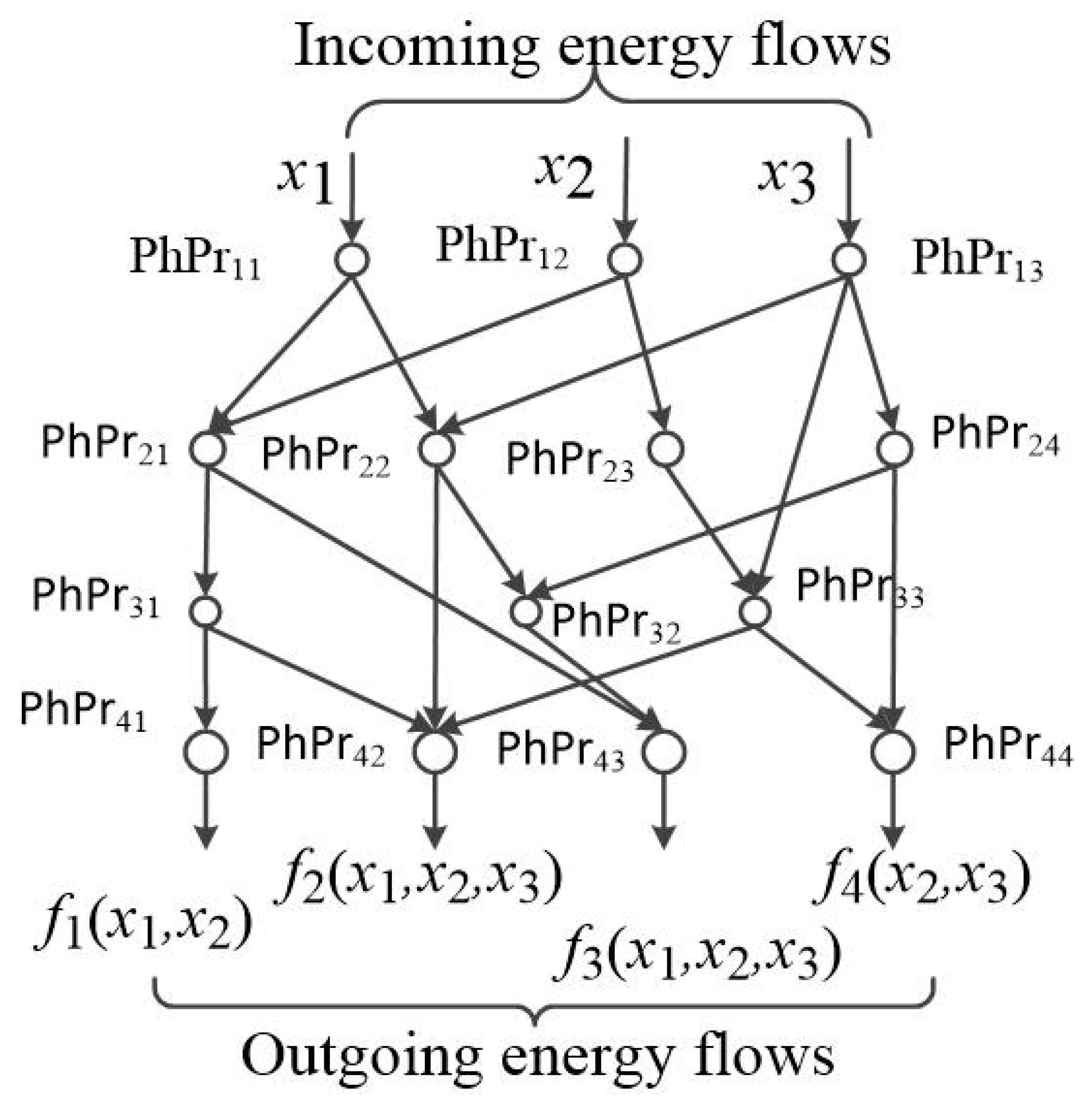

2.3. ACPN Structure

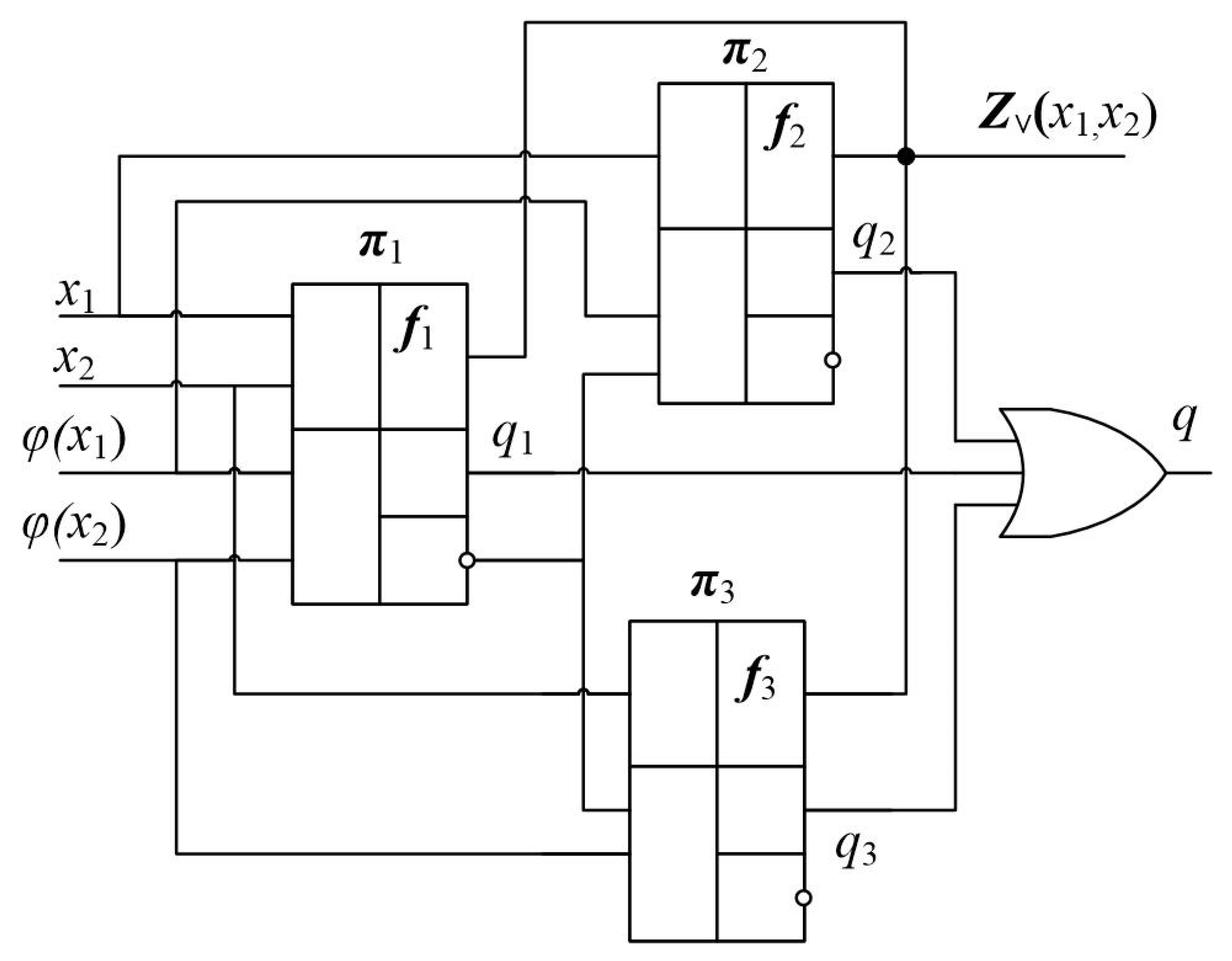

2.4. The ACPN Continuous Logic

2.5. Unary Operations of the Continuum Logic of Block Interaction in a Distributed Control Network

2.6. Binary Operations of the Continuum Logic of Block Interaction in a Distributed Control Network

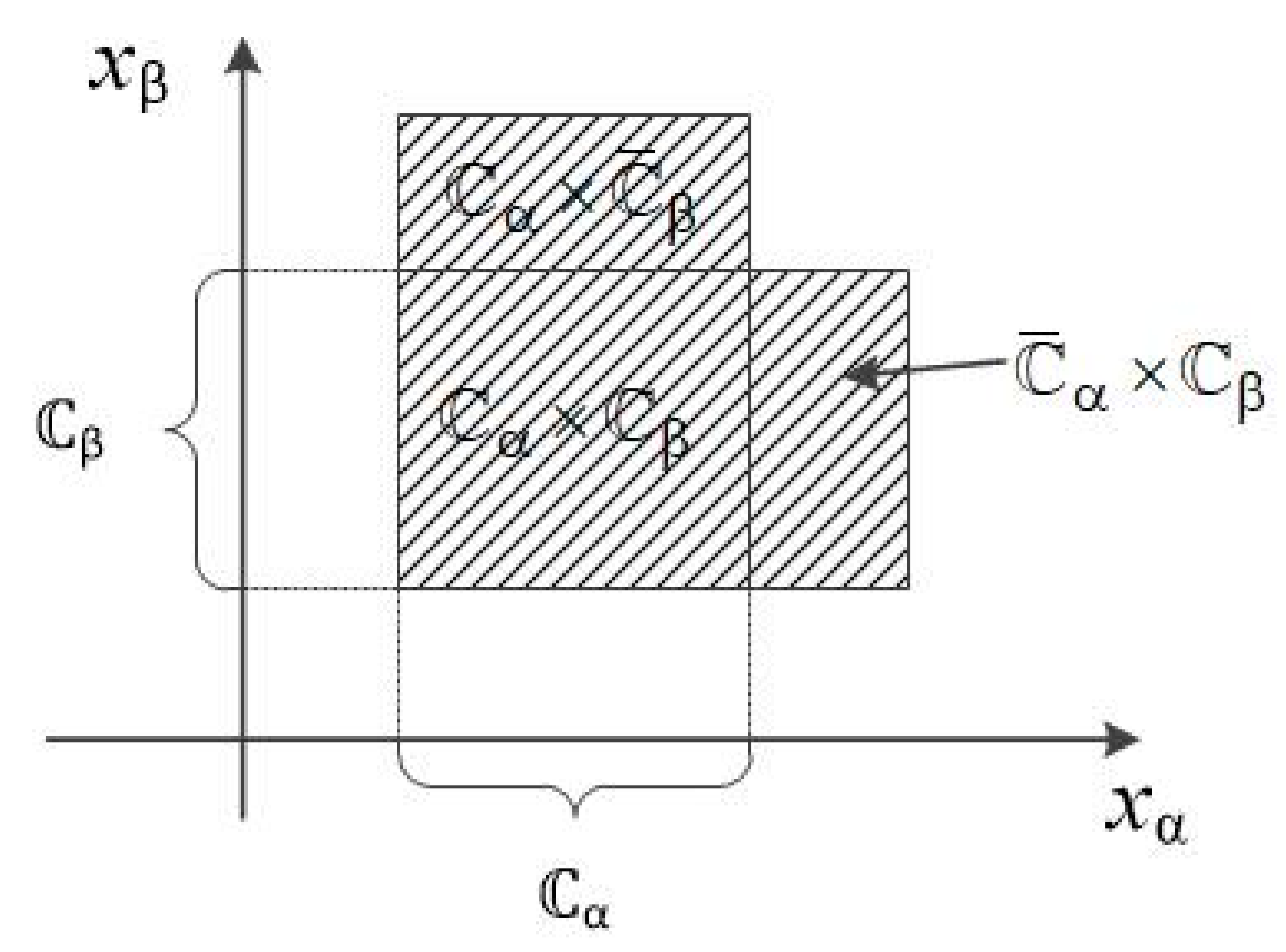

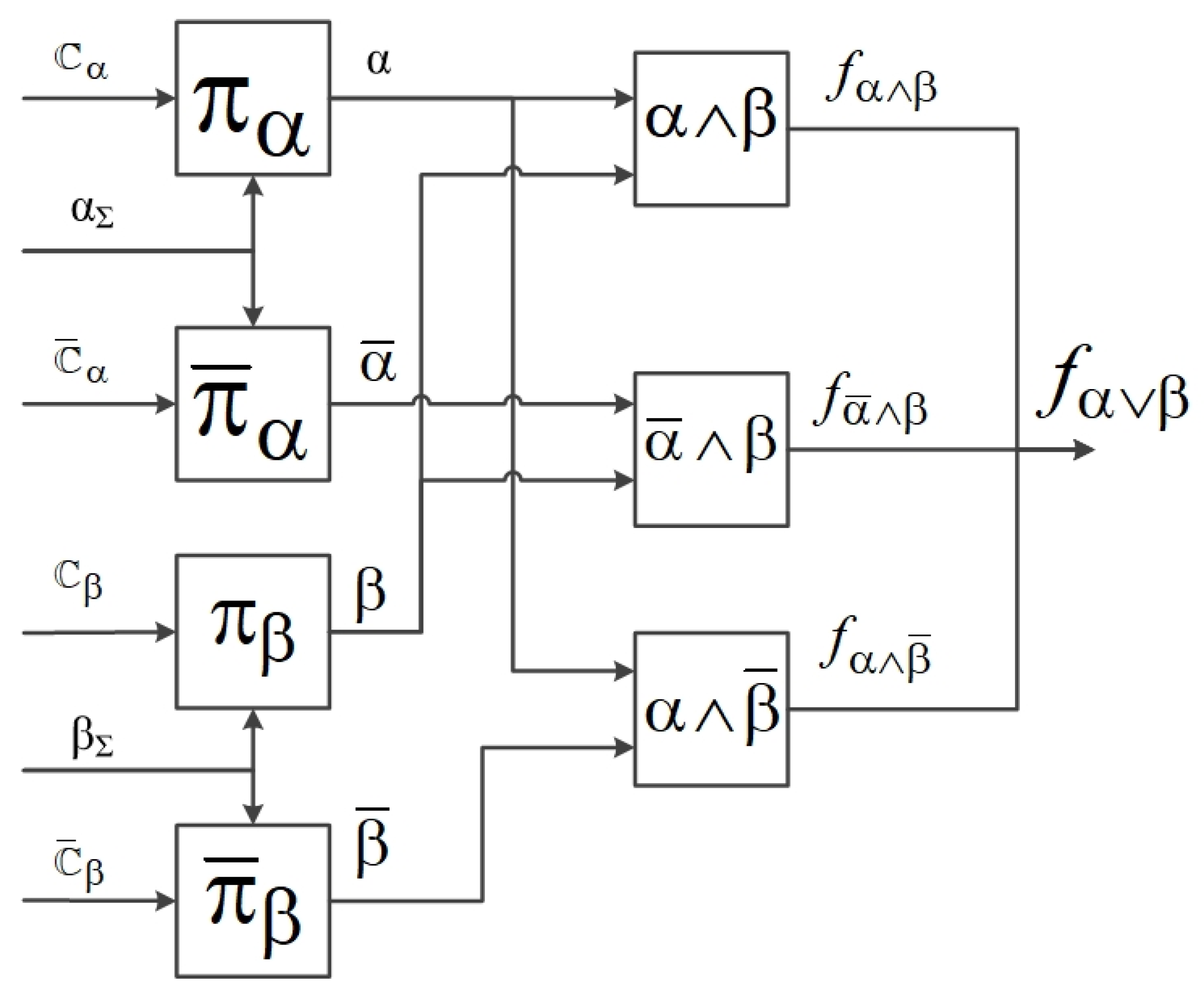

2.7. Operation of Conjunctive Unification of Energy Flows

2.8. Operation of Disjunctive Union of Energy Flows

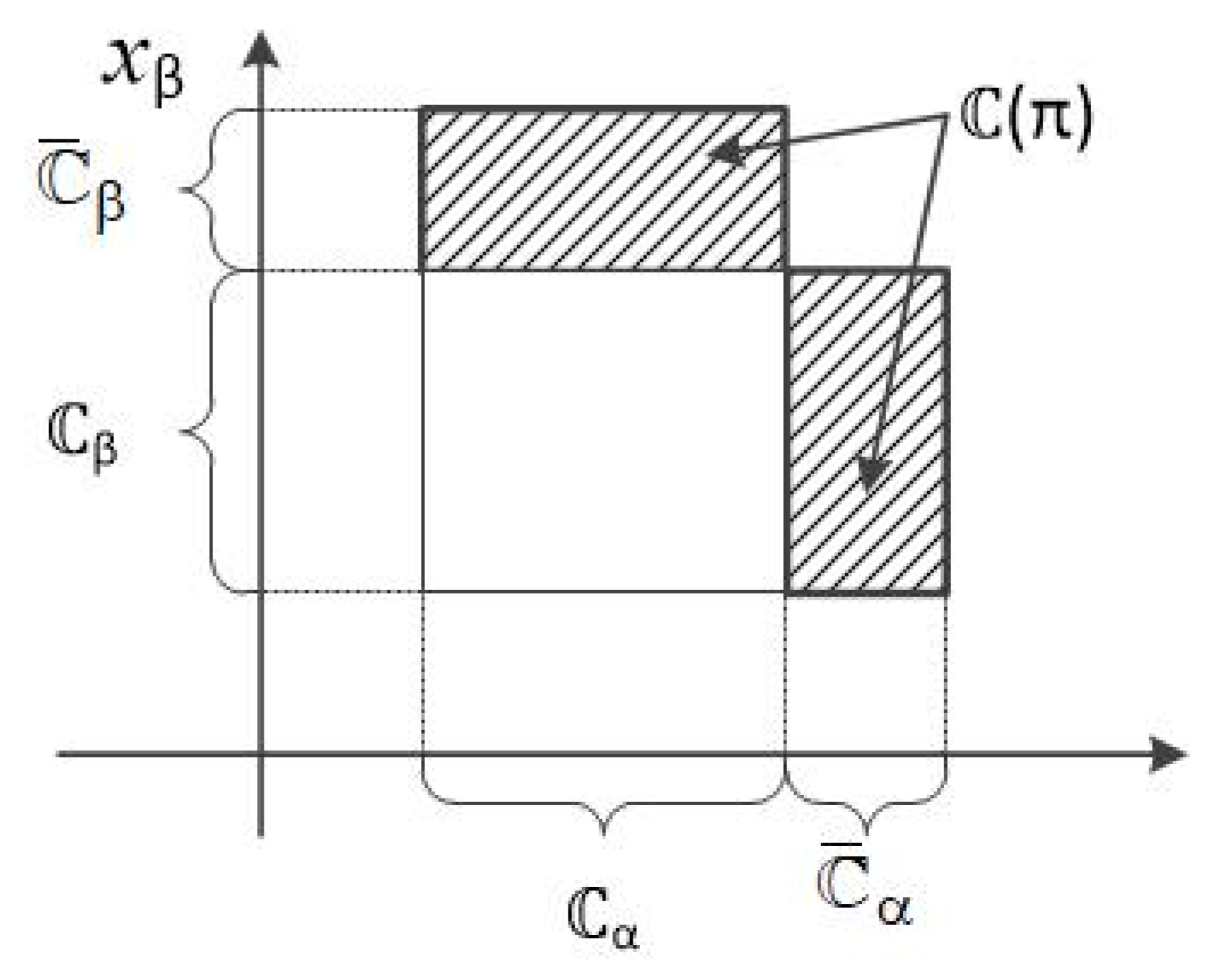

2.9. Operation of Conjunctive Negation of Energy Flows

2.10. Operation of Disjunctive Negation of Energy Flows

2.11. XOR Operation

3. Results

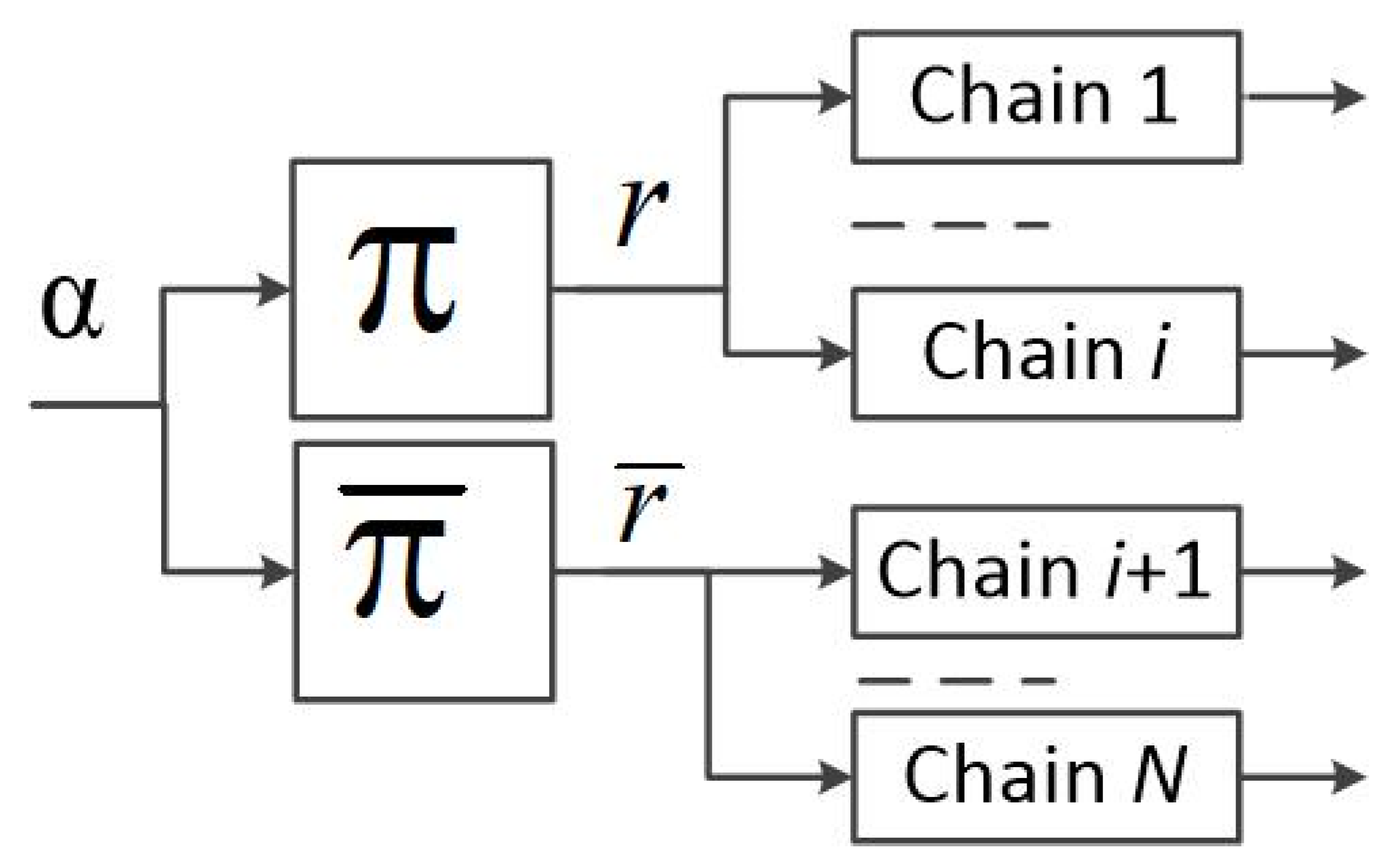

3.1. Circuitry of Analog Networks

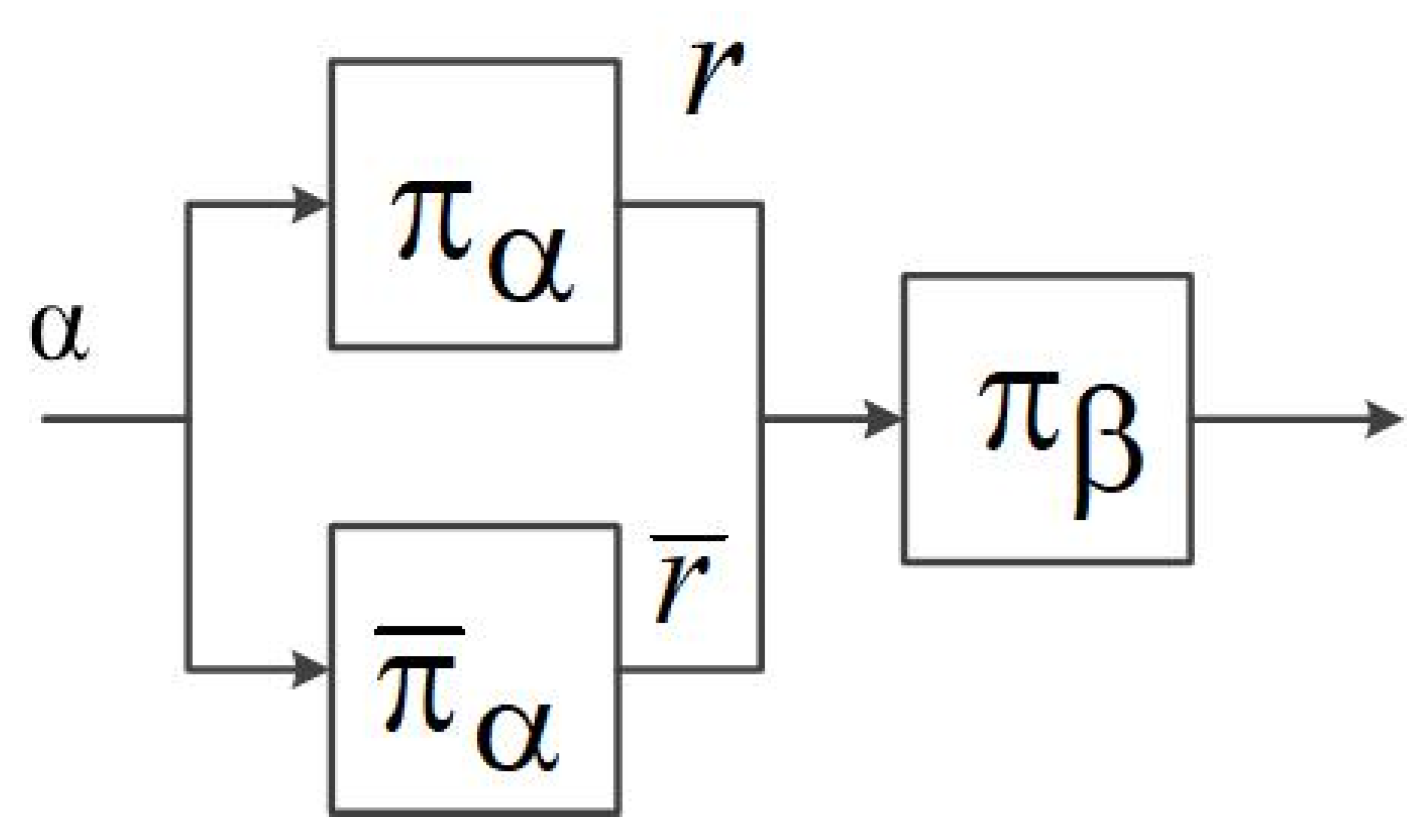

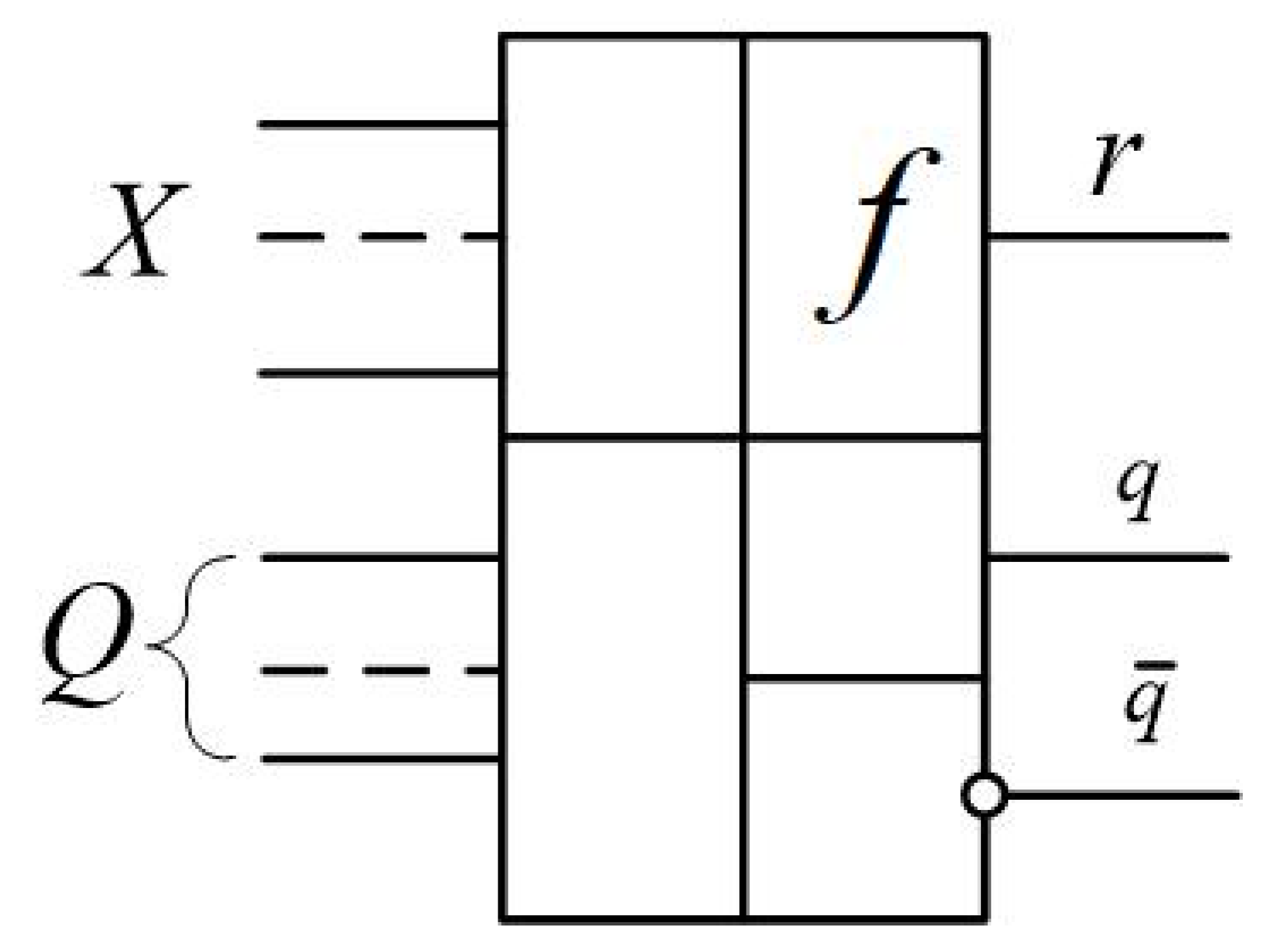

3.2. Continuum Processor

- when the signal x voltage enters the region , the outgoing signal x will appear at the output of the CP π, and there will be no analog signal at the input of the CP ;

- when the signal x voltage enters the region , the outgoing signal will appear at the output of the CP , and there will be no analog signal at the input of the CP π.

4. Discussion

- simultaneously process the states of the technical system and synthesize control signals;

- speed up the response of the control system to changes in the object’s parameters;

- reduce the design complexity, and improve the energy performance of the control system.

5. Conclusions

- (1)

- The possibilities of applying the theory of analog systems continuous logical analysis for obtaining deterministic solutions have been expanded. The developed models replace the fuzzy calculations used in continuum logic with logical operations of dividing decision-making areas into sub-areas, the boundaries of which are uniquely determined by the relationships between the instantaneous values of the parameters of the control object. The unambiguity of the decisions made increases the accuracy and reliability of the results of the situational analysis of the states of the vehicle in comparison with existing methods of continuous logic.

- (2)

- The presented generalized models of the logical analysis of the states of the TS allow systematizing the development of embedded analog devices for the distributed control of technical and technological objects that do not require: analog-to-digital conversions of sensor signals, programmable control devices and matching of embedded digital processors. The obtained hardware solutions are aimed at integrating computing processes into aggregates in order to create an ACPN, in which the synthesis of control signals of the TS takes place at low energy costs and the design complexity of the equipment.

- (3)

- The developed methods for the logical analysis of the states of the TS and the synthesis of control signals are implemented in analog devices based on continuum processors, which allow real-time (at a frequency of up to several tens of megahertz) of the operating modes of aggregates. Built-in CPs turn the TS into a distributed computing structure, in which analog computing is integrated with physical processes, leading to an increase in performance with a decrease in energy parameters due to the transition from sequential high-frequency digital calculations to continuous synthesis analog.

6. Patents

Funding

Data Availability Statement

Conflicts of Interest

References

- Tortora, G.J.; Derrickson, B.H. Principles of Anatomy and Physiology; John Wiley & Sons: Hoboken, NJ, USA, 2018; 1248p. [Google Scholar]

- Helbling, E.F.; Fuller, S.B.; Wood, R.J. Altitude Estimation and Control of an Insect-Scale Robot with an Onboard Proximity Sensor. Robot. Res. 2018, 1, 57–69. [Google Scholar]

- Tanenbaum, A.S.; van Steen, M. Distributed Systems: Principles and Paradigms; Pearson Prentice Hall: Hoboken, NJ, USA, 2007; 686p. [Google Scholar]

- Sangiovanni-Vincentelli, A.L. Quo Vadis, SLD? Reasoning about the Trends and Challenges of System Level Design. Proc. IEEE 2007, 95, 467–506. [Google Scholar] [CrossRef]

- Goebel, R.; Sanfelice, R.G.; Teel, A.R. Hybrid Dynamical Systems. Modeling, Stability, and Robustness; Princeton University Press: Princeton, NJ, USA; Oxford, UK, 2012; 212p. [Google Scholar]

- Lee, E.A. Cyber-Physical Systems—Are Computing Foundations Adequate? Position Paper for NSF Workshop on Cyber-Physical Systems: Research Motivation, Techniques and Roadmap; Department of EECS, UC Berkeley: Austin, TX, USA, 2006; 9p. [Google Scholar]

- Henzinger, T.A. The theory of hybrid automata. In Verification of Digital and Hybrid Systems; NATO ASI Series; Springer: Berlin/Heidelberg, Germany; Electronics Research Laboratory College of Engineering University of California: Berkeley, CA, USA, 1996; Volume 170, pp. 265–292. [Google Scholar] [CrossRef]

- Broy, M. Functional specification of time-sensitive communicating systems. ACM Trans. Softw. Eng. Methodol. 1993, 2, 325–367. [Google Scholar] [CrossRef]

- Caferra, R. Logic for Computer Science and Artificial Intelligence; John Wiley & Sons: Hoboken, NJ, USA, 2013; 523p. [Google Scholar]

- Ball, S.R. Analog Interfacing to Embedded Microprocessor Systems; Real World Design, Newnes; Elsevier: Amsterdam, The Netherlands, 2004; 322p. [Google Scholar]

- Omar, Y. Ismael Analysis, Design, and Implementation of an Omnidirectional Mobile Robot Platform. Am. Sci. Res. J. Eng. Technol. Sci. 2016, 22, 195–209. [Google Scholar]

- Ashok, B.; Denis, A.S.; Kumar, C. Ramesh A review on control system architecture of a SI engine management system. Annu. Rev. Control 2016, 41, 94–118. [Google Scholar] [CrossRef]

- Baek, S.S.; Bermudez, F.G.; Fearing, R. Flight control for target seeking by 13 gram ornithopter. In Proceedings of the 2011 IEEE/RSJ International Conference on Intelligent Robots and Systems, San Francisco, CA, USA, 25–30 September 2011. 16p. [Google Scholar]

- Vijay, K.; Nathan, M. Opportunities and challenges with autonomous micro aerial vehicles. Int. J. Robot. Res. 2012, 31, 1279–1291. [Google Scholar]

- Sapaty, S.P. Military Robotics: Latest Trends and Spatial Grasp Solutions. Int. J. Adv. Res. Artif. Intell. 2015, 4, 9–18. [Google Scholar]

- Duhamel, P.-E.J.; Perez-Arancibia, N.O.; Barrows, G.L.; Wood, R.J. Biologically inspired optical-flow sensing for altitude control of flapping-wing microrobots. IEEE/ASME Trans. Mechatron. 2013, 18, 556–568. [Google Scholar] [CrossRef]

- De Wagter, C.; Tijmons, S.; Remes, B.D.; de Croon, G. Autonomous flight of a 20-gram flapping wing mav with a 4-gram onboard stereo vision system. In Proceedings of the 2014 IEEE International Conference on Robotics and Automation (ICRA), Hong Kong, China, 31 May–7 June 2014; pp. 4982–4987. [Google Scholar]

- Helbling, E.F.; Fuller, S.B.; Wood, R.J. Pitch and yaw control of a robotic insect using an onboard magnetometer. In Proceedings of the 2014 IEEE International Conference on Robotics and Automation (ICRA), Hong Kong, China, 31 May–7 June 2014; IEEE: Piscataway, NJ, USA, 2014; pp. 5516–5522. [Google Scholar]

- Harel, D.; Pnueli, A. On the development of reactive systems. In Logic and Models of Concurrent Systems; NATO Advanced Study Institute on Logic and Models for Verification and Specification of Concurrent Systems; Springer: Berlin/Heidelberg, Germany, 1985; pp. 477–498. [Google Scholar]

- Escoffier, C.; Finnigan, K. Reactive Systems in Java: Resilient, Event-Driven Architecture with Quarkus; O’Reilly Media: Sebastopol, CA, USA, 2022; 250p. [Google Scholar]

- Lee, B. Specification and Design of Reactive Systems; Memorandum No. UCB/ERL MOO/29; University of California: Berkeley, CA, USA, 2000; 126p. [Google Scholar]

- DeBole, M.V.; Taba, B.; Amir, A.; Akopyan, F.; Andreopoulo, A.; Risk, W.P.; Kusnitz, J.; Otero, C.O.; Nayak, T.K.; Appuswamy, R.; et al. TrueNorth: Accelerating From Zero to 64 Million Neurons in 10 Years. Computer 2019, 52, 20–29. [Google Scholar] [CrossRef]

- Davies, M.; Srinivasa, N.; Lin, T.-H.; Chinya, G.; Cao, Y.; Choday, S.H.; Dimou, G.; Joshi, P.; Imam, N.; Jain, S.; et al. Loihi: A Neuromorphic Manycore Processor with On-Chip Learning. IEEE Micro 2018, 38, 82–99. [Google Scholar] [CrossRef]

- Billaudelle, S.; Cramer, B.; Petrovici, M.A.; Schreiber, K.; Kappel, D.; Schemmel, J.; Meier, K. Structural plasticity on an accelerated analog neuromorphic hardware system. Neural Netw. 2021, 133, 11–20. [Google Scholar] [CrossRef] [PubMed]

- Vigoda, B. Analog Logic: Continuous-Time Analog Circuits for Statistical Signal Processing. Ph.D. Thesis, Massachusetts Institute of Technology, Cambridge, CA, USA, 2003; 209p. Available online: https://cba.mit.edu/docs/theses/03.07.vigoda.pdf (accessed on 23 June 2023).

- Chen, K.; Leu, J.; Gershenfeld, N. Analog Logic Automata. In Proceedings of the 2008 IEEE Biomedical Circuits and Systems Conference, Baltimore, MD, USA, 20–22 November 2008; pp. 189–192. [Google Scholar]

- Gershenfeld, N. Programming Bits and Atoms. In Proceedings of the 2013 IEEE 34th Real-Time Systems Symposium, Vancouver, BC, Canada, 3–6 December 2013; p. xiv. [Google Scholar]

- Gandharv, K. World’s First AI Analog Chip; Endless Origins: Delhi, India, 2021; Available online: https://analyticsindiamag.com/worlds-first-ai-analog-chip/ (accessed on 23 June 2023).

- Timothy, M. Continuous logic and embeddings of Lebesgue spaces. Arch. Math. Log. 2021, 60, 13. Available online: https://www.researchgate.net/publication/341687035_Continuous_logic_and_embeddings_of_Lebesgue_spaces#fullTextFileContent/ (accessed on 23 June 2023).

- Hanson, J. Continuous Logic for Discontinuous Logicians. 28 May 2023, p. 25. Available online: https://james-hanson.github.io/publications/ConLogDisLog.pdf (accessed on 23 June 2023).

- Li, X. The Classical Logic and the Continuous Logic. In Proceedings of the Future Technologies Conference (FTC), Vancouver, BC, Canada, 20–21 October 2022; Volume 1. Available online: https://www.researchgate.net/publication/364508302_The_Classical_Logic_and_the_Continuous_Logic (accessed on 23 June 2023).

- Li, X. The Continuous Logic; Department of Mathematics and Computer Science Alabama State University: Montgomery, AL, USA, 2015; p. 8. [Google Scholar] [CrossRef]

- Dembitsky, N.L.; Polyakov, S.V.; Timoshenko, A.V. Recognition of Analog Signals of a Given Shape Using Continuous Processors. In Proceedings of the 2020 Systems of Signals Generating and Processing in the Field of on Board Communications, Moscow, Russia, 19–20 March 2020; IEEE: Piscataway, NJ, USA; pp. 1–5. [Google Scholar]

- Dembitsky, N.L. Analog Self-Learning Automata of Radio Engineering Devices Based on Cyber-Physical Networks. In Proceedings of the 2022 Systems of Signals Generating and Processing in the Field of on Board Communications, Moscow, Russia, 15–17 March 2022; pp. 1–5. [Google Scholar]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Dembitsky, N. Continuum Logic of Control Signals in Analog Cyber–Physical Nets. Inventions 2023, 8, 101. https://doi.org/10.3390/inventions8040101

Dembitsky N. Continuum Logic of Control Signals in Analog Cyber–Physical Nets. Inventions. 2023; 8(4):101. https://doi.org/10.3390/inventions8040101

Chicago/Turabian StyleDembitsky, Nikolay. 2023. "Continuum Logic of Control Signals in Analog Cyber–Physical Nets" Inventions 8, no. 4: 101. https://doi.org/10.3390/inventions8040101