Analysis of pn Junction Deep Trench Isolation with SU-8/SiO2-Liner Passivation in a Linear Butt-Coupled 3D CMOS Si Photodetector Array †

Abstract

:1. Introduction

2. Materials and Methods

3. Results and Discussion

4. Conclusions

Acknowledgments

Conflicts of Interest

References

- Park, B.J.; Jung, J.; Moon, C.R.; Hwang, S.H.; Lee, Y.W.; Kim, D.W.; Paik, K.H.; Yoo, J.R.; Lee, D.H.; Kim, K. Deep Trench Isolation for Crosstalk Suppression in Active Pixel Sensors with 1.7 µm Pixel Pitch. Jpn. J. Appl. Phys. 2007, 46, 2454. [Google Scholar] [CrossRef]

- Ahmed, N.; Roy, F.; Lu, G.N.; Mamdy, B.; Carrere, J.P.; Tournier, A.; Virollet, N.; Perrot, C.; Rivoire, M.; Seignard, A.; et al. (Eds.) MOS Capacitor Deep Trench Isolation for CMOS image sensors. In Proceedings of the 2014 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2014. [Google Scholar]

- Kitamura, Y.; Aikawa, H.; Kakehi, K.; Yousyou, T.; Eda, K.; Minami, T.; Uya, S.; Takegawa, Y.; Yamashita, H.; Kohyama, Y.; et al. (Eds.) Suppression of crosstalk by using backside deep trench isolation for 1.12 μm backside illuminated CMOS image sensor. In Proceedings of the 2012 International Electron Devices Meeting, San Francisco, CA, USA, 10–13 December 2012. [Google Scholar]

- Sabri Alirezaei, I.; Vierhaus, J.; Burte, E.P. A 3D-CMOS compatible silicon photo-sensor with a large vertical photosensitive area. Opt. Quantum Electron. 2017, 49, 123. [Google Scholar] [CrossRef]

- SabriAlirezaei, I.; Vierhaus, J.; Burte, E.P. (Eds.) A Butt-Coupled 3D-Bulk Si CMOS Photodetector Array Integrated with a Monolithic U-Groove Array on a Single Chip; Optical Society of America: Washington, DC, USA, 2017. [Google Scholar]

- Lotfi, D.; Hatem, E. Phosphorus diffusion gettering process of multicrystalline silicon using a sacrificial porous silicon layer. Nanoscale Res. Lett. 2012, 7, 424. [Google Scholar] [CrossRef] [PubMed]

| Regions | n++ | n+ |

|---|---|---|

| Surface doping concentration | ~1 × 1021 cm−3 | ~5 × 1020 cm−3 |

| Junction depth | ~600 nm | ~300 nm |

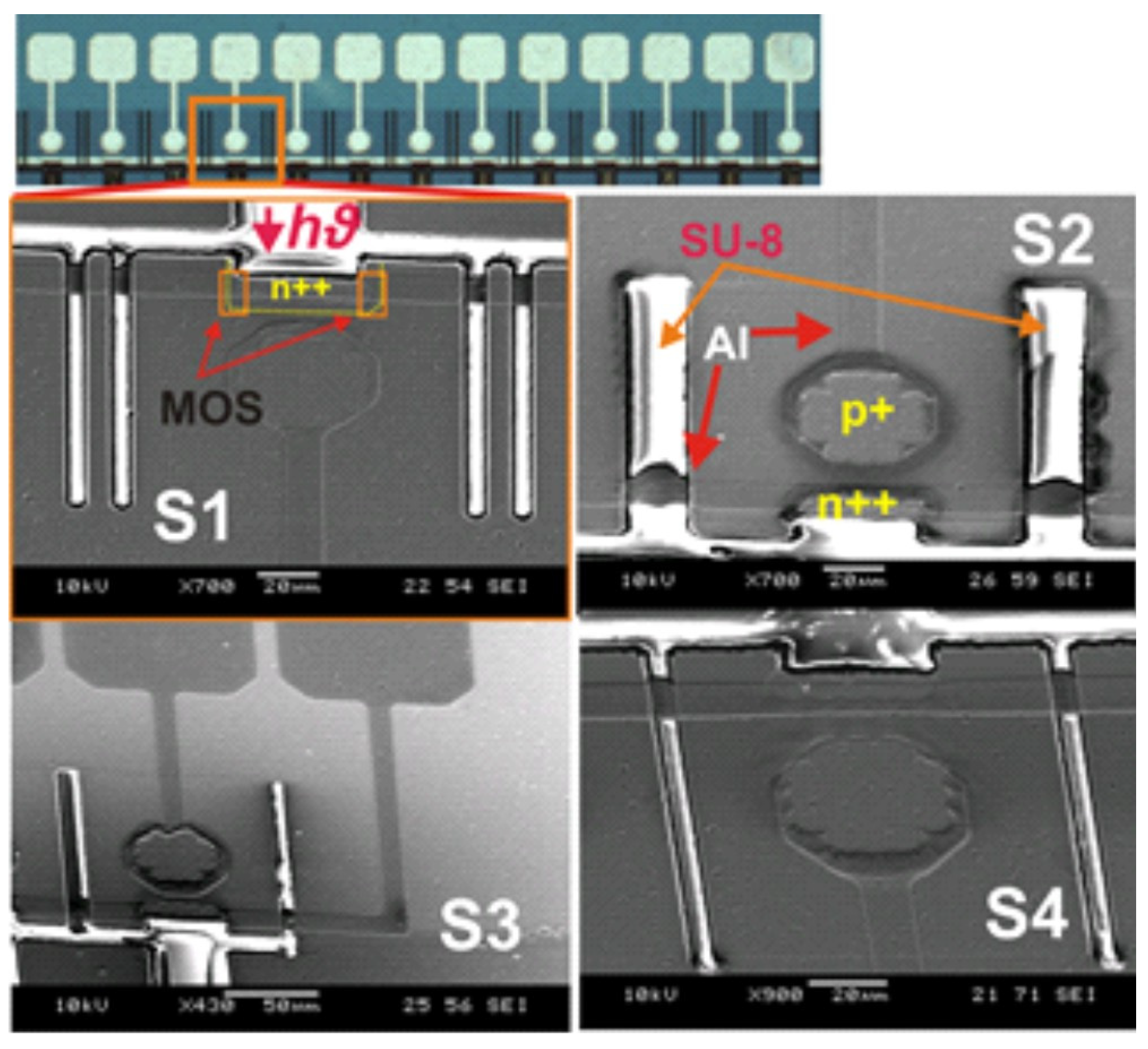

| Samples | Trench Isolation | Trench Width | Dark Current at 2 V |

|---|---|---|---|

| S1 | Double-trench isolation | ~7.5 µm | 1.14 nA |

| S2 | Single-trench isolation | ~24 µm | 520 µA |

| S3 | Single-trench isolation | ~13 µm | 27.6 nA |

| S4 | Single-trench isolation | ~8 µm | 12.5 nA |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Alirezaei, I.S.; Vierhaus, J.; Burte, E.P. Analysis of pn Junction Deep Trench Isolation with SU-8/SiO2-Liner Passivation in a Linear Butt-Coupled 3D CMOS Si Photodetector Array. Proceedings 2017, 1, 557. https://doi.org/10.3390/proceedings1040557

Alirezaei IS, Vierhaus J, Burte EP. Analysis of pn Junction Deep Trench Isolation with SU-8/SiO2-Liner Passivation in a Linear Butt-Coupled 3D CMOS Si Photodetector Array. Proceedings. 2017; 1(4):557. https://doi.org/10.3390/proceedings1040557

Chicago/Turabian StyleAlirezaei, Iman Sabri, Joerg Vierhaus, and Edmund P. Burte. 2017. "Analysis of pn Junction Deep Trench Isolation with SU-8/SiO2-Liner Passivation in a Linear Butt-Coupled 3D CMOS Si Photodetector Array" Proceedings 1, no. 4: 557. https://doi.org/10.3390/proceedings1040557

APA StyleAlirezaei, I. S., Vierhaus, J., & Burte, E. P. (2017). Analysis of pn Junction Deep Trench Isolation with SU-8/SiO2-Liner Passivation in a Linear Butt-Coupled 3D CMOS Si Photodetector Array. Proceedings, 1(4), 557. https://doi.org/10.3390/proceedings1040557