Thermal Noise Limited, Scalable Multi-Piezoresistor Readout Architecture †

Abstract

:1. Introduction

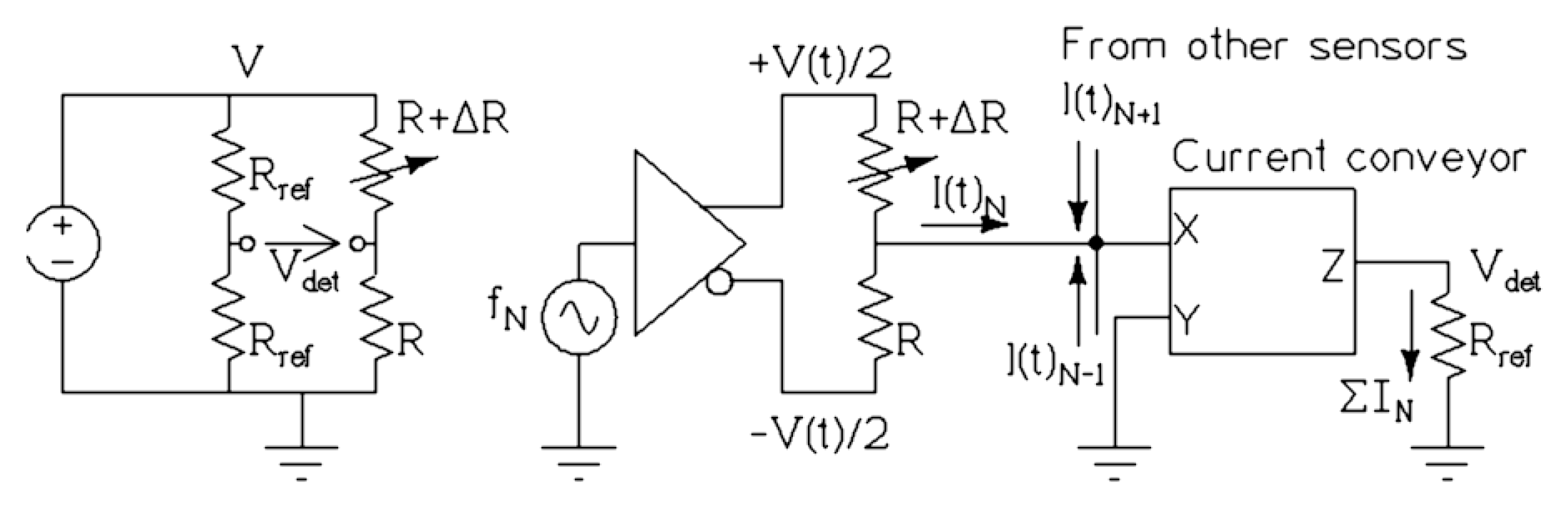

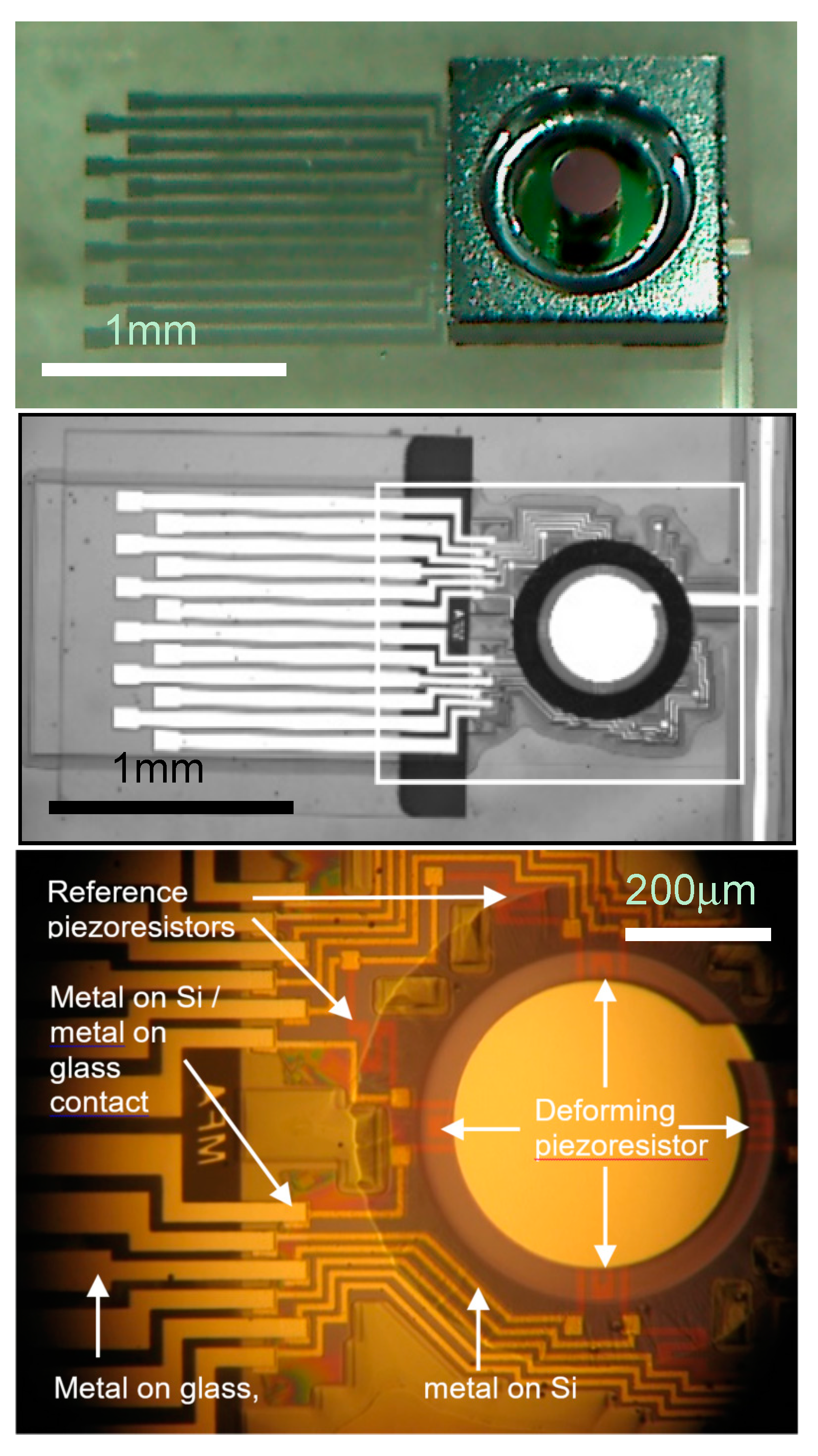

2. Materials and Methods

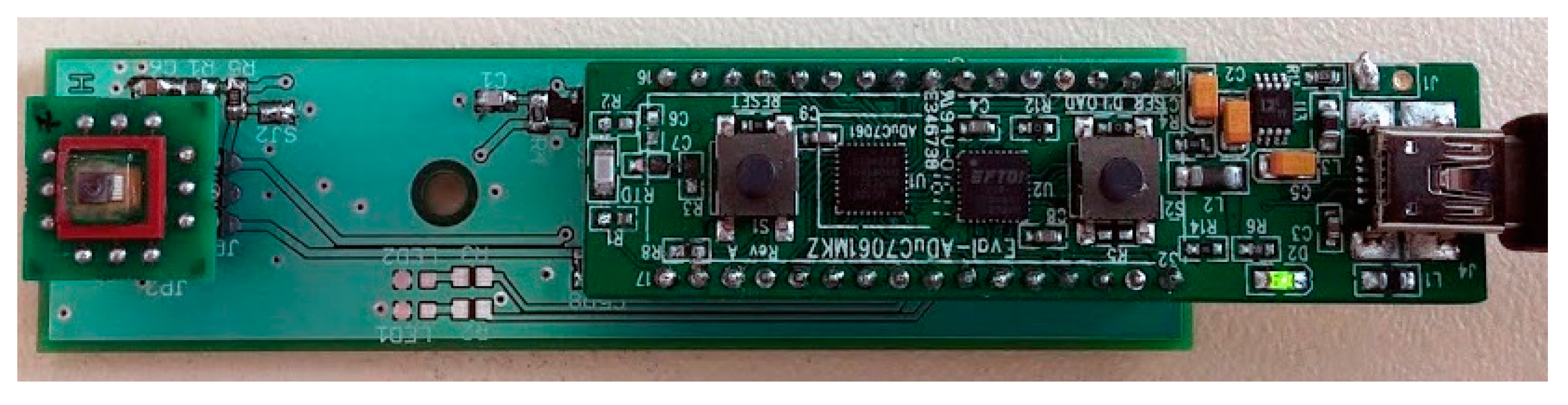

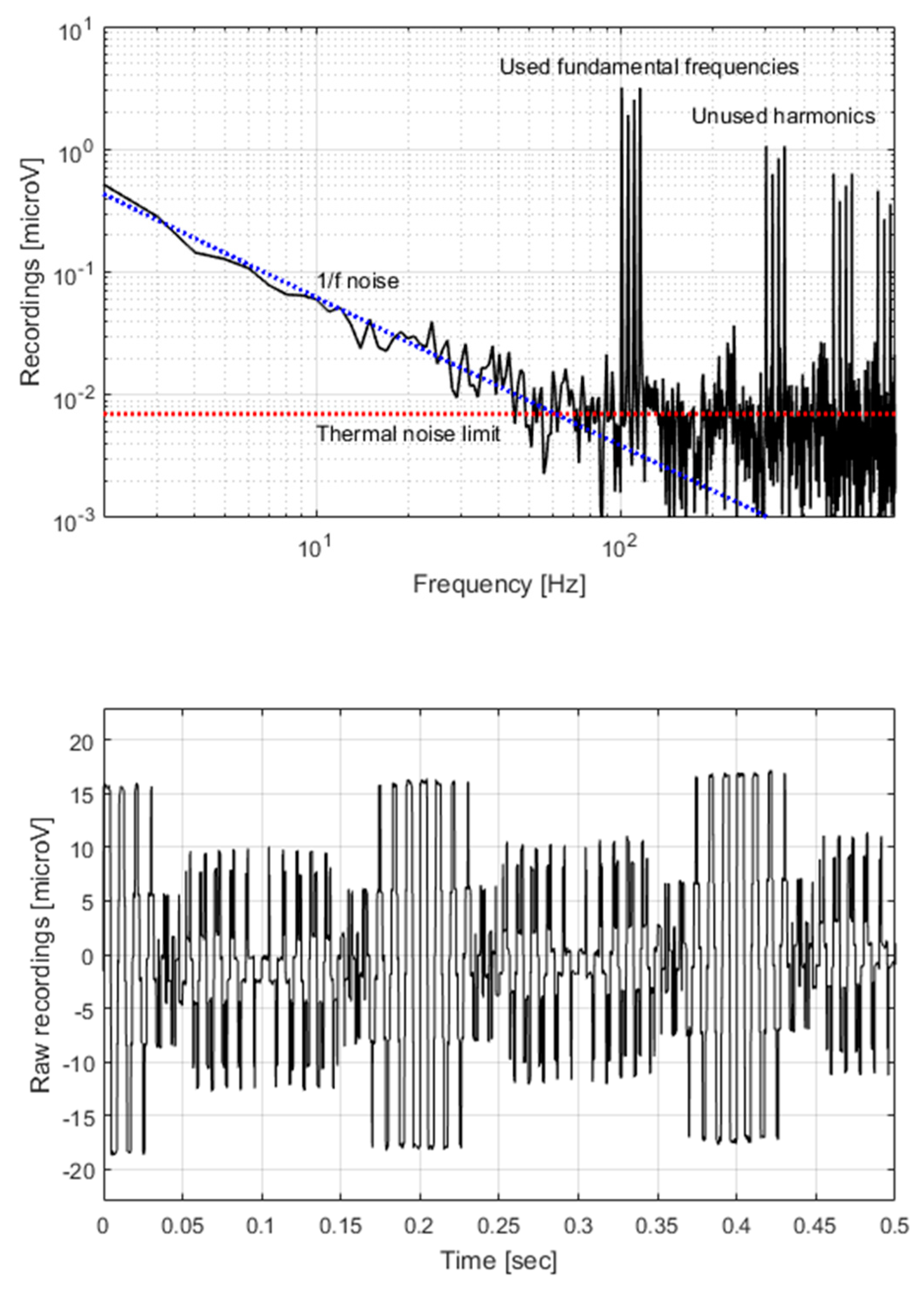

3. Results and Conclusions

Acknowledgments

Conflicts of Interest

References

- Xiaomei, Y.; Thaysen, J.; Hansen, O.; Boisen, A. Optimization of sensitivity and noise in piezoresistive cantilevers. J. Appl. Phys. 2002, 92, 6296–6301. [Google Scholar] [CrossRef]

- Radó, J.; Dücső, C.; Battistig, G.; Szebényi, G.; Fürjes, P.; Nawrat, Z.; Rohr, K. 3D force sensors for laparoscopic surgery tool. In Proceedings of the Design, Test, Integration and Packaging of MEMS/MOEMS—DTIP 2016 Conference, Budapest, Hungary, 30 May–2 June 2016; IEEE XPlore 7514829. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Radó, J.; Battistig, G.; Pap, A.E.; Fürjes, P.; Földesy, P. Thermal Noise Limited, Scalable Multi-Piezoresistor Readout Architecture. Proceedings 2017, 1, 598. https://doi.org/10.3390/proceedings1040598

Radó J, Battistig G, Pap AE, Fürjes P, Földesy P. Thermal Noise Limited, Scalable Multi-Piezoresistor Readout Architecture. Proceedings. 2017; 1(4):598. https://doi.org/10.3390/proceedings1040598

Chicago/Turabian StyleRadó, János, Gábor Battistig, Andrea Edit Pap, Péter Fürjes, and Péter Földesy. 2017. "Thermal Noise Limited, Scalable Multi-Piezoresistor Readout Architecture" Proceedings 1, no. 4: 598. https://doi.org/10.3390/proceedings1040598

APA StyleRadó, J., Battistig, G., Pap, A. E., Fürjes, P., & Földesy, P. (2017). Thermal Noise Limited, Scalable Multi-Piezoresistor Readout Architecture. Proceedings, 1(4), 598. https://doi.org/10.3390/proceedings1040598