Differential Hall Effect Metrology for Electrical Characterization of Advanced Semiconductor Layers

Abstract

1. Introduction

2. Hall Effect

3. Differential Hall Effect (DHE)

3.1. Early Work on Differential Conductivity Measurements

3.2. Early Work on DHE

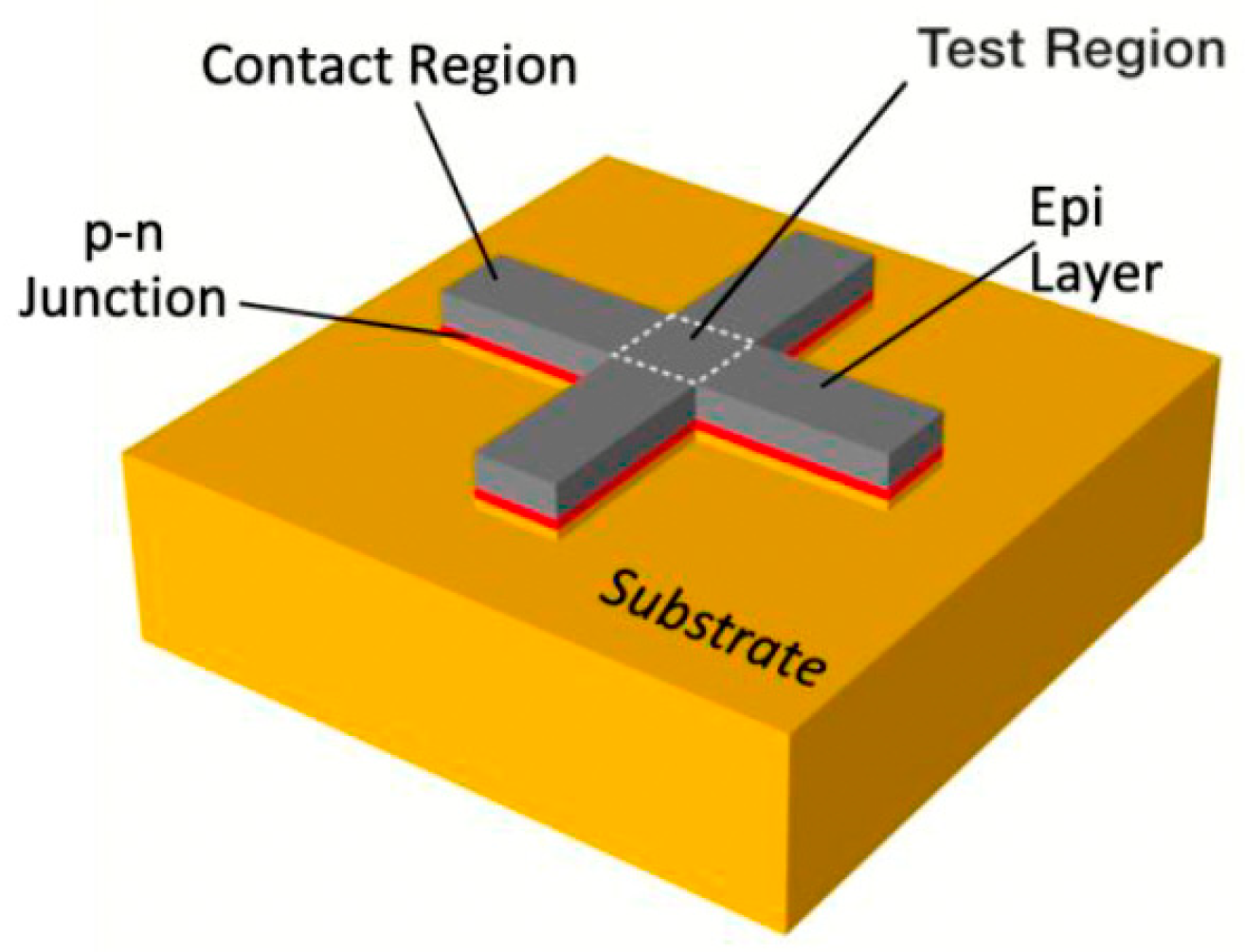

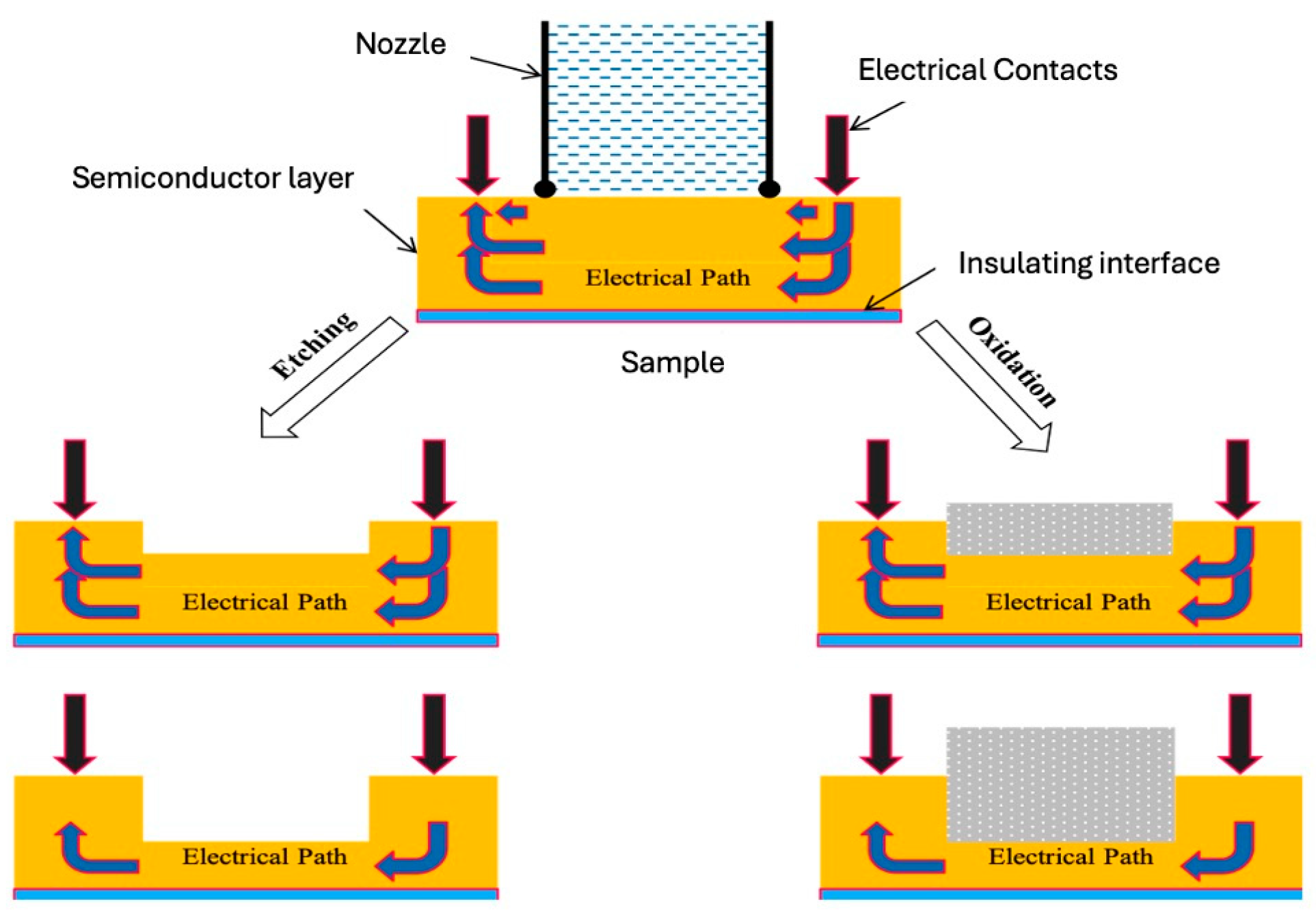

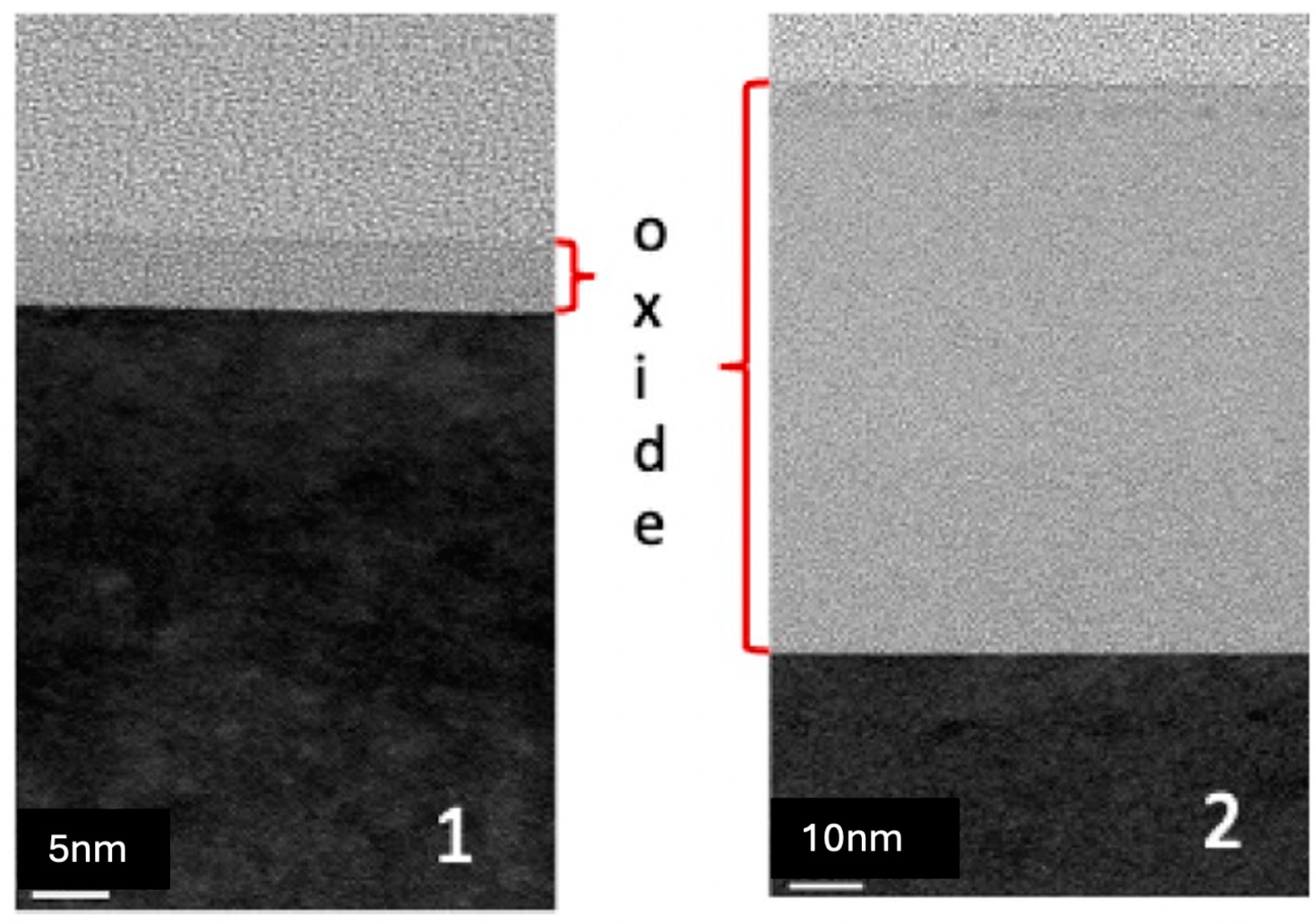

4. Differential Hall Effect Metrology (DHEM)

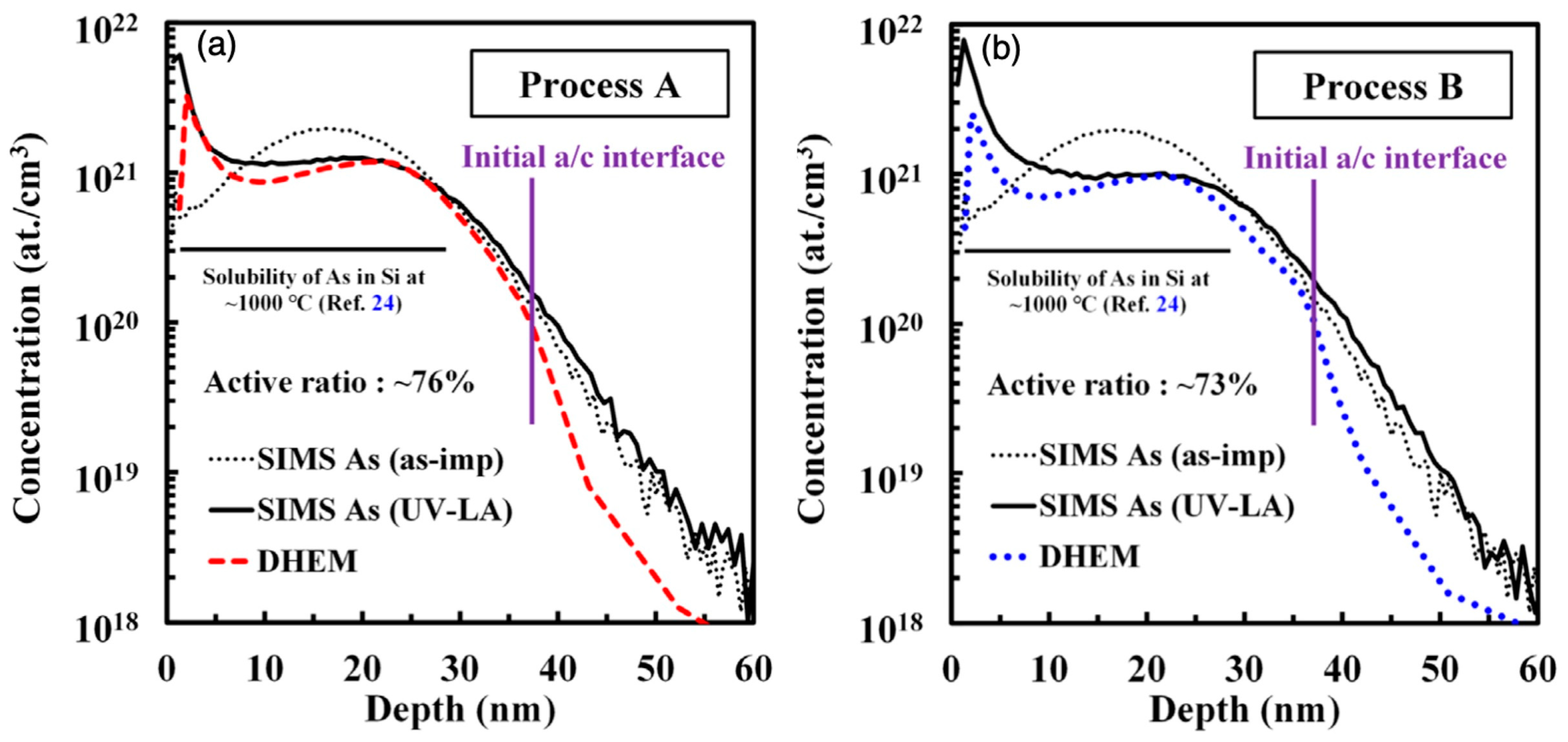

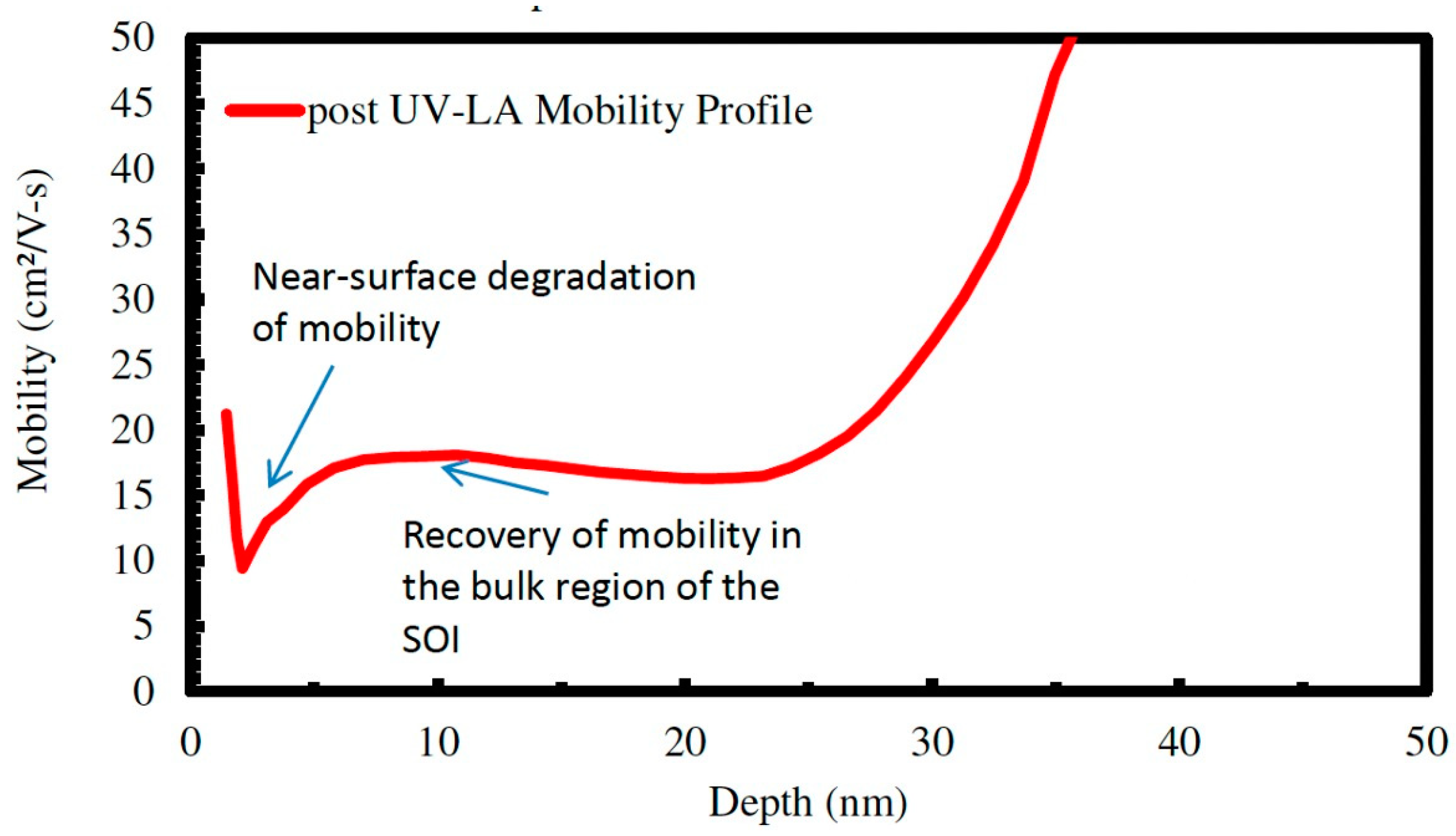

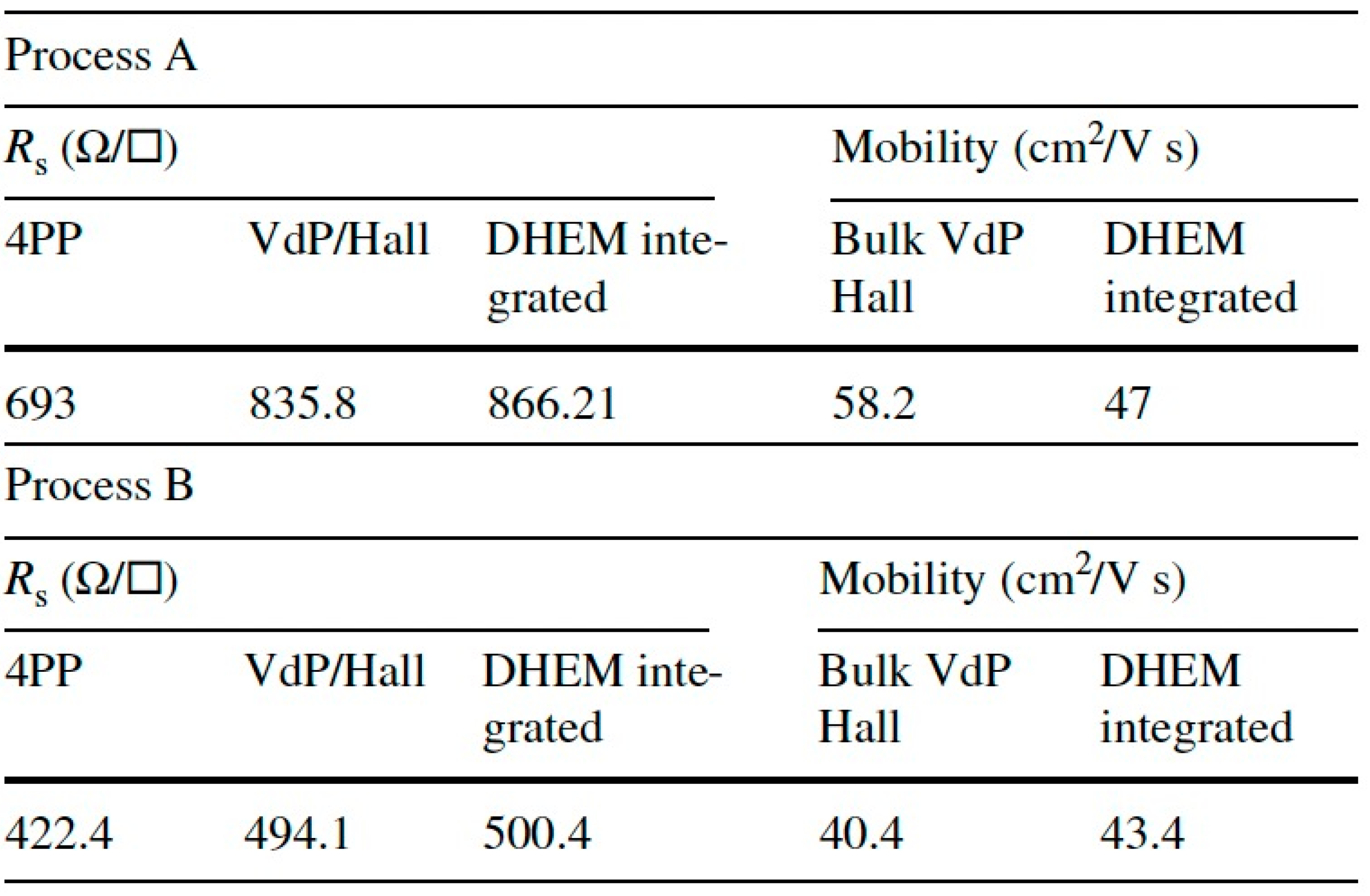

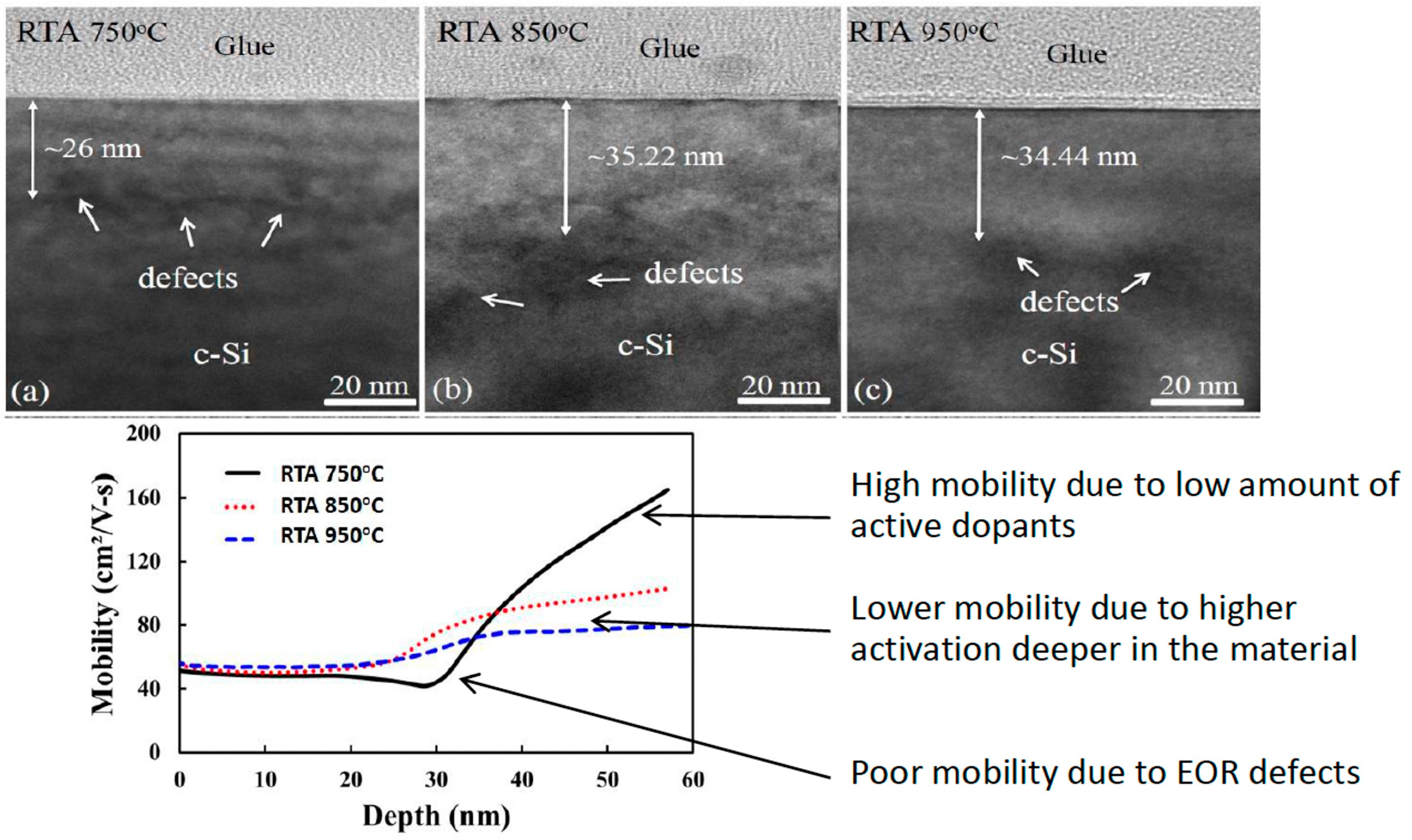

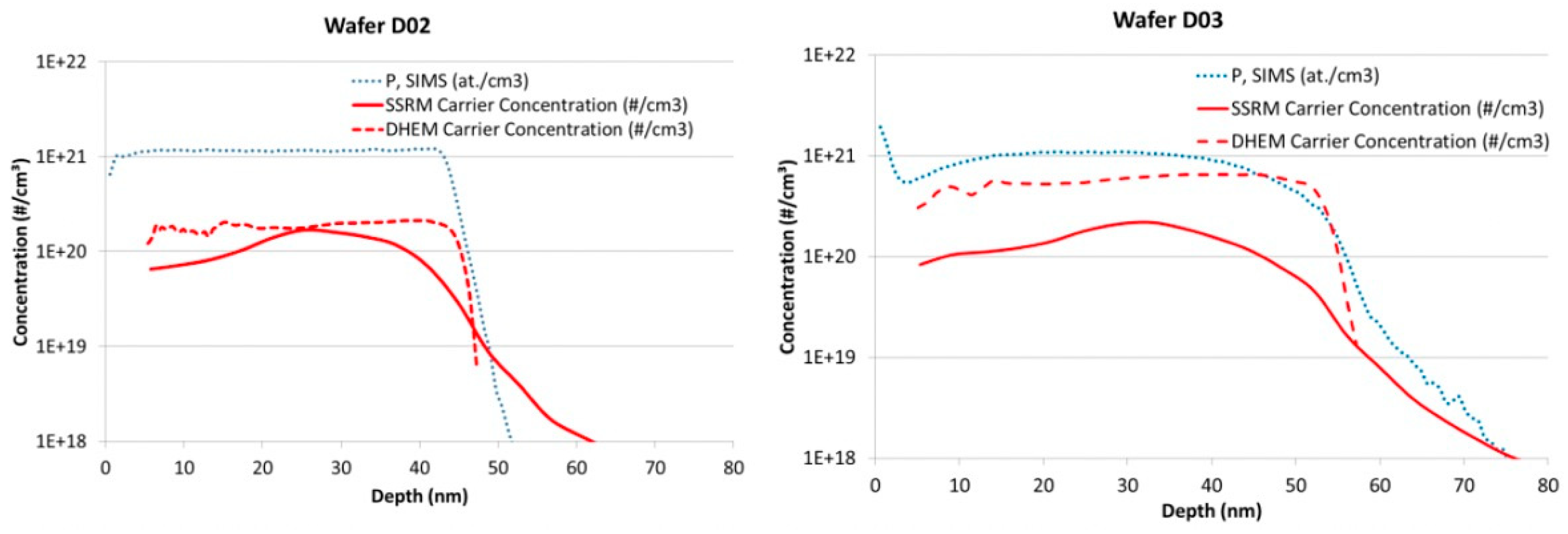

5. Recent DHEM Application Examples

6. Discussion of Assumptions and Uncertainties

7. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Mazur, R.G.; Dickey, D.H. A spreading resistance technique for resistivity measurements on silicon. J. Electrohem. Soc. 1966, 113, 255–259. [Google Scholar] [CrossRef]

- Vandervorst, W.; Clarysse, T.; Smith, H.E. Influence of the substrate doping level on spreading resistance profiling. J. Vac. Sci. Technol. B 1996, 14, 404–407. [Google Scholar] [CrossRef]

- Lin-Kwang, J.; Ramey, S.; Reynes, J.M.; Hillaed, R.J.; Thieme, T. The role of spreading resistance profiling in manufacturing control and technology development. Microelectron. Reliab. 2000, 40, 1497–1502. [Google Scholar] [CrossRef]

- Eyben, P.; Xu, M.; Duhayon, N.; Clarysse, T.; Callewaert, S.; Vandervorst, W. Scanning spreading resistance microscopy and spectroscopy for routine and quantitative two-dimensional carrier profiling. J. Vac. Sci. Technol. B 2002, 20, 471–478. [Google Scholar] [CrossRef]

- Clarysse, T.; Eyben, P.; Duhayon, N.; Xu, M.W.; Vandervorst, W. Carrier spilling revisited: On-bevel junction behavior of different electrical depth profiling techniques. J. Vac. Sci. Technol. B 2003, 21, 729–736. [Google Scholar] [CrossRef]

- Eyben, P.; Janssens, T.; Vandervorst, W. Scanning spreading resistance microscopy (SSRM) 2d carrier profiling for ultra-shallow junction characterization in deep-submicron technologies. Mater. Sci. Eng. B 2005, 124–125, 45–53. [Google Scholar] [CrossRef]

- Suchodolskis, A.; Hallen, A.; Gran, J.; Hansen, T.-E.; Karlsson, U.O. Scanning spreading resistance microscopy of shallow doping profiles in silicon. Nucl. Instrum. Methods Phys. Res. B 2006, 253, 141–144. [Google Scholar] [CrossRef]

- Dixon-Luinenburg, O.; Celano, U.; Vandervorst, W.; Paredis, K. Carrier profiling with fast Fourier transform scanning spreading resistance microscopy. A case study for Ge, GaAs, InGaAs, and InP. Ultramicroscopy 2019, 206, 112809. [Google Scholar] [CrossRef]

- Peiner, E.; Schlachetzki, A.; Kruger, D. Doping profile analysis in Si by electrochemical capacitance-voltage measurements. J. Electrochem. Soc. 1995, 142, 576–580. [Google Scholar] [CrossRef]

- Basaran, E.; Parry, C.P.; Kubiak, R.A.; Whall, T.E.; Parker, E.H.C. Electrochemical capacitance-voltage depth profiling of heavily boron-doped silicon. J. Cryst. Growth 1995, 157, 109–112. [Google Scholar] [CrossRef]

- Sermage, B.; Essa, Z.; Taleb, N.; Quillec, M.; Aubin, J.; Hartmann, J.M.; Veillerot, M. Electrochemical capacitance voltage measurements in highly doped silicon-germanium alloys. J. Appl. Phys. 2016, 119, 155703. [Google Scholar] [CrossRef]

- Essa, Z.; Taleb, N.; Sermage, B.; Broussillou, C.; Bazer-Bachi, B.; Quillec, M. Doping profile measurement on textured silicon surface. EPJ Photovolt. 2018, 9, 5. [Google Scholar] [CrossRef]

- Duhayon, N.; Clarysse, T.; Eyben, P.; Vandervorst, W.; Hellemans, L. Detailed study of scanning capacitance on cross-sectional and beveled junctions. J. Vac. Sci. Technol. B 2002, 20, 741–746. [Google Scholar] [CrossRef]

- Eyben, P.; Duhayon, N.; Alvarez, D.; Vandervorst, W. Assessing the resolution limits of scanning spreading resistance microscopy and scanning capacitance microscopy. AIP Conf. Proc. 2003, 683, 678–684. [Google Scholar] [CrossRef]

- Matey, J.R.; Blanc, J. Scanning capacitance microscopy. J. Appl. Phys. 1985, 57, 1437–1444. [Google Scholar] [CrossRef]

- Benstetter, G.; Biberger, R.; Liu, D. A review of advanced scanning probe microscope analysis of functional films and semiconductor devices. Thin Solid Films 2009, 517, 5100–5105. [Google Scholar] [CrossRef]

- Clarysse, T.; Vandervorst, W.; Lin, R.; Petersen, D.H.; Nielsen, P.F. Beyond SRP: Quantitative carrier profiling with M4PP. Nucl. Instrum. Methods Phys. Res. Beam Interact. Met. At. 2006, 253, 136–140. [Google Scholar] [CrossRef]

- Clarysse, T.; Eyben, P.; Parmentier, B.; Van Daele, B.; Satta, A.; Vandervorst, W.; Lin, R.; Petersen, D.H.; Nielsen, P.F. Advanced carrier depth profiling on Si and Ge with micro four-point probe. J. Vac. Sci. Technol. B 2008, 26, 317–321. [Google Scholar] [CrossRef]

- Clarysse, T.; Vanhaeren, D.; Vandervorst, W. Impact of probe penetration on the electrical characterization of sub-nm profiles. J. Vac. Sci. Technol. B 2002, 20, 459–466. [Google Scholar] [CrossRef]

- Eyben, P.; Duhayon, N.; Clarysse, T.; Vandervorst, W. Bias-induced junction displacements in scanning spreading resistance microscopy and scanning capacitance microscopy. J. Vac. Sci. Technol. B 2003, 21, 737–743. [Google Scholar] [CrossRef]

- Eyben, P.; Mody, J.; Vemula, S.; Vandervorst, W. Impact of environmental conditions on the electrical characteristics of scanning spreading resistance microscopy. J. Vac. Sci. Technol. B 2008, 26, 338–341. [Google Scholar] [CrossRef]

- Thurber, W.R.; Mattis, R.L.; Liu, Y.M.; Filliben, J.J. The Relationship between Resistivity and Dopant Density for Phosphorous and Boron Doped Silicon; National Bureau of Standards Special Publication 400-64; National Bureau of Standards: Washington, DC, USA, 1981. Available online: https://nvlpubs.nist.gov/nistpubs/Legacy/SP/nbsspecialpublication400-64.pdf (accessed on 14 August 2024).

- Cuttriss, D.B. Relation between surface concentration and average conductivity in diffused layers in germanium. Bell Syst. Tech. J. 1961, 40, 509–521. [Google Scholar] [CrossRef]

- Hall, E.H. On a new action of the magnet on electric currents. Am. J. Math. 1879, 2, 287–292. [Google Scholar] [CrossRef]

- Putley, E.H. The Hall Effect and Related Phenomena; Butterworths: London, UK, 1960. [Google Scholar]

- Van der Pauw, L.J. A method of measuring specific resistivity and Hall effect discs of arbitrary shape. Phil. Res. Rep. 1958, 13, 1–9. Available online: https://aki.issp.u-tokyo.ac.jp/okano/WalWiki/etc/VDP_PRR_13_1.pdf (accessed on 14 August 2024).

- Van der Pauw, L.J. A method of measuring the resistivity and Hall coefficient on lamellae of arbitrary shape. Phil. Tech. Rev. 1958, 20, 220–224. [Google Scholar]

- ASTM F76-08; Standard Test Methods for Measuring Resistivity and Hall Coefficient and Determining Hall Mobility in Single-Crystal Semiconductors. ASTM: West Conshohocken, PA, USA, 2016.

- Schroder, D.K. Mobility. In Semiconductor Material and Device Characterization, 3rd ed.; John Wiley & Sons: Hoboken, NJ, USA, 2006; pp. 465–475. [Google Scholar]

- Petritz, R.L. Theory of an experiment for measuring the mobility and density of carriers in the space-charge region of a semiconductor surface. Phys. Rev. 1958, 110, 1254–1262. [Google Scholar] [CrossRef]

- Tannenbaum, E. Detailed analysis of thin phosphorus-diffused layers in p-type silicon. Solid State Electron. 1961, 2, 123–132. [Google Scholar] [CrossRef]

- Iles, P.A.; Leibenhaut, B. Diffusant impurity concentration profiles in thin layers on silicon. Solid State Electron. 1962, 5, 331–339. [Google Scholar] [CrossRef]

- Nicholas, K.H. Studies of anomalous diffusion of impurities in silicon. Solid State Electron. 1966, 9, 35–47. [Google Scholar] [CrossRef]

- Tsai, J.C.C. Shallow phosphorus diffusion profiles in silicon. Proc. IEEE. 1969, 57, 1499–1506. [Google Scholar] [CrossRef]

- Whitton, J.L.; Carter, G.; Freeman, J.H.; Gard, G.A. The implantation profiles of 10, 20 and 40 keV 85Kr in gallium arsenide. J. Mater. Sci. 1969, 4, 208–217. [Google Scholar] [CrossRef]

- Davies, J.A.; Ball, G.C.; Brown, F.; Domeij, B. Range of energetic Xe125 ions in monocrystalline silicon. Can. J. Phys. 1964, 42, 1070–1080. [Google Scholar] [CrossRef]

- Subashchiev, V.K.; Poltinnikov, S.A. Determination of carrier mobility and density in the surface layer of a semiconductor. Sov. Phys. Solid State 1960, 2, 1059–1066. [Google Scholar]

- Buehler, M.G. A Point-Contact Method for Determining the Charge Carrier Density and Mobility in Thin Semiconducting Layers; Stanford Research Report. SEL-66-064; Stanford University: Palo Alto, CA, USA, 1966. [Google Scholar]

- Mayer, J.W.; Marsh, O.J.; Shifrin, G.A.; Baron, R. Ion implantation of silicon -electrical evaluation using Hall-effect measurements. Can. J. Phys. 1967, 45, 4073–4089. [Google Scholar] [CrossRef]

- Baron, R.; Shifrin, G.A.; Marsh, O.J.; Mayer, J.W. Electrical behavior of group III and V implanted dopants in silicon. J. Appl. Phys. 1969, 40, 3702–3719. [Google Scholar] [CrossRef]

- Johansson, N.G.E.; Mayer, J.W.; Marsh, O.J. Technique used in Hall effect analysis of ion implanted Si and Ge. Solid State Electron. 1970, 13, 317–335. [Google Scholar] [CrossRef]

- Cembali, F.; Galloni, R.; Mousty, F.; Rosa, R.; Zignani, F. Doping and radiation damage profiles of P+ ions implanted in silicon along the [110] axis. Radiat. Eff. 1974, 21, 255–264. [Google Scholar] [CrossRef]

- Hofker, W.K.; Werner, H.W.; Oosthoek, D.P.; Koeman, N.J. Boron implantations in silicon: A comparison of charge carrier and boron concentration profiles. Appl. Phys. 1974, 4, 125–133. [Google Scholar] [CrossRef]

- Kim, C.-S.; Sakata, M. Diffusion coefficient of selenium in silicon by sheet Hall coefficient measurements. Jpn. J. Appl. Phys. 1979, 18, 247–254. [Google Scholar] [CrossRef]

- Bennett, N.S.; Cowern, N.E.B. Doping characterization for germanium-based microelectronics and photovoltaics using differential Hall technique. Appl. Phys. Lett. 2012, 100, 172106. [Google Scholar] [CrossRef]

- Shin, B.K.; Look, D.C.; Park, Y.S.; Ehret, J.E. Hall-effect measurements in Cd-implanted GaAs. J. Appl. Phys. 1976, 47, 1574–1579. [Google Scholar] [CrossRef]

- McLevige, W.V.; Helix, M.J.; Vaidyanathan, K.V.; Streetman, B.G. Electrical profiling and optical activation studies of Be-implanted GaAs. J. Appl. Phys. 1977, 48, 3342–3346. [Google Scholar] [CrossRef]

- Whitehead, N.J.; Gwilliam, R.M.; Gillin, W.P.; Sealy, B.J. The use of Hall effect profiling to monitor the reactivation of silicon implants after oxygen implantation in gallium arsenide. Vacuum 1989, 39, 1149–1151. [Google Scholar] [CrossRef]

- Jackson, N.F. Pulsed anodic etching of III-V semiconductors for carrier concentration profiling. Semicond. Sci. Technol. 1992, 7, 686–690. [Google Scholar] [CrossRef]

- Clarysse, T.; Brammertz, G.; Vanhaeren, D.; Eyben, P.; Goossen, J.; Clemente, F.; Meuris, M.; Vandervorst, W.; Srnanek, R.; Kinder, R.; et al. Accurate carrier profiling of n-type GaAs junctions. Mater. Sci. Semicond. Process. 2008, 11, 259–266. [Google Scholar] [CrossRef]

- Plunkett, J.C.; Stone, J.L. A computer algorithm for accurate and repeatable profile analysis using anodization and stripping of silicon. Solid State Electron. 1977, 20, 447–453. [Google Scholar] [CrossRef]

- Hill, A.; Allen, W.G.; Bradley, R. An automatic smoothing algorithm for the calculation of impurity concentration from sheet resistivity and sheet Hall coefficient data. Solid State Electron. 1980, 23, 491–496. [Google Scholar] [CrossRef]

- Barber, H.D.; Lo, H.B.; Jones, J.E. Repeated removal of thin layers of silicon by anodic oxidation. J. Electrochem. Soc. 1976, 123, 1404–1409. [Google Scholar] [CrossRef]

- Galloni, R.; Gavina, G.; Lotti, R.; Piombini, A. An automated system for the controlled stripping of thin silicon layers. Rev. Phys. Appl. 1978, 13, 81–84. [Google Scholar] [CrossRef][Green Version]

- Young, N.D.; Hight, M.J. Automated Hall effect profiler. Electron. Lett. 1985, 21, 1044–1045. [Google Scholar] [CrossRef]

- Blight, S.R.; Nicholls, R.E.; Sangha, S.P.S.; Kirby, P.B.; Teale, L.; Hiscock, S.P.; Stewart, C.P. Automated Hall profiling system for the characterization of semiconductors at room and liquid nitrogen temperatures. J. Phys. E Sci. Instrum. 1988, 21, 470–479. [Google Scholar] [CrossRef]

- Galloni, R.; Sardo, A. Fully automatic apparatus for the determination of doping profiles in Si by electrical measurements and anodic stripping. Rev. Sci. Instrum. 1983, 54, 369–373. [Google Scholar] [CrossRef]

- Bouro, L.; Tsoukalas, D. Determination of doping and mobility profiles by automatic electrical measurements and anodic stripping. J. Phys. E Sci. Instrum. 1987, 20, 541–544. [Google Scholar] [CrossRef]

- Alzanki, T.; Gwilliam, R.; Emerson, N.; Sealy, B.J. Differential Hall effect profiling of ultrashallow junctions in Sb implanted silicon. Appl. Phys. Lett. 2004, 85, 1979–1980. [Google Scholar] [CrossRef]

- Alzanki, T.; Gwilliam, R.; Emerson, N.; Sealy, B.J. Carrier and mobility profiling of ultra-shallow junctions in Sb implanted silicon. Electron. Lett. 2004, 40, 774–775. [Google Scholar] [CrossRef]

- Alzanki, T.; Gwilliam, R.; Emerson, N.; Smith, A.; Webb, R.; Sealy, B.J. Electrical profiles of 20nm junctions in Sb implanted silicon. Nucl. Instr. Meth. Phys. Res. B 2006, 242, 693–695. [Google Scholar] [CrossRef]

- Bennett, N.S.; Smith, A.J.; Colombeau, B.; Gwilliam, R.; Cowern, N.E.B.; Sealy, B.J. Differential Hall profiling of ultra-shallow junctions in Si and SOI. Mater. Sci. Eng. B 2005, 124–125, 305–309. [Google Scholar] [CrossRef]

- Bennett, N.S.; Cowern, N.E.B.; Smith, A.J.; Kah, M.; Gwilliam, R.M.; Sealy, B.J.; Noakes, T.C.Q.; Bailey, P.; Giubertoni, D.; Bersani, M. Differential Hall characterization of ultrashallow doping in advanced Si-based materials. Mater. Sci. Eng. B 2008, 154–155, 229–233. [Google Scholar] [CrossRef]

- Daubriac, R.; Abou Daher, M.; Cristano, F.; Scheid, E.; Joblot, S.; Barge, D. Differential Hall characterization of shallow strained SiGe layers. In Proceedings of the Nanotechnology Materials and Devices Conference, Toulouse, France, 9 October 2016. [Google Scholar] [CrossRef]

- Daubriac, R.; Scheid, E.; Rizk, H.; Monflier, R.; Joblot, S.; Beneyton, R.; Alba, P.; Kerdiles, S.; Cristano, F. A differential Hall effect measurement method with sub-nanometer resolution for active dopant concentration profiling in ultrathin doped SiGe and Si layers. Beilstein J. Nanotechnol. 2018, 9, 1926–1939. [Google Scholar] [CrossRef]

- Prussin, S.A. In Situ Determination of Resistivity, Mobility and Dopant Concentration Profiles. U.S. Patent 7,078,919, 18 July 2006. [Google Scholar]

- Prussin, S.A. The continuous anodic oxidation technique. AIP Conf. Proc. 2007, 931, 275–278. [Google Scholar] [CrossRef]

- Prussin, S.; Qin, S.; Reyes, J.; Mcteer, A. The application of the continuous anodic oxidation technique for evaluation of state-of-the-art frontend structures. AIP Conf. Proc. 2008, 1066, 75–78. [Google Scholar] [CrossRef]

- Timans, P.J.; Hu, Y.Z.; Lee, Y.; Gelpey, J.; McCoy, S.; Lerch, W.; Paul, S.; Bolze, D.; Kheyrandish, H.; Reyes, J.; et al. Optimization of diffusion, activation and damage annealing in millisecond annealing. In Proceedings of 16th IEEE International Conference on Advanced Thermal Processing of Semiconductors, Las Vegas, NV, USA, 30 September 2008. [Google Scholar] [CrossRef]

- Prussin, S.; Reyes, J. The evaluation of state-of-the-art front-end structures by differential Hall effect continuous anodic oxidation technique. ECS Trans. 2009, 19, 135–146. [Google Scholar] [CrossRef]

- Prussin, S.; Reyes, J. The application of differential Hall effect continuous anodic oxidation technique for ultra shallow structures. ECS Trans. 2009, 25, 139–150. [Google Scholar] [CrossRef]

- Qin, S.; Prussin, S.A.; Reyes, J.; Hu, Y.J.; McTeer, A. Study of low-energy doping processes using continuous anodic oxidation technique/differential Hall effect measurements. IEEE Trans. Plasma Sci. 2009, 37, 1754–1759. [Google Scholar] [CrossRef]

- Onoda, H.; Hamamoto, N.; Nagayama, T.; Sakai, S.; Tanjyo, M.; Umisedo, S.; Koga, Y.; Maehara, N.; Kawamura, Y.; Nakashima, Y.; et al. Effect of cluster carbon implantation at low temperature on damage recovery after rapid thermal annealing. In Proceedings of 18th IEEE International Conference on Advanced Thermal Processing of Semiconductors, Gainesville, FL, USA, 31 May 2010. [Google Scholar] [CrossRef]

- Qin, S.; McTeer, A.; Hu, Y.J.; Prussin, S.; Reyes, J. A comparative study of dopant activation and deactivation in arsenic and phosphorus implanted silicon. AIP Conf. Proc. 2011, 1321, 188–191. [Google Scholar] [CrossRef]

- Collart, E.J.H.; Kopalidis, P.M.; Hou, M.; McCoy, S.; Timans, P.J.; Joshi, A.; Prussin, S. Effects of implant temperature and millisecond annealing on dopant activation and diffusion. AIP Conf. Proc. 2012, 1496, 95–98. [Google Scholar] [CrossRef]

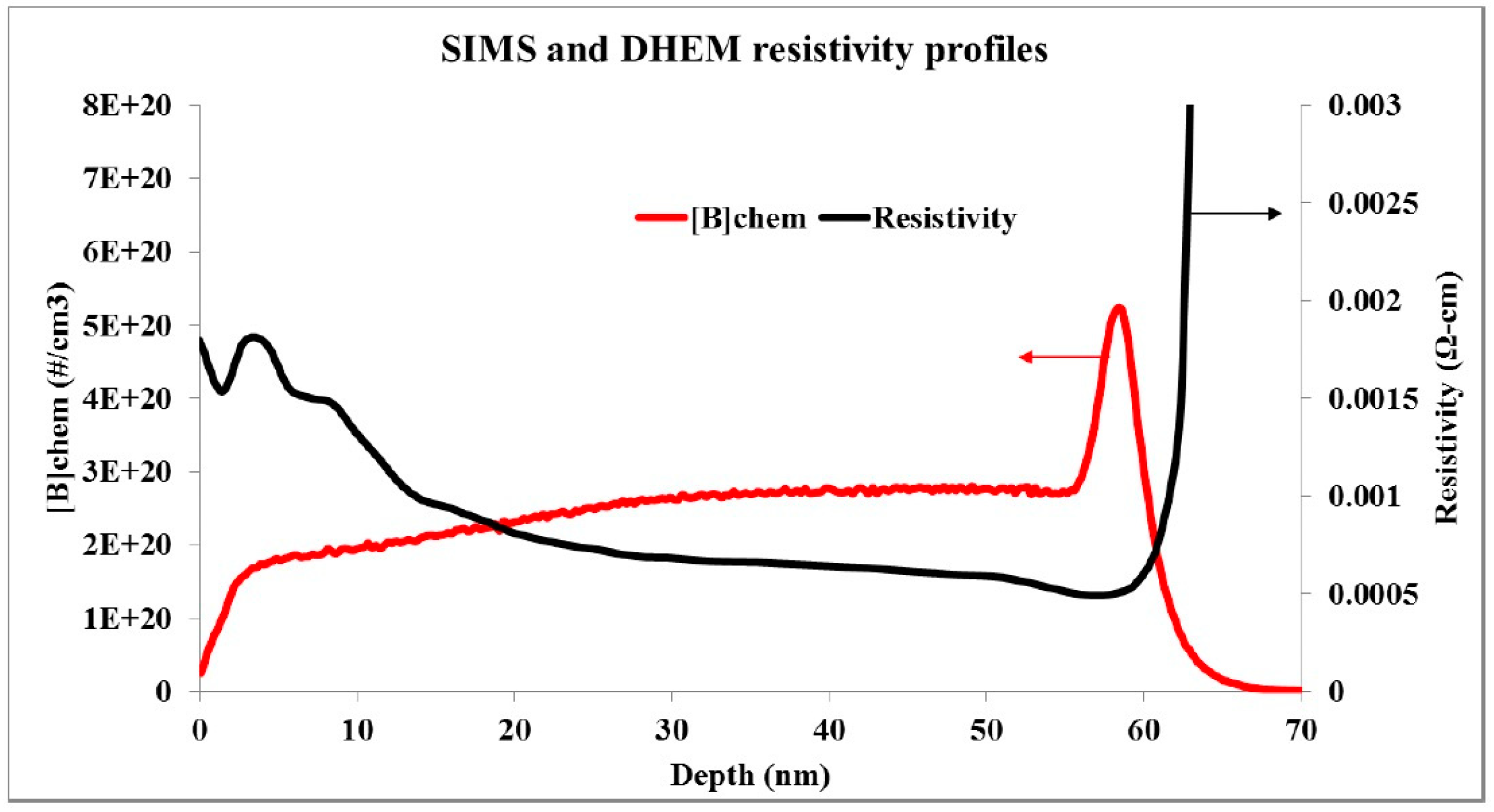

- Celano, U.; Wouters, L.; Franquet, A.; Spampinato, V.; van der Heide, P.; Schaekers, M.; Joshi, A.; Basol, B. Dopant activation depth profiling for highly doped Si:P by scanning spreading resistance microscopy (SSRM) and differential Hall effect metrology (DHEM). ECS Trans. 2022, 108, 9–15. [Google Scholar] [CrossRef]

- Joshi, A.; Basol, B. Sub-nm near-surface activation profiling for highly doped Si and Ge using differential Hall effect metrology (DHEM). ECS Trans. 2020, 98, 405–411. [Google Scholar] [CrossRef]

- Joshi, A.; Novak, S.W.; Basol, B.M. Differential Hall effect metrology (DHEM) for depth profiling of electrical properties at high resolution. In Proceedings of the International Conference on Frontiers of Characterization and Metrology for Nanoelectronics (FCMN), Monterey, CA, USA, 2 April 2019. [Google Scholar]

- Joshi, A.; Basol, B.M. Measuring activation depth profiles in very highly doped ultra-thin semiconductors at sub-nm depth resolution. MRS Adv. 2022, 7, 1326–1330. [Google Scholar] [CrossRef]

- Tabata, T.; Roze, F.; Thuries, L.; Halty, S.; Raynal, P.E.; Huet, K.; Mazzamuto, F.; Joshi, A.; Basol, B.M.; Alba, P.A.; et al. Microsecond non-melt UV laser annealing for future 3D-stacked CMOS. Appl. Phys. Express 2022, 15, 061002. [Google Scholar] [CrossRef]

- Joshi, A.; Tabata, T.; Roze, F.; Basol, B.M. Study of dopant activation in laser annealed highly doped arsenic-implanted Si by differential Hall effect metrology (DHEM). ECS Trans. 2022, 109, 329–333. [Google Scholar] [CrossRef]

- Ramesh, P.; Saraswat, K.C.; Joshi, A.; Basol, B.M.; Wang, L.; Buyuklimanli, T. Differential Hall effect metrology (DHEM) sub-nm profiling and its application to dopant activation in n-type Ge. ECS Trans. 2020, 97, 75–80. [Google Scholar] [CrossRef]

- Chang, H.-Y.; Wu, Y.-C.S.; Chang, C.-H.; Lin, K.-L.; Joshi, A.; Basol, B.M. Nano-scale depth profiles of electrical properties of phosphorus doped silicon for ultra-shallow junction evaluation. IEEE Trans. Semicond. Manuf. 2021, 34, 357–364. [Google Scholar] [CrossRef]

- Lin, K.-L.; Lee, F.-Y.; Chen, Y.-M.; Tseng, Y.-J.; Yen, H.-W. Complementary use of atom probe tomography (APT) and differential Hall effect metrology (DHEM) for activation loss in phosphorus-implanted polycrystalline silicon. Scr. Mater. 2024, 241, 115877. [Google Scholar] [CrossRef]

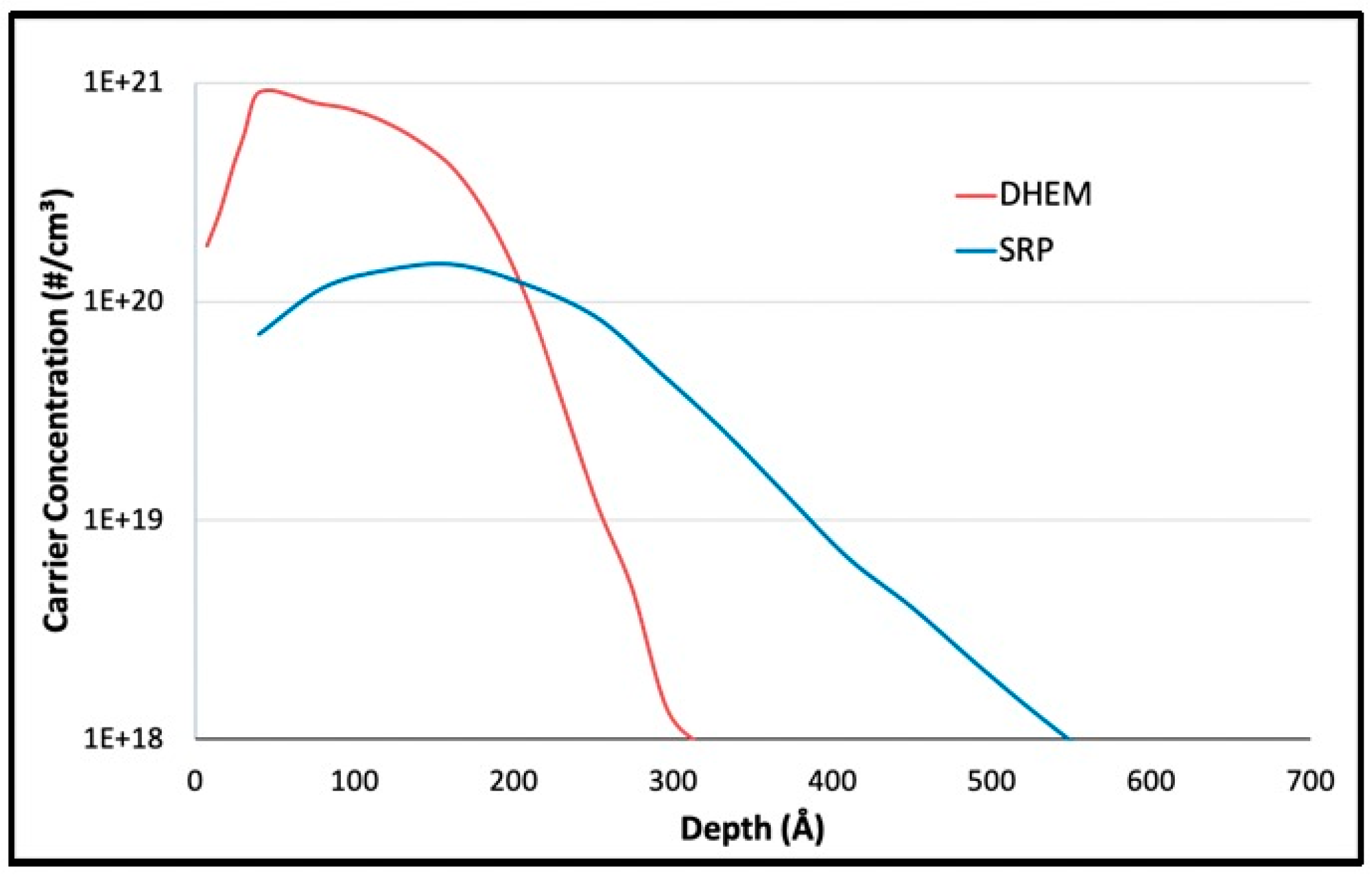

- Lin, K.-L.; Chang, C.H.; Joshi, A.; Basol, B.M. Comparison of dopant activation in Si as characterized by spreading resistance profiling (SRP) and differential Hall effect metrology (DHEM). In Proceedings of the International Conference on Frontiers of Characterization and Metrology for Nanoelectronics (FCMN), Monterey, CA, USA, 20 June 2022; Available online: https://drive.google.com/file/d/1KbglbuyqX_FxgDdLEh-1SHNQJNwGruuB/view (accessed on 14 August 2024).

- Joshi, A.; Rengo, G.; Porret, C.; Lin, K.-L.; Chang, C.-H.; Basol, B.M. Characterization of doping and activation processes using differential Hall effect metrology. ECS Trans. 2021, 102, 113–116. [Google Scholar] [CrossRef]

- Rengo, G.; Porret, C.; Hikavyy, A.Y.; Rosseel, E.; Nakazaki, N.; Pourtois, G.; Vantomme, A.; Loo, R. Highly doped Si1-xGex epitaxy in view of S/D applications. ECS Trans. 2020, 98, 27–36. [Google Scholar] [CrossRef]

- David, J.M.; Beuhler, M.G. A numerical analysis of various cross sheet resistor test structures. Solid State Electron. 1977, 20, 539–543. [Google Scholar] [CrossRef]

- De Mey, G. Potential calculations in Hall plates. In Advances in Electronics and Electron Physics; Marton, L., Marton, C., Eds.; Academic: New York, NY, USA, 1983; Volume 61, pp. 1–61. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Basol, B.M.; Joshi, A. Differential Hall Effect Metrology for Electrical Characterization of Advanced Semiconductor Layers. Metrology 2024, 4, 547-565. https://doi.org/10.3390/metrology4040034

Basol BM, Joshi A. Differential Hall Effect Metrology for Electrical Characterization of Advanced Semiconductor Layers. Metrology. 2024; 4(4):547-565. https://doi.org/10.3390/metrology4040034

Chicago/Turabian StyleBasol, Bulent M., and Abhijeet Joshi. 2024. "Differential Hall Effect Metrology for Electrical Characterization of Advanced Semiconductor Layers" Metrology 4, no. 4: 547-565. https://doi.org/10.3390/metrology4040034

APA StyleBasol, B. M., & Joshi, A. (2024). Differential Hall Effect Metrology for Electrical Characterization of Advanced Semiconductor Layers. Metrology, 4(4), 547-565. https://doi.org/10.3390/metrology4040034