E/E Architecture Synthesis: Challenges and Technologies

Abstract

:1. Introduction

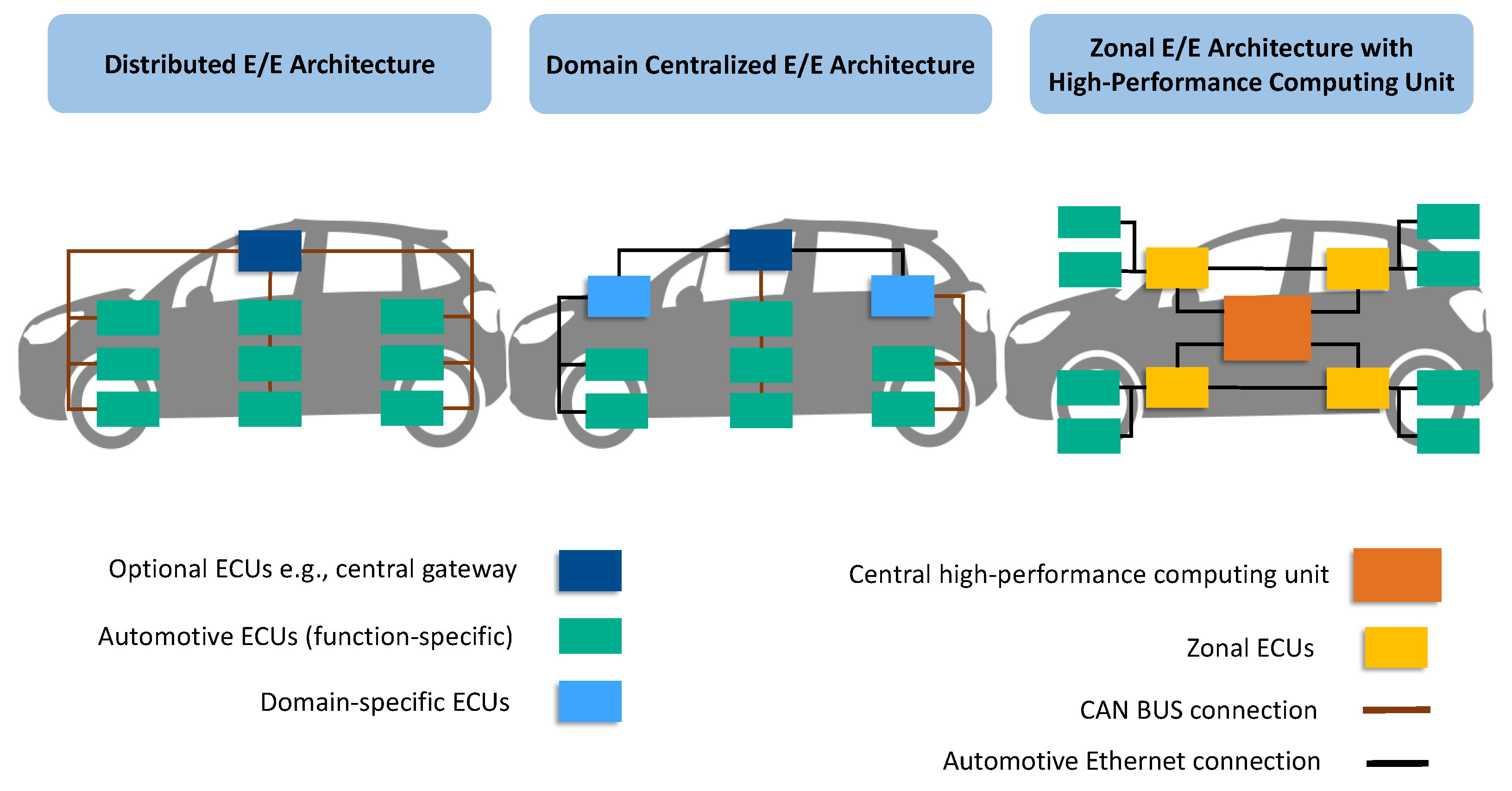

2. Basic Concepts

2.1. The Main Bottlenecks of Current E/E Architecture

2.2. The Main Technologies for Future’s E/E Architecture

- Type 1: also called Bare Metal or Native hypervisor, as it is installed and runs directly on top of the host’s hardware without using any host OS. This type of hypervisor has direct control over and access to hardware resources. For example, a type-1 hypervisor can assign a specific core to a partition (an execution environment managed by the hypervisor which uses the virtualized services) in such a way that other partitions cannot access that core.

- Type 2: also known as Hosted hypervisor. It runs as an application in the host OS and uses the hardware resources for its VMs by coordinating calls through the host’s OS. The host OS does not have any knowledge about this type of hypervisor and it treats it as any other normal process [22].

3. Technologies and Challenges

3.1. Task Mapping in Multi-Core Computing Units

3.1.1. Introduction to Task Mapping

3.1.2. Mapping Techniques

3.1.3. Optimization Parameters in Mapping

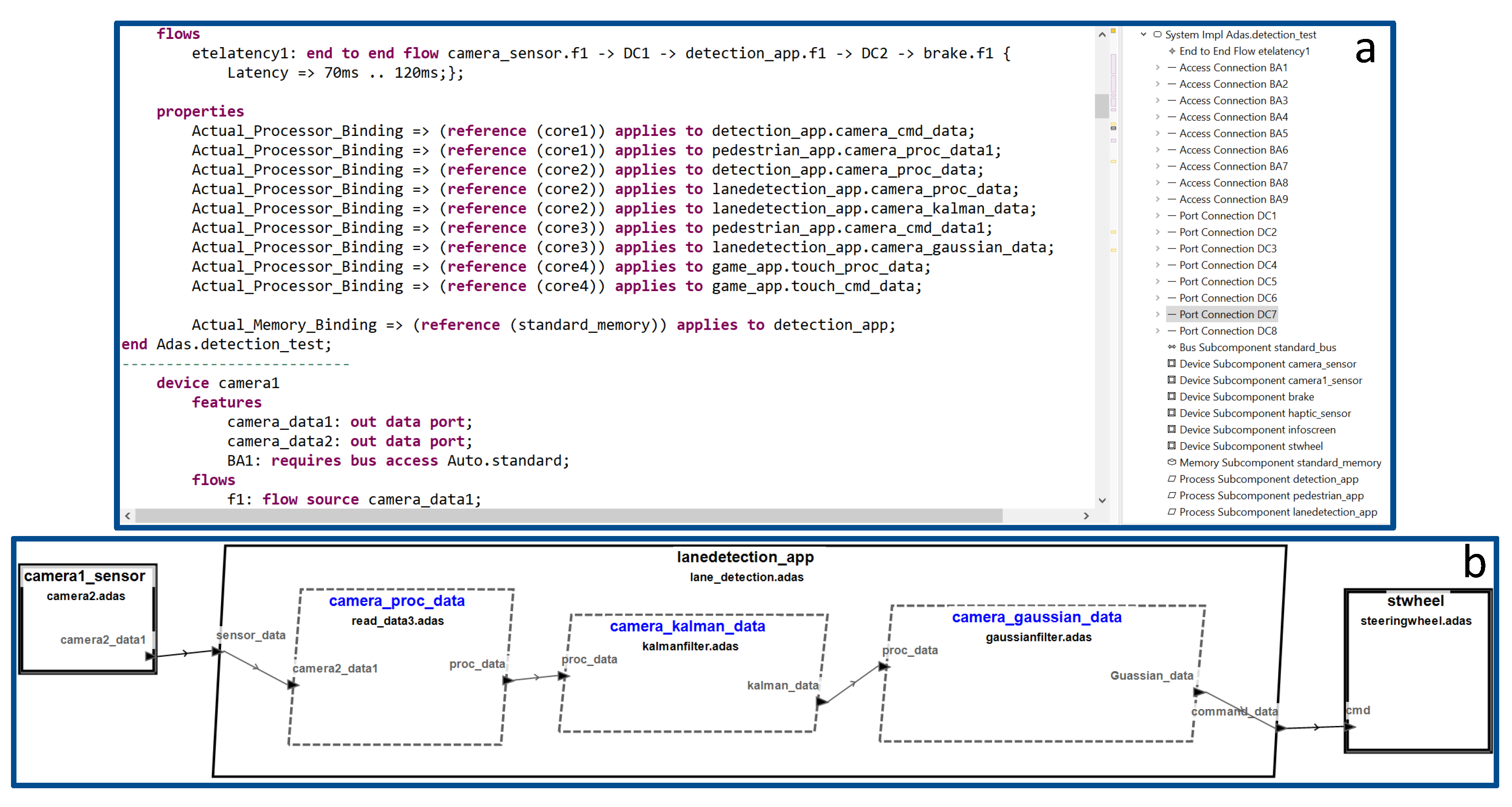

3.2. Technologies for Software Integration and Configuration in Design Process

- AADL Model Parser: This interprets and extracts system descriptions from an AADL specification coming from the OSATE tool. The module can access AADL elements such as components, services, buses, etc. The extracted parameters are sent to the Architecture Analysis Module, as an input, which supports the two interfaces for analyzing the model comprising Architecture Constraints Validation and Architecture Quality Evaluation Interface (see Figure 5).

- Architecture Constraints Validation Interface: As displayed in Figure 5, it provides a plug-in point for Constraint Evaluator modules that check a given architecture for constraint satisfaction.

- Architecture Quality Evaluation Interface: In this part, various quality evaluation functions can be taken into account. In ArcheOpterix, the Attribute Evaluator module performs quality evaluation functions, which can be extended for evaluated features. Current integrated features in ArcheOpterix are Service Reliability, Data Transmission Reliability, and Communication Overhead.

- Architecture Optimization Interface: This provides an opportunity to add new optimization algorithms to the framework. The current tool comprises Exact Algorithms, Genetic Algorithms, and Ant Colony Optimization [70].

4. Future Research Areas

- How to facilitate and automate the assignment of HPCU resources to safety-critical applications while verifying the satisfaction of the specified safety requirements in the design phase to compute a verified and optimized mapping configuration considering the predetermined optimization objectives?

- How to verify the fulfillment of the specified requirements (particularly safety-critical ones) after deployment of the derived configuration to the HPCU at run-time?

- How to evaluate the performance of the calculated mapping configuration at run-time focused on the specified optimization goals in design-time?

- How to discover the source of the conflict among defined constraints in our system while using the DSE approach to find the optimal solution in case of an infeasible solution?

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- ISO. Safety Of The Intended Functionality (SOTIF). 2019. Available online: https://www.iso.org/standard/70939.html (accessed on 16 September 2021).

- ISO 26262-1:2018. 2018. Available online: https://www.iso.org/standard/68383.html (accessed on 30 August 2021).

- Freddie Holmes, J.H.; Moreton, J. Zonal E/E Architectures the Cornerstone of Future Mobility Development. 2021. Available online: https://www.automotiveworld.com/articles/zonal-e-e-architectures-the-cornerstone-of-future-mobility-development (accessed on 30 September 2021).

- Broy, M. Challenges in automotive software engineering. In Proceedings of the 28th International Conference on Software Engineering, Shanghai, China, 20–28 May 2006; pp. 33–42. [Google Scholar]

- Askaripoor, H.; Farzaneh, M.H.; Knoll, A. A Model-Based Approach to Facilitate Design of Homogeneous Redundant E/E Architectures. In Proceedings of the 2021 IEEE International Intelligent Transportation Systems Conference (ITSC), Indianapolis, IN, USA, 19–22 September 2021; pp. 3426–3431. [Google Scholar] [CrossRef]

- Bandur, V.; Selim, G.; Pantelic, V.; Lawford, M. Making the Case for Centralized Automotive E/E Architectures. IEEE Trans. Veh. Technol. 2021, 70, 1230–1245. [Google Scholar] [CrossRef]

- Askaripoor, H.; Farzaneh, M.H.; Knoll, A. A Platform to Configure and Monitor Safety-Critical Applications for Automotive Central Computers. In Proceedings of the 2021 26th IEEE International Conference on Emerging Technologies and Factory Automation (ETFA ), Vasteras, Sweden, 7–10 September 2021; pp. 1–4. [Google Scholar] [CrossRef]

- Apostu, S.; Burkacky, O.; Deichmann, J.; Doll, G. Automotive Software and Electrical/Electronic Architecture: Implications for OEMs. 2019. Available online: https://www.mckinsey.com/industries/automotive-and-assembly/our-insights/automotive-software-and-electrical-electronic-architecture-implications-for-oems (accessed on 10 October 2021).

- Butzkamm, C.; Brand, K. E/E Architecture in the HARRI Innovation Platform. Atzelectroni. Worldw. 2020, 15, 18–24. [Google Scholar] [CrossRef]

- Zerfowski, D.; Lock, A. Functional Architecture and E/E-Architecture–A Challenge for the Automotive Industry; Internationales Stuttgarter Symposium; Springer: Berlin/Heidelberg, Germany, 2019; pp. 909–920. [Google Scholar]

- Jiang, S. Vehicle e/e Architecture and Its Adaptation to New Technical Trends; Technical Report; SAE Technical Paper: Warrendale, PA, USA, 2019. [Google Scholar]

- Shavit, M.; Gryc, A.; Miucic, R. Firmware Update over the Air (FOTA) for Automotive Industry; Technical Report; SAE Technical Paper: Warrendale, PA, USA, 2007. [Google Scholar]

- Wang, J.; Liu, J.; Kato, N. Networking and communications in autonomous driving: A survey. IEEE Commun. Surv. Tutor. 2018, 21, 1243–1274. [Google Scholar] [CrossRef]

- Singer, S. The Car Will Become a Data Center. Atzelectron. Worldw. 2020, 15, 8–13. [Google Scholar] [CrossRef]

- Navale, V.M.; Williams, K.; Lagospiris, A.; Schaffert, M.; Schweiker, M.A. (R) evolution of E/E architectures. SAE Int. J. Passeng.-Cars-Electron. Electr. Syst. 2015, 8, 282–288. [Google Scholar] [CrossRef]

- Sommer, S.; Camek, A.; Becker, K.; Buckl, C.; Zirkler, A.; Fiege, L.; Armbruster, M.; Spiegelberg, G.; Knoll, A. RACE: A Centralized Platform Computer Based Architecture for Automotive Applications. In Proceedings of the 2013 IEEE International Electric Vehicle Conference (IEVC), Santa Clara, CA, USA, 23–25 October 2013; pp. 1–6. [Google Scholar] [CrossRef] [Green Version]

- Sangiovanni-Vincentelli, A.; Di Natale, M. Embedded System Design for Automotive Applications. Computer 2007, 40, 42–51. [Google Scholar] [CrossRef]

- Brunner, S.; Roder, J.; Kucera, M.; Waas, T. Automotive E/E-architecture enhancements by usage of ethernet TSN. In Proceedings of the 2017 13th Workshop on Intelligent Solutions in Embedded Systems (WISES), Hamburg, Germany, 12–13 June 2017; pp. 9–13. [Google Scholar]

- Shapiro, D. The Future of Automotive is Software-defined. Atzelectron. Worldw. 2020, 15, 72. [Google Scholar] [CrossRef]

- Knoll, A.; Buckl, C.; Kuhn, K.J.; Spiegelberg, G. The RACE Project: An Informatics-Driven Greenfield Approach to Future E/E Architectures for Cars. In Automotive Systems and Software Engineering; Springer: Berlin/Heidelberg, Germany, 2019; pp. 171–195. [Google Scholar]

- Dall, C.; Nieh, J. KVM/ARM: The design and implementation of the linux ARM hypervisor. ACM Sigplan Not. 2014, 49, 333–348. [Google Scholar] [CrossRef]

- Desai, A.; Oza, R.; Sharma, P.; Patel, B. Hypervisor: A survey on concepts and taxonomy. Int. J. Innov. Technol. Explor. Eng. 2013, 2, 222–225. [Google Scholar]

- Khan, A.; Zugenmaier, A.; Jurca, D.; Kellerer, W. Network virtualization: A hypervisor for the Internet? IEEE Commun. Mag. 2012, 50, 136–143. [Google Scholar] [CrossRef]

- Pelliccione, P.; Knauss, E.; Heldal, R.; Ågren, S.M.; Mallozzi, P.; Alminger, A.; Borgentun, D. Automotive architecture framework: The experience of volvo cars. J. Syst. Archit. 2017, 77, 83–100. [Google Scholar] [CrossRef]

- Askaripoor, H.; Shafaei, S.; Knoll, A.C. A Flexible Scheduling Architecture of Resource Distribution Proposal for Autonomous Driving Platforms. In Proceedings of the VEHITS, Online Streaming, 28–30 April 2021; pp. 594–599. [Google Scholar]

- Askaripoor, H.; Farzaneh, M.H.; Knoll, A. Considering Safety Requirements in Design Phase of Future E/E Architectures. In Proceedings of the 2020 25th IEEE International Conference on Emerging Technologies and Factory Automation (ETFA), Vienna, Austria, 8–11 September 2020; Volume 1, pp. 1165–1168. [Google Scholar] [CrossRef]

- Zheng, B.; Liang, H.; Zhu, Q.; Yu, H.; Lin, C.W. Next generation automotive architecture modeling and exploration for autonomous driving. In Proceedings of the 2016 IEEE Computer Society Annual Symposium on VLSI (ISVLSI), Pittsburgh, PA, USA, 11–13 July 2016; pp. 53–58. [Google Scholar]

- Singh, A.K.; Shafique, M.; Kumar, A.; Henkel, J. Resource and Throughput Aware Execution Trace Analysis for Efficient Run-Time Mapping on MPSoCs. IEEE Trans. -Comput.-Aided Des. Integr. Circuits Syst. 2016, 35, 72–85. [Google Scholar] [CrossRef]

- Sahu, P.K.; Chattopadhyay, S. A survey on application mapping strategies for network-on-chip design. J. Syst. Archit. 2013, 59, 60–76. [Google Scholar] [CrossRef]

- Mehrara, M.; Jablin, T.; Upton, D.; August, D.; Hazelwood, K.; Mahlke, S. Multicore compilation strategies and challenges. IEEE Signal Process. Mag. 2009, 26, 55–63. [Google Scholar] [CrossRef] [Green Version]

- Xie, G.; Zeng, G.; Liu, Y.; Zhou, J.; Li, R.; Li, K. Fast functional safety verification for distributed automotive applications during early design phase. IEEE Trans. Ind. Electron. 2017, 65, 4378–4391. [Google Scholar] [CrossRef]

- Xie, G.; Li, Y.; Han, Y.; Xie, Y.; Zeng, G.; Li, R. Recent advances and future trends for automotive functional safety design methodologies. IEEE Trans. Ind. Inform. 2020, 16, 5629–5642. [Google Scholar] [CrossRef]

- Gupta, M.; Bhargava, L.; Indu, S. Mapping techniques in multicore processors: Current and future trends. J. Supercomput. 2021, 77, 9308–9363. [Google Scholar] [CrossRef]

- Singh, A.K.; Shafique, M.; Kumar, A.; Henkel, J. Mapping on multi/many-core systems: Survey of current and emerging trends. In Proceedings of the 2013 50th ACM/EDAC/IEEE Design Automation Conference (DAC), Austin, TX, USA, 29 May–7 June 2013; pp. 1–10. [Google Scholar]

- Deveci, M.; Kaya, K.; Uçar, B.; Çatalyürek, Ü.V. Hypergraph partitioning for multiple communication cost metrics: Model and methods. J. Parallel Distrib. Comput. 2015, 77, 69–83. [Google Scholar] [CrossRef] [Green Version]

- Shivle, S.; Castain, R.; Siegel, H.J.; Maciejewski, A.A.; Banka, T.; Chindam, K.; Dussinger, S.; Pichumani, P.; Satyasekaran, P.; Saylor, W.; et al. Static mapping of subtasks in a heterogeneous ad hoc grid environment. In Proceedings of the 18th International Parallel and Distributed Processing Symposium, Santa Fe, NM, USA, 26–30 April 2004; p. 110. [Google Scholar]

- Bokhari, S.H. A shortest tree algorithm for optimal assignments across space and time in a distributed processor system. IEEE Trans. Softw. Eng. 1981, SE-7, 583–589. [Google Scholar] [CrossRef]

- Braun, T.D.; Siegel, H.J.; Beck, N.; Bölöni, L.L.; Maheswaran, M.; Reuther, A.I.; Robertson, J.P.; Theys, M.D.; Yao, B.; Hensgen, D.; et al. A comparison of eleven static heuristics for mapping a class of independent tasks onto heterogeneous distributed computing systems. J. Parallel Distrib. Comput. 2001, 61, 810–837. [Google Scholar] [CrossRef] [Green Version]

- Castrillon, J.; Tretter, A.; Leupers, R.; Ascheid, G. Communication-aware mapping of KPN applications onto heterogeneous MPSoCs. In Proceedings of the DAC Design Automation Conference, San Francisco, CA, USA, 3–7 June 2012; pp. 1262–1267. [Google Scholar]

- Niemann, R.; Marwedel, P. An algorithm for hardware/software partitioning using mixed integer linear programming. Des. Autom. Embed. Syst. 1997, 2, 165–193. [Google Scholar] [CrossRef]

- Hu, J.; Marculescu, R. Energy-and performance-aware mapping for regular NoC architectures. IEEE Trans. -Comput.-Aided Des. Integr. Circuits Syst. 2005, 24, 551–562. [Google Scholar]

- Bhatti, Z.W.; Miniskar, N.R.; Preuveneers, D.; Wuyts, R.; Berbers, Y.; Catthoor, F. Memory and communication driven spatio-temporal scheduling on MPSoCs. In Proceedings of the 2012 25th Symposium on Integrated Circuits and Systems Design (SBCCI), Brasilia, Brazil, 30 August–2 September 2012; pp. 1–6. [Google Scholar]

- Kaida, J.; Hieda, T.; Taniguchi, I.; Tomiyama, H.; Hara-Azumi, Y.; Inoue, K. Task mapping techniques for embedded many-core socs. In Proceedings of the 2012 International SoC Design Conference (ISOCC), Jeju Island, Korea, 4–7 November 2012; pp. 204–207. [Google Scholar]

- Pascual, J.A.; Miguel-Alonso, J.; Lozano, J.A. Optimization-based mapping framework for parallel applications. J. Parallel Distrib. Comput. 2011, 71, 1377–1387. [Google Scholar] [CrossRef]

- Giannopoulou, G.; Stoimenov, N.; Huang, P.; Thiele, L. Mapping mixed-criticality applications on multi-core architectures. In Proceedings of the 2014 Design, Automation & Test in Europe Conference & Exhibition (DATE), Dresden, Germany, 24–28 March 2014; pp. 1–6. [Google Scholar]

- Gan, Z.; Zhang, M.; Gu, Z.; Zhang, J. Minimizing energy consumption for embedded multicore systems using cache configuration and task mapping. In Proceedings of the 2016 International Conference on Cyber-Enabled Distributed Computing and Knowledge Discovery (CyberC), Chengdu, China, 13–15 October 2016; pp. 328–334. [Google Scholar]

- Ferrandi, F.; Lanzi, P.L.; Pilato, C.; Sciuto, D.; Tumeo, A. Ant colony heuristic for mapping and scheduling tasks and communications on heterogeneous embedded systems. IEEE Trans. -Comput.-Aided Des. Integr. Circuits Syst. 2010, 29, 911–924. [Google Scholar] [CrossRef] [Green Version]

- Xu, X.X.; Hu, X.M.; Chen, W.N.; Li, Y. Set-based particle swarm optimization for mapping and scheduling tasks on heterogeneous embedded systems. In Proceedings of the 2016 Eighth International Conference on Advanced Computational Intelligence (ICACI), Chiang Mai, Thailand, 14–16 February 2016; pp. 318–325. [Google Scholar]

- Carvalho, E.; Calazans, N.; Moraes, F. Heuristics for dynamic task mapping in NoC-based heterogeneous MPSoCs. In Proceedings of the 18th IEEE/IFIP International Workshop on Rapid System Prototyping (RSP’07), Porto Alegre, Brazil, 28–30 May 2007; pp. 34–40. [Google Scholar]

- Xie, G.; Peng, H.; Li, Z.; Song, J.; Xie, Y.; Li, R.; Li, K. Reliability enhancement toward functional safety goal assurance in energy-aware automotive cyber-physical systems. IEEE Trans. Ind. Inf. 2018, 14, 5447–5462. [Google Scholar] [CrossRef]

- Peress, Y. Multi-core Design and Memory Feature Selection Survey. Available online: https://ww2.cs.fsu.edu/~peress/publications/AreaSurvey.pdf (accessed on 30 August 2021).

- Das, A.; Kumar, A.; Veeravalli, B. Communication and migration energy aware task mapping for reliable multiprocessor systems. Future Gener. Comput. Syst. 2014, 30, 216–228. [Google Scholar] [CrossRef]

- Huang, L.; Yuan, F.; Xu, Q. Lifetime reliability-aware task allocation and scheduling for MPSoC platforms. In Proceedings of the 2009 Design, Automation & Test in Europe Conference & Exhibition, Nice, France, 20–24 April 2009; pp. 51–56. [Google Scholar]

- Ding, H.; Liang, Y.; Mitra, T. Shared cache aware task mapping for WCRT minimization. In Proceedings of the 2013 18th Asia and South Pacific Design Automation Conference (ASP-DAC), Yokohama, Japan, 22–25 January 2013; pp. 735–740. [Google Scholar]

- Coskun, A.K.; Rosing, T.S.; Whisnant, K.A.; Gross, K.C. Temperature-aware MPSoC scheduling for reducing hot spots and gradients. In Proceedings of the 2008 Asia and South Pacific Design Automation Conference, Seoul, Korea, 21–24 March 2008; pp. 49–54. [Google Scholar]

- Girault, A.; Zarandi, H.R. Erpot: A quad-criteria scheduling heuristic to optimize execution time, reliability, power consumption and temperature in multicores. IEEE Trans. Parallel Distrib. Syst. 2019, 30, 2193–2210. [Google Scholar]

- Hartman, A.S.; Thomas, D.E.; Meyer, B.H. A case for lifetime-aware task mapping in embedded chip multiprocessors. In Proceedings of the Eighth IEEE/ACM/IFIP International Conference on Hardware/Software Codesign and System Synthesis, Scottsdale, AZ, USA, 24–29 October 2010; pp. 145–154. [Google Scholar]

- Das, A.; Kumar, A.; Veeravalli, B.; Bolchini, C.; Miele, A. Combined DVFS and mapping exploration for lifetime and soft-error susceptibility improvement in MPSoCs. In Proceedings of the 2014 Design, Automation & Test in Europe Conference & Exhibition (DATE), Dresden, Germany, 24–28 March 2014; pp. 1–6. [Google Scholar]

- Kinsy, M.A.; Devadas, S. Algorithms for scheduling task-based applications onto heterogeneous many-core architectures. In Proceedings of the 2014 IEEE High Performance Extreme Computing Conference (HPEC), Waltham, MA USA, 9–11 September 2014; pp. 1–6. [Google Scholar]

- Lee, S.; Ro, W.W. Workload and variation aware thread scheduling for heterogeneous multi-processor. In Proceedings of the 18th IEEE International Symposium on Consumer Electronics (ISCE 2014), Jeju, Korea, 22–25 June 2014; pp. 1–2. [Google Scholar]

- Liu, G.; Park, J.; Marculescu, D. Dynamic thread mapping for high-performance, power-efficient heterogeneous many-core systems. In Proceedings of the 2013 IEEE 31st International Conference on Computer Design (ICCD), Asheville, NC, USA, 6–9 October 2013; pp. 54–61. [Google Scholar]

- Bolchini, C.; Carminati, M.; Mitra, T.; Muthukaruppan, T.S. Combined on-line lifetime-energy optimization for asymmetric multicores. In Proceedings of the 2016 IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems (DFT), Storrs, CT, USA, 19–20 September 2016; pp. 35–40. [Google Scholar]

- Feiler, P. The Open Source AADL Tool Environment (OSATE); Technical Report; Carnegie Mellon University Software Engineering Institute, 2019; Available online: https://resources.sei.cmu.edu/asset_files/Presentation/2019_017_001_635851.pdf (accessed on 30 August 2021).

- Welcome to OSATE. 2021. Available online: https://osate.org/ (accessed on 11 November 2021).

- Feiler, P.H.; Gluch, D.P.; Hudak, J.J. The Architecture Analysis & Design Language (AADL): An Introduction; Technical Report; Carnegie-Mellon Univ Pittsburgh PA Software Engineering Inst: Pittsburgh, PA, USA, 2006. [Google Scholar]

- Introduction to Ocarina Plugin. 2021. Available online: https://ocarina.readthedocs.io/en/latest/introduction.html (accessed on 10 November 2021).

- Hugues, J.; Zalila, B.; Pautet, L.; Kordon, F. From the prototype to the final embedded system using the Ocarina AADL tool suite. ACM Trans. Embed. Comput. Syst. (TECS) 2008, 7, 1–25. [Google Scholar] [CrossRef]

- MATLAB. Version 7.10.0 (R2010a); The MathWorks Inc.: Natick, MA, USA, 2010. [Google Scholar]

- Aleti, A.; Bjornander, S.; Grunske, L.; Meedeniya, I. ArcheOpterix: An extendable tool for architecture optimization of AADL models. In Proceedings of the 2009 ICSE Workshop on Model-Based Methodologies for Pervasive and Embedded Software, Vancouver, BC, USA, 16 May 2009; pp. 61–71. [Google Scholar]

- Meedeniya, I.; Buhnova, B.; Aleti, A.; Grunske, L. Reliability-driven deployment optimization for embedded systems. J. Syst. Softw. 2011, 84, 835–846. [Google Scholar] [CrossRef]

- Koziolek, A.; Koziolek, H.; Reussner, R. PerOpteryx: Automated application of tactics in multi-objective software architecture optimization. In Proceedings of the joint ACM SIGSOFT Conference–QoSA and ACM SIGSOFT Symposium–ISARCS on Quality of Software Architectures–QoSA and Architecting Critical Systems–ISARCS, Boulder, CO, USA, 20–24 June 2011; pp. 33–42. [Google Scholar]

- Behrmann, G.; David, A.; Larsen, K.G.; Håkansson, J.; Pettersson, P.; Yi, W.; Hendriks, M. Uppaal 4.0. In Proceedings of the Quantitative Evaluation of SysTems (QEST), University of California, Riverside, CA, USA, 11–14 September 2006. [Google Scholar]

- Burmester, S.; Giese, H.; Tichy, M. Model-driven development of reconfigurable mechatronic systems with mechatronic UML. In Model Driven Architecture; Springer: Berlin/Heidelberg, Germany, 2004; pp. 47–61. [Google Scholar]

- Fritzson, P.; Engelson, V. Modelica—A unified object-oriented language for system modeling and simulation. In European Conference on Object-Oriented Programming; Springer: Berlin/Heidelberg, Germany, 1998; pp. 67–90. [Google Scholar]

- Schäfer, W.; Wehrheim, H. Model-driven development with mechatronic uml. In Graph Transformations and Model-Driven Engineering; Springer: Berlin/Heidelberg, Germany, 2010; pp. 533–554. [Google Scholar]

- Höttger, R.; Krawczyk, L.; Igel, B. Model-based automotive partitioning and mapping for embedded multicore systems. International Conference on Parallel, Distributed Systems and Software Engineering. Citeseer 2015, 2, 888. [Google Scholar]

- Höttger, R.; Mackamul, H.; Sailer, A.; Steghöfer, J.P.; Tessmer, J. APP4MC: Application platform project for multi-and many-core systems. Inf. Technol. 2017, 59, 243–251. [Google Scholar] [CrossRef]

- Aravantinos, V.; Voss, S.; Teufl, S.; Hölzl, F.; Schätz, B. AutoFOCUS 3: Tooling Concepts for Seamless, Model-based Development of Embedded Systems. ACES-MB&WUCOR@ MoDELS 2015, 1508, 19–26. [Google Scholar]

- Voss, S.; Eder, J.; Hölzl, F. Design Space Exploration and its Visualization in AUTOFOCUS3. Available online: http://ceur-ws.org/Vol-1129/paper33.pdf (accessed on 30 August 2021).

- Juodisius, P.; Sarkar, A.; Mukkamala, R.R.; Antkiewicz, M.; Czarnecki, K.; Wasowski, A. Clafer: Lightweight modeling of structure, behaviour, and variability. arXiv 2018, arXiv:1807.08576. [Google Scholar] [CrossRef] [PubMed]

- Kugele, S.; Pucea, G.; Popa, R.; Dieudonné, L.; Eckardt, H. On the deployment problem of embedded systems. In Proceedings of the 2015 ACM/IEEE International Conference on Formal Methods and Models for Codesign (MEMOCODE), Austin, TX, USA, 21–23 September 2015; pp. 158–167. [Google Scholar]

- Hilbrich, R.; Dieudonné, L. Deploying Safety-Critical Applications on Complex Avionics Hardware Architectures. Available online: https://www.scirp.org/html/1-9301646_31297.htm?pagespeed=noscript (accessed on 10 October 2021).

- Hilbrich, R.; Behrisch, M. Experiences gained from modeling and solving large mapping problems during system design. In Proceedings of the 2017 Annual IEEE International Systems Conference (SysCon), Montreal, QC, Canada, 24–27 April 2017; pp. 1–8. [Google Scholar]

- Bondarev, E.; Chaudron, M.R.; de Kock, E.A. Exploring performance trade-offs of a JPEG decoder using the DeepCompass framework. In Proceedings of the 6th International Workshop on Software and Performance, Buenes Aires, Argentina, 5–8 February 2007; pp. 153–163. [Google Scholar]

- Švogor, I.; Carlson, J. SCALL: Software component allocator for heterogeneous embedded systems. In Proceedings of the 2015 European Conference on Software Architecture Workshops, Dubrovnik/Cavtat, Croatia, 7–11 September 2015; pp. 1–5. [Google Scholar]

- Li, R.; Etemaadi, R.; Emmerich, M.T.; Chaudron, M.R. An evolutionary multiobjective optimization approach to component-based software architecture design. In Proceedings of the 2011 IEEE Congress of Evolutionary Computation (CEC), New Orleans, LA, USA, 5–8 June 2011; pp. 432–439. [Google Scholar]

- Bondarev, E.; Chaudron, M. A process for resolving performance trade-offs in component-based architectures. In International Symposium on Component-Based Software Engineering; Springer: Berlin/Heidelberg, Germany, 2006; pp. 254–269. [Google Scholar]

- Frank, S.; van Hoorn, A. SQuAT-Vis: Visualization and Interaction in Software Architecture Optimization. In European Conference on Software Architecture; Springer: Berlin/Heidelberg, Germany, 2020; pp. 107–119. [Google Scholar]

- Terzimehić, T. Optimization and reconfiguration of iec 61499-based software architectures. In Proceedings of the 21st ACM/IEEE International Conference on Model Driven Engineering Languages and Systems: Companion Proceedings, Copenhagen, Denmark, 14–19 October 2018; pp. 180–185. [Google Scholar]

- Waszecki, P.; Lukasiewycz, M.; Masrur, A.; Chakraborty, S. How to engineer tool-chains for automotive e/e architectures? ACM Sigbed Rev. 2013, 10, 6–15. [Google Scholar] [CrossRef]

- Fürst, S.; Mössinger, J.; Bunzel, S.; Weber, T.; Kirschke-Biller, F.; Heitkämper, P.; Kinkelin, G.; Nishikawa, K.; Lange, K. AUTOSAR–A Worldwide Standard is on the Road. In Proceedings of the 14th International VDI Congress Electronic Systems for Vehicles, Baden-Baden, Germany, 7–8 October 2009; Volume 62, p. 5. [Google Scholar]

- Vector. PREEvision. 2021. Available online: https://www.vector.com/de/en/products/products-a-z/software/preevision/#c1789 (accessed on 30 September 2021).

- Schäuffele, J. E/e Architectural Design and Optimization using Preevision; Technical Report; SAE Technical Paper; SAE: Warrendale, PA, USA, 2016. [Google Scholar]

- TTTechAuto. MotionWise. 2021. Available online: https://www.tttech-auto.com/products/safety-software-platform/motionwise (accessed on 20 October 2021).

- The Community for Open Innovation and Collaboration: The Eclipse Foundation. Available online: http://www.eclipse.org/ (accessed on 29 September 2021).

- Volcano Vehicle Systems Architect (VSA). Available online: https://www.mathworks.com/products/connections/product_detail/volcano-vehicle-systems-architect.html (accessed on 1 October 2021).

- ASCET-DEVELOPER. Available online: https://www.etas.com/en/products/ascet-developer.php (accessed on 25 September 2021).

- Simulation Toolset: Autosarbuilder—Dassault Systèmes. Available online: https://www.3ds.com/products-services/catia/products/autosar-builder/ (accessed on 9 October 2021).

- Simulation Toolset: Autosarbuilder. Available online: https://www.3ds.com/fileadmin/Welcome_to_AUTOSAR_Builder_2020x.pdf (accessed on 10 October 2021).

- Henia, R.; Hamann, A.; Jersak, M.; Racu, R.; Richter, K.; Ernst, R. System level performance analysis–the SymTA/S approach. IEE-Proc.-Comput. Digit. Tech. 2005, 152, 148–166. [Google Scholar] [CrossRef] [Green Version]

- Hamann, A.; Henia, R.; Racu, R.; Jersak, M.; Richter, K.; Ernst, R. Symta/s-symbolic timing analysis for systems. In Proceedings of the WIP Proc. Euromicro Conference on Real-Time Systems 2004 (ECRTS’04). Citeseer, Catania, Italy, 30 June–2 July 2004; pp. 17–20. [Google Scholar]

- Anssi, S.; Albers, K.; Dörfel, M.; Gérard, S. chronval/chronsim: A tool Suite for Timing Verification of Auto-Motive Applications. Embedded Real Time Software and Systems (ERTS2012). Available online: https://hal.archives-ouvertes.fr/hal-02191852/document (accessed on 20 December 2021).

- ChronVALWorst-Case Timing Analysis. 2021. Available online: https://www.inchron.com/chronval/ (accessed on 10 October 2021).

| E/E Configurator | Problem | Problem Attributes | Design Space Exploration |

|---|---|---|---|

| ArcheOpterix | Deployment and Mapping | Memory Consumption and Response time | Multi-Objective Optimization and Constraints Satisfaction |

| PerOpteryx | Software Clustering including Component/Resource Selection, Allocation, and Feature Configuration | Response time | Multi-Objective Optimization |

| MechatronicUML | Model Checking, Deployment, Formal Analysis of the Requirements, and the Design | Allocation Specification Language | Constraints Satisfaction |

| APP4MC | Mapping, Resource Management, Performance Simulation, and Validation | Task Response Time, Scheduling, and Partitioning focused on Timing | Multi-Objective Optimization and Constraints Satisfaction |

| Autofocus3 | Model Checking and Deployment | Schedule Synthesis and Latency | Optimization and Constraints Satisfaction |

| Clafer | Model Analysis and Feature Modelling | Timing | Multi-Objective Optimization and Constraints Satisfaction |

| OSATE | Model Analysis and Model Checking | Scheduling Analysis, End-to-End Latency, Safety Analysis, Computer Budget Analysis, and Weight Analysis | Constraints Satisfaction excluding DSE method |

| AAOL | Deployment and Mapping | Memory Usage, CPU Time, Network Bandwidth, and ASIL Level | Multi-Objective Optimization and Constraints Satisfaction |

| ASSIST | Deployment and Mapping | Redundancy, Scheduling, and Managing Shared Resources | Multi-Objective Optimization and Constraints Satisfaction |

| Deepcompass Framework | Model Analysis, Model Validation, and Mapping | Task Completion Latency and Missing Deadline in Scheduling | Multi-Objective Optimization and Constraints Satisfaction |

| SCALL | Software Component Allocation | Heterogeneous Components Allocation, Bandwidth, and Communication Cost | Constraints Satisfaction |

| AQOSA | Software Clustering and Mapping | Task Latencies, Processor Utilization, and Architecture Cost | Multi-Objective Optimization and Constraints Satisfaction |

| SQUAT | Software Clustering | Response Time | Multi-Objective Optimization and Constraints Satisfaction |

| E/E Configurator | Optimization Algorithms | Safety-Related Attributes | Optimization Attributes |

|---|---|---|---|

| ArcheOpterix | Genetic Algorithm (GA), ParetoAnt Colony Algorithm (P-ACO), Simulated Annealing (SA), Ayesian Heuristic for Component Deployment optimization (BHCDO), Random Search Algorithm, and Brute-Force Algorithms | Reliability | Cost, data transmission reliability and communication overhead |

| PerOpteryx | Genetic Algorithm (GA) | Reliability | Performance, Reliability, and Monetary Cost |

| MechatronicUML | Not Applicable (N.A.) | N.A. | N.A. |

| APP4MC | Genetic Algorithm (GA) | Safety parallelization and Traceability | Load Balancing, Energy Consumption, Memory Mapping, and Inter-Core Communication |

| Autofocus3 | Meta Search, e.g., Binary Search | Safety Integrity Level | Timing and Communication Load |

| Clafer | Guided Improvement Algorithm (GIA) Using Alloy, Z3 SMT, and Choco 3 CSP Solvers | N.A. | Mass, End-to-End Latency, and Cost |

| OSATE | N.A. | FTA, FMEA, and FHA | N.A. |

| AAOL | Evolutionary Algorithms | ASIL Level | Cost, Weight |

| ASSIST | Heuristic approach e.g., Simulated Annealing | Redundancy | Resource Usage, Weight, Power |

| Deepcompass Framework | Pareto approach | N.A. | Cost, Throughput, and Resource Utilization |

| SCALL | Genetic Algorithm (GA) | N.A. | N.A. |

| AQOSA | Nondominated Sorting Genetic Algorithm, Strength Pareto Evolutionary, and S-metric Selection | N.A. | Data Flow Latency, Architecture Cost, and Processor Usage |

| SQUAT | Genetic Algorithm (GA) | N.A. | Response Time and CPU Utilization |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Askaripoor, H.; Hashemi Farzaneh, M.; Knoll, A. E/E Architecture Synthesis: Challenges and Technologies. Electronics 2022, 11, 518. https://doi.org/10.3390/electronics11040518

Askaripoor H, Hashemi Farzaneh M, Knoll A. E/E Architecture Synthesis: Challenges and Technologies. Electronics. 2022; 11(4):518. https://doi.org/10.3390/electronics11040518

Chicago/Turabian StyleAskaripoor, Hadi, Morteza Hashemi Farzaneh, and Alois Knoll. 2022. "E/E Architecture Synthesis: Challenges and Technologies" Electronics 11, no. 4: 518. https://doi.org/10.3390/electronics11040518

APA StyleAskaripoor, H., Hashemi Farzaneh, M., & Knoll, A. (2022). E/E Architecture Synthesis: Challenges and Technologies. Electronics, 11(4), 518. https://doi.org/10.3390/electronics11040518