A Low-Power, Fast-Transient FVF-Based Output-Capacitorless LDO with Push–Pull Buffer and Adaptive Resistance Unit

Abstract

:1. Introduction

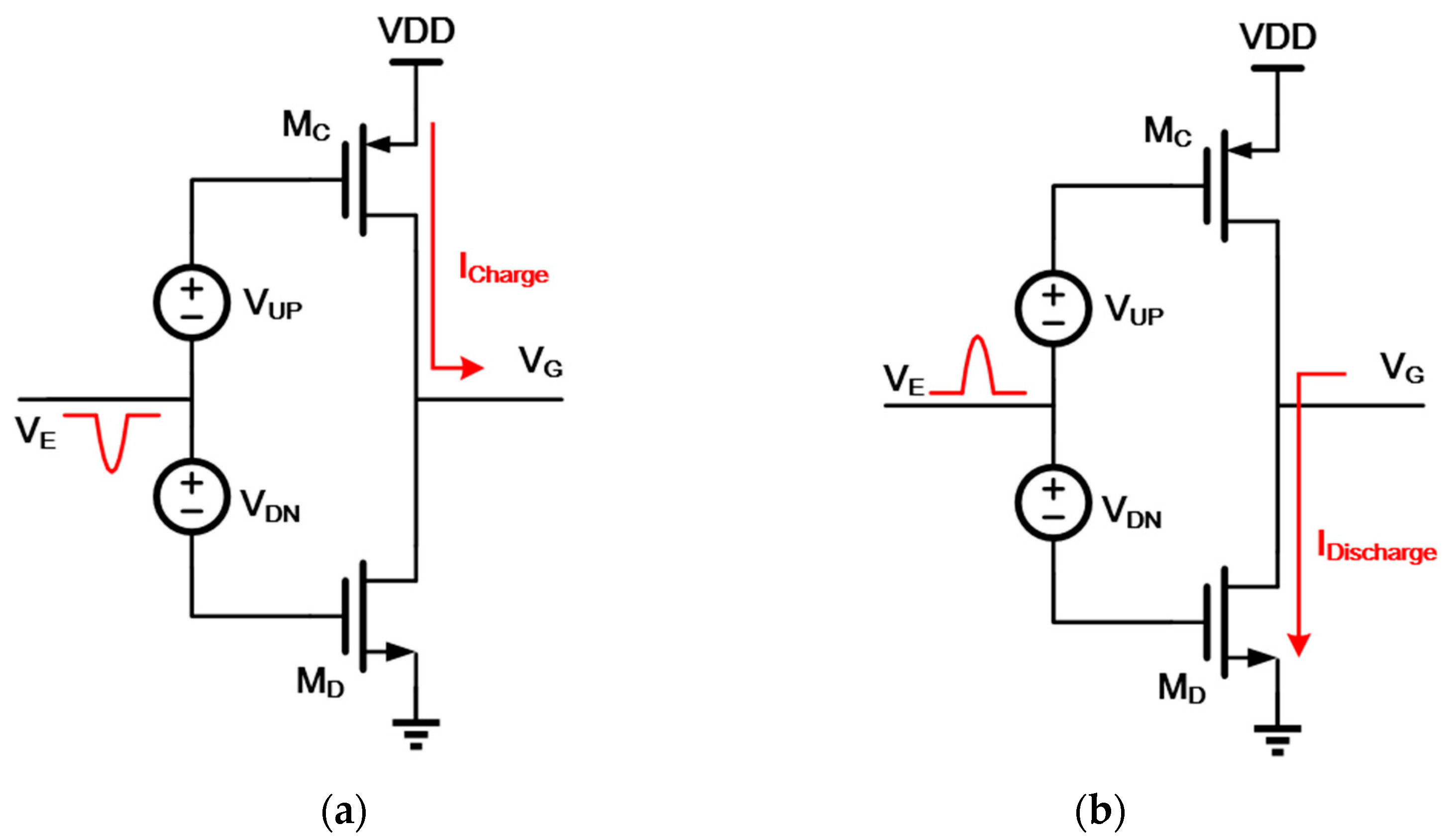

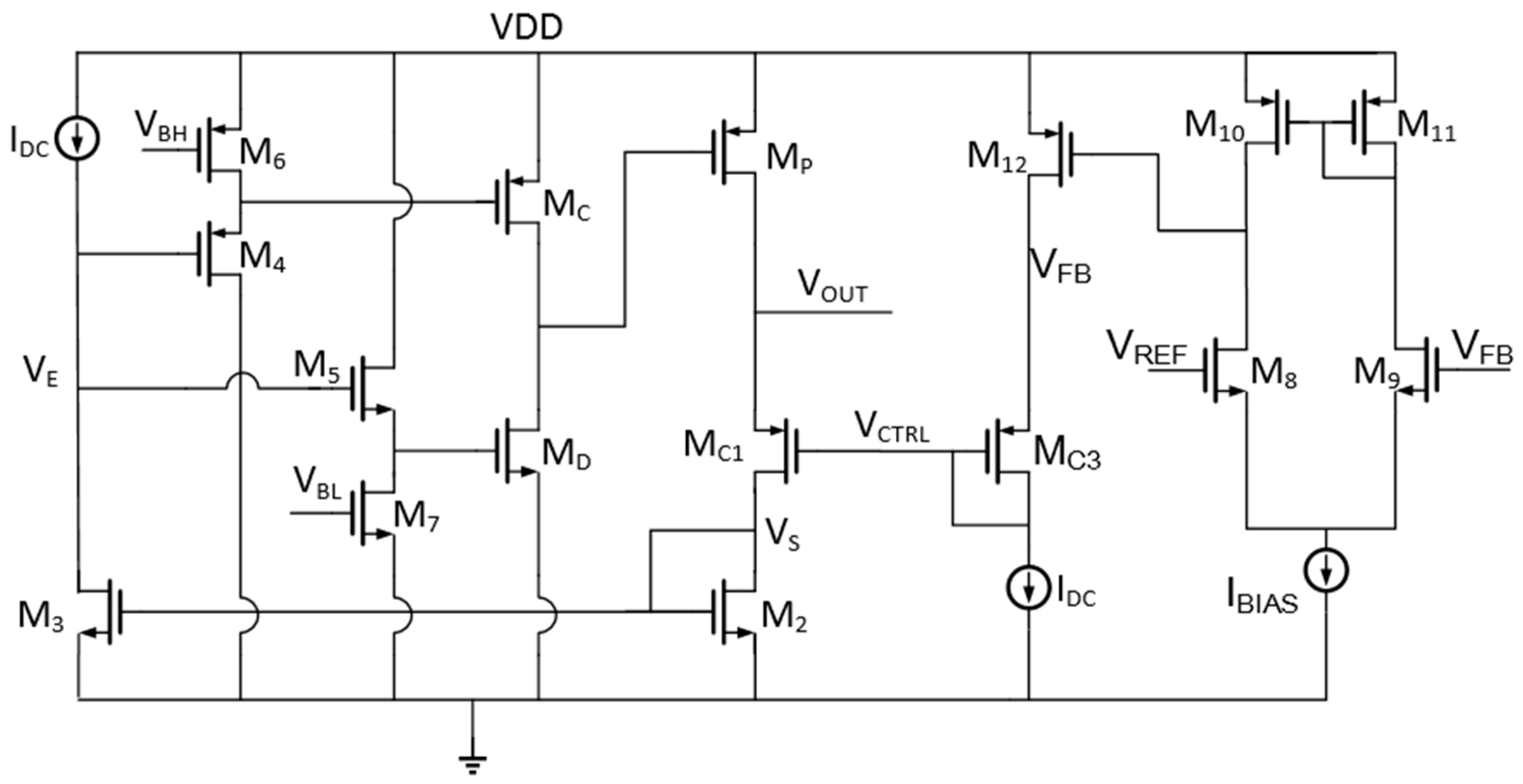

2. Optimization of Transient Response

2.1. FVF-Based OCL-LDO

2.2. FVF-Based OCL-LDO

2.3. LDO with the Push–Pull Buffer

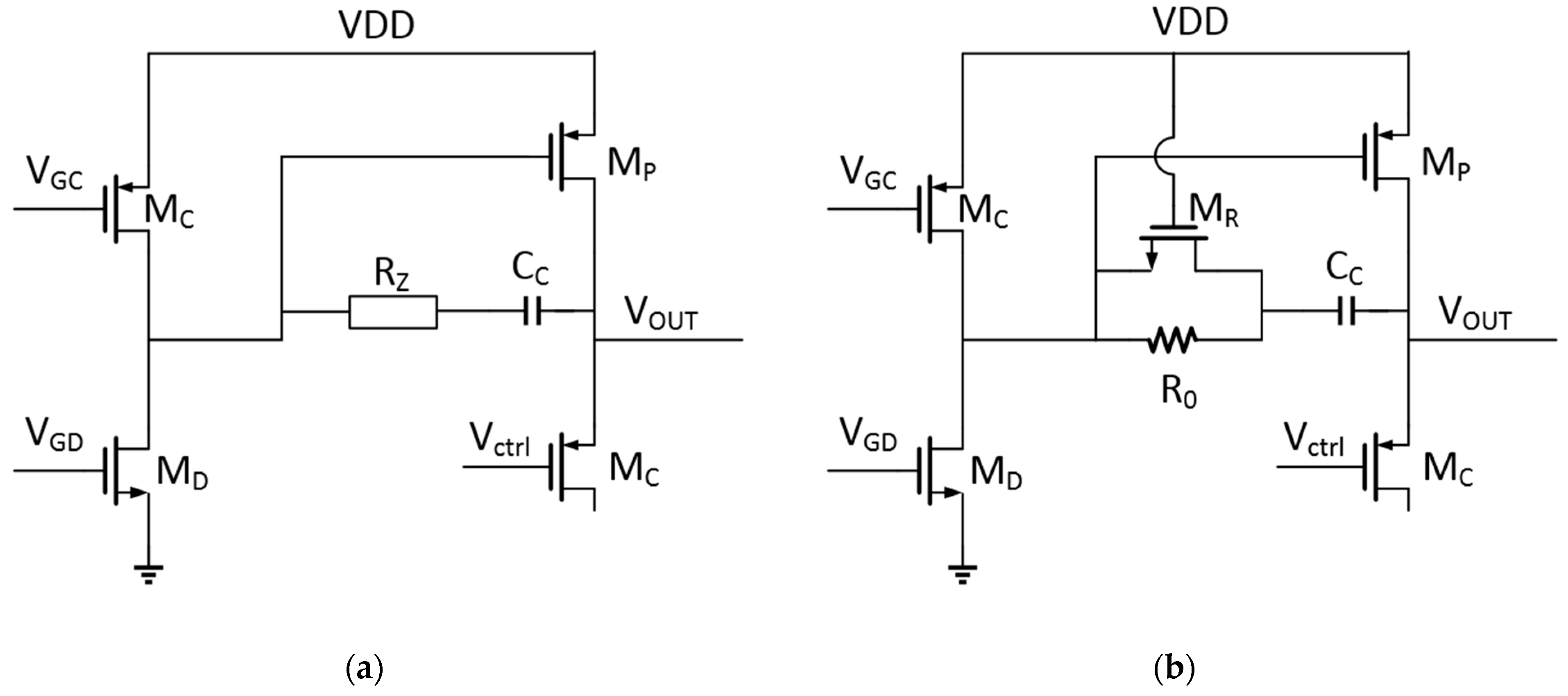

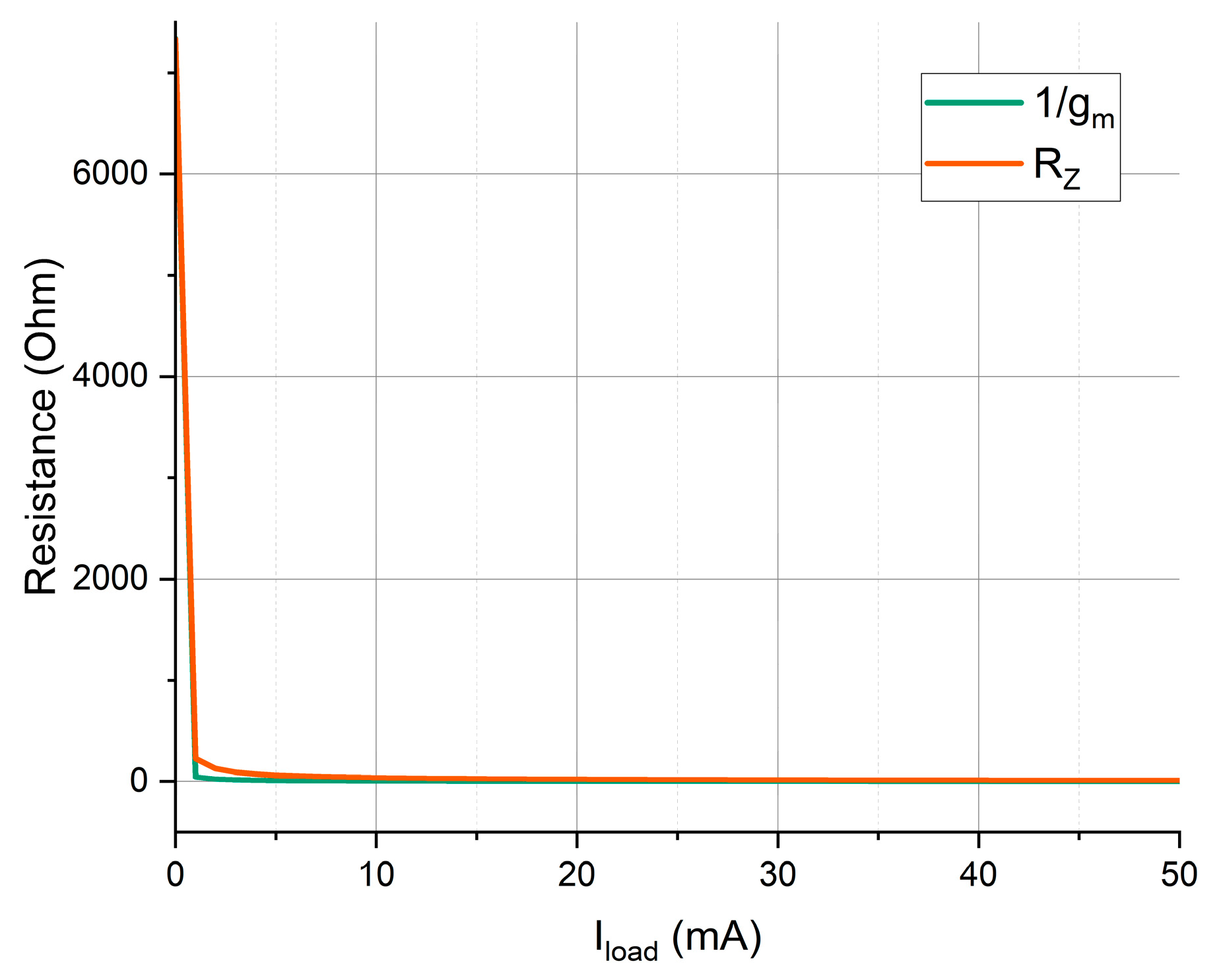

3. Optimization of Loop Stability

4. Simulation Result and Discussion

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Zhao, J.; Gao, Y.; Zhang, T.T.; Son, H.; Heng, C.H. A 310-nA Quiescent Current 3-fs-FoM Fully Integrated Capacitorless Time-Domain LDO with Event-Driven Charge Pump and Feedforward Transient Enhancement. IEEE J. Solid State Circuits 2021, 56, 2924–2933. [Google Scholar] [CrossRef]

- Park, C.J.; Onabajo, M.; Silva-Martinez, J. External Capacitor-Less Low Drop-Out Regulator With 25 dB Superior Power Supply Rejection in the 0.4–4 MHz Range. IEEE J. Solid State Circuits 2014, 49, 486–501. [Google Scholar] [CrossRef]

- Lu, Y.; Wang, Y.; Pan, Q.; Ki, W.H.; Yue, C.P. A Fully-Integrated Low-Dropout Regulator With Full-Spectrum Power Supply Rejection. IEEE Trans. Circuits Syst. I Regul. Pap. 2015, 62, 707–716. [Google Scholar] [CrossRef]

- Chong, S.; Chan, P.K. A 0.9-/spl mu/A Quiescent Current Output-Capacitorless LDO Regulator with Adaptive Power Transistors in 65-nm CMOS. IEEE Trans. Circuits Syst. I Regul. Pap. 2013, 60, 1072–1081. [Google Scholar] [CrossRef]

- Torres, J.; El-Nozahi, M.; Amer, A.; Gopalraju, S.; Abdullah, R.; Entesari, K.; Sanchez-Sinencio, E. Low Drop-Out Voltage Regulators: Capacitor-less Architecture Comparison. IEEE Circuits Syst. Mag. 2014, 14, 6–26. [Google Scholar] [CrossRef]

- Sularea, I.; Răducan, C.; Neag, M. A Capacitor-Less LDO with High PSR over a Wide Frequency Range. In Proceedings of the 2021 International Semiconductor Conference (CAS), Sinaia, Romania, 6–8 October 2021; pp. 213–216. [Google Scholar]

- Li, R.; Zhang, X.; Zeng, Y.; Lin, Y.; Yang, J.; Tan, H.Z. High PSR Output-Capacitor-Less LDO with Double Buffers Technique. In Proceedings of the 2020 27th IEEE International Conference on Electronics, Glasgow, UK, 23–25 November; Circuits and Systems (ICECS): Glasgow, UK, 2020; pp. 1–4. [Google Scholar]

- Leo, C.J.; Raja, M.K.; Minkyu, J. An ultra low-power capacitor-less LDO with high PSR. In Proceedings of the 2013 IEEE MTT-S International Microwave Workshop Series on RF and Wireless Technologies for Biomedical and Healthcare Applications (IMWS-BIO), Singapore, 9–11 December 2013; pp. 1–3. [Google Scholar]

- Lim, Y.; Lee, J.; Lee, Y.; Song, S.-S.; Kim, H.-T.; Lee, O.; Choi, J. An External Capacitor-Less Ultralow-Dropout Regulator Using a Loop-Gain Stabilizing Technique for High Power-Supply Rejection Over a Wide Range of Load Current. IEEE Trans. Very Large Scale Integr. VLSI Syst. 2017, 25, 3006–3018. [Google Scholar] [CrossRef]

- Hazucha, P.; Karnik, T.; Bloechel, B.A.; Parsons, C.; Finan, D.; Borkar, S. Area-efficient linear regulator with ultra-fast load regulation. IEEE J. Solid State Circuits 2005, 40, 933–940. [Google Scholar] [CrossRef]

- Liu, X.; Krishnamurthy, H.K.; Na, T.; Weng, S.; Ahmed, K.Z.; Schaef, C.; Ravichandran, K.; Tschanz, J.W.; De, V. A Universal Modular Hybrid LDO With Fast Load Transient Response and Programmable PSRR in 14-nm CMOS Featuring Dynamic Clamp Strength Tuning. IEEE J. Solid State Circuits 2021, 56, 2402–2415. [Google Scholar] [CrossRef]

- Lu, Y.; Ki, W.H.; Yue, C.P. A 0.65ns-response-time 3.01ps FOM fully-integrated low-dropout regulator with full-spectrum power-supply-rejection for wideband communication systems. In Proceedings of the 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 9–13 February 2014; pp. 306–307. [Google Scholar]

- Duong, Q.H.; Kong, J.-W.; Shin, H.-S.; Nguyen, H.-H.; Kim, P.-J.; Ko, Y.-S.; Yu, H.-Y.; Park, H.-J. Multiple-Loop Design Technique for High-Performance Low-Dropout Regulator. IEEE J. Solid State Circuits 2017, 52, 2533–2549. [Google Scholar] [CrossRef]

- Magod, R.; Bakkaloglu, B.; Manandhar, S. A 1.24 uA Quiescent Current NMOS Low Dropout Regulator with Integrated Low-Power Oscillator-Driven Charge-Pump and Switched-Capacitor Pole Tracking Compensation. IEEE J. Solid State Circuits 2018, 53, 2356–2367. [Google Scholar] [CrossRef]

- Al-Shyoukh, M.; Lee, H.; Perez, R. A Transient-Enhanced Low-Quiescent Current Low-Dropout Regulator with Buffer Impedance Attenuation. IEEE J. Solid State Circuits 2007, 42, 1732–1742. [Google Scholar] [CrossRef] [Green Version]

- Ho, M.; Mak, K.L.; Leung, K.N. A Low-Power Fast-Transient 90-nm Low-Dropout Regulator with Multiple Small-Gain Stages. IEEE J. Solid State Circuits 2010, 45, 2466–2475. [Google Scholar]

- Li, R.; Zeng, Y.; Lin, Y.; Yang, J.; Tan, H.-z. High-PSR and fast-transient LDO regulator with nested adaptive FVF structure. In Proceedings of the 2020 IEEE International Conference on Integrated Circuits, Technologies and Applications (ICTA), Nanjing, China, 23–25 November 2020; pp. 51–52. [Google Scholar]

- Huang, M.; Feng, H.; Lu, Y. A Fully Integrated FVF-Based Low-Dropout Regulator with Wide Load Capacitance and Current Ranges. IEEE Trans. Power Electron. 2019, 34, 11880–11888. [Google Scholar] [CrossRef]

- Guo, J.; Leung, K.N. A 6µW Chip-Area-Efficient Output-Capacitorless LDO in 90-nm CMOS Technology. IEEE J. Solid State Circuits 2010, 45, 1896–1905. [Google Scholar] [CrossRef]

- Man, T.Y.; Leung, K.N.; Leung, C.Y.; Mok, P.K.T.; Chan, M. Development of Single-Transistor-Control LDO Based on Flipped Voltage Follower for SoC. IEEE Trans. Circuits Syst. I Regul. Pap. 2008, 55, 1392–1401. [Google Scholar] [CrossRef] [Green Version]

- Or, P.Y.; Leung, K.N. An Output-Capacitorless Low-Dropout Regulator with Direct Voltage-Spike Detection. IEEE J. Solid State Circuits 2010, 45, 458–466. [Google Scholar] [CrossRef]

- Cai, G.; Lu, Y.; Zhan, C.; Martins, R.P. A Fully Integrated FVF LDO With Enhanced Full-Spectrum Power Supply Rejection. IEEE Trans. Power Electron. 2021, 36, 4326–4337. [Google Scholar] [CrossRef]

- Lam, Y.H.; Ki, W.H. A 0.9V 0.35 µm Adaptively Biased CMOS LDO Regulator with Fast Transient Response. In Proceedings of the 2008 IEEE International Solid-State Circuits Conference—Digest of Technical Papers, San Francisco, CA, USA, 3–7 February 2008; pp. 442–626. [Google Scholar]

- Rincon-Mora, G.A.; Allen, P. A low-voltage, low quiescent current, low drop-out regulator. IEEE J. Solid State Circuits 1998, 33, 36–44. [Google Scholar] [CrossRef] [Green Version]

- Ramirez-Angulo, J.; Carvajal, R.G.; Torralba, A.; Galan, J.; Vega-Leal, A.P.; Tombs, J. The flipped voltage follower: A useful cell for low-voltage low-power circuit design. In Proceedings of the 2002 IEEE International Symposium on Circuits and Systems. Proceedings (Cat. No.02CH37353), Phoenix-Scottsdale, AZ, USA, 26–29 May 2002; p. III. [Google Scholar]

- Kwok, K.C.; Mok, P.K.T. Pole-zero tracking frequency compensation for low dropout regulator. In Proceedings of the 2002 IEEE International Symposium on Circuits and Systems (ISCAS), Phoenix-Scottsdale, AZ, USA, 26–29 May 2002; p. IV. [Google Scholar]

- Milliken, R.J.; Silva-Martinez, J.; Sanchez-Sinencio, E. Full On-Chip CMOS Low-Dropout Voltage Regulator. IEEE Trans. Circuits Syst. I Regul. Pap. 2007, 54, 1879–1890. [Google Scholar] [CrossRef]

- Ho, E.N.Y.; Mok, P.K.T. Wide-Loading-Range Fully Integrated LDR With a Power-Supply Ripple Injection Filter. IEEE Trans. Circuits Syst. II Express Briefs 2012, 59, 356–360. [Google Scholar] [CrossRef]

- Li, G.; Qian, H.; Guo, J.; Mo, B.; Lu, Y.; Chen, D. Dual Active-Feedback Frequency Compensation for Output-Capacitorless LDO with Transient and Stability Enhancement in 65-nm CMOS. IEEE Trans. Power Electron. 2020, 35, 415–429. [Google Scholar] [CrossRef]

- Yang, F.; Mok, P.K.T. A 65nm inverter-based low-dropout regulator with rail-to-rail regulation and over −20dB PSR at 0.2V lowest supply voltage. In Proceedings of the 2017 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 5–9 February 2017; pp. 106–107. [Google Scholar]

| [27] | [28] | [2] | [4] | [29] | [30] | This Work | |

|---|---|---|---|---|---|---|---|

| Year | 2007 | 2012 | 2014 | 2012 | 2020 | 2017 | 2023 |

| Technology (nm) | 350 | 130 | 180 | 65 | 65 | 65 | 180 |

| Chip Area (mm2) | 0.12 | 0.018 | 0.14 | 0.017 | 0.0105 | 0.016 | 0.046 |

| Input Voltage (V) | 3 | 1.2 | 1.8 | 1.2 | 0.95–1.2 | 0.6 | 1.8 |

| Maximum Output Current (mA) | 50 | 50 | 50 | 100 | 100 | 50 | 50 |

| Quiescent Current (µA) | 65 | 37.32 | 55 | 0.9–82.4 | 14 | 32 | 16.1 |

| Current Efficiency (%) | 99.87 | 99.93 | 99.89 | 99.99 | 99.99 | 99.94 | 99.97 |

| On-chip Capacitor (pF) | 23 | 21 | 28 | 4.5 | 6 | 40 | 50 |

| Off-chip Capacitor (pF) | 100 | 20 | 100 | 0–100 | 100 | 40 | 0–1000 |

| Settling Time (µs) | 15 | 0.4 | 6 | 6 | 3.2 | N/A | 0.2 |

| FOM (ps) | 0.233 | 0.017 | 0.264 | 0.056 | 0.0322 | 0.137 | 0.0415 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Li, Y.; Wang, L.; Wang, Y.; Wang, S.; Cui, M.; Guo, M. A Low-Power, Fast-Transient FVF-Based Output-Capacitorless LDO with Push–Pull Buffer and Adaptive Resistance Unit. Electronics 2023, 12, 1285. https://doi.org/10.3390/electronics12061285

Li Y, Wang L, Wang Y, Wang S, Cui M, Guo M. A Low-Power, Fast-Transient FVF-Based Output-Capacitorless LDO with Push–Pull Buffer and Adaptive Resistance Unit. Electronics. 2023; 12(6):1285. https://doi.org/10.3390/electronics12061285

Chicago/Turabian StyleLi, Yuanzhe, Lixin Wang, Yue Wang, Shixin Wang, Mengyao Cui, and Min Guo. 2023. "A Low-Power, Fast-Transient FVF-Based Output-Capacitorless LDO with Push–Pull Buffer and Adaptive Resistance Unit" Electronics 12, no. 6: 1285. https://doi.org/10.3390/electronics12061285