Chip Implementation with a Combined Wireless Temperature Sensor and Reference Devices Based on the DZTC Principle

Abstract

: This paper presents a novel CMOS wireless temperature sensor design in order to improve the sensitivity and linearity of our previous work on such devices. Based on the principle of CMOS double zero temperature coefficient (DZTC) points, a combined device is first created at the chip level with two voltage references, one current reference, and one temperature sensor. It was successfully fabricated using the 0.35 μm CMOS process. According to the chip results in a wide temperature range from −20 °C to 120 °C, two voltage references can provide temperature-stable outputs of 823 mV and 1,265 mV with maximum deviations of 0.2 mV and 8.9 mV, respectively. The result for the current reference gives a measurement of 23.5 μA, with a maximum deviation of 1.2 μA. The measurements also show that the wireless temperature sensor has good sensitivity of 9.55 mV/°C and high linearity of 97%. The proposed temperature sensor has 4.15-times better sensitivity than the previous design. Moreover, to facilitate temperature data collection, standard wireless data transmission is chosen; therefore, an 8-bit successive-approximation-register (SAR) analog-to-digital converter (ADC) and a 433 MHz wireless transmitter are also integrated in this chip. Sensing data from different places can be collected remotely avoiding the need for complex wire lines.1. Introduction

Reference devices, such as voltage and/or current references, are key elements in many mixed-signal and analog applications. They are required to be stable throughout the process and to not be susceptible to power supply voltage, and temperature variations. In particular, in the system-on-a-chip (SoC) era, millions of transistors greatly increase the power dissipation. A chip with a built-in temperature sensor increases the system’s reliability by predicting fatal faults caused by excessive chip temperature. That means if the chip temperature is over the limit, the sensor can signal the chip power management unit to enter into the power-saving mode or give a warning.

With the rapid evolution of CMOS technology, CMOS bandgap references were developed [1,2], but only parasitic bipolar junction transistors (BJTs) can be used. Lakdawala [3] used the ratio of currents driven into a BJT pair with current chopping to up-convert the temperature signal and cancel the effects of parasitic resistance. For full CMOS voltage references, Najafizadeh [4] used the proportional to the absolute temperature (PTAT) current source to bias a diode-connected transistor to achieve a temperature-independent voltage reference, but there were no chip results to justify the claims. The M3 transistor suffers from a body effect because its source terminal is connected to a resistor. Zito [5] also used the PTAT sensing element to detect different emitter currents, but the device can only measure temperatures ranging from 20 °C to 100 °C. Smart temperature sensors [6–8] based on parasitic bipolar transistors display inaccuracies as low as a few tenths of a degree over the military temperature range, i.e., from −55 °C to 125 °C, but require a one-point trim. Another way [9] was to bias a diode-connected transistor at a zero temperature coefficient (ZTC) point by using a constant current, but the realization of a temperature-independent current source was difficult. Although the combined design of the voltage reference and the temperature sensor was proposed in [10], only simulation results were available. In our previous design [11], based on the CMOS PTAT principle, a combined device for voltage reference and temperature sensors was successfully implemented using a fully digital process. For the temperature range from 20 °C to 120 °C, the experimental results showed that the voltage reference has a temperature stable output of 717 mV and the associated temperature sensor has the sensitivity of 2.3 mV/°C with linearity up to 95%. In order to improve the measurement range, linearity, and sensitivity of our previous design using the PTAT principle, a new DZTC-based temperature sensor design is proposed for performance enhancement. According to the chip results, the new design [12] can achieves better sensitivity and linearity than the one described in our previous work. For standalone applications, the device gives an analog output and provides digital output with embedded successive-approximation-register (SAR) analog-to-digital converter (ADC).

Here, a novel CMOS wireless temperature sensor is designed in order to improve the sensitivity and linearity of our previous design. Based on the principle of CMOS DZTC points, a combined device is first created at the chip level with two voltage references, one current reference, and one temperature sensor. In addition, with the integrated wireless transmitter, sensing temperature data from the chip can be transmitted to a data collector through a standard wireless approach.

This paper is organized as follows: Section 2 describes the system architecture. Section 3 introduces the circuit design of the proposed wireless temperature sensor. The experimental results are presented in Section 4. Finally, conclusions are given in Section 5.

2. System Architecture

A block diagram of the proposed architecture is given in Figure 1. The architecture is mainly divided into four parts: the temperature sensor, 8-bit SAR ADC, on-off keying (OOK) transmitter, and the regulator. The temperature sensor block consists of two voltage references, one current reference, and one temperature sensor. During operation, the surrounding temperature is converted into a voltage signal by the temperature sensor. Subsequently, the magnitude of the voltage signal is converted into serial digital data in an RS-232 format by an 8-bit SAR ADC, and then is wirelessly transmitted by the 433 MHz OOK transmitter. Finally, the data collectors, such as laptops and personal digital assistants (PDAs), can acquire and store immediate data through the developed wireless receiver module. In addition, data analysis can also be carried out by the software.

3. Circuit Design

3.1. Temperature Sensor

A. ZTC Point

Considering a diode-connected NMOS transistor exactly biased at the ZTC point with a constant drain current ID,ZTC for T = T0, its gate-source voltage can be written as:

Let the gate-source voltage of Equation (2) be independent of temperature, and differentiate VGS(T) with respect to T and assume UTE is exactly equal to −2. Then it is easy to prove the following identity for all T:

The typical value of parameter UTE, is −1.5. However, in modern technologies, UTE = −2 is achievable for n-channel devices by adjusting the dopant concentrations of NA and ND [4]. The I-V curve for a diode-connected NMOS with UTE = −2 exists at a unique ZTC point, but for UTE = −1.5, there is no common intersection point. It exists in a bottleneck only.

B. Double ZTC Voltage and Current Reference

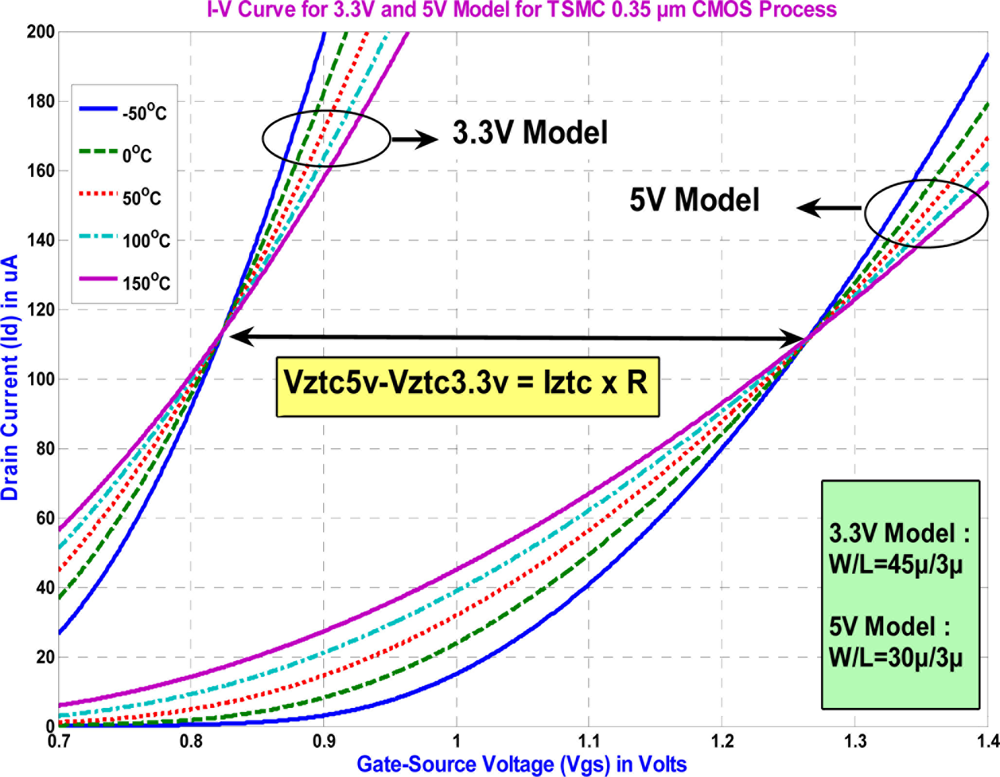

TSMC 0.35 μm CMOS technology not only provides the 3.3 V transistor model with thin gate-oxide, but also gives the 5 V transistor model with thick gate-oxide. If both can have their UTE at about −2, there exist two unique ZTC points simultaneously. One is for the 3.3 V model and the other is for the 5 V model, as shown in Figure 2.

Fortunately, the NMOS models, for the channel length and width in the range of 12 μm ≤ (L,W) ≤ 20 μm, read UTE = − 2.06 for the 3.3 V model, and UTE = − 1.82 for the 5 V model. Both ZTC points are shown in Figure 2. Using these two ZTC points, the DZTC voltage and current references can be designed for temperature independency. Assuming that the resistor, R, is less sensitive with respect to temperature, the IR drop equals the difference of both ZTC voltages:

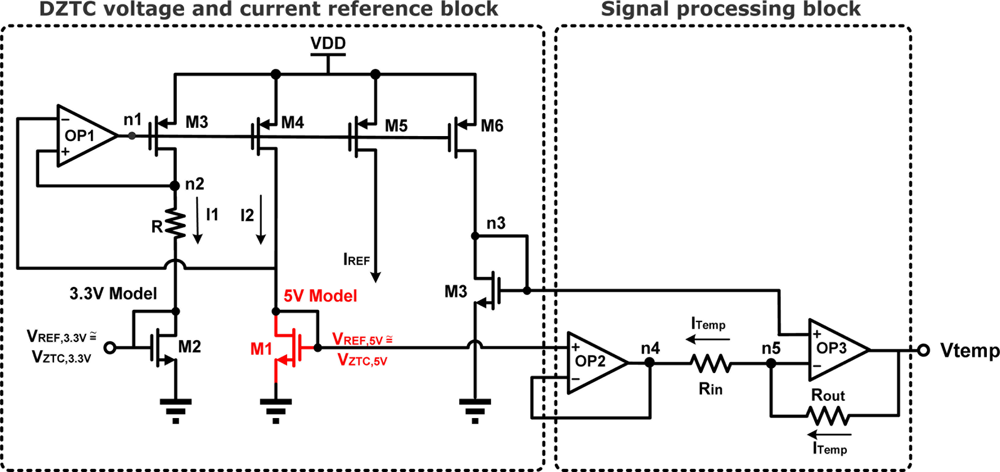

The left portion of the block shown in Figure 3 is utilized to realize the concept of DZTC voltage and current references. In this block, all transistors use the 3.3 V CMOS model, except M1 which uses the 5 V model. To improve the circuit stability, the operational amplifier OP1 in Figure 3 must provide a sufficient stability margin. It uses folded-cascode topology and provides about a 52 dB gain, a 2 MHz gain-bandwidth, and an 87° phase margin. Since both nodes of n2 and VREF,5V are connected to the inputs of OP1, they have the same voltage. The output of OP1 adjusts the current to suitably bias the transistors of M1 and M2 at their ZTC points according to the relationship of Equation (4). The output voltage for M1 is denoted as VREF,5V with a value of about VZTC,5V, and for M2 as VREF,3.3V with a value of about VZTC,3.3V. For the resistor, R, with less temperature sensitivity, the topology gives two reference voltages and a temperature-invariant current source. All of these are temperature-invariant.

C. Sensitivity Enhancement of Temperature Sensor

The right portion of the block shown in Figure 3 is used to realize the temperature sensor. The temperature information is obtained from nodes n3 and VREF,5V in Figure 3. A unity-gain buffer, OP2, is utilized for isolation purposes. The other OP3 is used to amplify the signal and to improve the linearity with respect to temperature. Assume the open-loop gains of OP2 and OP3 are infinite. The closed-loop gain arising from OP3 becomes:

The sensitivity of the temperature sensor is calculated by:

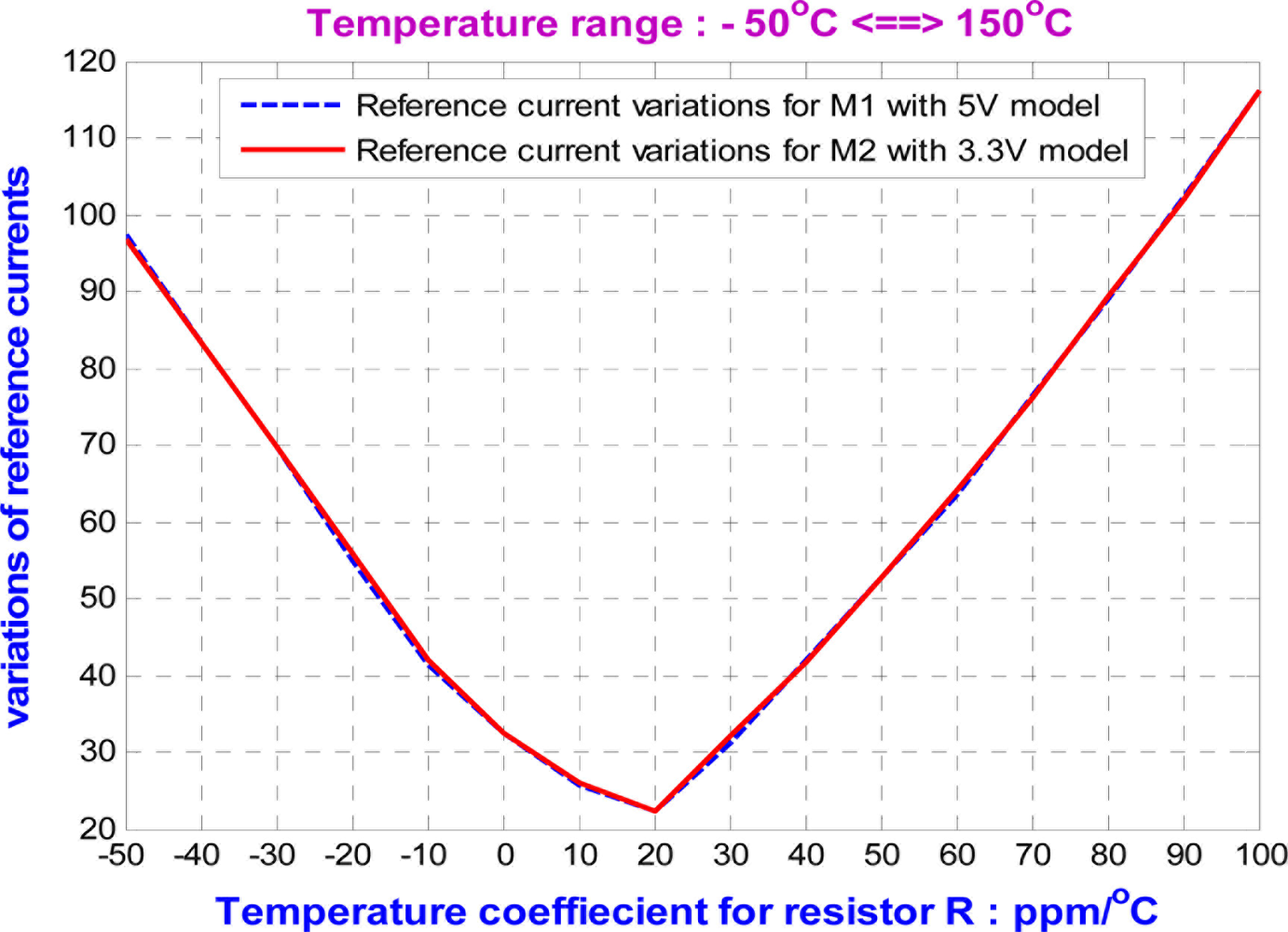

D. Temperature Variation of the Resistor

The temperature variation of the resistor, R, has an influence on the stability of the DZTC voltage and current references for wide temperature operations. Sweeping the temperature variations of the resistor, R, from −50 ppm/°C to 100 ppm/°C, both output reference voltages show temperature variations of less than 30 ppm/°C, as shown in Figure 4. Furthermore, the reference current source keeps the temperature variation below 120 ppm/°C, as shown in Figure 5. Obviously, the voltage reference is more stable than the current reference for large temperature variations of the resistor, R. In fact, if the temperature variation of the resistor, R, is small, the DZTC voltage and current references provide a reference current source and two reference voltages with very low temperature dependency.

The accuracy of the proposed DZTC voltage and current references depend on the temperature variation of the resistor, R. Fortunately, some commercial resistor products with low temperature coefficient can be obtained, such as the metal film resistor possibly achieving temperature coefficients of 10 ppm/°C. For applications, this design can use off-chip connection of the metal film resistor to achieve highly temperature-independent voltage and current references.

E. Monte Carlo Analysis

In Monte Carlo analysis, we assume that the W/L ratio of M1 and M2 in Figure 3 has a Gaussian distribution with 10% and three sigma process variations and 1,000 sample points. According to the simulation results, two voltage references can provide temperature-stable outputs of 818.67 mV and 1,244.83 mV with maximum deviations of 1.9 mV and 19.3 mV, respectively, as shown in Figure 6(a,b). Figure 6(c,d) shows the measured voltage reference points for each of the 1,000 sample points of the Monte Carlo run. The yield analysis of the voltage references for 3.3 V model indicates that 97.3% of the device samples will have a voltage reference within the required limit of the nominal value ±5 mV. The yield analysis of the voltage references for the 5 V model indicates that 98.9% of the device samples will have a voltage reference within the required limit of the nominal value ±50 mV.

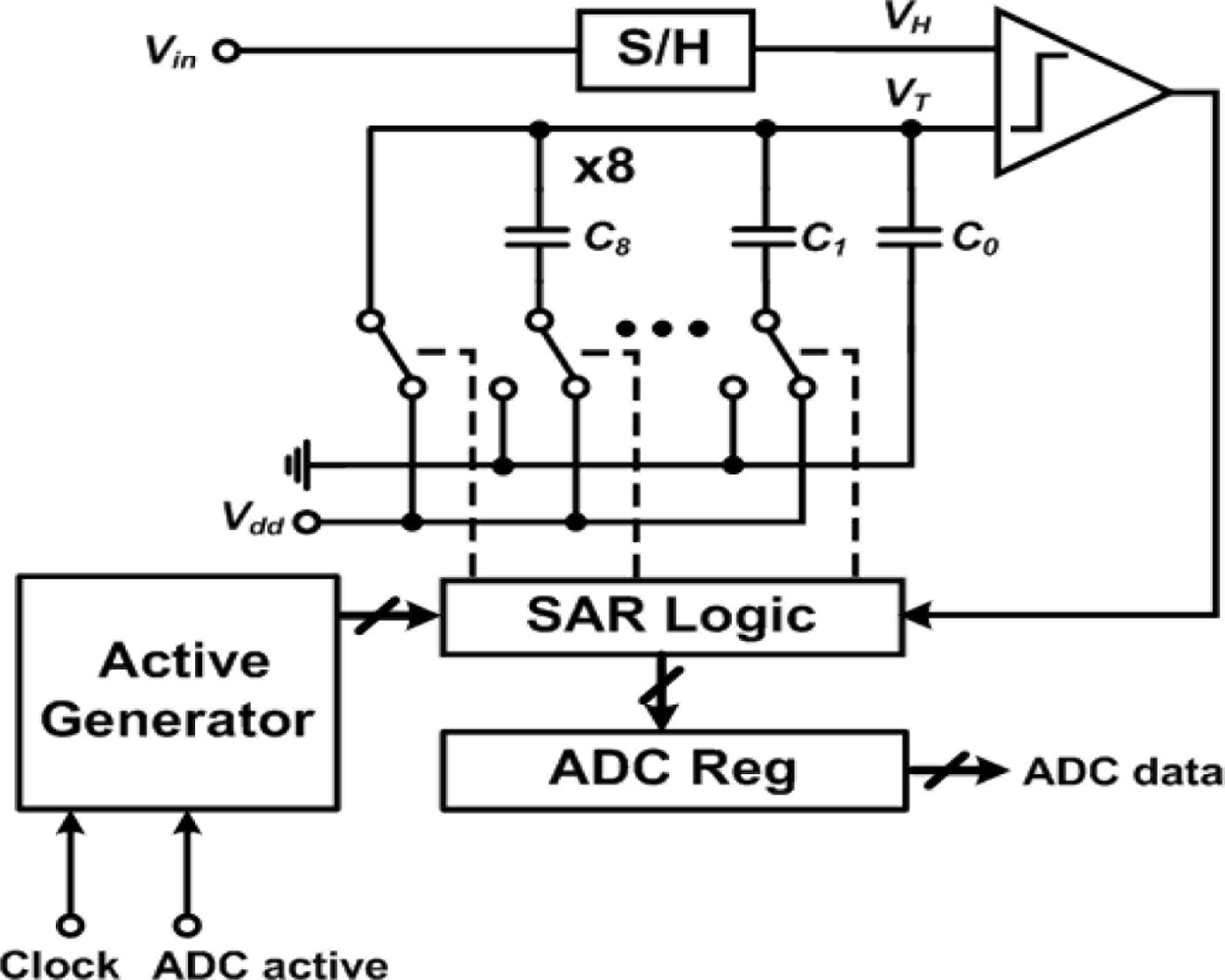

3.2. Successive-Approximation-Register ADC (SAR ADC)

Since the rate of temperature change is relatively slow, the SAR ADC is chosen for its lower area and the good ratio of speed/power [14]. Figure 7 shows the architecture of the SAR ADC that comprises a sample and hold (S/H), a comparator, a register array, a logic controller, and a binary-weighted capacitor array as a digital-to-analog converter (DAC) where C8 = 2C7, C7 = 2C6…, C2 = 2C1, and C1=C0. This ADC works as follows: first, the SAR sets the capacitor array to its middle scale (100…00) so that the output voltage VT of the DAC is VDD/2. Then the comparator compares the sample-and-hold (S/H) voltage VH with VT to determine whether the current setting is larger or smaller than VH. If VH > VT, the most significant bit (MSB) of SAR stays at logic 1, whereas if VH < VT, the MSB of SAR is set to logic 0. After the first bit is determined, the next bit is set to logic 1 (110…00 or 010…00), and the same procedure is repeated to determine the next bit. The sequence will be repeated eight times until all the bits are set.

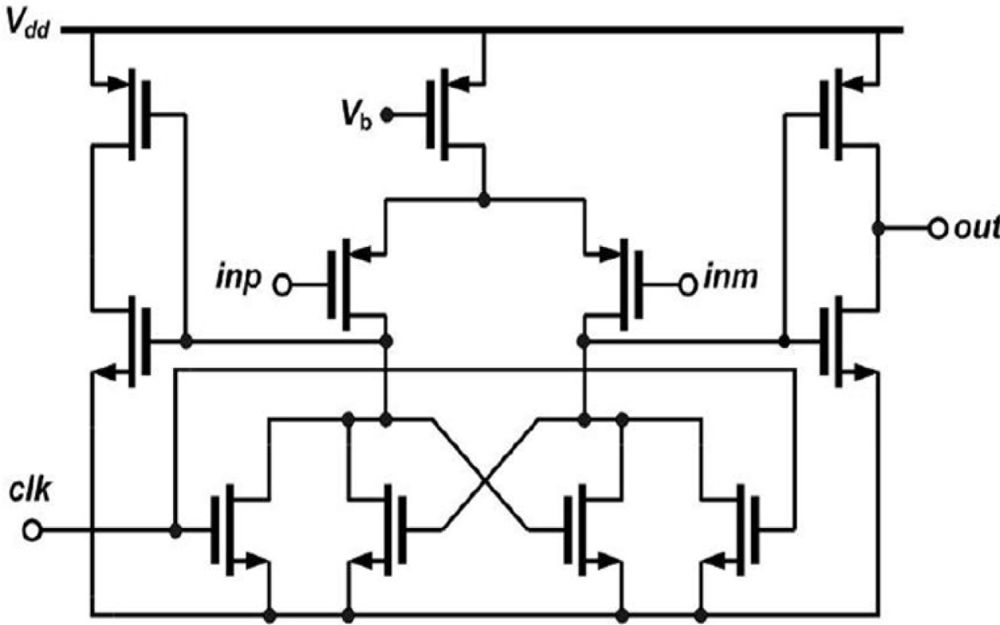

In order to lower the power consumption, the comparator used in this successive approximation ADC is a simple regenerative resettable comparator [15] followed by inverters for full-swing signal recovery, whose schematic is depicted in Figure 8. The comparator will be reset when the clock is high, while it will compare the DAC output voltage and input voltage when the clock is turned to low. Since the mismatch in the capacitance will seriously degrade the performance of the ADC, the capacitor array is arranged in the common-centroid configuration by using a relatively large unit capacitor of 400 fF. This ADC adopts a front-end passive S/H circuit composed of two switches and one capacitor (CH). The speed of the S/H circuit depends on the on-state channel-resistance (Ron) of the switches, and the capacitance of CH. Since high-speed operation (or very small time constant) is unnecessary in this work, a relatively large CH of 21 pF (obtained by laying out as many capacitors as possible out of the available space) is adopted to reduce the conversion error. No power is dissipated in the S/H circuit due to its passive structure. The SAR is performed by the static CMOS logic circuit, which also generates the control signals such as the reset clock for the comparator and the sample clock for the S/H. The eventual digitized data converted by the ADC are stored in ADC registers.

3.3. On-Off Keying (OOK) Transmitter

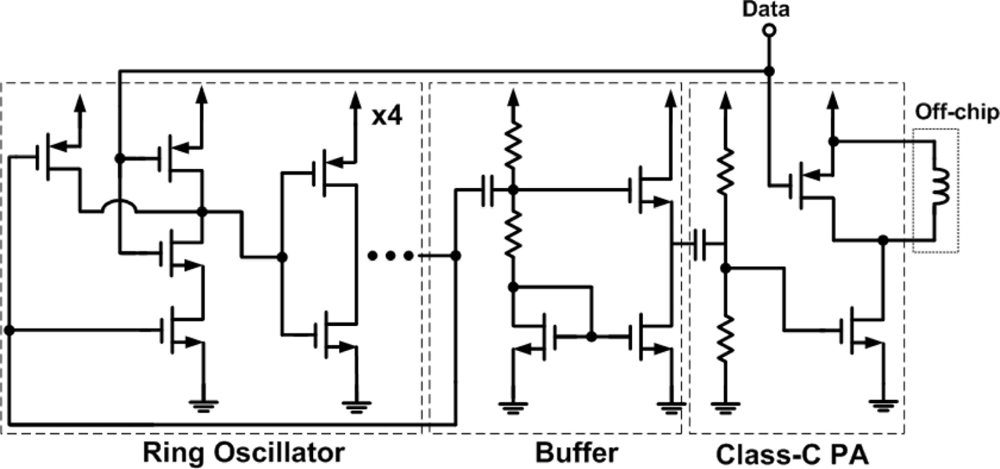

In this work, the OOK modulation scheme was chosen for high throughput and high energy efficiency [16]. The circuit schematic of the OOK transmitter is depicted in Figure 9. It is composed of a ring-oscillator, a buffer (source follower), and a class-C power amplifier. The 433 MHz carrier signal is generated by the ring oscillator and the on-off keying modulation is achieved by turning the ring oscillator on and off. The Class-C power amplifier, consisting of an off-chip surface-mounted-device inductor, a large n-MOSFET, and a p-MOSFET switch, drives a sinusoidal current through the surface-mounted-device inductor, and in conjunction with the parasitic capacitance of the transistors/die pads to achieve a narrow band-pass frequency response in power amplifier. To prevent the data-rate degradation, a p-MOSFET switch is parallel-connected to the inductor, which accelerates the voltage decline at the output when the input signal changes from logic one to logic zero [17].

However, the oscillation frequency of this ring oscillator is very sensitive to temperature variation. As shown in Figure 10, the carrier center wavelength will change from 6.64 cm to 8.83 cm when the temperature varies from 0 °C to 120 °C. It is undoubtedly a big problem when applying this transmitter in wide-range temperature sensing application. Therefore, to overcome this problem, an off-chip phase locked loop (PLL) is replaced with the on-chip ring oscillator to provide a stable 433 MHz oscillation carrier in this phase. In the next version, a PLL circuit will be further integrated into this temperature chip.

3.4. Regulator

In our integrated wireless system, to prevent interference between each circuit block through the power line, several reference voltages and separate power supply sources are required. For example, we need a common mode voltage for the amplifier, a clean voltage source for the OOK transmitter and separate power supplies for the analog and digital circuits respectively, etc. Therefore, a circuit that can provide tunable voltage and enough driving ability is necessary in our design. Besides, a stable temperature-independent voltage supply circuit is essential because this temperature sensing system may operate in wide range of temperatures.

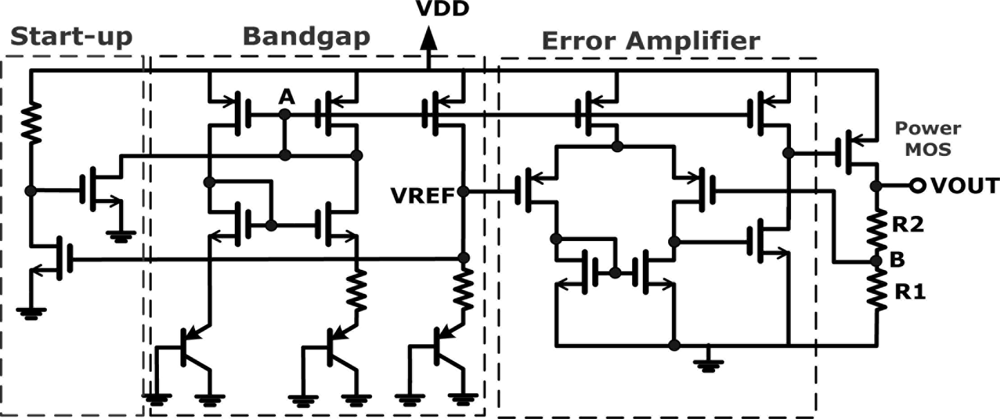

The schematic of the regulator is shown in Figure 11 and consists of a start-up circuit, a bandgap reference, and an error amplifier. The function of the bandgap reference is to generate a temperature insensitive voltage (VREF) that is realized by typical current-mirroring bandgap reference topology. A start-up circuit is implemented to prevent the reluctance of the bandgap reference circuit from interfering the supply voltage. It helps to drag down the gate voltage at node A right after the supply voltage is applied, so that all transistors of bandgap reference can be biased correctly. The error amplifier is a simple single-ended op-amp architecture. Through negative feedback resistors (R1 and R2), the error amplifier will lock the voltage at node B to the reference voltage generated by the bandgap reference. Consequently, an output voltage (VOUT) of the regulator is also temperature-independent and given by:

4. Experimental Results

4.1. Temperature Sensor

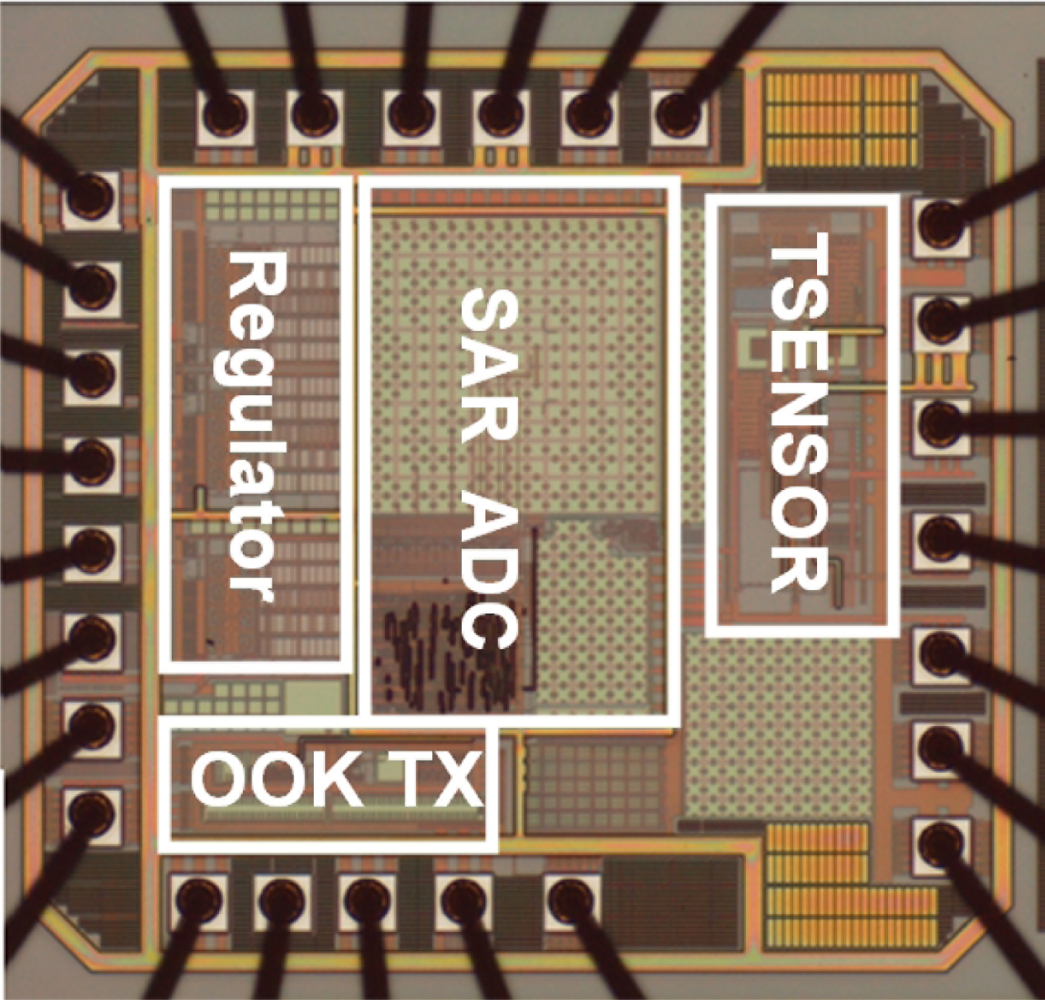

The proposed wireless temperature sensor has been tested in a MC-810 Mini-Subzero temperature chamber provided by Integrated Service Technology (IST) and the experimental setup has been established to test the sensitivity and linearity of the wireless temperature sensor, as shown in Figure 12. The red circle in Figure 12 highlights the wireless receiver module that acquires and stores immediate data from the wireless temperature sensor in Figure 1. A photograph of the test PCB block is given in Figure 13. The chip, shown in Figure 14, is 1.225 mm × 1.325 mm and contains the TSENSOR, SAR ADC, OOK TX, and Regulator blocks. Here, the TSENSOR and OOK TX mean the temperature sensor and OOK transmitter, respectively.

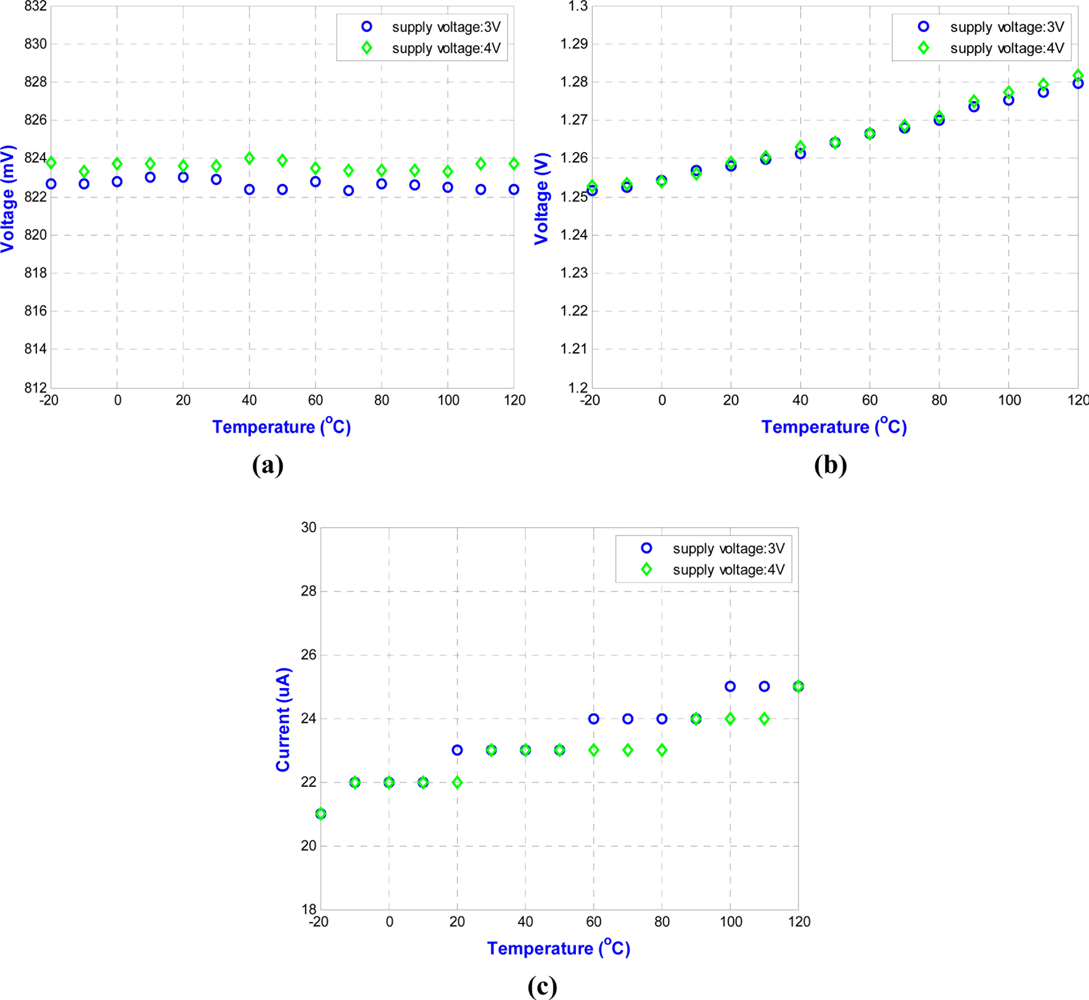

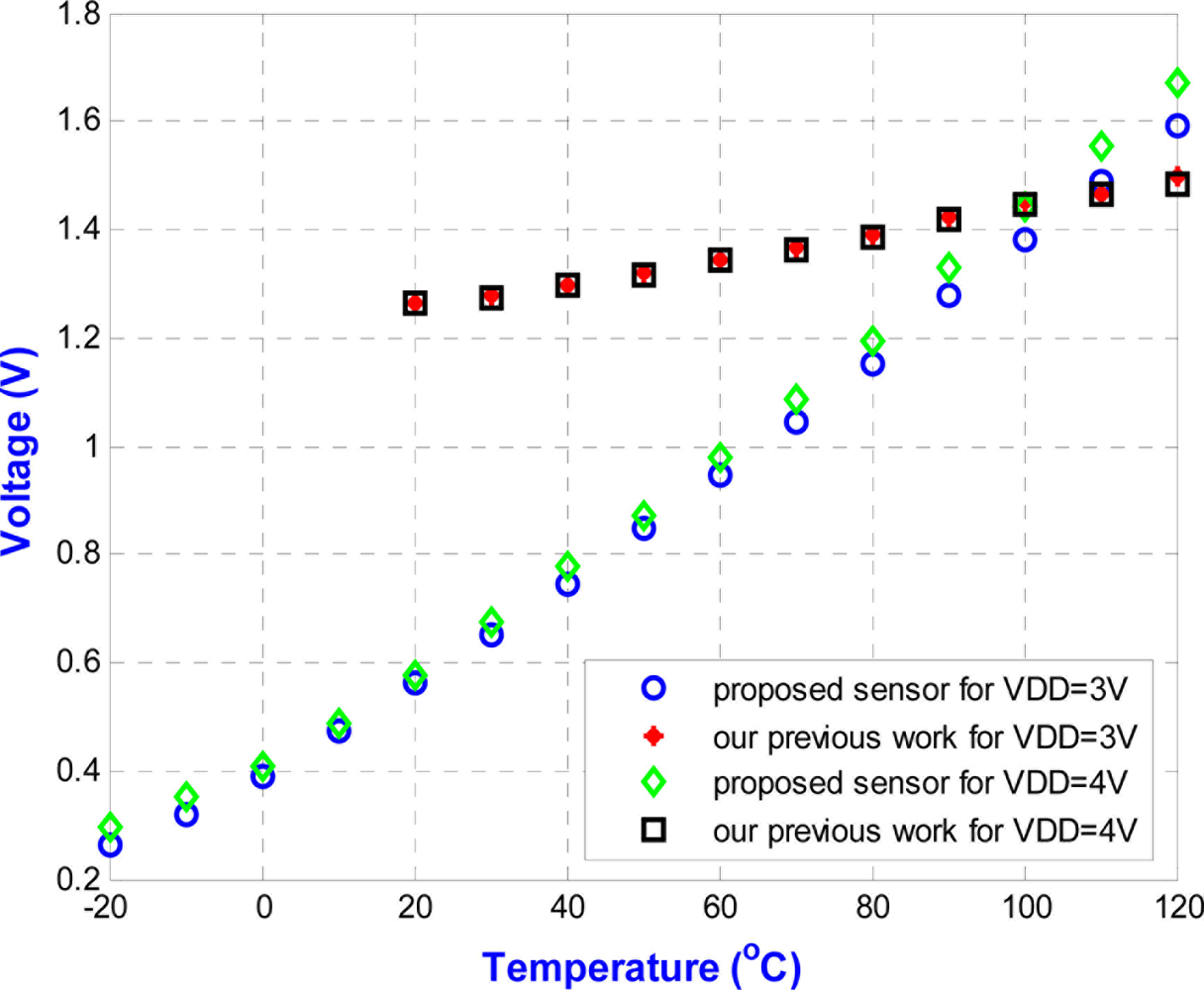

The circuit is fabricated using the 0.35 μm n-well double-poly CMOS process. The measurements use power supplies of 3.0 V and 4.0 V. The chip is measured in a temperature chamber by varying the temperature from −20 °C to 120 °C. For the voltage references, VREF,3.3V, VREF,5V, and the current reference, IREF are plotted in Figure 15. The two voltage references in Figure 15(a,b) can provide temperature-stable outputs of 823 mV and 1,265 mV with maximum deviations of 0.2 mV and 8.9 mV, respectively. The result for the current reference in Figure 15(c) gives a measurement of 23.5 μA, with a maximum deviation of 1.2 μA. The blue circle dots in Figure 16 show the variation of output voltage of the temperature sensor for power supply of 3.0 V. Thus, the sensitivity and linearity of the proposed wireless temperature sensor are 9.55 mV/°C, and 97%, respectively. The measurement results of the sensor in Figure 16 have 4.15-times better sensitivity than the previous design. The comparison of these two temperature sensors is shown in Figure 16. The variation of supply voltage has little effect on the design.

4.2. Wireless Transmitter

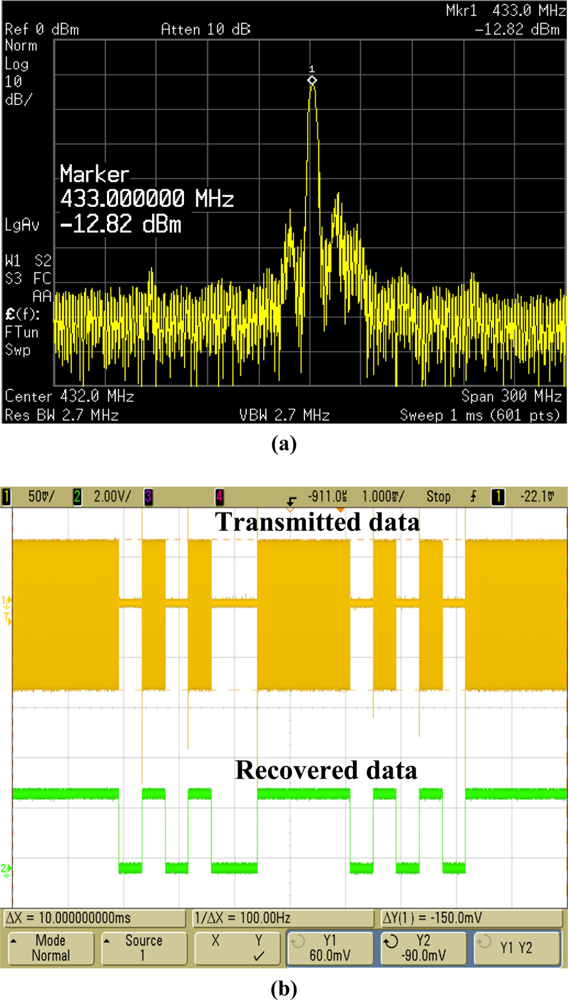

Figure 17(a) shows the spectrum of the output power of the wireless OOK transmitter measured by using an Agilent E4440A PSA spectrum analyzer. The maximum power is about −13 dBm centered at 433 MHz, which is matched to the license-free ISM band. In our experimental setup, a self-designed low-power CMOS OOK receiver chip with sensitivity of −62 dBm and an antenna with 2 dBi gain are combined together to pick up the wireless transmitted data. During experiments, the distance between the transmitter and the receiver module is about 2 m and the data transmission looks quite stable. Furthermore, the maximum transmission distance in free space can be roughly calculated to be about 25 m according to the Friis transmission equation shown below:

The corresponding transmitted waveform with OOK modulation is shown in Figure 17(b). After being demodulated by the OOK receiver module, the original serial data can be successfully recovered and fed into the data collectors (laptops in this work). To further facilitate the recording process, a simple graphical user interface (GUI) based on LabVIEW software was developed. The blue circle dots in Figure 18 show the RX output for a power supply of 3.0 V. In addition, the linearity of the RX output of the proposed wireless temperature sensor is 98%, but the temperature range is only from 0 °C to 120 °C. At subzero temperatures, the output results of the RX output are not very linear because the on-chip OOK transmitter used here cannot be operated normally under such temperatures. From the chip results measured from −20 °C to 120 °C, the linearity of the proposed wireless temperature sensor is 97%. A performance summary is given in Table 1.

5. Conclusions

A combined device with two voltage references, one current reference, and a temperature sensor was created by using the DZTC principle and fabricated using the TSMC 2P4M process. From the chip results measured from −20 °C to 120 °C, the voltage references can provide a temperature-stable output at 823 mV and 1,265 mV. The temperature sensor has sensitivity and linearity up to 9.55 mV/°C, and 97%, respectively. For comparison, our previous PTAT temperature sensor only had sensitivity and linearity of 2.3 mV/°C, and 95%, respectively. In other words, the proposed sensor improves the sensitivity of our previous design 4.15-fold. The temperature sensor operates from −20 °C to 120 °C, achieving a resolution of 0.46875 °C, and ±0.6 °C inaccuracy without calibration. According to the experimental results, we can see that the proposed wireless temperature sensor has good precision and repeatability. The experimental results show that the immediate sensing temperature data can be successfully transmitted to the data collector through wireless communication. The combined device can also be fabricated using the CMOS process, which is suitable for embedded SoC applications.

Acknowledgments

The authors would like to thank the National Chip Implementation Center (CIC) for chip realization and the Industrial Technology Research Institute (ITRI) for providing measurement services. This work was partially supported by the Industrial Development Bureau, Ministry of Economic Affairs of R.O.C. under grants NSC 98-2221-E-002-133-MY3.

References and Notes

- Song, B.S.; Gray, P.R. A precision curvature-compensated CMOS bandgap reference. IEEE J. Solid State Circ 1983, 18, 634–643. [Google Scholar]

- Weng, M.C.; Wu, J.C. A Temperature Sensor in 0.6 μm CMOS Technology. Proceedings of the First IEEE Asia Pacific Conference on ASICs, Seoul, South Korea, 23–25 August 1999; pp. 116–119.

- Lakdawala, H.; Li, Y.W.; Raychowdhury, A.; Taylor, G.; Soumyanath, K. A 1.05 V 1.6 mW 0.45 °C 3σ resolution ΣΔ based temperature sensor with parasitic resistance compensation in 32 nm digital CMOS process. IEEE J. Solid State Circ 2009, 44, 3621–3630. [Google Scholar]

- Najafizadeh, L.; Filanovsky, I.M. A Simple Voltage Reference Using Transistor with ZTC Point and PTAT Current Source. Proceedings of the International Symposium on Circuits and Systems, Vancouver, BC, Canada, 23–26 May 2004; 1, pp. 23–26.

- Zito, F.; Fragomeni, L.; Aquilino, F.; Corte, F.G.D. Wireless Temperature Sensor Integrated Circuits with On-Chip Antennas. Proceedings of 15th IEEE Mediterranean Electrotechnical Conference, Valletta, Malta, 26–28 April 2010; pp. 1368–1373.

- Pertijs, M.A.P.; Makinwa, K.A.A.; Huijsing, J.H. A CMOS temperature sensor with a 3σ inaccuracy of ±0.1 °C from −55 °C to 125 °C. IEEE J. Solid State Circ 2005, 40, 2805–2815. [Google Scholar]

- Sebastiano, F.; Breems, L.J.; Makinwa, K.A.A.; Drago, S.; Leenaerts, D.; Nauta, B. A 1.2-V 10 μW NPN-based temperature sensor in 65-nm CMOS with an inaccuracy of 0.2 °C (3σ) from −70 °C to 125 °C. IEEE J. Solid State Circ 2010, 45, 2591–2601. [Google Scholar]

- Souri, K.; Makinwa, K.A.A. A 0.12 mm2 7.4 μW micropower temperature sensor with an inaccuracy of ±0.2 °C (3σ) from −30 °C to 125 °C. IEEE J. Solid State Circ 2011, 46, 1693–2601. [Google Scholar]

- Manku, T.; Wang, Y. Temperature-independent output voltage generated by threshold voltage of an NMOS transistor. Electr. Lett 1995, 31, 935–936. [Google Scholar]

- Liu, C.P.; Huang, H.P. A CMOS Voltage Reference with Temperature Sensor Using Self-PTAT Current Compensation. Proceedings of the International SOC Conference, Herndon, VA, USA, 19–23 September 2005; pp. 37–42.

- Liu, C.P.; Huang, H.P. Experimental validation of PTAT for in situ temperature sensor and voltage reference. Electr. Lett 2008, 44, 1016–1017. [Google Scholar]

- Chang, M.H.; Liu, C.P.; Huang, H.P. Chip implementation with combined temperature sensor and reference devices based on DZTC principle. Electr. Lett 2010, 46, 919–921. [Google Scholar]

- Foty, D. MOSFET Modeling with SPICE: Principle and Practice, 2nd ed; Practice-Hall: Upper Saddle River, NJ, USA, 1997. [Google Scholar]

- Chen, C.H.; Hwang, R.Z.; Huang, L.S.; Lin, S.M.; Chen, H.C.; Yang, Y.C.; Lin, Y.T.; Yu, S.A.; Lin, Y.S.; Wang, Y.H.; Chou, N.K.; Lu, S.S. A wireless bio-MEMS sensor for c-reactive protein detection based on nanomechanics. IEEE Trans. Biomed. Eng 2009, 56, 462–470. [Google Scholar]

- Sauerbery, J.; Schmitt-Landsiedel, D.; Thewes, R. A 0.5 V, 1 μW successive approximation ADC. IEEE J. Solid State Circ 2003, 38, 1261–1264. [Google Scholar]

- Jung, J.; Zhu, S.; Liu, P.; Chen, Y.J. 22-pJ/bit energy-efficient 2.4-GHz implantable OOK transmitter for wireless biotelemetry systems: In vitro experiments using rat skin-mimic. IEEE Trans. Microwave Theory Tech 2010, 58, 4102–4111. [Google Scholar]

- Yu, H.; Najafi, K. Low-Power Interface Circuits for Bio-Implantable Microsystems. Proceedings of IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 13 February 2003; 1, pp. 194–197.

| Process | 0.35 μm n-well double-poly CMOS |

| Chip size | 1.62 mm2 |

| Temperature Sensor | |

| Supply voltage | 3 V–4 V |

| Temperature range | −20 °C to 120 °C |

| Sensitivity | 9.55 mV/°C |

| Linearity | 97% |

| Resolution | 0.46875 °C |

| Inaccuracy | ±0.6 °C |

| VREF,3.3V | 823 mV |

| VREF,5V | 1,265 mV |

| Current reference | 23 μA |

| SAR ADC | |

| Resolution | 8 bits |

| Power consumption | 156.7 μW @ 2.4 kbps |

| OOK Transmitter | |

| Operating frequency | 433 MHz |

| Output power | −12.8 dBm |

| Power consumption | 11.9 mW @ 3 V |

| Regulator | |

| Line regulation | <80 mV/V |

| Load regulation | <66 μV/mA |

| Output to temperature variation | <4.67 μV/°C |

© 2011 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution license (http://creativecommons.org/licenses/by/3.0/).

Share and Cite

Chang, M.-H.; Huang, Y.-J.; Huang, H.-P.; Lu, S.-S. Chip Implementation with a Combined Wireless Temperature Sensor and Reference Devices Based on the DZTC Principle. Sensors 2011, 11, 10308-10325. https://doi.org/10.3390/s111110308

Chang M-H, Huang Y-J, Huang H-P, Lu S-S. Chip Implementation with a Combined Wireless Temperature Sensor and Reference Devices Based on the DZTC Principle. Sensors. 2011; 11(11):10308-10325. https://doi.org/10.3390/s111110308

Chicago/Turabian StyleChang, Ming-Hui, Yu-Jie Huang, Han-Pang Huang, and Shey-Shi Lu. 2011. "Chip Implementation with a Combined Wireless Temperature Sensor and Reference Devices Based on the DZTC Principle" Sensors 11, no. 11: 10308-10325. https://doi.org/10.3390/s111110308