Review of CMOS Integrated Circuit Technologies for High-Speed Photo-Detection

Abstract

:1. Introduction

2. Silicon Photonics for High-Speed Data Communications

2.1. Overview of Optical Link

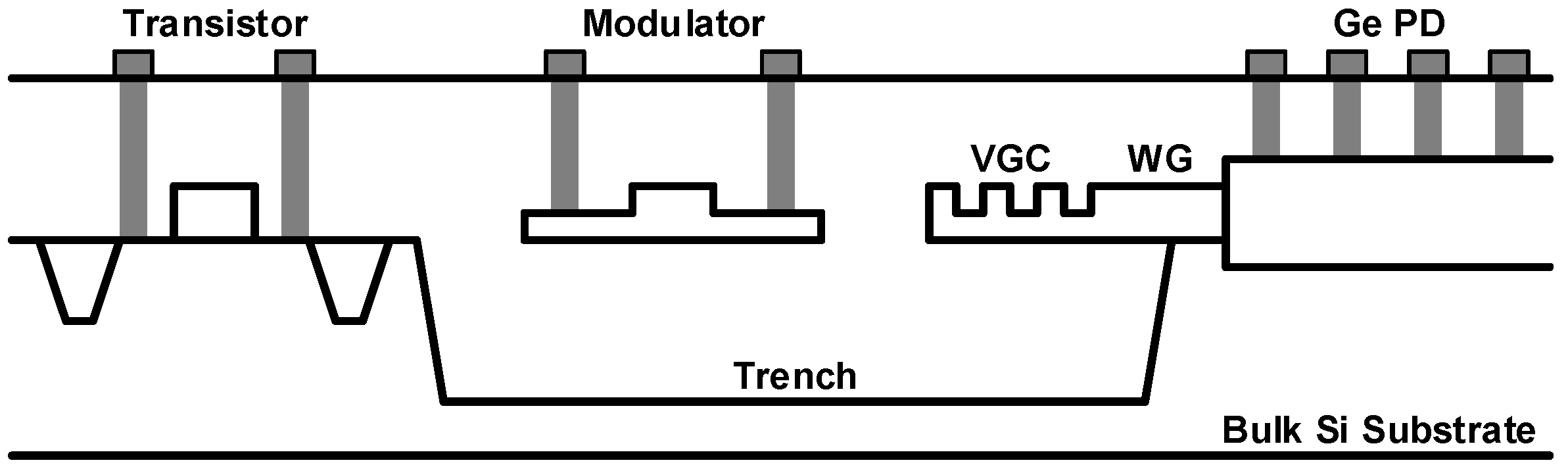

2.2. Silicon Photonics

2.3. Hybrid Integration

3. Si-Based Photodetectors

3.1. Basic Terminology

3.2. Si PD

3.3. Ge-Introduced PD

3.4. Integration of PD with Waveguide

4. CMOS Transimpedance Amplifier (TIA)

4.1. Resistor-Based TIA

4.2. Common-Gate-Based TIA

4.3. Feedback-Based TIA

4.4. Inverter-Based TIA

4.5. Integrating Receiver

5. Bandwidth Extension Techniques

5.1. Inductive Peaking

5.2. Equalization

6. Clock and Data Recovery (CDR) Circuits

6.1. CDR Basic

6.2. CDR Examples

7. Summary and Outlook

- Circuit and system topologies which utilize the advantages of highly-scaled CMOS technology, such as the inverter-based TIA and all-digital CDR. It is because advanced CMOS technology focuses on optimizing digital circuits.

- Circuit techniques to overcome the noise-bandwidth tradeoff in front-end circuit, such as the inductive peaking techniques, the equalization scheme, and the integration-based circuit. Since it is obvious that the front-end circuit has been and will be the bottleneck, both in terms of speed and SNR, it is highly required to break the tradeoff.

Author Contributions

Conflicts of Interest

References

- Cisco Systems, Inc. Available online: http://www.cisco.com (accessed on 19 June 2017).

- Soref, R.A. Silicon-based optoelectronics. Proc. IEEE 1993, 81, 1687–1706. [Google Scholar] [CrossRef]

- Izhaky, N.; Morse, M.T.; Koehl, S.; Cohen, O.; Rubin, D.; Barkai, A.; Sarid, G.; Cohen, R.; Paniccia, M.J. Development of CMOS-compatible integrated silicon photonics devices. IEEE J. Sel. Top. Quantum Electron. 2006, 12, 1688–1698. [Google Scholar] [CrossRef]

- Vlasov, Y.A. Silicon CMOS-integrated nano-photonics for computer and data communications beyond 100G. IEEE Commun. Mag. 2012, 50, s67–s72. [Google Scholar] [CrossRef]

- Fedeli, J.-M.; Fulbert, L.; Van Thourhout, D.; Viktorovitch, P.; O’Connor, I.; Duan, G.-H.; Reed, G.; Corte, F.D.; Vivien, L.; Royo, F.L.; et al. HELIOS: Photonics electronics functional integration on CMOS. SPIE Proc. 2010, 7719, 1–10. [Google Scholar]

- Gunn, C. CMOS photonics for high-speed interconnects. IEEE Micro 2006, 26, 58–66. [Google Scholar] [CrossRef]

- Liu, F.Y.; Patil, D.; Lexau, J.; Amberg, P.; Dayringer, M.; Gainsley, J.; Moghadam, H.F.; Zheng, X.; Cunningham, J.E.; Krishnamoorthy, A.V. 10-Gbps, 5.3-mW optical transmitter and receiver circuits in 40-nm CMOS. IEEE J. Solid-State Circuits 2012, 47, 2049–2067. [Google Scholar] [CrossRef]

- Arakawa, Y.; Nakamura, T.; Urino, Y.; Fujita, T. Silicon photonics for next generation system integration platform. IEEE Commun. Mag. 2013, 51, 72–77. [Google Scholar] [CrossRef]

- Zhang, B.; Khanoyan, K.; Hatamkhani, H.; Tong, H.; Hu, K.; Fallahi, S.; Abdul-Latif, M.; Vakilian, K.; Fujimori, I.; Brewster, A. A 28 Gb/s multistandard serial link transceiver for backplane applications in 28 nm CMOS. IEEE J. Solid-State Circuits 2015, 50, 3089–3100. [Google Scholar] [CrossRef]

- Kawamoto, T.; Norimatsu, T.; Kogo, K.; Yuki, F.; Nakajima, N.; Tsuge, M.; Usugi, T.; Hokari, T.; Koba, H.; Komori, T. Multi-standard 185 fs rms 0.3-to-28 Gb/s 40 dB backplane signal conditioner with adaptive pattern-match 36-Tap DFE and data-rate-adjustment PLL in 28 nm CMOS. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 22–26 February 2015; pp. 1–3. [Google Scholar]

- Norimatsu, T.; Kawamoto, T.; Kogo, K.; Kohmu, N.; Yuki, F.; Nakajima, N.; Muto, T.; Nasu, J.; Komori, T.; Koba, H. A 25 Gb/s multistandard serial link transceiver for 50 dB-loss copper cable in 28 nm CMOS. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 31 January–4 February 2016; pp. 60–61. [Google Scholar]

- Peng, P.-J.; Li, J.-F.; Chen, L.-Y.; Lee, J. A 56 Gb/s PAM-4/NRZ transceiver in 40 nm CMOS. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 5–9 February 2017; pp. 110–111. [Google Scholar]

- Im, J.; Freitas, D.; Roldan, A.; Casey, R.; Chen, S.; Chou, A.; Cronin, T.; Geary, K.; McLeod, S.; Zhou, L. A 40-to-56 Gb/s PAM-4 receiver with 10-tap direct decision-feedback equalization in 16 nm FinFET. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 5–9 February 2017; pp. 114–115. [Google Scholar]

- Steffan, G.; Depaoli, E.; Monaco, E.; Sabatino, N.; Audoglio, W.; Rossi, A.A.; Erba, S.; Bassi, M.; Mazzanti, A. A 64 Gb/s PAM-4 transmitter with 4-Tap FFE and 2.26 pJ/b energy efficiency in 28 nm CMOS FDSOI. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 5–9 February 2017; pp. 116–117. [Google Scholar]

- Dickson, T.O.; Ainspan, H.A.; Meghelli, M. A 1.8 pJ/b 56 Gb/s PAM-4 transmitter with fractionally spaced. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 5–9 February 2017; pp. 118–119. [Google Scholar]

- Gupta, S.; Tellado, J.; Begur, S.; Yang, F.; Balan, V.; Inerfield, M.; Dabiri, D.; Dring, J.; Goel, S.; Muthukumaraswamy, K.; et al. A 10 Gb/s IEEE 802.3 an-compliant Ethernet transceiver for 100 m UTP cable in 0.13 um CMOS. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 3–7 February 2008; pp. 106–107. [Google Scholar]

- Hidaka, Y.; Gai, W.; Horie, T.; Jiang, J.H.; Koyanagi, Y.; Osone, H. A 4-channel 10.3 Gb/s backplane transceiver macro with 35 dB equalizer and sign-based zero-forcing adaptive control. IEEE J. Solid-State Circuits 2009, 44, 3547–3559. [Google Scholar] [CrossRef]

- Fukuda, K.; Yamashita, H.; Ono, G.; Nemoto, R.; Suzuki, E.; Takemoto, T.; Yuki, F. A 12.3 mW 12.5 Gb/s complete transceiver in 65 nm CMOS. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 7–11 February 2010; pp. 368–369. [Google Scholar]

- Chen, M.-S.; Shih, Y.-N.; Lin, C.-L.; Hung, H.-W.; Lee, J. A 40 Gb/s TX and RX chip set in 65 nm CMOS. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 20–24 February 2011; pp. 146–147. [Google Scholar]

- Bulzacchelli, J.; Beukema, T.; Storaska, D.; Hsieh, P.-H.; Rylov, S.; Furrer, D.; Gardellini, D.; Prati, A.; Menolfi, C.; Hanson, D.; et al. A 28 Gb/s 4-tap FFE/15-tap DFE serial link transceiver in 32 nm SOI CMOS technology. IEEE J. Solid-State Circuits 2012, 47, 3232–3248. [Google Scholar] [CrossRef]

- Raghavan, B.; Cui, D.; Singh, U.; Maarefi, H.; Pi, D.; Vasani, A.; Huang, Z.; Momtaz, A.; Cao, J. A sub-2W 39.8-to-44.6 Gb/s transmitter and receiver chipset with SFI-5.2 interface in 40 nm CMOS. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 17–21 February 2013; pp. 32–33. [Google Scholar]

- Jaussi, J.; Balamurugan, G.; Hyvonen, S.; Hsueh, T.-C.; Musah, T.; Keskin, G.; Shekhar, S.; Kennedy, J.; Sen, S.; Inti, R.; et al. A 205 mW 32 Gb/s 3-tap FFE/6-tap DFE bidirectional serial link in 22 nm CMOS. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 9–13 February 2014; pp. 440–441. [Google Scholar]

- Upadhyaya, P.; Savoj, J.; An, F.-T.; Bekele, A.; Jose, A.; Xu, B.; Wu, D.; Turker, D.; Aslanzadeh, H.; Hedayati, H.; et al. A 0.5-to-32.75 Gb/s flexible-reach wireline transceiver in 20 nm CMOS. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 22–26 February 2015; pp. 56–57. [Google Scholar]

- Shibasake, T.; Danjo, T.; Ogata, Y.; Sakai, Y.; Miyaoka, H.; Terasawa, F.; Kudo, M.; Kano, H.; Matsuda, A.; Kawai, S.; et al. A 56 Gb/s NRZ-electrical 247 mW/lane serial-link transceiver in 28 nm CMOS. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 31 January–4 February 2016; pp. 64–65. [Google Scholar]

- Han, J.; Lu, Y.; Sutardja, N.; Alon, E. A 60 Gb/s 288 mW NRZ transceiver with adaptive equalization and baud-rate clock and data recovery in 65 nm CMOS technology. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 5–9 February 2017; pp. 112–113. [Google Scholar]

- Balamurugan, G.; O’Mahony, F.; Mansuri, M.; Jaussi, J.E.; Kennedy, J.T.; Casper, B. A 5-to-25 Gb/s 1.6-to-3.8 mW/(Gb/s) reconfigurable transceiver in 45 nm CMOS. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 7–11 February 2010; pp. 372–373. [Google Scholar]

- Chiang, P.-C.; Hung, H.-W.; Chu, H.-Y.; Chen, G.-S.; Lee, J. 60 Gb/s NRZ and PAM4 transmitters for 400 GbE in 65 nm CMOS. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 9–13 February 2014; pp. 42–43. [Google Scholar]

- Kim, J.; Balankutty, A.; Elshazly, A.; Huang, Y.-Y.; Song, H.; Yu, K.; O’Mahony, F. A 16-to-40 Gb/s quarter-rate NRZ/PAM4 dual-mode transmitter in 14 nm CMOS. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 22–26 February 2015; pp. 60–61. [Google Scholar]

- Gopalakrishnan, K.; Ren, A.; Tan, A.; Farhood, A.; Tiruvur, A.; Helal, B.; Loi, C.-F.; Jiang, C.; Cirit, H.; Quek, I.; et al. A 40/50/100 Gb/s PAM-4 ethernet transceiver in 28 nm CMOS. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 31 January–4 February 2016; pp. 62–63. [Google Scholar]

- IEEE P802.3ae 10 Gb/s Ethernet Task Force. Available online: http://www.ieee802.org/3/ae/ (accessed on 19 June 2017).

- IEEE P802.3ba and 100 Gb/s Ethernet Task Force. Available online: http://www.ieee802.org/3/ba/ (accessed on 19 June 2017).

- 100G CLR4 Alliance. Available online: https://www.clr4-alliance.org/ (accessed on 19 June 2017).

- CWDM4 MSA. Available online: http://www.cwdm4-msa.org/ (accessed on 19 June 2017).

- Jalali, B.; Paniccia, M.; Reed, G. Silicon photonics. IEEE Microw. Mag. 2006, 7, 58–68. [Google Scholar] [CrossRef] [Green Version]

- Soref, R. The past, present, and future of silicon photonics. IEEE J. Sel. Top. Quantum Electron. 2006, 12, 1678–1687. [Google Scholar] [CrossRef]

- Hochberg, M.; Harris, N.C.; Ding, R.; Zhang, Y.; Novack, A.; Xuan, Z.; Baehr-Jones, T. Silicon photonics: The next fabless semiconductor industry. IEEE Solid-State Circuits Mag. 2013, 5, 48–58. [Google Scholar] [CrossRef]

- Vivien, L.; Polzer, A.; Marris-Morini, D.; Osmond, J.; Hartmann, J.M.; Crozat, P.; Cassan, E.; Kopp, C.; Zimmermann, H.; Fédéli, J.M. Zero-bias 40 Gbit/s germanium waveguide photodetector on silicon. Opt. Express 2012, 20, 1096–1101. [Google Scholar] [CrossRef] [PubMed]

- Assefa, S.; Xia, F.; Vlasov, Y.A. Reinventing germanium avalanche photodetector for nanophotonic on-chip optical interconnects. Nature 2010, 464, 80–84. [Google Scholar] [CrossRef] [PubMed]

- Thomson, D.J.; Gardes, F.Y.; Fedeli, J.-M.; Zlatanovic, S.; Hu, Y.; Kuo, B.P.P.; Myslivets, E.; Alic, N.; Radic, S.; Mashanovich, G.Z. 50-Gb/s silicon optical modulator. IEEE Photonics Technol. Lett. 2012, 24, 234–236. [Google Scholar] [CrossRef]

- Temporiti, E.; Minoia, G.; Repossi, M.; Baldi, D.; Ghilioni, A.; Svelto, F. A 56 Gb/s 300 mW silicon-photonics transmitter in 3D-integrated PIC25G and 55 nm BiCMOS technologies. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 31 January–4 February 2016; pp. 404–405. [Google Scholar]

- Xu, Q.; Schmidt, B.; Pradhan, S.; Lipson, M. Micrometre-scale silicon electro-optic modulator. Nature 2005, 435, 325–327. [Google Scholar] [CrossRef] [PubMed]

- Li, G.; Zheng, X.; Yao, J.; Thacker, H.; Shubin, I.; Luo, Y.; Raj, K.; Cunningham, J.E.; Krishnamoorthy, A.V. 25 Gb/s 1V-driving CMOS ring modulator with integrated thermal tuning. Opt. Express 2011, 19, 20435–20443. [Google Scholar] [CrossRef] [PubMed]

- Rakowski, M.; Pantouvaki, M.; De Heyn, P.; Verheyen, P.; Ingels, M.; Chen, H.; De Coster, J.; Lepage, G.; Snyder, B.; De Meyer, K. A 4 × 20 Gb/s WDM ring-based hybrid CMOS silicon photonics transceiver. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 22–26 February 2015; pp. 1–3. [Google Scholar]

- Analui, B.; Guckenberger, D.; Kucharski, D.; Narasimha, A. A Fully Integrated 20-Gb/s Optoelectronic Transceiver Implemented in a Standard 0.13-µm CMOS SOI Technology. IEEE J. Solid-State Circuits 2006, 41, 2945–2955. [Google Scholar] [CrossRef]

- Narasimha, A.; Analui, B.; Liang, Y.; Sleboda, T.J.; Abdalla, S.; Balmater, E.; Gloeckner, S.; Guckenberger, D.; Harrison, M.; Koumans, R.G.M.P.; et al. A Fully Integrated 4 × 10-Gb/s DWDM Optoelectronic Transceiver Implemented in a Standard 0.13 µm CMOS SOI Technology. IEEE J. Solid-State Circuits 2007, 42, 2736–2744. [Google Scholar] [CrossRef]

- Georgas, M.; Orcutt, J.; Ram, R.J.; Stojanovic, V. A monolithically-integrated optical receiver in standard 45-nm SOI. IEEE J. Solid-State Circuits 2012, 47, 1693–1702. [Google Scholar] [CrossRef]

- Buckwalter, J.F.; Zheng, X.; Li, G.; Raj, K.; Krishnamoorthy, A.V. A monolithic 25-Gb/s transceiver with photonic ring modulators and Ge detectors in a 130-nm CMOS SOI process. IEEE J. Solid-State Circuits 2012, 47, 1309–1322. [Google Scholar] [CrossRef]

- Sun, C.; Wade, M.T.; Lee, Y.; Orcutt, J.S.; Alloatti, L.; Georgas, M.S.; Waterman, A.S.; Shainline, J.M.; Avizienis, R.R.; Lin, S. Single-chip microprocessor that communicates directly using light. Nature 2015, 528, 534–538. [Google Scholar] [CrossRef] [PubMed]

- Meade, R.; Orcutt, J.S.; Mehta, K.; Tehar-Zahav, O.; Miller, D.; Georgas, M.; Moss, B.; Sun, C.; Chen, Y.-H.; Shainline, J. Integration of silicon photonics in bulk CMOS. In Proceedings of the IEEE Symposium on VLSI Technology Digest of Technical Papers, Honolulu, HI, USA, 9–12 June 2014; pp. 1–2. [Google Scholar]

- Sun, C.; Georgas, M.; Orcutt, J.; Moss, B.; Chen, Y.-H.; Shainline, J.; Wade, M.; Mehta, K.; Nammari, K.; Timurdogan, E. A monolithically-integrated chip-to-chip optical link in bulk CMOS. IEEE J. Solid-State Circuits 2015, 50, 828–844. [Google Scholar] [CrossRef]

- Byun, H.; Bok, J.; Cho, K.; Cho, K.; Choi, H.; Choi, J.; Choi, S.; Han, S.; Hong, S.; Hyun, S. Bulk-Si photonics technology for DRAM interface [Invited]. Photonics Res. 2014, 2, A25–A33. [Google Scholar] [CrossRef]

- Proesel, J.; Schow, C.; Rylyakov, A. 25 Gb/s 3.6 pJ/b and 15 Gb/s 1.37 pJ/b VCSEL-based optical links in 90 nm CMOS. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 19–23 February 2012; pp. 418–420. [Google Scholar]

- Cevrero, A.; Ozkaya, I.; Francese, P.A.; Menolfi, C.; Morf, T.; Brandli, M.; Kuchta, D.; Kull, L.; Proesel, J.; Kossel, M. A 64 Gb/s 1.4 pJ/b NRZ optical-receiver data-path in 14 nm CMOS FinFET. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 5–9 February 2017; pp. 482–483. [Google Scholar]

- Takemoto, T.; Yamashita, H.; Yazaki, T.; Chujo, N.; Lee, Y.; Matsuoka, Y. A 25-to-28 Gb/s High-Sensitivity (−9.7 dBm) 65 nm CMOS Optical Receiver for Board-to-Board Interconnects. IEEE J. Solid-State Circuits 2014, 49, 2259–2276. [Google Scholar] [CrossRef]

- Morita, H.; Uchino, K.; Otani, E.; Ohtorii, H.; Ogura, T.; Oniki, K.; Oka, S.; Yanagawa, S.; Suzuki, H. A 12× 5 two-dimensional optical I/O array for 600 Gb/s chip-to-chip interconnect in 65 nm CMOS. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 9–13 February 2014; pp. 140–141. [Google Scholar]

- Chen, Y.; Kibune, M.; Toda, A.; Hayakawa, A.; Akiyama, T.; Sekiguchi, S.; Ebe, H.; Imaizumi, N.; Akahoshi, T.; Akiyama, S. A 25 Gb/s hybrid integrated silicon photonic transceiver in 28 nm CMOS and SOI. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 22–26 February 2015; pp. 1–3. [Google Scholar]

- Cignoli, M.; Minoia, G.; Repossi, M.; Baldi, D.; Ghilioni, A.; Temporiti, E.; Svelto, F. A 1310 nm 3D-integrated silicon photonics Mach-Zehnder-based transmitter with 275 mW multistage CMOS driver achieving 6 dB extinction ratio at 25 Gb/s. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 22–26 February 2015; pp. 1–3. [Google Scholar]

- Geis, M.; Spector, S.; Grein, M.; Schulein, R.; Yoon, J.; Lennon, D.; Deneault, S.; Gan, F.; Kaertner, F.; Lyszczarz, T. CMOS-compatible all-Si high-speed waveguide photodiodes with high responsivity in near-infrared communication band. IEEE Photonics Technol. Lett. 2007, 19, 152–154. [Google Scholar] [CrossRef]

- Geis, M.; Spector, S.; Grein, M.; Yoon, J.; Lennon, D.; Lyszczarz, T. Silicon waveguide infrared photodiodes with> 35 GHz bandwidth and phototransistors with 50 AW-1 response. Opt. Express 2009, 17, 5193–5204. [Google Scholar] [CrossRef]

- Doylend, J.; Jessop, P.; Knights, A. Silicon photonic resonator-enhanced defect-mediated photodiode for sub-bandgap detection. Opt. Express 2010, 18, 14671–14678. [Google Scholar] [CrossRef] [PubMed]

- Preston, K.; Lee, Y.H.D.; Zhang, M.; Lipson, M. Waveguide-integrated telecom-wavelength photodiode in deposited silicon. Opt. Lett. 2011, 36, 52–54. [Google Scholar] [CrossRef] [PubMed]

- Mehta, K.K.; Orcutt, J.S.; Shainline, J.M.; Tehar-Zahav, O.; Sternberg, Z.; Meade, R.; Popović, M.A.; Ram, R.J. Polycrystalline silicon ring resonator photodiodes in a bulk complementary metal-oxide-semiconductor process. Opt. Lett. 2014, 39, 1061–1064. [Google Scholar] [CrossRef] [PubMed]

- Reed, G.T. Silicon Photonics: The State of the Art; John Wiley & Sons: Hoboken, NJ, USA, 2008. [Google Scholar]

- Samavedam, S.; Currie, M.; Langdo, T.; Fitzgerald, E. High-quality germanium photodiodes integrated on silicon substrates using optimized relaxed graded buffers. Appl. Phys. Lett. 1998, 73, 2125–2127. [Google Scholar] [CrossRef]

- Colace, L.; Masini, G.; Galluzzi, F.; Assanto, G.; Capellini, G.; Di Gaspare, L.; Palange, E.; Evangelisti, F. Metal–semiconductor–metal near-infrared light detector based on epitaxial Ge/Si. Appl. Phys. Lett. 1998, 72, 3175–3177. [Google Scholar] [CrossRef]

- Luan, H.-C.; Lim, D.R.; Lee, K.K.; Chen, K.M.; Sandland, J.G.; Wada, K.; Kimerling, L.C. High-quality Ge epilayers on Si with low threading-dislocation densities. Appl. Phys. Lett. 1999, 75, 2909–2911. [Google Scholar] [CrossRef]

- Fama, S.; Colace, L.; Masini, G.; Assanto, G.; Luan, H.-C. High performance germanium-on-silicon detectors for optical communications. Appl. Phys. Lett. 2002, 81, 586–588. [Google Scholar] [CrossRef]

- Yu, H.-Y.; Ren, S.; Jung, W.S.; Okyay, A.K.; Miller, D.A.; Saraswat, K.C. High-efficiency pin photodetectors on selective-area-grown Ge for monolithic integration. IEEE Electron Device Lett. 2009, 30, 1161–1163. [Google Scholar]

- Kim, J.; Buckwalter, J.F. A 40-Gb/s optical transceiver front-end in 45 nm SOI CMOS. IEEE J. Solid-State Circuits 2012, 47, 615–626. [Google Scholar] [CrossRef]

- Proesel, J.; Rylyakov, A.; Schow, C. Optical receivers using DFE-IIR equalization. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 17–21 February 2013; pp. 130–131. [Google Scholar]

- Park, S.M.; Toumazou, C. A packaged low-noise high-speed regulated cascode transimpedance amplifier using a 0.6 µm N-well CMOS technology. In Proceedings of the IEEE European Solid-State Circuits Conference (ESSCIRC), Stockholm, Sweden, 19–21 September 2000; pp. 431–434. [Google Scholar]

- Park, S.M.; Yoo, H.-J. 1.25-Gb/s regulated cascode CMOS transimpedance amplifier for gigabit ethernet applications. IEEE J. Solid-State Circuits 2004, 39, 112–121. [Google Scholar] [CrossRef]

- Park, S.M.; Lee, J.; Yoo, H.-J. 1-Gb/s 80-dBΩ fully differential CMOS transimpedance amplifier in multichip on oxide technology for optical interconnects. IEEE J. Solid-State Circuits 2004, 39, 971–974. [Google Scholar] [CrossRef]

- Takemoto, T.; Yamashita, H.; Yuki, F.; Masuda, N.; Toyoda, H.; Chujo, N.; Lee, Y.; Tsuji, S.; Nishimura, S. A 25-Gb/s 2.2-W 65-nm CMOS optical transceiver using a power-supply-variation-tolerant analog front end and data-format conversion. IEEE J. Solid-State Circuits 2014, 49, 471–485. [Google Scholar] [CrossRef]

- Kromer, C.; Sialm, G.; Morf, T.; Schmatz, M.L.; Ellinger, F.; Erni, D.; Jackel, H. A low-power 20-GHz 52-dBΩ transimpedance amplifier in 80-nm CMOS. IEEE J. Solid-State Circuits 2004, 39, 885–894. [Google Scholar] [CrossRef]

- Abidi, A.A. Gigahertz transresistance amplifiers in fine line NMOS. IEEE J. Solid-State Circuits 1984, 19, 986–994. [Google Scholar] [CrossRef]

- Chiang, P.-C.; Jiang, J.-Y.; Hung, H.-W.; Wu, C.-Y.; Chen, G.-S.; Lee, J. 4× 25 Gb/s transceiver with optical front-end for 100 GbE system in 65 nm CMOS technology. IEEE J. Solid-State Circuits 2015, 50, 573–585. [Google Scholar] [CrossRef]

- Lim, P.-W.; Tzeng, A.Y.; Chuang, H.L.; Onge, S.S. A 3.3-V monolithic photodetector/CMOS-preamplifier for 531 Mb/s optical data link applications. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 24–26 February 1993; pp. 96–97. [Google Scholar]

- Woodward, T.; Krishnamoorthy, A.; Rozier, R.; Lentine, A. Low-power, small-footprint gigabit Ethernet-compatible optical receiver circuit in 0.25/spl mu/m CMOS. Electron. Lett. 2000, 36, 1489–1491. [Google Scholar] [CrossRef]

- Analui, B.; Hajimiri, A. Bandwidth enhancement for transimpedance amplifiers. IEEE J. Solid-State Circuits 2004, 39, 1263–1270. [Google Scholar] [CrossRef]

- Ingels, M.; Van der Plas, G.; Crols, J.; Steyaert, M. A CMOS 18 THz/spl Omega/248 Mb/s transimpedance amplifier and 155 Mb/s LED-driver for low cost optical fiber links. IEEE J. Solid-State Circuits 1994, 29, 1552–1559. [Google Scholar] [CrossRef]

- Yoon, T.; Jalali, B. 1.25 Gb/s CMOS differential transimpedance amplifier for gigabit networks. In Proceedings of the IEEE European Solid-State Circuits Conference (ESSCIRC), Southampton, UK, 16–18 September 1997; pp. 140–143. [Google Scholar]

- Tavernier, F.; Steyaert, M.S. High-speed optical receivers with integrated photodiode in 130 nm CMOS. IEEE J. Solid-State Circuits 2009, 44, 2856–2867. [Google Scholar] [CrossRef]

- Woodward, T.; Krishnamoorthy, A.V. 1 Gbit/s CMOS photoreceiver with integrated detector operating at 850 nm. Electron. Lett. 1998, 34, 1252–1253. [Google Scholar] [CrossRef]

- Huang, T.-C.; Chung, T.-W.; Chern, C.-H.; Huang, M.-C.; Lin, C.-C.; Hsueh, F.-L. A 28 Gb/s 1 pJ/b shared-inductor optical receiver with 56% chip-area reduction in 28 nm CMOS. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 9–13 February 2014; pp. 144–145. [Google Scholar]

- Li, C.; Bai, R.; Shafik, A.; Tabasy, E.Z.; Wang, B.; Tang, G.; Ma, C.; Chen, C.-H.; Peng, Z.; Fiorentino, M. Silicon photonic transceiver circuits with microring resonator bias-based wavelength stabilization in 65 nm CMOS. IEEE J. Solid-State Circuits 2014, 49, 1419–1436. [Google Scholar] [CrossRef]

- Li, D.; Minoia, G.; Repossi, M.; Baldi, D.; Temporiti, E.; Mazzanti, A.; Svelto, F. A low-noise design technique for high-speed CMOS optical receivers. IEEE J. Solid-State Circuits 2014, 49, 1437–1447. [Google Scholar] [CrossRef]

- Rylyakov, A.; Proesel, J.; Rylov, S.; Lee, B.; Bulzacchelli, J.; Ardey, A.; Parker, B.; Beakes, M.; Baks, C.; Schow, C. A 25 Gb/s burst-mode receiver for rapidly reconfigurable optical networks. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 22–26 February 2015; pp. 1–3. [Google Scholar]

- Chu, S.-H.; Bae, W.; Jeong, G.-S.; Jang, S.; Kim, S.; Joo, J.; Kim, G.; Jeong, D.-K. A 22 to 26.5 Gb/s optical receiver with all-digital clock and data recovery in a 65 nm CMOS process. IEEE J. Solid-State Circuits 2015, 50, 2603–2612. [Google Scholar] [CrossRef]

- Sun, C.; Wade, M.; Georgas, M.; Lin, S.; Alloatti, L.; Moss, B.; Kumar, R.; Atabaki, A.H.; Pavanello, F.; Shainline, J.M. A 45 nm CMOS-SOI monolithic photonics platform with bit-statistics-based resonant microring thermal tuning. IEEE J. Solid-State Circuits 2016, 51, 893–907. [Google Scholar] [CrossRef]

- Yu, K.; Li, C.; Li, H.; Titriku, A.; Shafik, A.; Wang, B.; Wang, Z.; Bai, R.; Chen, C.-H.; Fiorentino, M. A 25 Gb/s Hybrid-Integrated Silicon Photonic Source-Synchronous Receiver With Microring Wavelength Stabilization. IEEE J. Solid-State Circuits 2016, 51, 2129–2141. [Google Scholar] [CrossRef]

- Emami-Neyestanak, A.; Liu, D.; Keeler, G.; Helman, N.; Horowitz, M. A 1.6 Gb/s, 3 mW CMOS receiver for optical communication. In Proceedings of the IEEE Symposium on VLSI Circuits Digest of Technical Papers, Honolulu, HI, USA, 13–15 June 2002; pp. 84–87. [Google Scholar]

- Palermo, S.; Emami-Neyestanak, A.; Horowitz, M. A 90 nm CMOS 16 Gb/s transceiver for optical interconnects. IEEE J. Solid-State Circuits 2008, 43, 1235–1246. [Google Scholar] [CrossRef]

- Nazari, M.H.; Emami-Neyestanak, A. A 24-Gb/s double-sampling receiver for ultra-low-power optical communication. IEEE J. Solid-State Circuits 2013, 48, 344–357. [Google Scholar] [CrossRef]

- Mohan, S.S.; Hershenson, M.D.M.; Boyd, S.P.; Lee, T.H. Bandwidth extension in CMOS with optimized on-chip inductors. IEEE J. Solid-State Circuits 2000, 35, 346–355. [Google Scholar] [CrossRef]

- Lee, J.; Kundert, K.S.; Razavi, B. Analysis and modeling of bang-bang clock and data recovery circuits. IEEE J. Solid-State Circuits 2004, 39, 1571–1580. [Google Scholar]

- Han, J.; Choi, B.; Seo, M.; Yun, J.; Lee, D.; Kim, T.; Eo, Y.; Park, S.M. A 20-Gb/s Transformer-Based Current-Mode Optical Receiver in 0.13-µm CMOS. IEEE Trans. Circuits Syst. II Express Br. 2010, 57, 348–352. [Google Scholar]

- Kim, J.; Buckwalter, J.F. Bandwidth enhancement with low group-delay variation for a 40-Gb/s transimpedance amplifier. IEEE Trans. Circuits Syst. I Regul. Pap. 2010, 57, 1964–1972. [Google Scholar]

- Park, K.-S.; Yoo, B.-J.; Hwang, M.-S.; Chi, H.; Kim, H.-C.; Park, J.-W.; Kim, K.; Jeong, D.-K. A 10-Gb/s optical receiver front-end with 5-mW transimpedance amplifier. In Proceedings of the IEEE Asian Solid-State Circuits Conference (A-SSCC), Beijing, China, 8–10 November 2010; pp. 1–4. [Google Scholar]

- Bae, W.; Jeong, G.-S.; Kim, Y.; Chi, H.-K.; Jeong, D.-K. Design of silicon photonic interconnect ICS in 65-nm CMOS technology. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2016, 24, 2234–2243. [Google Scholar] [CrossRef]

- Galal, S.; Razavi, B. 40-Gb/s amplifier and ESD protection circuit in 0.18-µm CMOS technology. IEEE J. Solid-State Circuits 2004, 39, 2389–2396. [Google Scholar] [CrossRef]

- Shekhar, S.; Walling, J.S.; Allstot, D.J. Bandwidth extension techniques for CMOS amplifiers. IEEE J. Solid-State Circuits 2006, 41, 2424–2439. [Google Scholar] [CrossRef]

- Kim, J.; Kim, J.-K.; Lee, B.-J.; Jeong, D.-K. Design Optimization of On-Chip Inductive Peaking Structures for 0.13-µm CMOS 40-Gb/s Transmitter Circuits. IEEE Trans. Circuits Syst. I Regul. Pap. 2009, 56, 2544–2555. [Google Scholar]

- Razavi, B. Challenges in the design high-speed clock and data recovery circuits. IEEE Commun. Mag. 2002, 40, 94–101. [Google Scholar] [CrossRef]

- Jeong, G.-S.; Chi, H.; Kim, K.; Jeong, D.-K. A 20-Gb/s 1.27 pJ/b low-power optical receiver front-end in 65 nm CMOS, Circuits and Systems (ISCAS). In Proceedings of the IEEE Symposium on Circuits and Systems (ISCAS), Melbourne, Australia, 1–5 June 2014; pp. 1492–1495. [Google Scholar]

- Kao, T.S.-C.; Musa, F.A.; Carusone, A.C. A 5-Gbit/s CMOS optical receiver with integrated spatially modulated light detector and equalization. IEEE Trans. Circuits Syst. I Regul. Pap. 2010, 57, 2844–2857. [Google Scholar] [CrossRef]

- Razavi, B. Fundamentals of Microelectronics; Wiley: New York, NY, USA, 2009. [Google Scholar]

- Razavi, B. Design of Integrated Circuits for Optical Communications; McGraw-Hill: New York, NY, USA, 2002. [Google Scholar]

- Bulzacchelli, J.F.; Meghelli, M.; Rylov, S.V.; Rhee, W.; Rylyakov, A.V.; Ainspan, H.A.; Parker, B.D.; Beakes, M.P.; Chung, A.; Beukema, T.J. A 10-Gb/s 5-tap DFE/4-tap FFE transceiver in 90-nm CMOS technology. IEEE J. Solid-State Circuits 2006, 41, 2885–2900. [Google Scholar] [CrossRef]

- Kimura, H.; Aziz, P.M.; Jing, T.; Sinha, A.; Kotagiri, S.P.; Narayan, R.; Gao, H.; Jing, P.; Hom, G.; Liang, A. A 28 Gb/s 560 mW multi-standard SerDes with single-stage analog front-end and 14-tap decision feedback equalizer in 28 nm CMOS. IEEE J. Solid-State Circuits 2014, 49, 3091–3103. [Google Scholar] [CrossRef]

- Kajley, R.S.; Hurst, P.J.; Brown, J.E. A mixed-signal decision-feedback equalizer that uses a look-ahead architecture. IEEE J. Solid-State Circuits 1997, 32, 450–459. [Google Scholar] [CrossRef]

- Stojanovic, V.; Ho, A.; Garlepp, B.W.; Chen, F.; Wei, J.; Tsang, G.; Alon, E.; Kollipara, R.T.; Werner, C.W.; Zerbe, J.L. Autonomous dual-mode (PAM2/4) serial link transceiver with adaptive equalization and data recovery. IEEE J. Solid-State Circuits 2005, 40, 1012–1026. [Google Scholar] [CrossRef]

- Wong, K.-L.J.; Chen, E.-H.; Yang, C.-K.K. Edge and data adaptive equalization of serial-link transceivers. IEEE J. Solid-State Circuits 2008, 43, 2157–2169. [Google Scholar] [CrossRef]

- Wang, H.; Lee, J. A 21-Gb/s 87-mW transceiver with FFE/DFE/analog equalizer in 65-nm CMOS technology. IEEE J. Solid-State Circuits 2010, 45, 909–920. [Google Scholar] [CrossRef]

- Sharif-Bakhtiar, A.; Carusone, A.C. A 20 Gb/s CMOS Optical Receiver With Limited-Bandwidth Front End and Local Feedback IIR-DFE. IEEE J. Solid-State Circuits 2016, 51, 2679–2689. [Google Scholar] [CrossRef]

- Kim, J.; Jeong, D.-K. Multi-gigabit-rate clock and data recovery based on blind oversampling. IEEE Commun. Mag. 2003, 41, 68–74. [Google Scholar]

- Nikolic, B.; Oklobdzija, V.G.; Stojanovic, V.; Jia, W.; Chiu, J.K.-S.; Leung, M.M.-T. Improved sense-amplifier-based flip-flop: Design and measurements. IEEE J. Solid-State Circuits 2000, 35, 876–884. [Google Scholar] [CrossRef]

- Kim, J.; Leibowitz, B.S.; Ren, J.; Madden, C.J. Simulation and analysis of random decision errors in clocked comparators. IEEE Trans. Circuits Syst. I Regul. Pap. 2009, 56, 1844–1857. [Google Scholar] [CrossRef]

- Bae, W.; Jeong, G.-S.; Park, K.; Cho, S.-Y.; Kim, Y.; Jeong, D.-K. A 0.36 pJ/bit, 0.025 mm2, 12.5 Gb/s Forwarded-Clock Receiver With a Stuck-Free Delay-Locked Loop and a Half-Bit Delay Line in 65-nm CMOS Technology. IEEE Trans. Circuits Syst. I Regul. Pap. 2016, 63, 1393–1403. [Google Scholar] [CrossRef]

- Hsieh, M.-T.; Sobelman, G.E. Architectures for multi-gigabit wire-linked clock and data recovery. IEEE Circuits Syst. Mag. 2008, 8, 45–57. [Google Scholar] [CrossRef]

- Casper, B.; O’Mahony, F. Clocking analysis, implementation and measurement techniques for high-speed data links—A tutorial. IEEE Trans. Circuits Syst. I Regul. Pap. 2009, 56, 17–39. [Google Scholar] [CrossRef]

- Kim, J. Design of CMOS Adaptive-Supply Serial Links. Ph.D. Thesis, Stanford University, Stanford, CA, USA, 2002. [Google Scholar]

- Hwang, M.-S.; Lee, S.-Y.; Kim, J.-K.; Kim, S.; Jeong, D.-K. A 180-Mb/s to 3.2-Gb/s, continuous-rate, fast-locking CDR without using external reference clock. In Proceedings of the IEEE Asian Solid-State Circuits Conference (A-SSCC), Jeju City, Korea, 12–14 November 2007; pp. 144–147. [Google Scholar]

- Wu, K.-C.; Lee, J. A 2 × 25-Gb/s Receiver with 2: 5 DMUX for 100-Gb/s Ethernet. IEEE J. Solid-State Circuits 2010, 45, 2421–2432. [Google Scholar]

- Emami-Neyestanak, A.; Palermo, S.; Lee, H.-C.; Horowitz, M. CMOS transceiver with baud rate clock recovery for optical interconnects. In Proceedings of the IEEE Symposium on VLSI Circuits Digest of Technical Papers, Honolulu, HI, USA, 17–19 June 2004; pp. 410–413. [Google Scholar]

- Sidiropoulos, S.; Horowitz, M.A. A semidigital dual delay-locked loop. IEEE J. Solid-State Circuits 1997, 32, 1683–1692. [Google Scholar] [CrossRef]

- Lo, S.-H.; Buchanan, D.; Taur, Y.; Wang, W. Quantum-mechanical modeling of electron tunneling current from the inversion layer of ultra-thin-oxide nMOSFET’s. IEEE Electron Device Lett. 1997, 18, 209–211. [Google Scholar] [CrossRef]

- Holzer, R. A 1 V CMOS PLL designed in high-leakage CMOS process operating at 10–700 MHz. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 7 February 2002; pp. 272–273. [Google Scholar]

- Chen, J.-S.; Ker, M.-D. Impact of gate leakage on performances of phase-locked loop circuit in nanoscale CMOS technology. IEEE Trans. Electron Devices 2009, 56, 1774–1779. [Google Scholar] [CrossRef]

- Hung, C.-C.; Liu, S.-I. A leakage-compensated PLL in 65-nm CMOS technology. IEEE Trans. Circuits Syst. II Express Br. 2009, 56, 525–529. [Google Scholar] [CrossRef]

- Bae, W.; Ju, H.; Jeong, D.-K. Design of a Transceiver Transmitting Power, Clock, and Data over a Single Optical Fiber for Future Automotive Network System. J. Semicond. Technol. Sci. 2017, 17, 48–55. [Google Scholar] [CrossRef]

| [44] | [45] | [47] | [50] | [52] | [55] | [56] | [43] | |

|---|---|---|---|---|---|---|---|---|

| Integration method | Monolithic | Monolithic | Monolithic | Monolithic | Hybrid | Hybrid | Hybrid | Hybrid |

| Technology (EIC) | 130 nm SOI | 130 nm SOI | 130 nm SOI | 180 nm Bulk | 90 nm bulk | 65 nm bulk | 28 nm bulk | 40 nm bulk |

| Technology (PIC) | GaAs | GaAs | 28 nm SOI | 130 nm SOI | ||||

| Wavelength | 1535–1555 nm | 1549–1554 nm | 1560 nm | 1280–1295 nm | 850 nm | 850 nm | 1556 nm | 1550 nm |

| # of WDM channels | N/A | 4 | N/A | 9 | N/A | N/A | N/A | 4 |

| Max. data rate/CH | 10 Gb/s | 10 Gb/s | 25 Gb/s | 5 Gb/s | 25 Gb/s | 10 Gb/s | 25 Gb/s | 20 Gb/s |

| Total throughput | 20 Gb/s | 40 Gb/s | 25 Gb/s | 45 Gb/s | 25 Gb/s | 600 Gb/s | 25 Gb/s | 80 Gb/s |

| TX | ||||||||

| Modulation type | MZI | MZI | MRR | MRR | VCSEL | VCSEL | MRR | MRR |

| ER | 5–6 dB | >4 dB | 6.9 dB | 6.9 dB | 5.1 dB | 5.6 dB | 6.5 dB | >7 dB |

| Power/CH | N/A | 575 mW | 208 mW | N/A | 46 mW | 69.5 mW | 72.5 mW | 32.3 mW |

| Energy efficiency/CH | N/A | 57.5 pJ/b | 8.32 pJ/b | N/A | 1.84 pJ/b | 6.95 pJ/b | 2.9 dB | 1.6 pJ/b |

| RX | ||||||||

| PD type | N/A (external) | N/A (external) | Ge waveguide | Si (defect) waveguide | GaAs (top illumination) | N/A | N/A | Ge waveguide |

| Sensitivity (BER of 10−12) @ max. data rate | −19.5 dBm | −15 dBm | −6 dBm | −7.5 dBm | −6 dBm @ 22 Gb/s | −16 dBm (estimated) | −8 dBm | −7.2 dBm |

| Power/CH | N/A | 120 mW | 48 mW | N/A | 44.4 mW | 68.2 mW | 50 mW | 11.6 mW |

| Energy efficiency/CH | N/A | 12 pJ/b | 1.92 pJ/b | N/A | 1.78 pJ/b | 6.82 pJ/b | 2 pJ/b | 0.73 pJ/b |

| Total power | 2.5 W | 3.5 W | 256 mW | 675 mW | 90.4 mW | 8.26 W | 122.5 mW | 175.6 mW |

| Total energy efficiency | 125 pJ/b | 87.5 pJ/b | 10.2 pJ/b | 15 pJ/b | 3.62 pJ/b | 13.77 pJ/b | 4.9 pJ/b | 2.2 pJ/b |

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jeong, G.-S.; Bae, W.; Jeong, D.-K. Review of CMOS Integrated Circuit Technologies for High-Speed Photo-Detection. Sensors 2017, 17, 1962. https://doi.org/10.3390/s17091962

Jeong G-S, Bae W, Jeong D-K. Review of CMOS Integrated Circuit Technologies for High-Speed Photo-Detection. Sensors. 2017; 17(9):1962. https://doi.org/10.3390/s17091962

Chicago/Turabian StyleJeong, Gyu-Seob, Woorham Bae, and Deog-Kyoon Jeong. 2017. "Review of CMOS Integrated Circuit Technologies for High-Speed Photo-Detection" Sensors 17, no. 9: 1962. https://doi.org/10.3390/s17091962