A Modular Multilevel Converter with Power Mismatch Control for Grid-Connected Photovoltaic Systems

Abstract

:1. Introduction

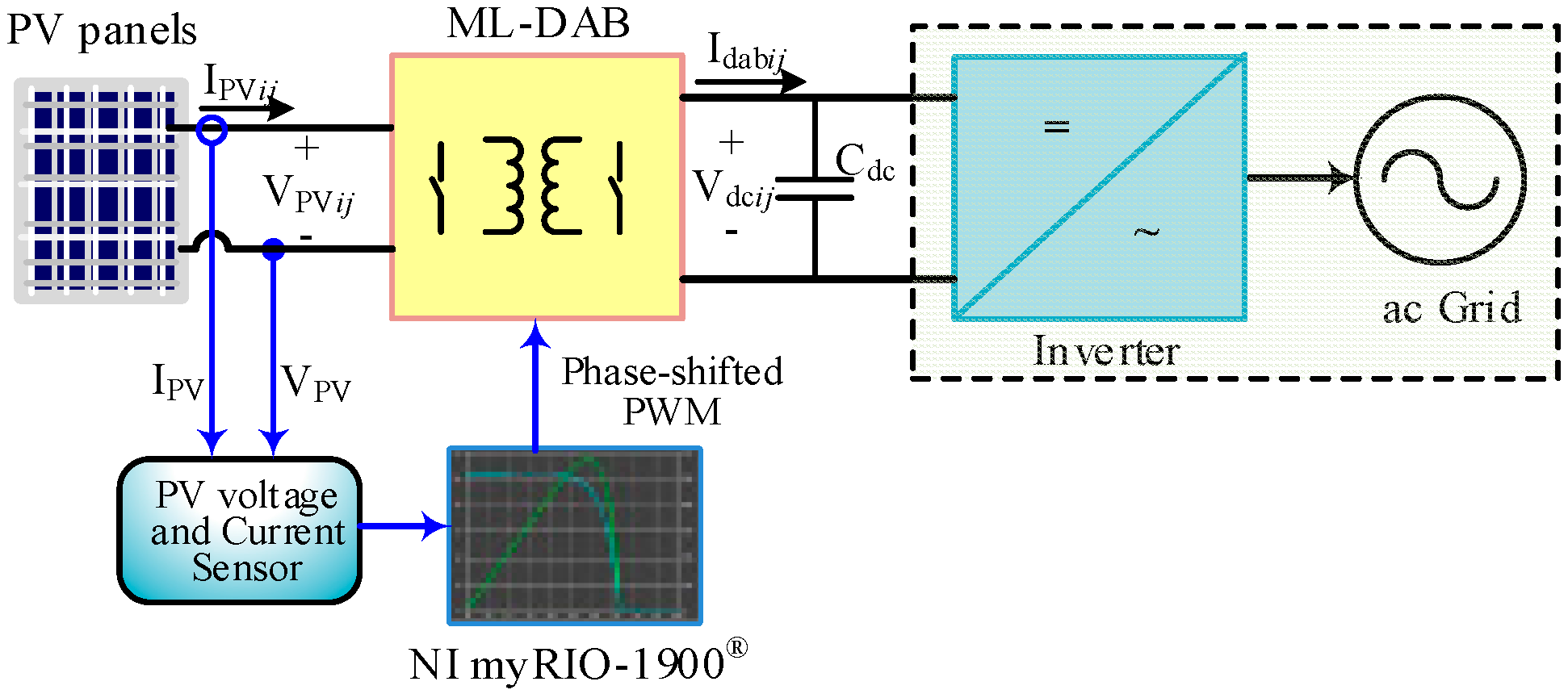

2. Proposed N-Port Converter Architecture

2.1. dc-dc Power Conversion Stage

2.1.1. Power Flow through the dc-dc ML-DAB

2.1.2. Soft-Switching Operation of ML-DAB

2.1.3. Transformer Design

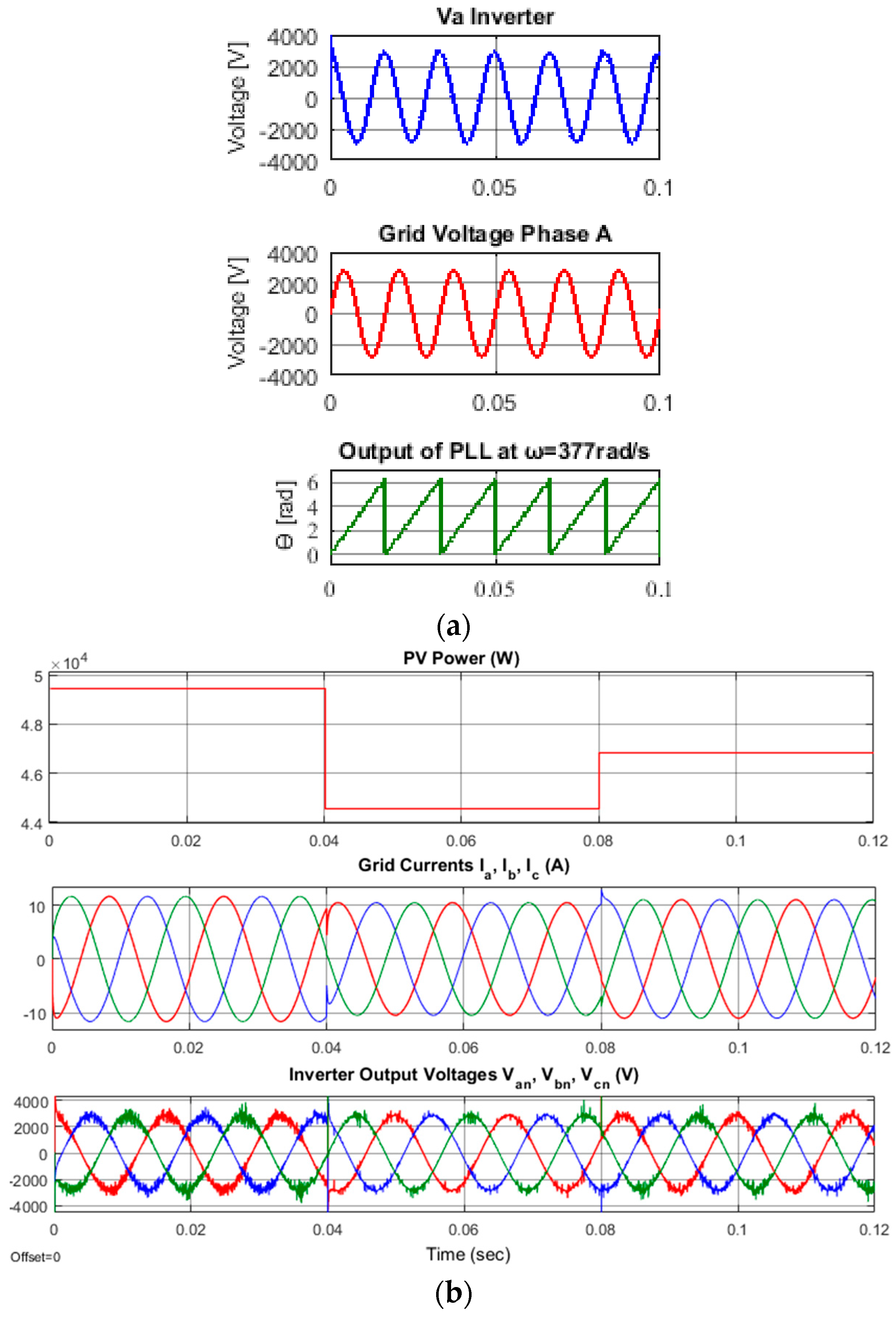

2.2. Three-Level NPC Bridge Inverter

2.3. Calculation of Power Stage Paramaters

2.4. Selection of Semiconductor Switches

2.4.1. Choosing Semiconductor Switches for the NPC Inverter

2.4.2. Choosing Semiconductor Switches for the ML-DAB

2.5. Cost-Effectiveness of the Proposed N-Port Converter

2.6. Global Efficiency of the Proposed N-Port Converter

3. Control of N-Port Converter

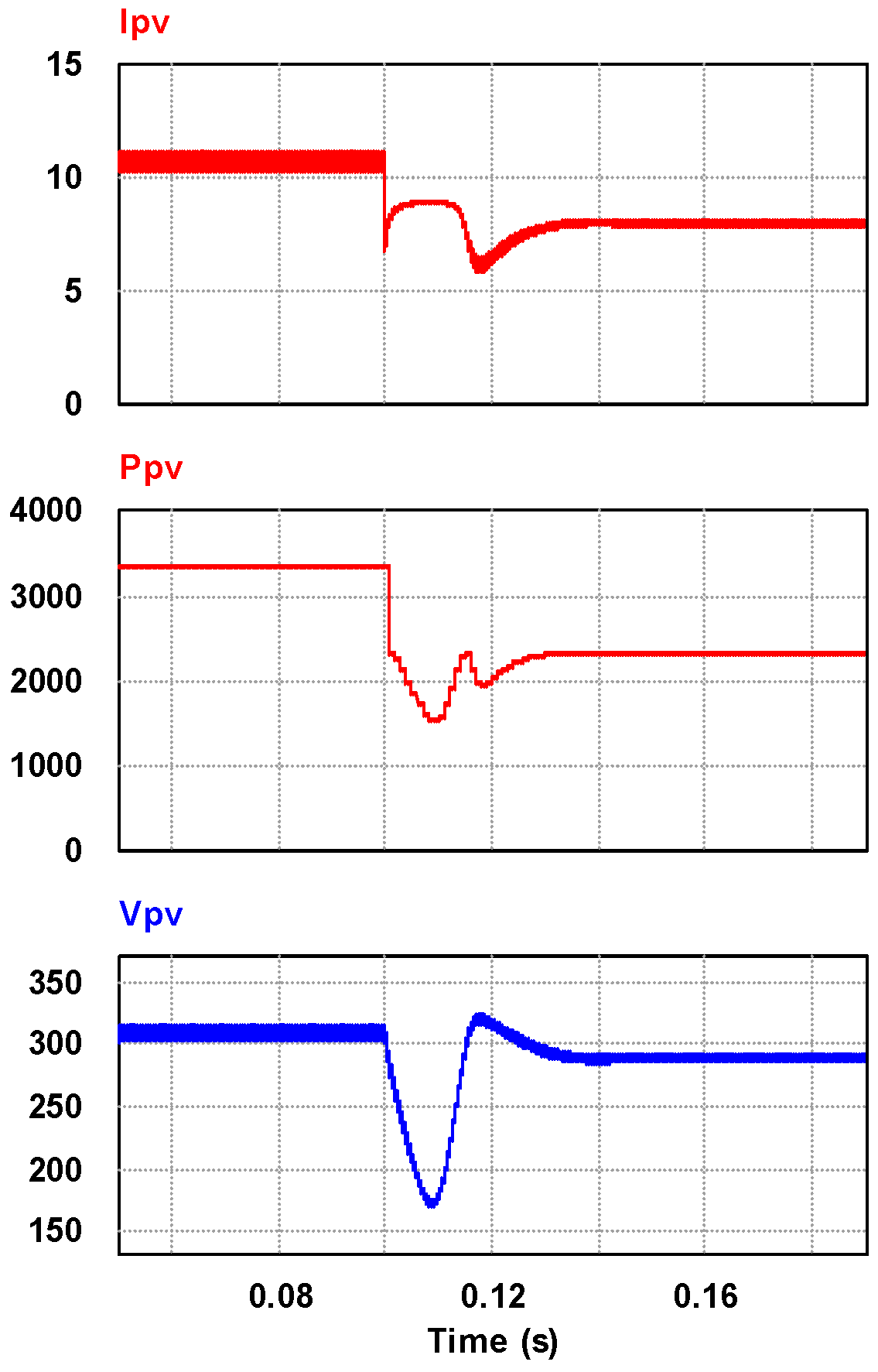

3.1. PV Modelling and MPPT Control

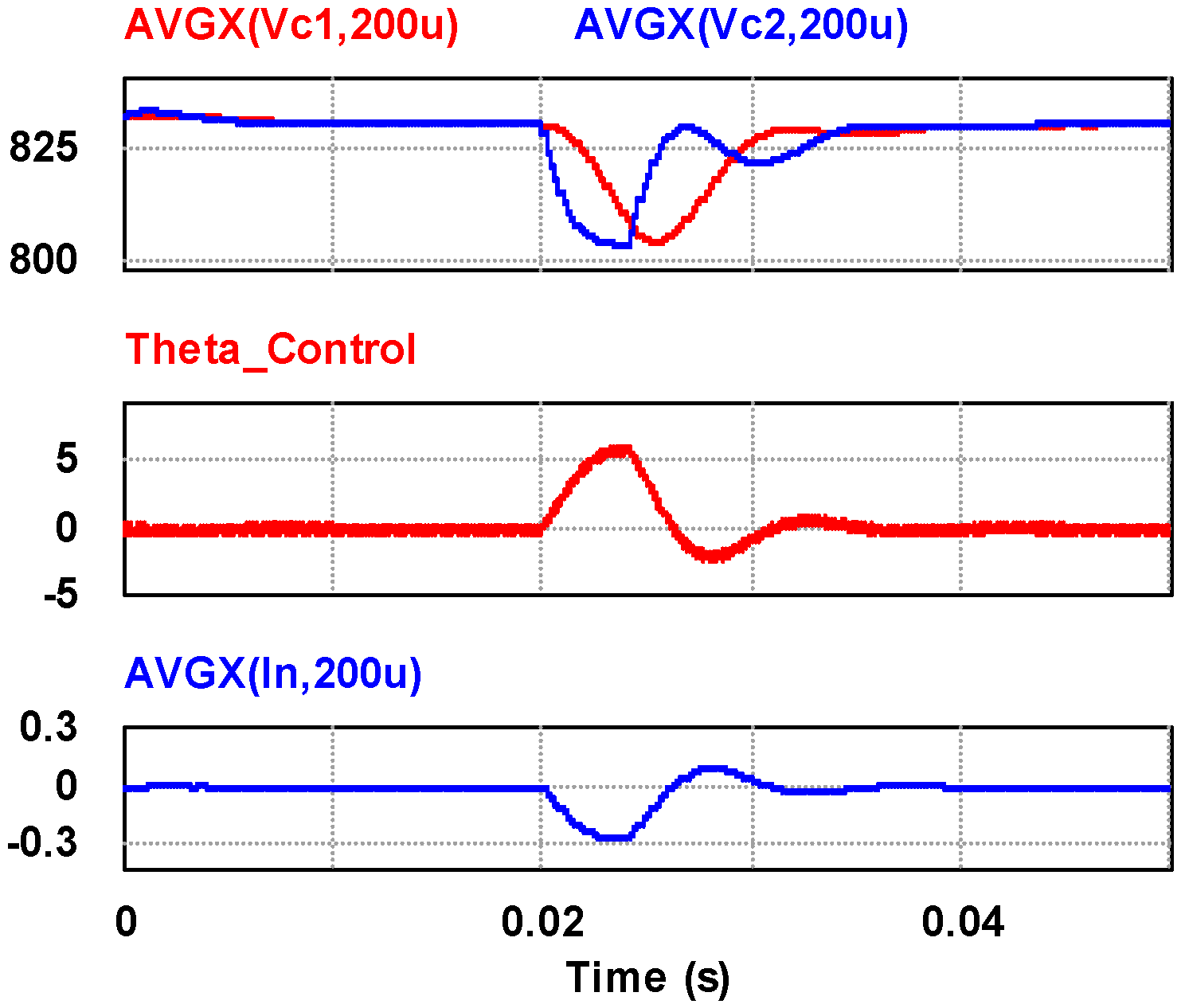

3.2. Capacitor Voltage Mismatch Control at the ML-DAB

3.3. dc-Link Voltage Control Using Power Mismatch among N Ports

3.4. (N − 1) Redundancy

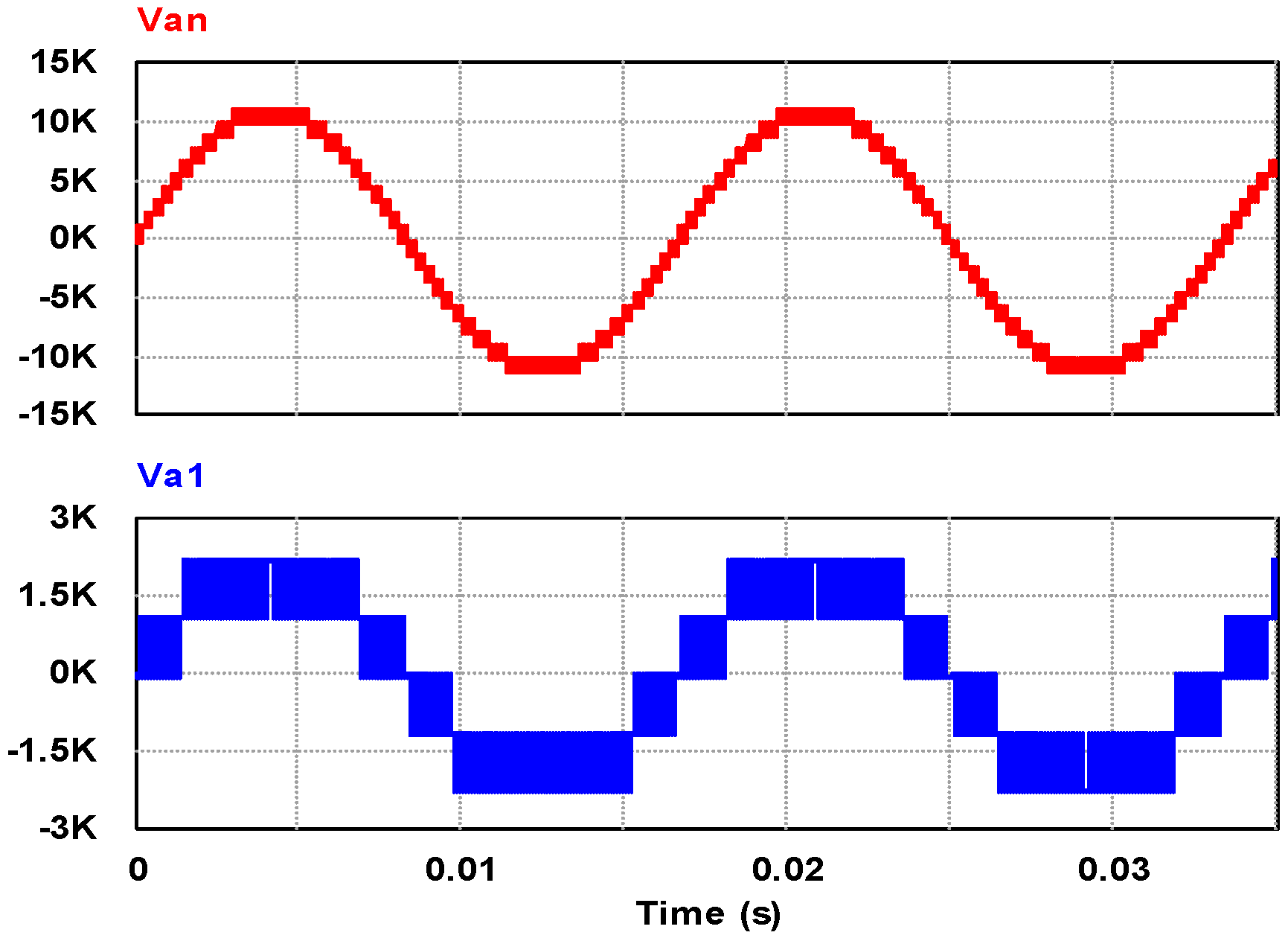

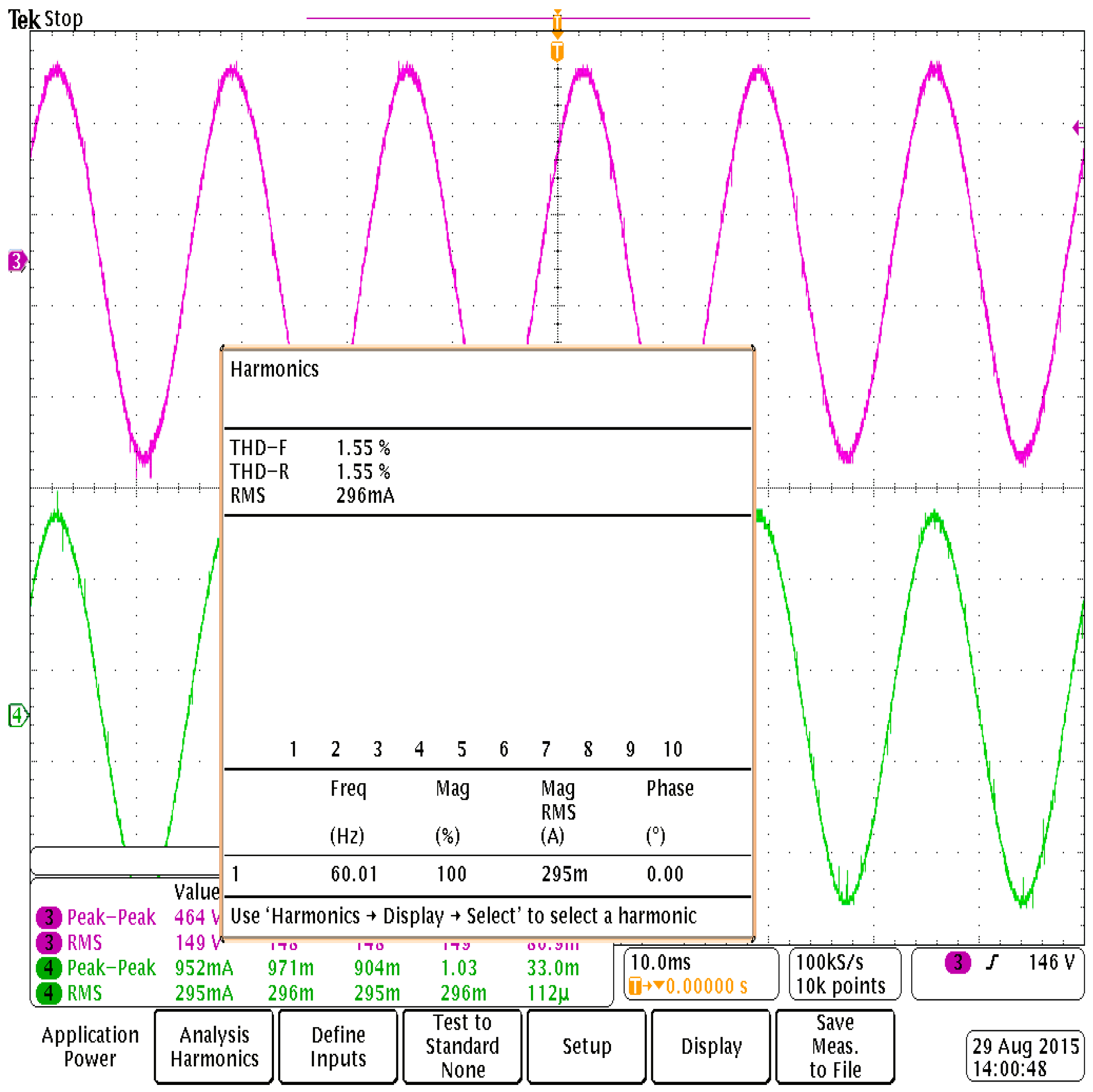

4. Simulation and Experimental Results

5. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- ALENCON. Available online: http://alenconsystems.com/wp-content/uploads/2014/10/GrIP_Datasheet-2.pdf (accessed on 16 May 2015).

- Schmalzel, J.; Jansson, P.; Schmalzel, D.; Schwabe, U.; Fishman, O. Novel inverter technology reduces utility-scale pv system costs. In Proceedings of the 2011 37th IEEE Photovoltaic Specialists Conference (PVSC), Seattle, WA, USA, 19–24 June 2011; pp. 1869–1871. [Google Scholar] [CrossRef]

- Idaho_National_Lab. Transformer Efficiency Assessment—Okinawa, Japan. Available online: https://inldigitallibrary.inl.gov/sti/5516342.pdf (accessed on 20 June 2014).

- Kouro, S.; Leon, J.I.; Vinnikov, D.; Franquelo, L.G. Grid-connected photovoltaic systems: An overview of recent research and emerging pv converter technology. IEEE Ind. Electron. Mag. 2015, 9, 47–61. [Google Scholar] [CrossRef]

- Calais, M.; Agelidis, V.G. Multilevel Converters for Single-Phase Grid Connected Photovoltaic Systems—An Overview. In Proceedings of the 1998 IEEE International Symposium on Industrial Electronics (ISIE’98), Pertoria, South Africa, 7–10 July 1998; Volume 221, pp. 224–229. [Google Scholar] [CrossRef]

- Freddy, T.K.S.; Rahim, N.A.; Hew, W.P.; Che, H.S. Comparison and analysis of single-phase transformerless grid-connected pv inverters. IEEE Trans. Power Electron. 2014, 29, 5358–5369. [Google Scholar] [CrossRef]

- Islam, M.R.; Guo, Y.; Zhu, J. A multilevel medium-voltage inverter for step-up-transformer-less grid connection of photovoltaic power plants. IEEE J. Photovolt. 2014, 4, 881–889. [Google Scholar] [CrossRef]

- Essakiappan, S.; Krishnamoorthy, H.S.; Enjeti, P.; Balog, R.S.; Ahmed, S. Multilevel medium-frequency link inverter for utility scale photovoltaic integration. IEEE Trans. Power Electron. 2015, 30, 3674–3684. [Google Scholar] [CrossRef]

- Kjaer, S.B.; Pedersen, J.K.; Blaabjerg, F. A review of single-phase grid-connected inverters for photovoltaic modules. IEEE Trans. Ind. Appl. 2005, 41, 1292–1306. [Google Scholar] [CrossRef]

- Meneses, D.; Blaabjerg, F.; Óscar, G.; Cobos, J.A. Review and comparison of step-up transformerless topologies for photovoltaic ac-module application. IEEE Trans. Power Electron. 2013, 28, 2649–2663. [Google Scholar] [CrossRef]

- Koutroulis, E.; Blaabjerg, F. Design optimization of transformerless grid-connected pv inverters including reliability. IEEE Trans. Power Electron. 2013, 28, 325–335. [Google Scholar] [CrossRef]

- Huang, A.Q. FREEDM SYSTEM—A vision for the future grid. In Proceedings of the IEEE PES General Meeting, Providence, RI, USA, 25–29 July 2010; pp. 1–4. [Google Scholar] [CrossRef]

- Zhang, L.; Sun, K.; Feng, L.; Wu, H.; Xing, Y. A family of neutral point clamped full-bridge topologies for transformerless photovoltaic grid-tied inverters. IEEE Trans. Power Electron. 2013, 28, 730–739. [Google Scholar] [CrossRef]

- Lesnicar, A.; Marquardt, R. An innovative modular multilevel converter topology suitable for a wide power range. In Proceedings of the 2003 IEEE Bologna Power Tech Conference, Bologna, Italy, 23–26 June 2003; Volume 3, p. 6. [Google Scholar] [CrossRef]

- Nichols, S.; Huang, J.; Ilic, M.; Casey, L.; Prestero, M. Two-stage pv power system with improved throughput and utility control capability. In Proceedings of the 2010 IEEE Conference on Innovative Technologies for an Efficient and Reliable Electricity Supply (CITRES), Waltham, MA, USA, 27–29 September 2010; pp. 110–115. [Google Scholar] [CrossRef]

- Rivera, S.; Kouro, S.; Wu, B.; Leon, J.I.; Rodriguez, J.; Franquelo, L.G. Cascaded h-bridge multilevel converter multistring topology for large scale photovoltaic systems. In Proceedings of the 2011 IEEE International Symposium on Industrial Electronics, Gdansk, Poland, 27–30 June 2011; pp. 1837–1844. [Google Scholar] [CrossRef]

- Liming, L.; Hui, L.; Yaosuo, X.; Wenxin, L. Decoupled active and reactive power control for large-scale grid-connected photovoltaic systems using cascaded modular multilevel converters. IEEE Trans. Power Electron. 2015, 30, 176–187. [Google Scholar] [CrossRef]

- Islam, M.R.; Guo, Y.; Zhu, J. A high-frequency link multilevel cascaded medium-voltage converter for direct grid integration of renewable energy systems. IEEE Trans. Power Electron. 2014, 29, 4167–4182. [Google Scholar] [CrossRef]

- Tripathi, A.; Mainali, K.; Patel, D.; Kadavelugu, A.; Hazra, S.; Bhattacharya, S.; Hatua, K. Design considerations of a 15 kV SiC IGBT enabled high-frequency isolated dc-dc converter. In Proceedings of the 2014 International Power Electronics Conference (IPEC-Hiroshima 2014—ECCE-ASIA), Hiroshima, Japan, 18–21 May 2014; pp. 758–765. [Google Scholar] [CrossRef]

- Mainali, K.; Tripathi, A.; Madhusoodhanan, S.; Kadavelugu, A.; Patel, D.; Hazra, S.; Hatua, K.; Bhattacharya, S. A transformerless intelligent power substation: A three-phase sst enabled by a 15-kV SiC IGBT. IEEE Power Electron. Mag. 2015, 2, 31–43. [Google Scholar] [CrossRef]

- Yuxiang, S.; Rui, L.; Yaosuo, X.; Hui, L. High-frequency-link-based grid-tied pv system with small dc-link capacitor and low-frequency ripple-free maximum power point tracking. IEEE Trans. Power Electron. 2016, 31, 328–339. [Google Scholar] [CrossRef]

- Zhao, T.; Wang, G.; Bhattacharya, S.; Huang, A.Q. Voltage and power balance control for a cascaded h-bridge converter-based solid-state transformer. IEEE Trans. Power Electron. 2013, 28, 1523–1532. [Google Scholar] [CrossRef]

- Kouro, S.; Wu, B.; Moya, A.; Villanueva, E.; Correa, P.; Rodriguez, J. Control of a cascaded h-bridge multilevel converter for grid connection of photovoltaic systems. In Proceedings of the 2009 35th Annual Conference of IEEE Industrial Electronics (IECON’09), Porto, Portugal, 3–5 November 2009; pp. 3976–3982. [Google Scholar] [CrossRef]

- Vijay Vittal, R.A. Grid Integration and Dynamic Impact of Wind Energy; Springer: New York, NY, USA, 2013; ISBN 978-1-4419-9323-6. [Google Scholar]

- Wang, L.; Zhang, D.; Wang, Y.; Wu, B.; Athab, H. Power and voltage balance control of a novel three-phase solid state transformer using multilevel cascaded h-bridge inverters for microgrid applications. IEEE Trans. Power Electron. 2015, 31, 3289–3301. [Google Scholar] [CrossRef]

- Yu, Y.; Konstantinou, G.; Hredzak, B.; Agelidis, V.G. Power balance of cascaded h-bridge multilevel converters for large-scale photovoltaic integration. IEEE Trans. Power Electron. 2016, 31, 292–303. [Google Scholar] [CrossRef]

- Kheraluwala, M.H.; Gascoigne, R.W.; Divan, D.M.; Baumann, E.D. Performance characterization of a high-power dual active bridge. IEEE Trans. Ind. Appl. 1992, 28, 1294–1301. [Google Scholar] [CrossRef]

- Kulasekaran, S.; Ayyanar, R. Analysis, design, and experimental results of the semidual-active-bridge converter. IEEE Trans. Power Electron. 2014, 29, 5136–5147. [Google Scholar] [CrossRef]

- Moonem, M.; Pechacek, C.; Hernandez, R.; Krishnaswami, H. Analysis of a multilevel dual active bridge (ML-DAB) DC-DC converter using symmetric modulation. Electronics 2015, 4, 239. [Google Scholar] [CrossRef]

- ROHM Semiconductor. Available online: http://www.rohm.com/documents/11308/98b20d7a-0c11-4689-b4db-85150574b12c (accessed on 17 March 2015).

- Mouser Electronic Inc. Available online: http://www.mouser.com/Semiconductors/Discrete-Semiconductors/Transistors/IGBT-Modules/_/N-ax1sd/ (accessed on 24 November 2015).

- ABB Ltd. Application Note 5sya 2042-04: Failure Rates of Hipak Modules Due to Cosmic Rays; ABB Ltd.: Zurich, Switzerland, 2011. [Google Scholar]

- Jun, W.; Huang, A.; Woongje, S.; Yu, L.; Baliga, B.J. Smart grid technologies. IEEE Ind. Electron. Mag. 2009, 3, 16–23. [Google Scholar] [CrossRef]

- Wang, X.; Cooper, J.A. High-Voltage n-channel igbts on free-standing 4H-SiC epilayers. IEEE Trans. Electron. Devices 2010, 57, 511–515. [Google Scholar] [CrossRef]

- Xi, X.; Liu, S.; Kuang, J. Research of efficient dc-dc converter based on SiC power devices and zvs soft switches. In Proceedings of the 2013 1st International Future Energy Electronics Conference (IFEEC), Tainan, Taiwan, 3–6 November 2013; pp. 194–198. [Google Scholar] [CrossRef]

- Moonem, M.A.; Krishnaswami, H. Control and configuration of three-level dual-active bridge dc-dc converter as a front-end interface for photovoltaic system. In Proceedings of the 2014 Twenty-Ninth Annual IEEE, Applied Power Electronics Conference and Exposition (APEC), Fort Worth, TX, USA, 16–20 March 2014; pp. 3017–3020. [Google Scholar] [CrossRef]

- Filba-Martinez, A.; Busquets-Monge, S.; Bordonau, J. Modulation and capacitor voltage balancing control of a three-level NPC dual-active-bridge DC-DC converter. In Proceedings of the39th Annual Conference of the IEEE Industrial Electronics Society (IECON 2013), Vienna, Austria, 10–13 November 2013; pp. 6251–6256. [Google Scholar] [CrossRef]

| No. of Modules per Phase (N) | Assuming N-Nos. of CHB Modules per Phase | Assuming N-Nos. of CNPC Modules per Phase | ||||||

|---|---|---|---|---|---|---|---|---|

| Vdc at Each Port of CHB Inverter (V) | Required IGBT (kV) | VCE@100FIT (V) | DVUF (%) | Vdc/2 at Each Port of CNPC Inverter (V) | Required IGBT (kV) | VCE@100FIT (V) | DVUF (%) | |

| 3 | 3906 | >6.5 | - | - | 1953 | 4.5 | 2899 | 67.37 |

| 4 | 2930 | 6.5 | 3865 | 75.81 | 1465 | 3.3 | 1794 | 81.66 |

| 5 | 2344 | 4.5 | 2899 | 80.86 | 1172 | 2.5 | 1289 | 90.92 |

| 6 | 1953 | 4.5 | 2899 | 67.37 | 977 | 1.7 | 1072 | 91.14 |

| 7 | 1674 | 3.3 | 1794 | 93.31 | 837 | 1.7 | 1072 | 78.08 |

| 8 | 1465 | 3.3 | 1794 | 81.66 | 733 | 1.7 | 1072 | 68.38 |

| 9 | 1302 | 3.3 | 1794 | 72.58 | 651 | 1.2 | No FIT data available. Assuming 720 V (60% of VCES) | 90.42 |

| 10 | 1172 | 2.5 | 1289 | 90.92 | 586 | 1.2 | 81.39 | |

| 11 | 1065 | 1.7 | 1072 | 99.35 | 533 | 1.2 | 74.03 | |

| 12 | 977 | 1.7 | 1072 | 91.14 | 489 | 1.2 | 67.92 | |

| For a 500 kW 3-ph 13.8 kV Converter | N = 3 Ports/Phase | N = 5 Ports/Phase | N = 8 Ports/Phase | N = 12 Ports/Phase |

|---|---|---|---|---|

| Power rating of 1 ML-DAB | 55.6 kW | 33.4 kW | 20.8 kW | 13.9 kW |

| PV output voltage, Vs (for 10 or more parallel strings) | 947.7 V to 1000 V | 583.2 to 1000 V | 364.5 V to 1000 V | 291.6 V to 1000 V |

| ML-DAB output voltage, VP | 6.67 kV | 4 kV | 2.5 kV | 1.67 kV |

| HF transformer turns ratio, n = VP/Vs | 7.035 or less | 6.858 or less | 6.858 or less | 5.716 or less |

| Leakage inductor L (for minimum Vs & fs = 5 kHz) | 0.32 mH | 0.20 mH | 0.12 mH | 0.122 mH |

| ML-DAB primary IGBTs Vce | 1700 V | 1200 V | 600 V | 600 V |

| ML-DAB secondary IGBTs Vce | 4.5 kV | 3.3 kV | 1700 V | 1200 V |

| Components | Proposed N-Port Inverter |

|---|---|

| Inverters | $0.2000 |

| Transformers | Included in Inverter Cost |

| Copper Cable | $0.0252 |

| PVC conduit | $0.0085 |

| AC switchgear | $0.0337 |

| Combiners | $0.0060 |

| Concrete | $0.0059 |

| Key items above: | $0.2000 |

| Assuming rest of the project cost is same for both central and N-port inverter | |

| Overall $/watt | $1.72 |

| Item Description | Each Port (for N = 12) | Each Port (for N − 1 = 11) |

|---|---|---|

| Power Rating of 1 single DAB module | 3.34 kW | 3.34 kW |

| 291.6 V | 291.6 V | |

| 1667 V | 1820 V | |

| DAB high frequency transformer’s turn ratio, n | 5.716 | 5.716 |

| 11.43 A | 10.48 A | |

| 2 A | 1.835 A | |

| Phase-shift among CNPC inverter outputs | (N/180) =15° | ((N − 1)/180) = 16.37° |

| Hardware Component | Item Description | Quantity per Port | |

|---|---|---|---|

| PV source Emulator | MAGNA Power XR200-10 | 1 | |

| Voltage transducer | SCK-MU-1500V | 1 | |

| Current Transducer | CR5410-20 | 1 | |

| MPPT controller | NI myRIO-1900®, LabVIEW | 1 | |

| ML-DAB primary bridge | IGBT (Dual) | Infineon FF100R12YT3 | 2 |

| Capacitor | 550 V, 1200 µF | 1 | |

| High frequency transformer | Core Material | Metglass amorphous alloy 2605SA1 AMCC-125 | 1 |

| Winding turns ratio | 89:509 | - | |

| Winding wire (Round Litz Wire) | Primary: AWG 12-259/36, Secondary: AWG 20-38/30 | - | |

| ML-DAB secondary NPC bridge | IGBT (Dual) | Infineon FF100R12YT3 | 4 |

| Capacitor | 1200 V, 100 µF | 2 | |

| Clamping Diode | IXYS DSEP30-12AR | 4 | |

| NPC Inverter bridge | IGBT (Dual) | Infineon FF100R12YT3 | 4 |

| Clamping Diode | IXYS DSEP30-12AR | 4 | |

| Gate pulse generator | ML-DAB&Inverter | NI myRIO-1900®, LabVIEW | 1 |

| Load at output | R-L load | R = 500 Ω, L = 500 mH | 1 |

| Waveform measurement | Signal Oscilloscope | Tektronix MSO-4034 | 1 |

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Duman, T.; Marti, S.; Moonem, M.A.; Abdul Kader, A.A.R.; Krishnaswami, H. A Modular Multilevel Converter with Power Mismatch Control for Grid-Connected Photovoltaic Systems. Energies 2017, 10, 698. https://doi.org/10.3390/en10050698

Duman T, Marti S, Moonem MA, Abdul Kader AAR, Krishnaswami H. A Modular Multilevel Converter with Power Mismatch Control for Grid-Connected Photovoltaic Systems. Energies. 2017; 10(5):698. https://doi.org/10.3390/en10050698

Chicago/Turabian StyleDuman, Turgay, Shilpa Marti, M. A. Moonem, Azas Ahmed Rifath Abdul Kader, and Hariharan Krishnaswami. 2017. "A Modular Multilevel Converter with Power Mismatch Control for Grid-Connected Photovoltaic Systems" Energies 10, no. 5: 698. https://doi.org/10.3390/en10050698