DC Fault Analysis and Clearance Solutions of MMC-HVDC Systems

Abstract

:1. Introduction

- The first solution is to trip the AC circuit breaker (ACCB). The advantages of this method are the good economic efficiency and the high technical maturity. That is the reason most practical commercial VSC-HVDC projects use this method to clear DC line faults. Noted the slow response of the ACCB, it will take a long time for the system to recover from the DC line faults [27].

- Adopting fault blocking converters is another option [29]. To prevent IGBT damage due to overheating, converters will be blocked when the current flowing through the IGBT reaches 2 times of its rated value. Some converters may produce reversed electromotive force to impede the fault current, such as full-bridge MMC. For this solution, the speed of resuming power transmission from temporary DC faults is fast. However, more power electronic devices are needed, and the device cost and power losses increase accordingly. Compared with the half-bridge sub-modules (SMs) MMC, the converter based on full-bridge SMs needs twice insulated gate bipolar transistor (IGBT) modules and the power losses increase by about 100%; the converter based on clamp-double SMs needs 1.25 times IGBT modules and the power losses increase by about 35% [30].

- The employing of DC circuit breakers (DCCBs) is the third method for handling DC fault. In late 2012, ABB released a hybrid DCCB that can break a maximum DC fault current of 9 kA within 5 ms [31]. Technically speaking, there have been some drawbacks for the existing DCCBs, such as high manufacture cost and low technology maturity.

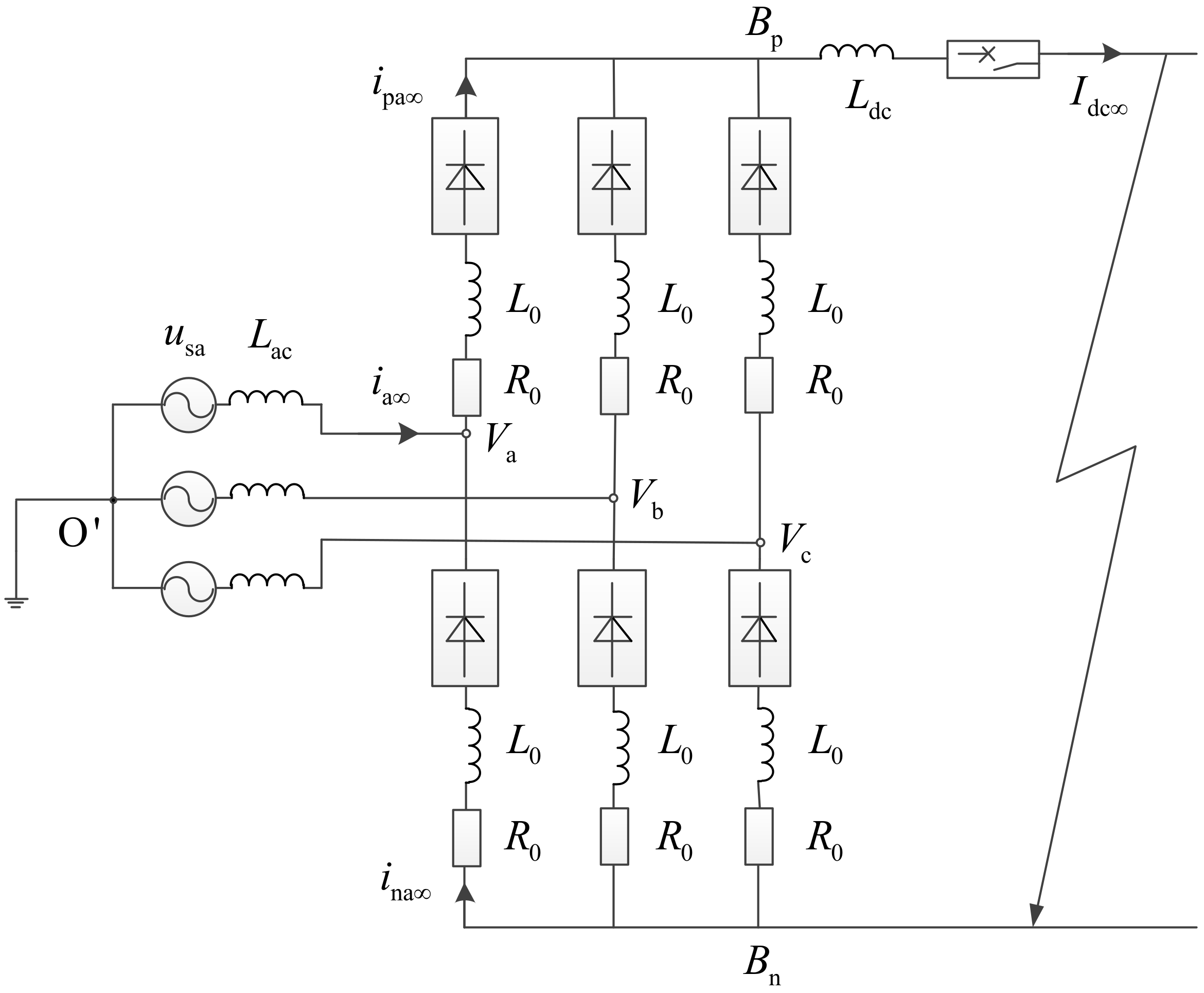

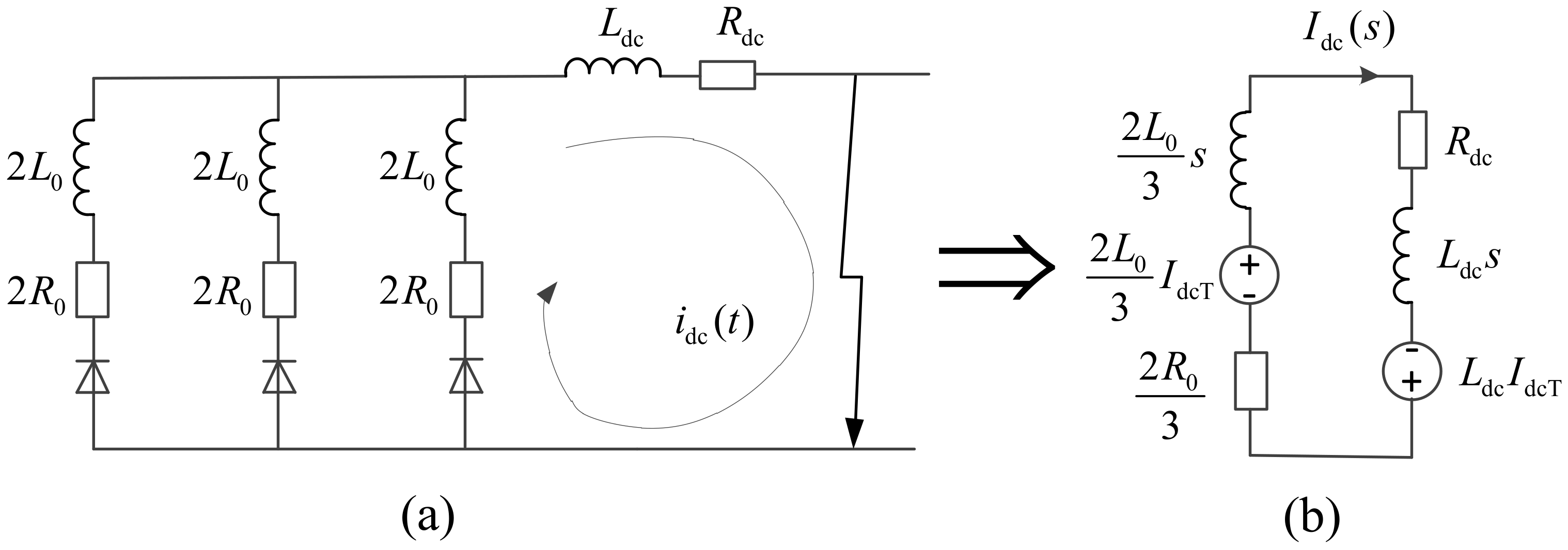

2. DC Fault Analysis of MMC before Blocking

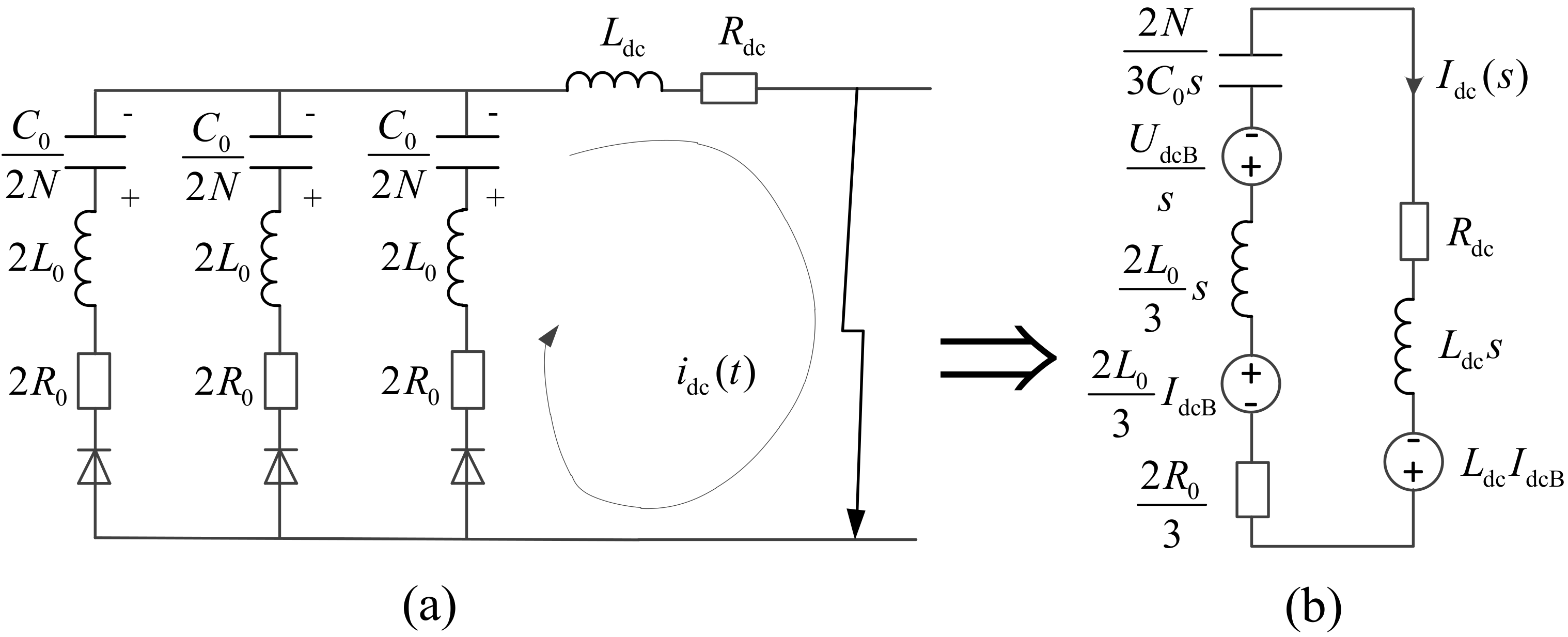

3. DC Fault Analysis of MMC after Blocking

4. Three DC Fault Clearance Solutions and Corresponding Characteristics

4.1. Solution 1: Tripping AC Circuit Breaker

4.2. Solution 2: Adopting F-MMC with DC Fault Clearance Capability

4.3. Solution 3: Adopting DC Circuit Breaker

5. Case Study

5.1. Test System

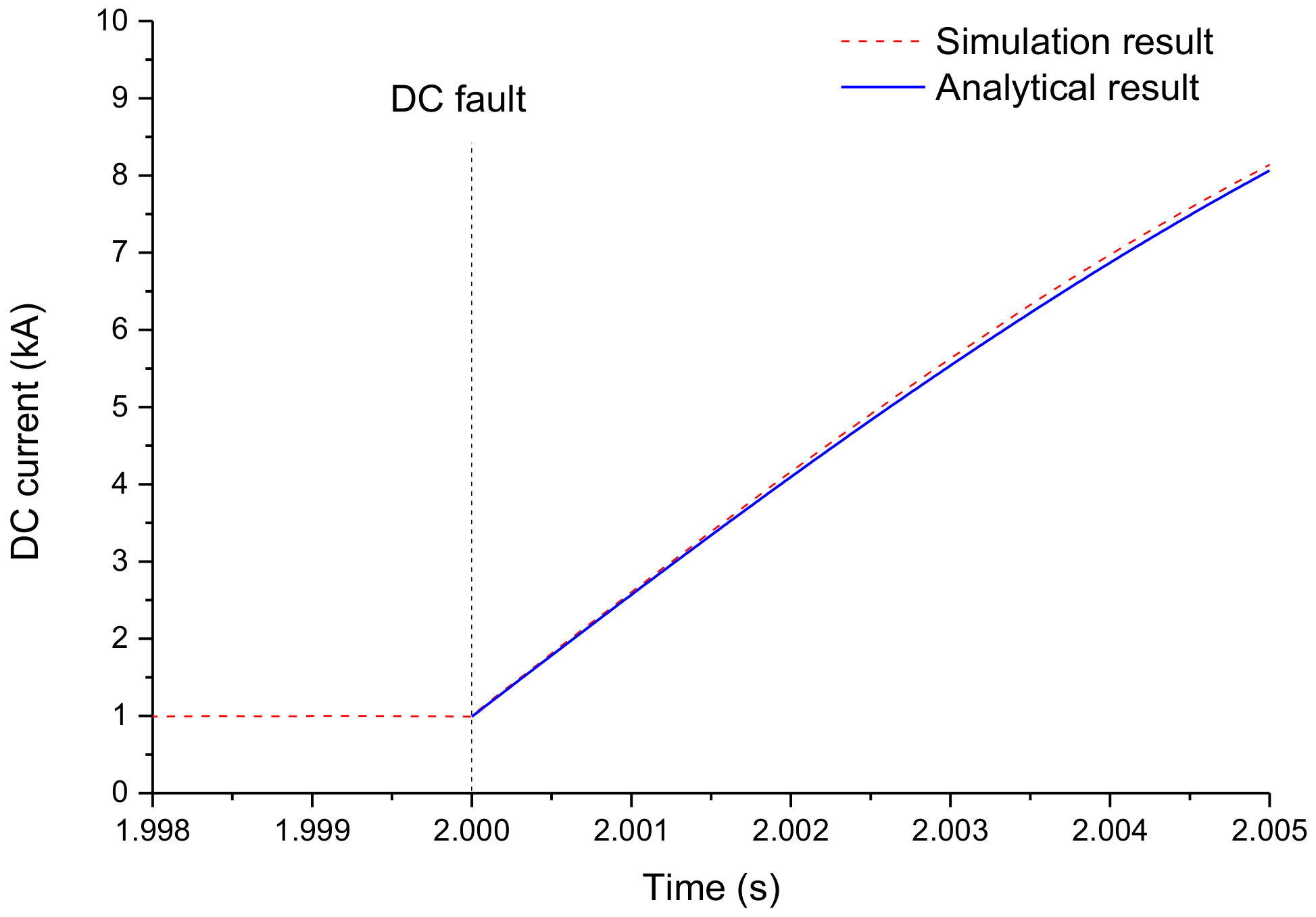

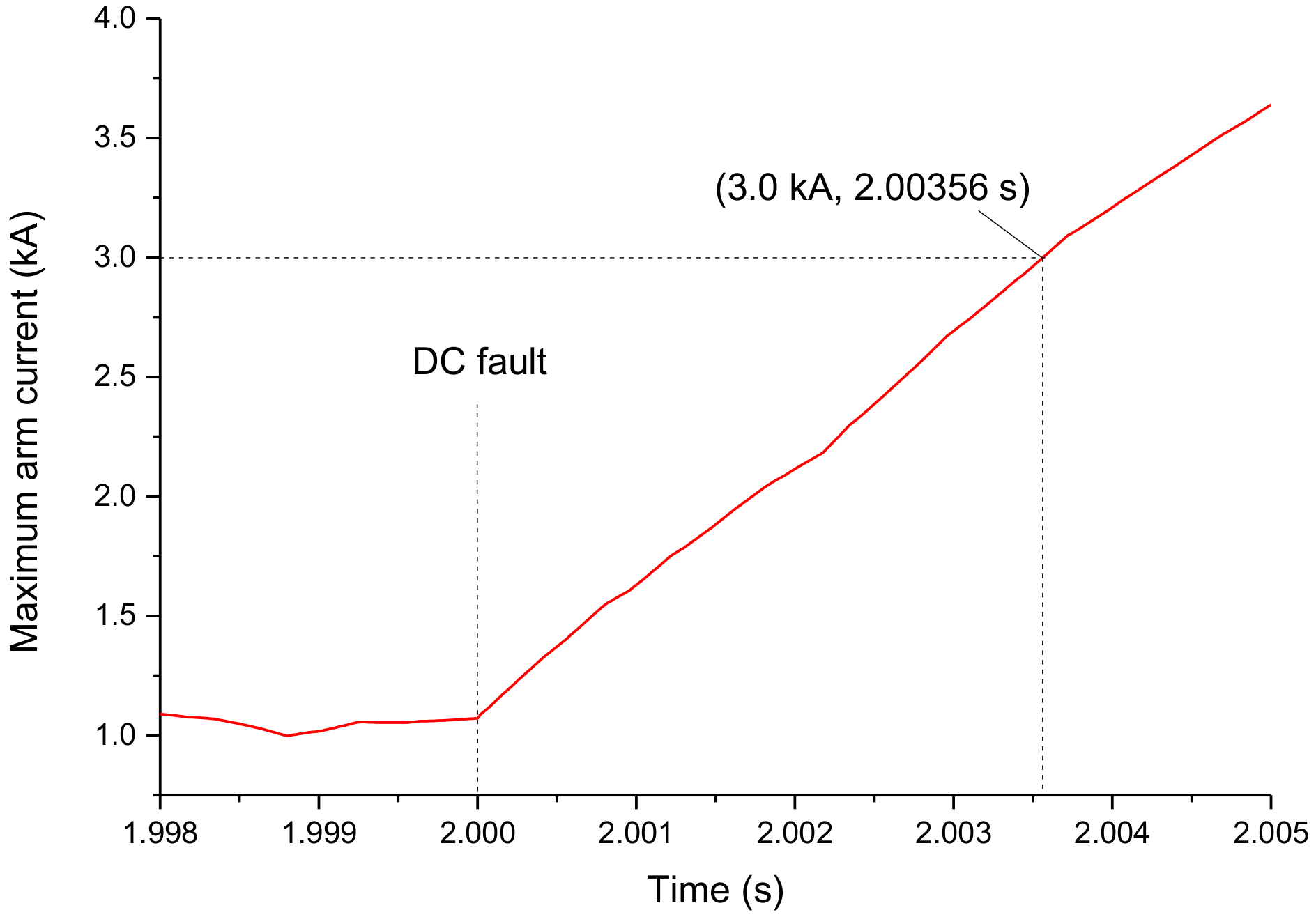

5.2. Performances of MMC Before Blocking

5.3. Performances of MMC after Blocking

5.4. Performances of MMC with Solution 1

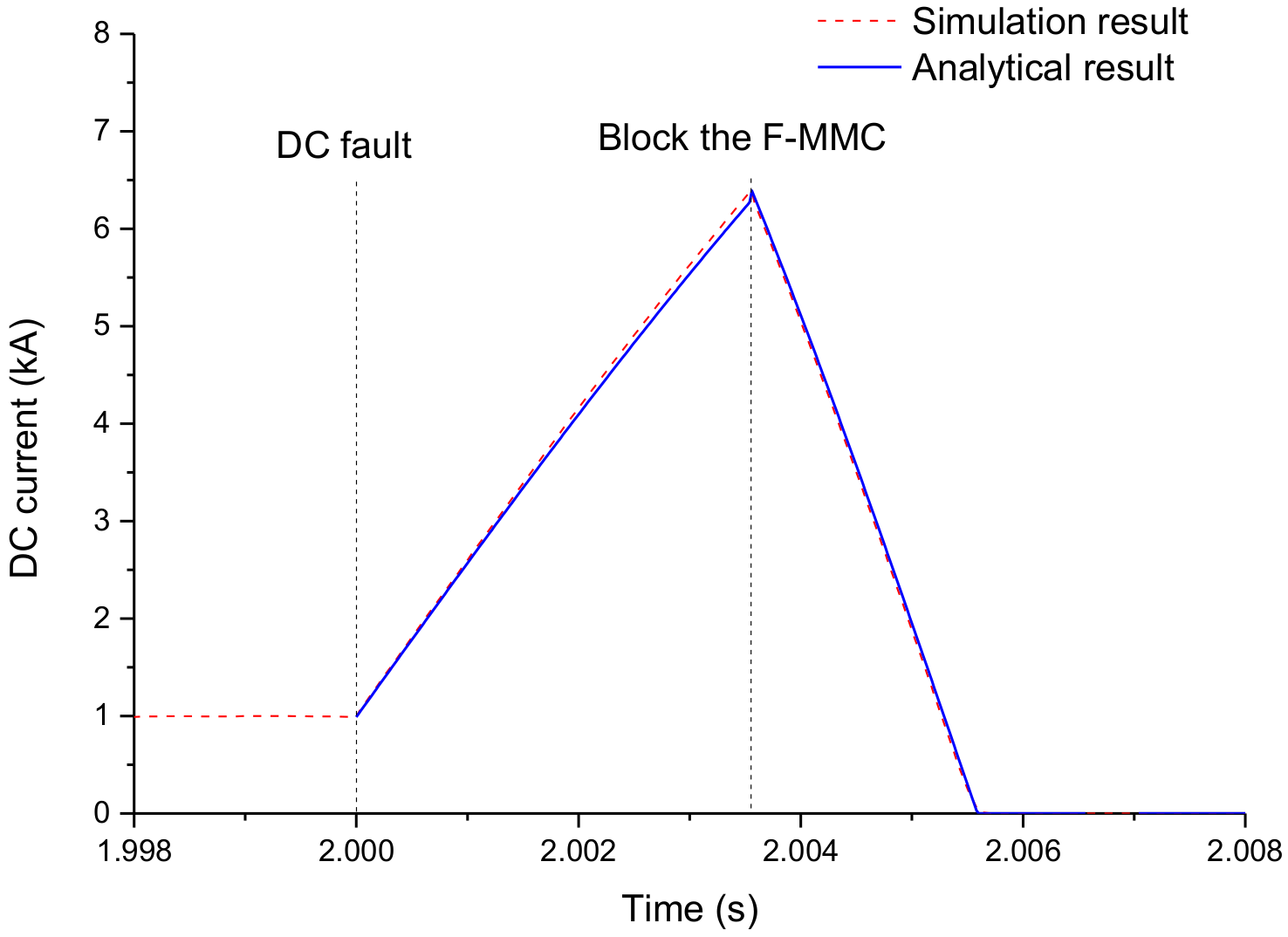

5.5. Performances of MMC with Solution 2

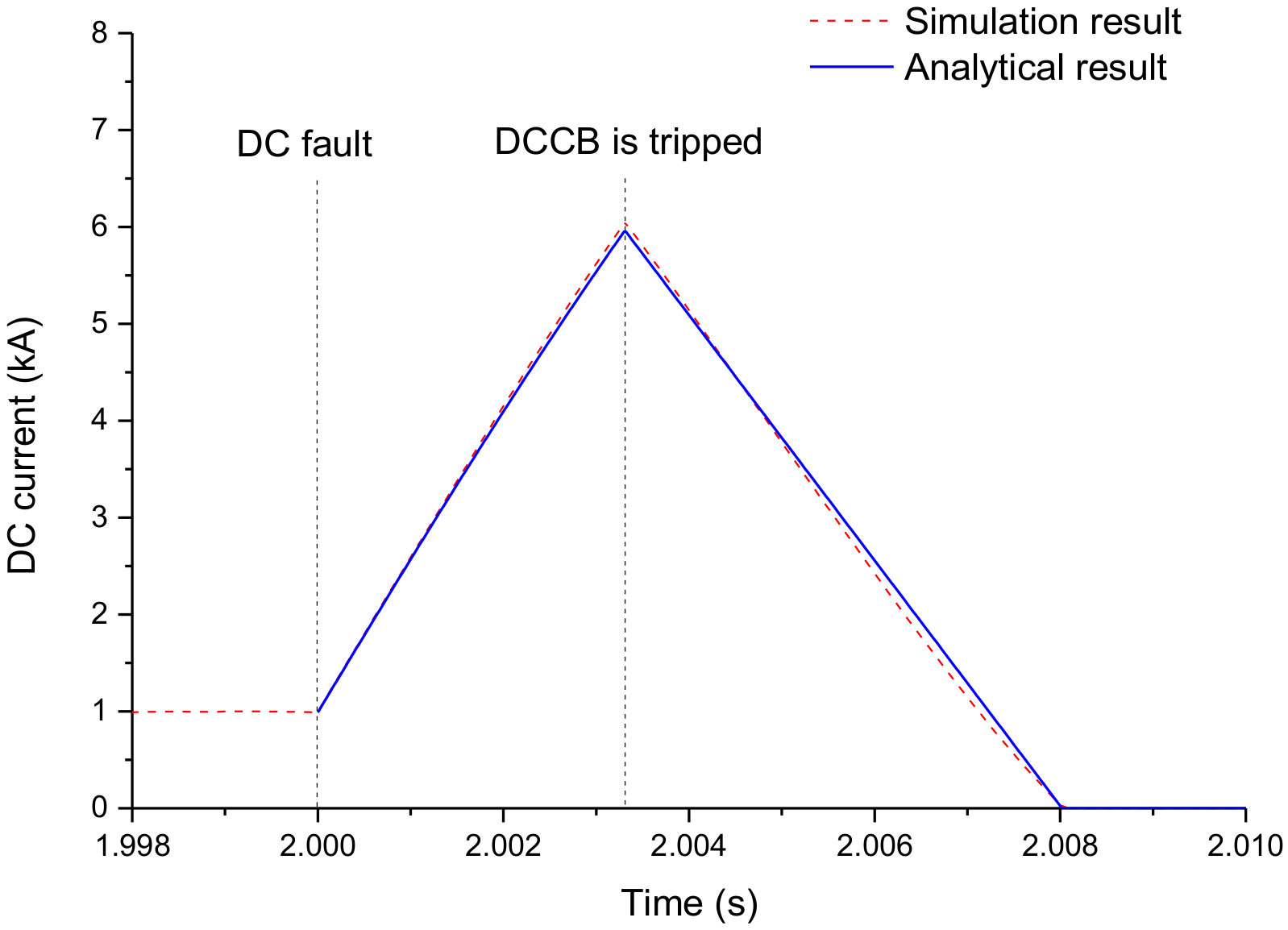

5.6. Performances of MMC with Solution 3

5.7. Comparison of Three Solutions

6. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

Appendix A

References

- Flourentzou, N.; Agelidis, V.G.; Demetriades, G.D. VSC-based HVDC power transmission systems: An overview. IEEE Trans. Power Electron. 2009, 24, 592–602. [Google Scholar] [CrossRef]

- Pinto, R.T.; Bauer, P.; Rodrigues, S.F.; Wiggelinkhuizen, E.J.; Pierik, J.; Ferreira, B. A Novel Distributed Direct-Voltage Control Strategy for Grid Integration of Offshore Wind Energy Systems through MTDC Network. IEEE Trans. Ind. Electron. 2013, 60, 2429–2441. [Google Scholar] [CrossRef]

- Marquardt, R. Stromrichterschaltungen Mit Verteilten Energiespeichern. German Patent DE10103031A1, 24 January 2001. [Google Scholar]

- Tu, Q.; Xu, Z. Impact of Sampling Frequency on Harmonic Distortion for Modular Multilevel Converter. IEEE Trans. Power Deliv. 2011, 26, 298–306. [Google Scholar] [CrossRef]

- Debnath, S.; Qin, J.; Bahrani, B.; Saeedifard, M.; Barbosa, P. Operation, Control, and Applications of the Modular Multilevel Converter: A Review. IEEE Trans. Power Electron. 2015, 30, 37–53. [Google Scholar] [CrossRef]

- Saeedifard, M.; Iravani, R. Dynamic Performance of a Modular Multilevel Back-to-Back HVDC System. IEEE Trans. Power Deliv. 2010, 25, 2903–2912. [Google Scholar] [CrossRef]

- Xue, Y.; Xu, Z.; Tang, G. Self-Start Control with Grouping Sequentially Precharge for the C-MMC-Based HVDC System. IEEE Trans. Power Deliv. 2014, 29, 187–198. [Google Scholar] [CrossRef]

- Solas, E.; Abad, G.; Barrena, J.A.; Aurtenetxea, S.; Cárcar, A.; Zając, L. Modular Multilevel Converter with Different Submodule Concepts—Part II: Experimental Validation and Comparison for HVDC Application. IEEE Trans. Ind. Electron. 2013, 60, 4536–4545. [Google Scholar] [CrossRef]

- Westerweller, T.; Friedrich, K.; Armonies, U.; Orini, A.; Parquet, D.; Wehn, S. Trans bay cable-world’s first HVDC system using multilevel voltage-sourced converter. In Proceedings of the CIGRE Session, Paris, France, 22–27 August 2010. [Google Scholar]

- Li, C.; Hu, X.; Guo, J.; Liang, J. The DC grid reliability and cost evaluation with Zhoushan five-terminal HVDC case study. In Proceedings of the 2015 50th International Universities Power Engineering Conference (UPEC), Stoke-on-Trent, UK, 1–4 September 2015. [Google Scholar]

- Nicolosi, M. Wind power integration and power system flexibility—An empirical analysis of extreme events in Germany under the new negative price regime. Energy Policy 2010, 38, 7257–7268. [Google Scholar] [CrossRef] [Green Version]

- Gnanarathna, U.N.; Gole, A.M.; Jayasinghe, R.P. Efficient Modeling of Modular Multilevel HVDC Converters (MMC) on Electromagnetic Transient Simulation Programs. IEEE Trans. Power Deliv. 2011, 26, 316–324. [Google Scholar] [CrossRef]

- Xu, J.; Zhao, C.; Liu, W.; Guo, C. Accelerated Model of Modular Multilevel Converters in PSCAD/EMTDC. IEEE Trans. Power Deliv. 2013, 28, 129–136. [Google Scholar] [CrossRef]

- Xiao, H.; Xu, Z.; Tang, G.; Xue, Y. Complete mathematical model derivation for modular multilevel converter based on successive approximation approach. IET Power Electron. 2015, 8, 2396–2410. [Google Scholar] [CrossRef]

- Guan, M.; Xu, Z. Modeling and Control of a Modular Multilevel Converter-Based HVDC System under Unbalanced Grid Conditions. IEEE Trans. Power Electron. 2012, 27, 4858–4867. [Google Scholar] [CrossRef]

- Bergna, G.; Berne, E.; Egrot, P.; Lefranc, P.; Arzande, A.; Vannier, J.C.; Molinas, M. An Energy-Based Controller for HVDC Modular Multilevel Converter in Decoupled Double Synchronous Reference Frame for Voltage Oscillation Reduction. IEEE Trans. Ind. Electron. 2013, 60, 2360–2371. [Google Scholar] [CrossRef]

- Tu, Q.; Xu, Z.; Chang, Y.; Guan, L. Suppressing DC Voltage Ripples of MMC-HVDC under Unbalanced Grid Conditions. IEEE Trans. Power Deliv. 2012, 27, 1332–1338. [Google Scholar] [CrossRef]

- Ilves, K.; Antonopoulos, A.; Norrga, S.; Nee, H.P. Steady-State Analysis of Interaction between Harmonic Components of Arm and Line Quantities of Modular Multilevel Converters. IEEE Trans. Power Electron. 2012, 27, 57–68. [Google Scholar] [CrossRef]

- Song, Q.; Liu, W.; Li, X.; Rao, H.; Xu, S.; Li, L. A Steady-State Analysis Method for a Modular Multilevel Converter. IEEE Trans. Power Electron. 2013, 28, 3702–3713. [Google Scholar] [CrossRef]

- Rafferty, J.; Xu, L.; Morrow, D.J. DC fault analysis of VSC based multi-terminal HVDC systems. In Proceedings of the 10th IET International Conference on AC and DC Power Transmission (ACDC 2012), Birmingham, UK, 4–5 December 2012. [Google Scholar]

- Yang, J.; Fletcher, J.E.; O’Reilly, J. Short-circuit and ground fault analyses and location in VSC-based DC network cables. IEEE Trans. Ind. Electron. 2012, 59, 3827–3837. [Google Scholar] [CrossRef]

- Vidal-Albalate, R.; Beltran, H.; Rolán, A.; Belenguer, E.; Peña, R.; Blasco-Gimenez, R. Analysis of the Performance of MMC Under Fault Conditions in HVDC-Based Offshore Wind Farms. IEEE Trans. Power Deliv. 2016, 31, 839–847. [Google Scholar] [CrossRef]

- Zhang, Z.; Xu, Z. Short-circuit current calculation and performance requirement of HVDC breakers for MMC-MTDC systems. IEEJ Trans. Electr. Electron. Eng. 2016, 11, 168–177. [Google Scholar] [CrossRef]

- Qin, J.; Saeedifard, M.; Rockhill, A.; Zhou, R. Hybrid Design of Modular Multilevel Converters for HVDC Systems Based on Various Submodule Circuits. IEEE Trans. Power Deliv. 2015, 30, 385–394. [Google Scholar] [CrossRef]

- Li, C.; Zhao, C.; Xu, J.; Ji, Y.; Zhang, F.; An, T. A Pole-to-Pole Short-Circuit Fault Current Calculation Method for DC Grids. IEEE Trans. Power Syst. 2017, 32, 4943–4953. [Google Scholar] [CrossRef]

- Li, B.; He, J.; Tian, J.; Feng, Y.; Dong, Y. DC fault analysis for modular multilevel converter-based system. J. Mod. Power Syst. Clean Energy 2017, 5, 275–282. [Google Scholar] [CrossRef]

- Tang, G.; Xu, Z.; Zhou, Y. Impacts of Three MMC-HVDC Configurations on AC System Stability under DC Line Faults. IEEE Trans. Power Syst. 2014, 29, 3030–3040. [Google Scholar] [CrossRef]

- Liu, G.; Xu, F.; Xu, Z.; Zhang, Z.; Tang, G. Assembly HVDC Breaker for HVDC Grids with Modular Multilevel Converters. IEEE Trans. Power Electron. 2017, 32, 931–941. [Google Scholar] [CrossRef]

- Lin, W.; Jovcic, D.; Nguefeu, S.; Saad, H. Full-Bridge MMC Converter Optimal Design to HVDC Operational Requirements. IEEE Trans. Power Deliv. 2016, 31, 1342–1350. [Google Scholar] [CrossRef]

- Modeer, T.; Nee, H.P.; Norrga, S. Loss comparison of different sub-module implementations for modular multilevel converters in HVDC applications. In Proceedings of the 2011 14th European Conference on Power Electronics and Applications, Birmingham, UK, 30 August–1 September 2011. [Google Scholar]

- Callavik, M.; Blomberg, A.; Häfner, J.; Jacobson, B. The Hybrid HVDC Breaker; ABB Grid Systems Technical Paper; ABB: Zurich, Switzerland, 2012. [Google Scholar]

| Items | Values | |

|---|---|---|

| AC Side | Rated capacity | 400 MVA |

| Grid side AC voltage | 230 kV | |

| Transformer MVA | 450 MVA | |

| Transformer ratio | 230 kV/208 kV | |

| leakage inductance | 10% | |

| DC Side | Rated DC voltage | 400 kV |

| Smoothing reactor | 200 mH | |

| Converter | Number of SMs per arm | 20 |

| SM capacitance | 666 μF | |

| Capacitor voltage | 20 kV | |

| Arm inductance | 76 mH | |

| Fault Clearance Time (ms) | Maximum Fault Current (kA) | Converter Blocked | |

|---|---|---|---|

| Solution 1 | 9318 | 10.8 | Yes |

| Solution 2 | 6.26 | 6.4 | Yes |

| Solution 3 | 8.06 | 6.0 | No |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Xu, Z.; Xiao, H.; Xiao, L.; Zhang, Z. DC Fault Analysis and Clearance Solutions of MMC-HVDC Systems. Energies 2018, 11, 941. https://doi.org/10.3390/en11040941

Xu Z, Xiao H, Xiao L, Zhang Z. DC Fault Analysis and Clearance Solutions of MMC-HVDC Systems. Energies. 2018; 11(4):941. https://doi.org/10.3390/en11040941

Chicago/Turabian StyleXu, Zheng, Huangqing Xiao, Liang Xiao, and Zheren Zhang. 2018. "DC Fault Analysis and Clearance Solutions of MMC-HVDC Systems" Energies 11, no. 4: 941. https://doi.org/10.3390/en11040941