Improvement in Voltage Conversion Ratio of Ultrahigh Step-Down Converter

Abstract

:1. Introduction

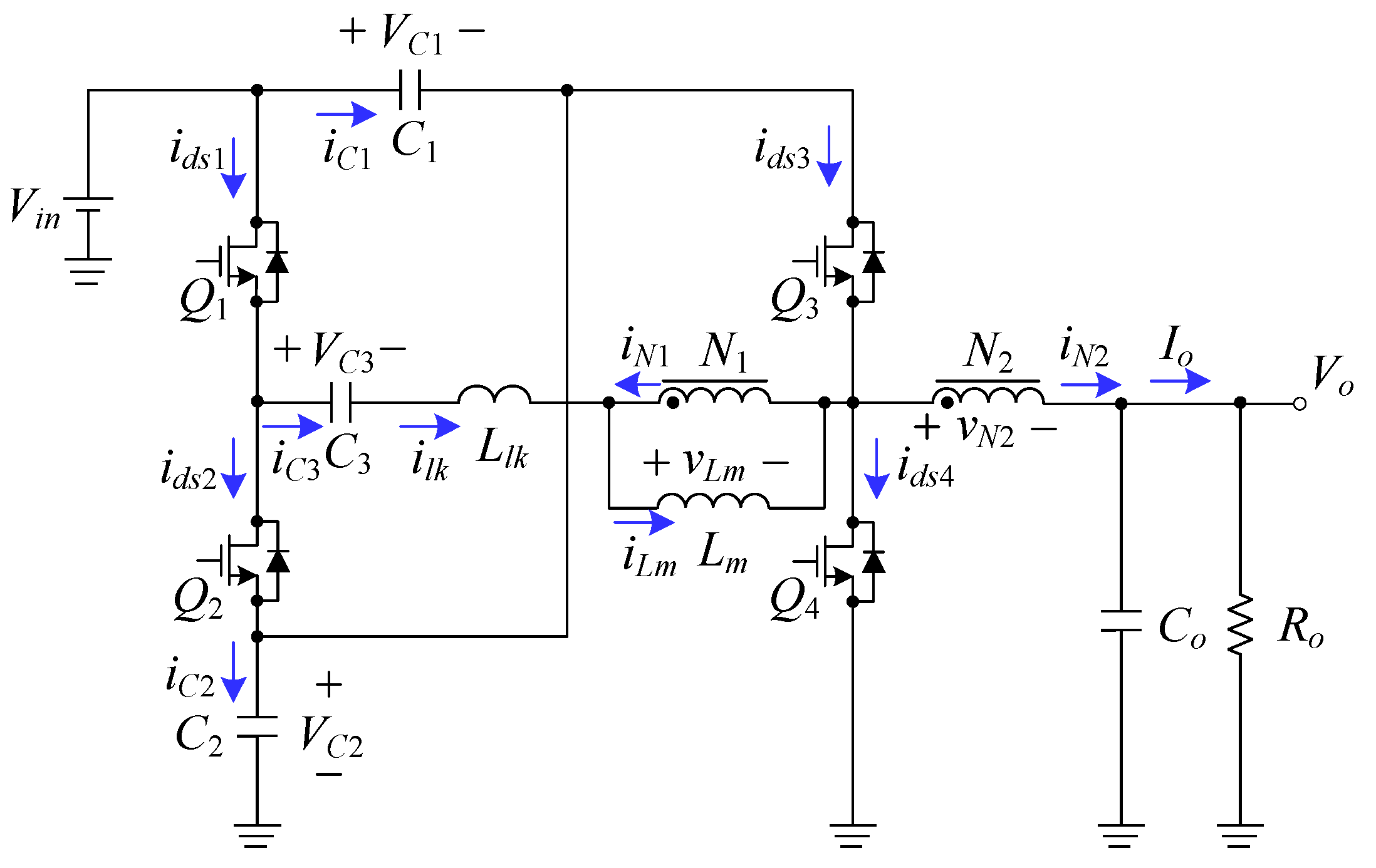

2. Circuit Configuration and Its Operating Behavior

2.1. Operating Principles

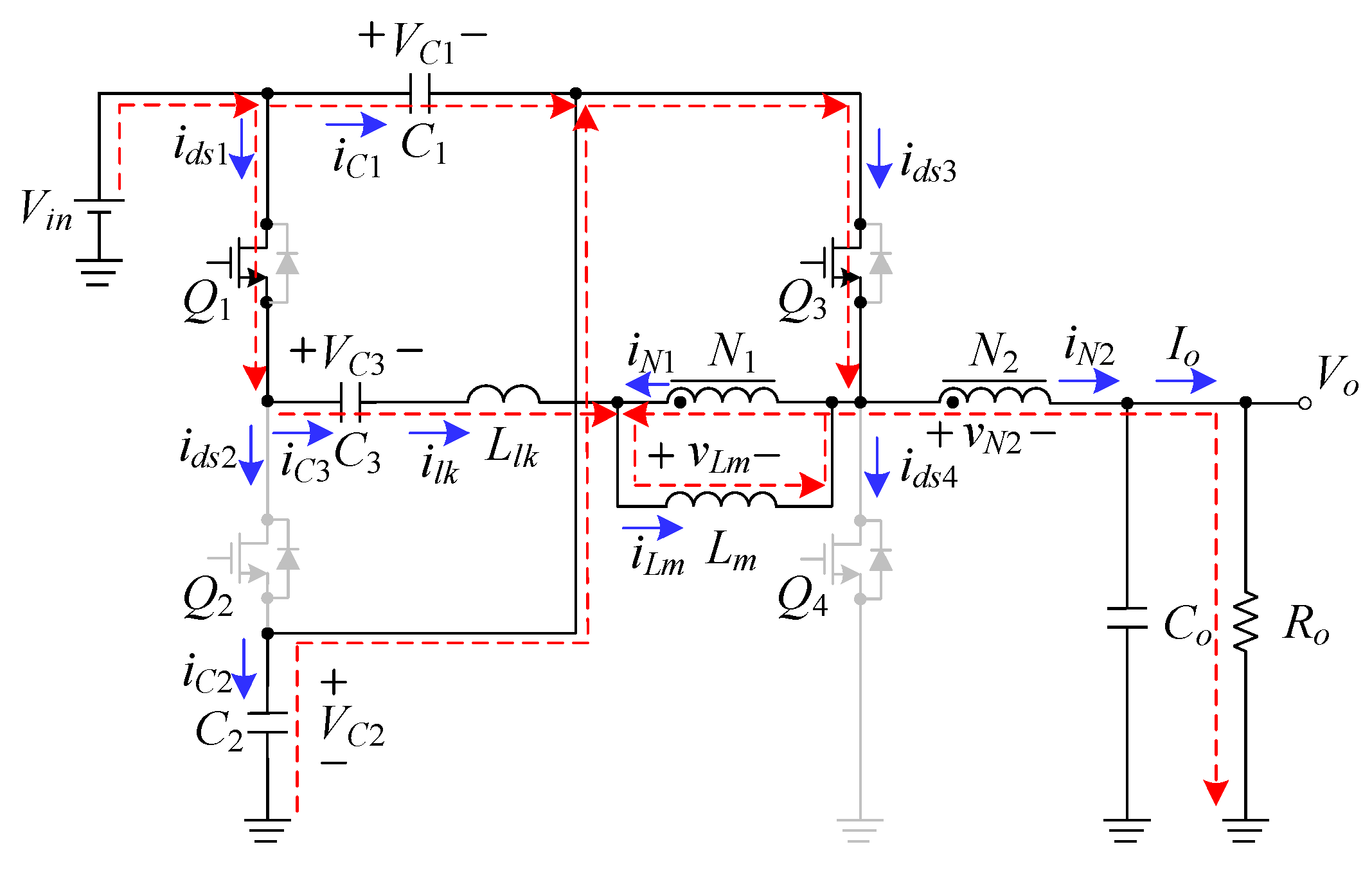

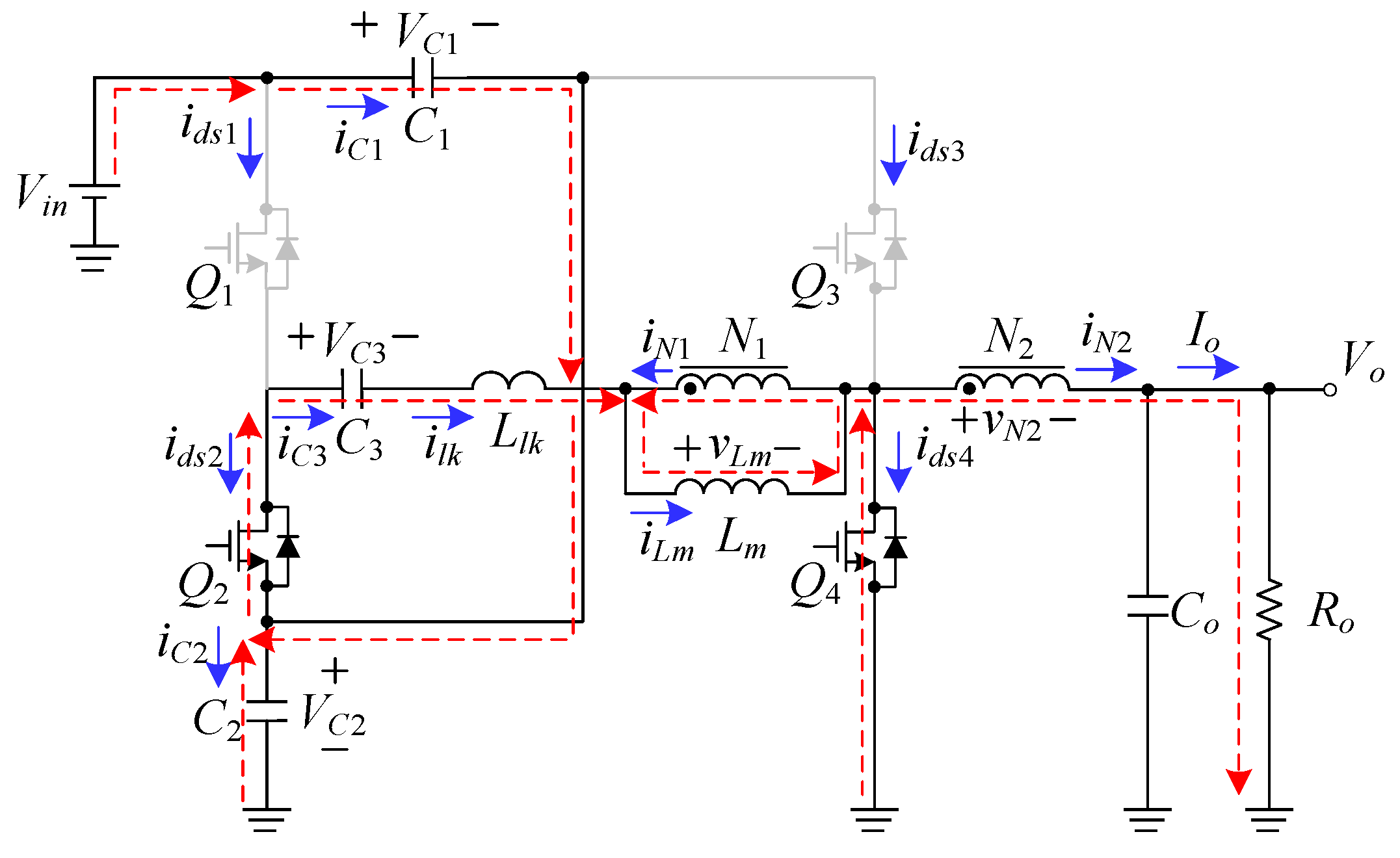

2.1.1. State 1: [t0 ≤ t ≤ t1]

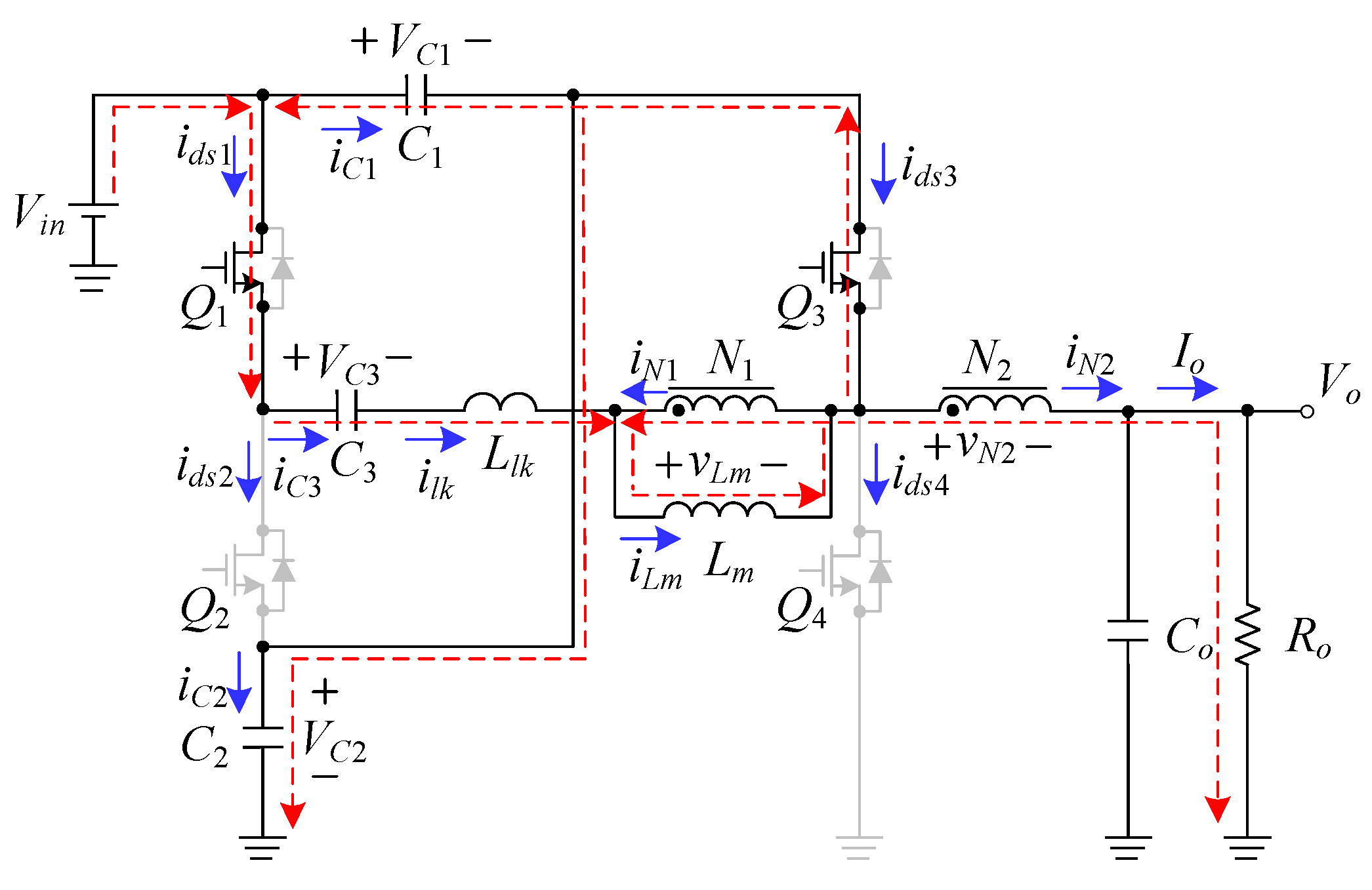

2.1.2. State 2: [t1 ≤ t ≤ t2]

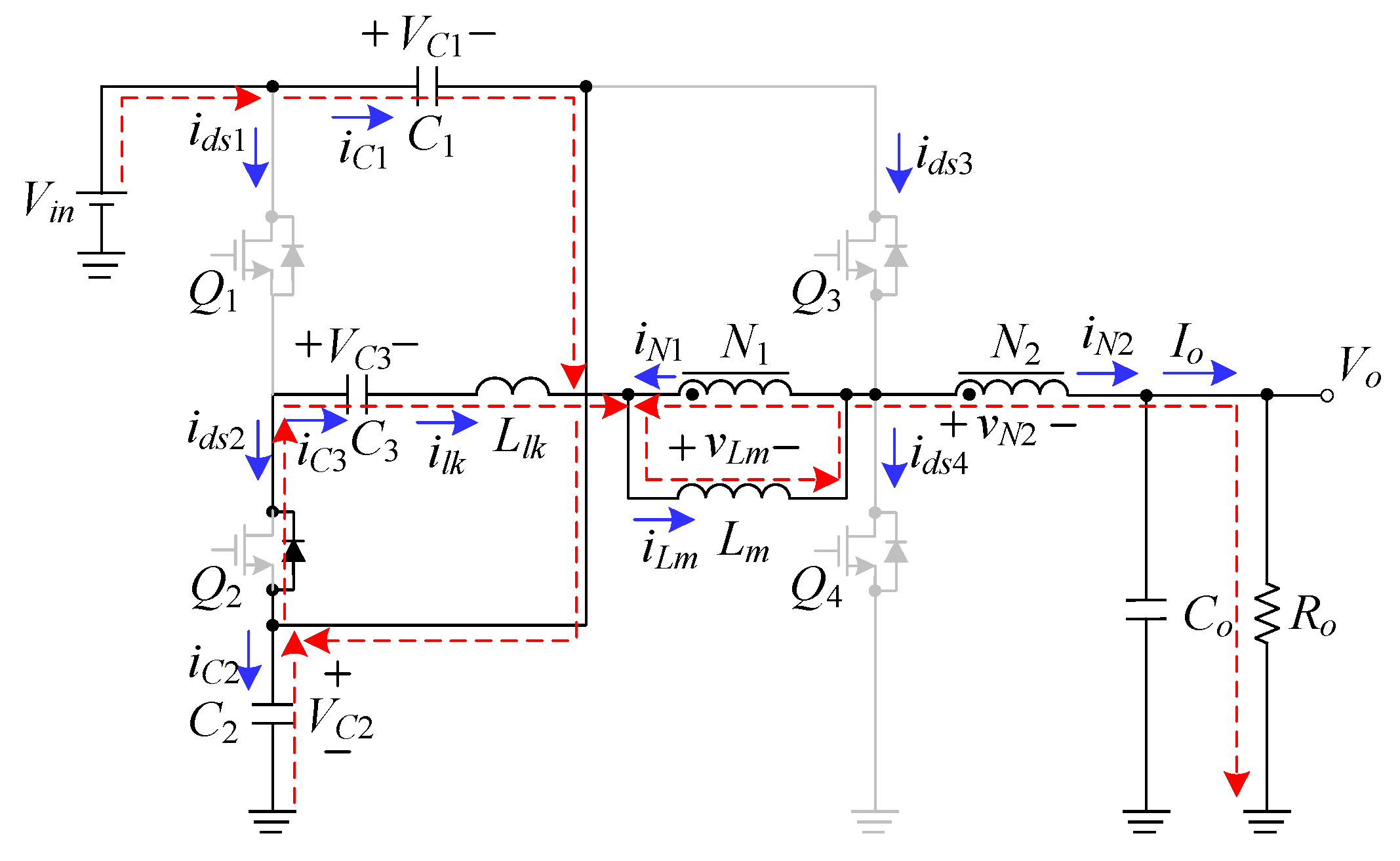

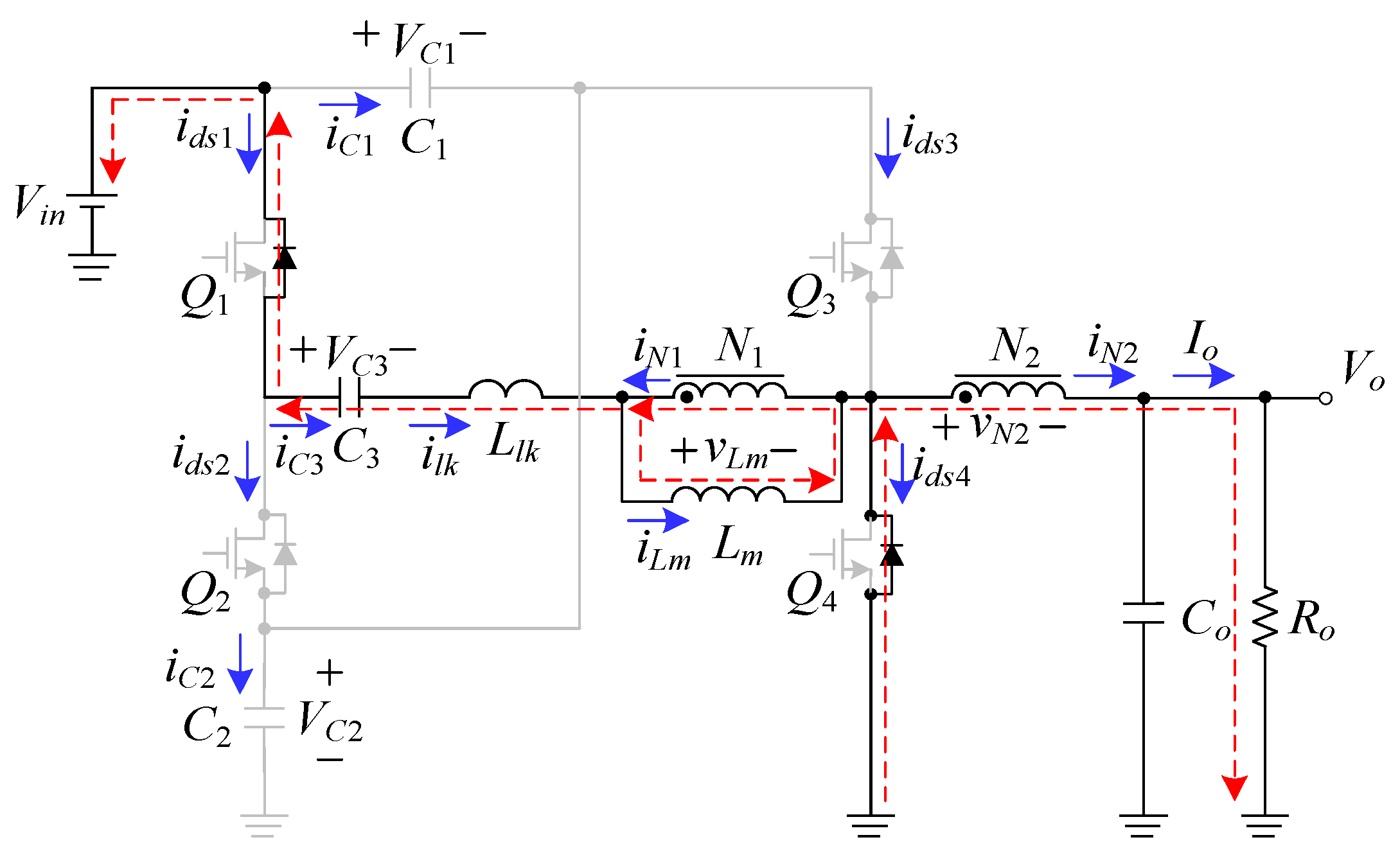

2.1.3. State 3: [t2 ≤ t ≤ t3]

2.1.4. State 4: [t3 ≤ t ≤ t4]

2.1.5. State 5: [t4 ≤ t ≤ t5]

2.1.6. State 6: [t5 ≤ t ≤ t0 + Ts]

2.2. Voltage Conversion Ratio

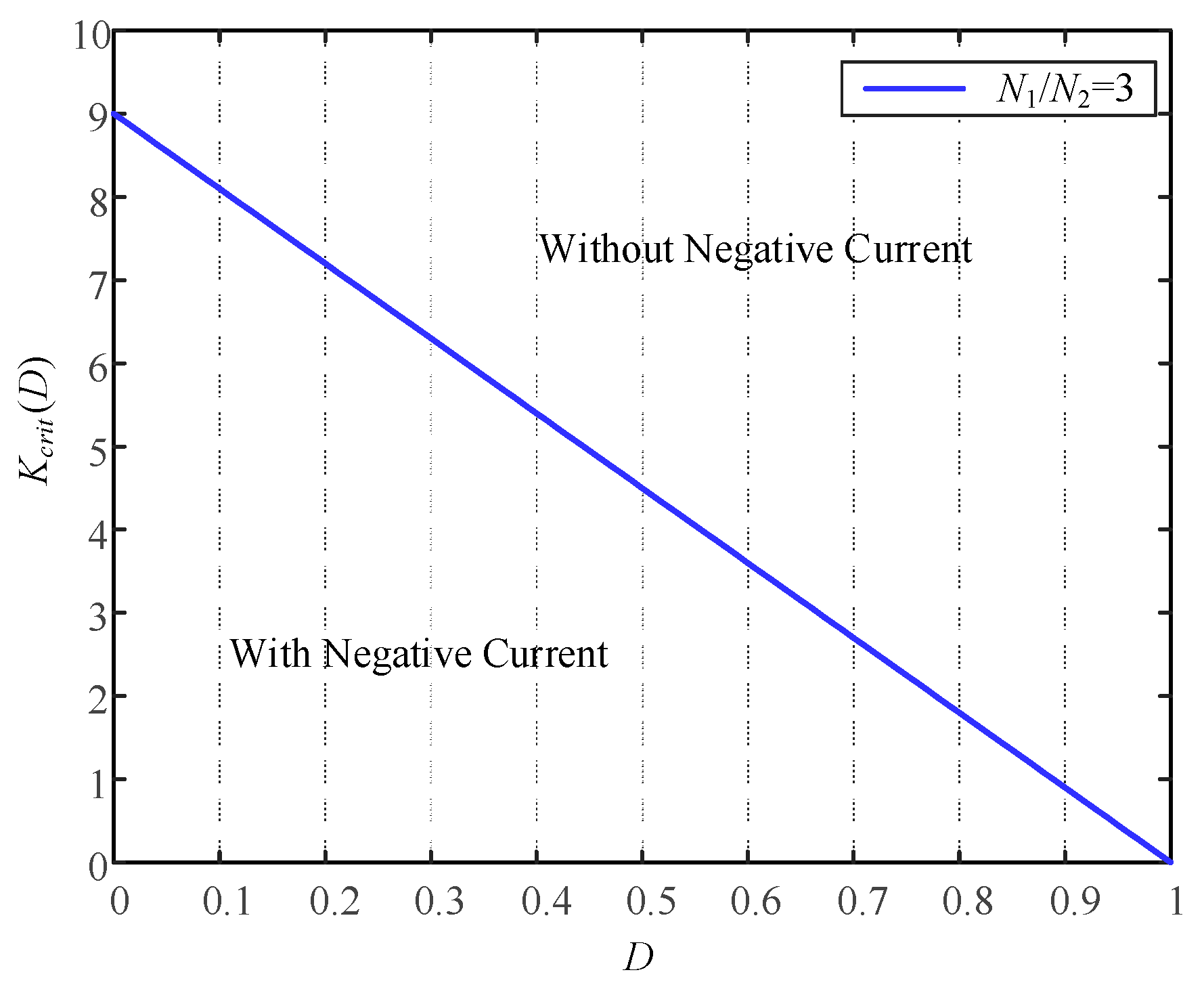

2.3. Boundary Condition Analysis

2.4. Comparison of Proposed Circuit with Existing Circuits

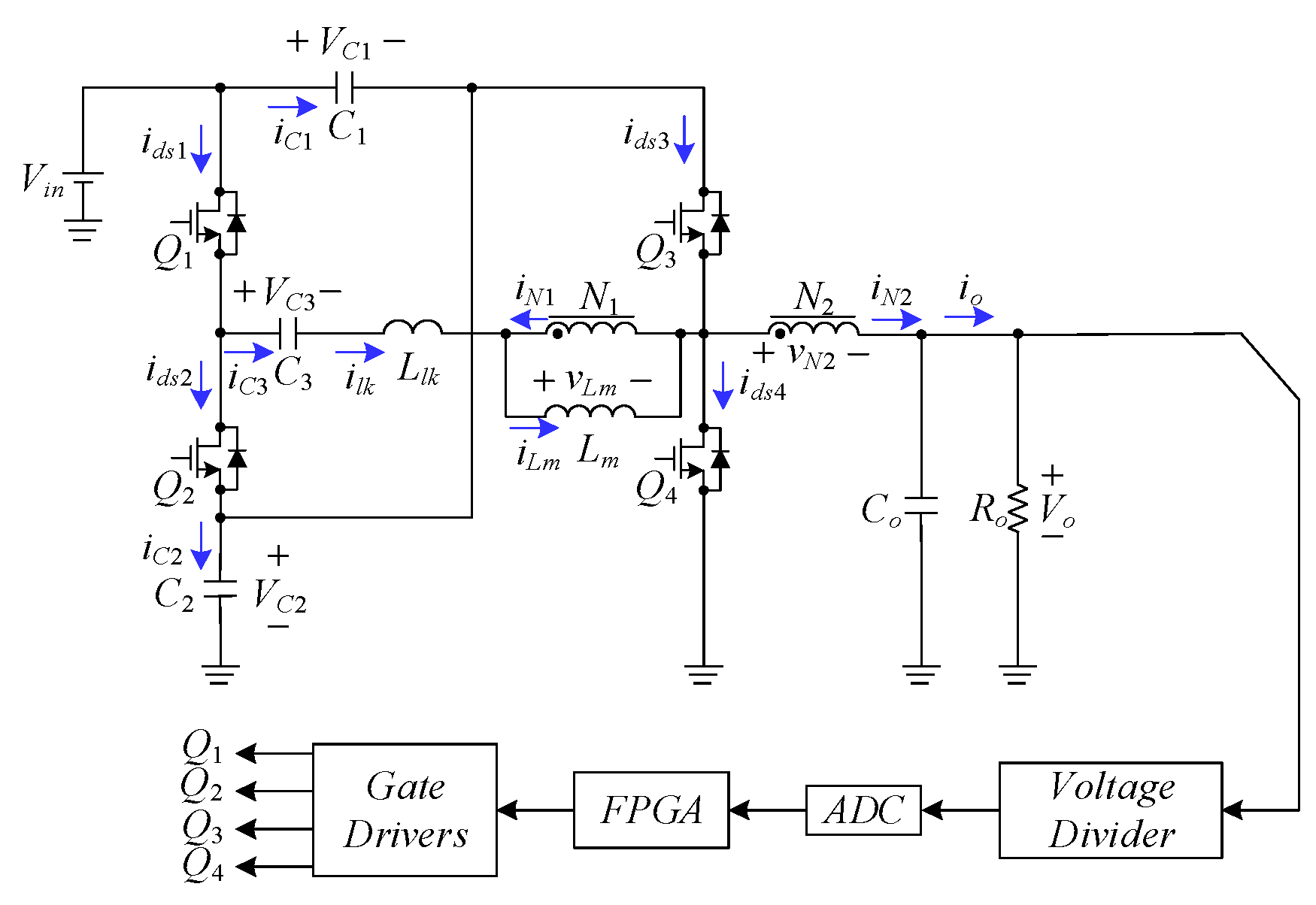

3. Control Strategy

How to Set Switching Frequency from FPGA and How to Get DPWM Signal

4. Design Considerations

4.1. Design of Coupling Inductor

4.1.1. Design of Turns Ratio

4.1.2. Design of Magnetizing Inductance

4.2. Component Specifications

5. Experimental Results

5.1. Test Bench for Measuring Efficiency and Waveforms

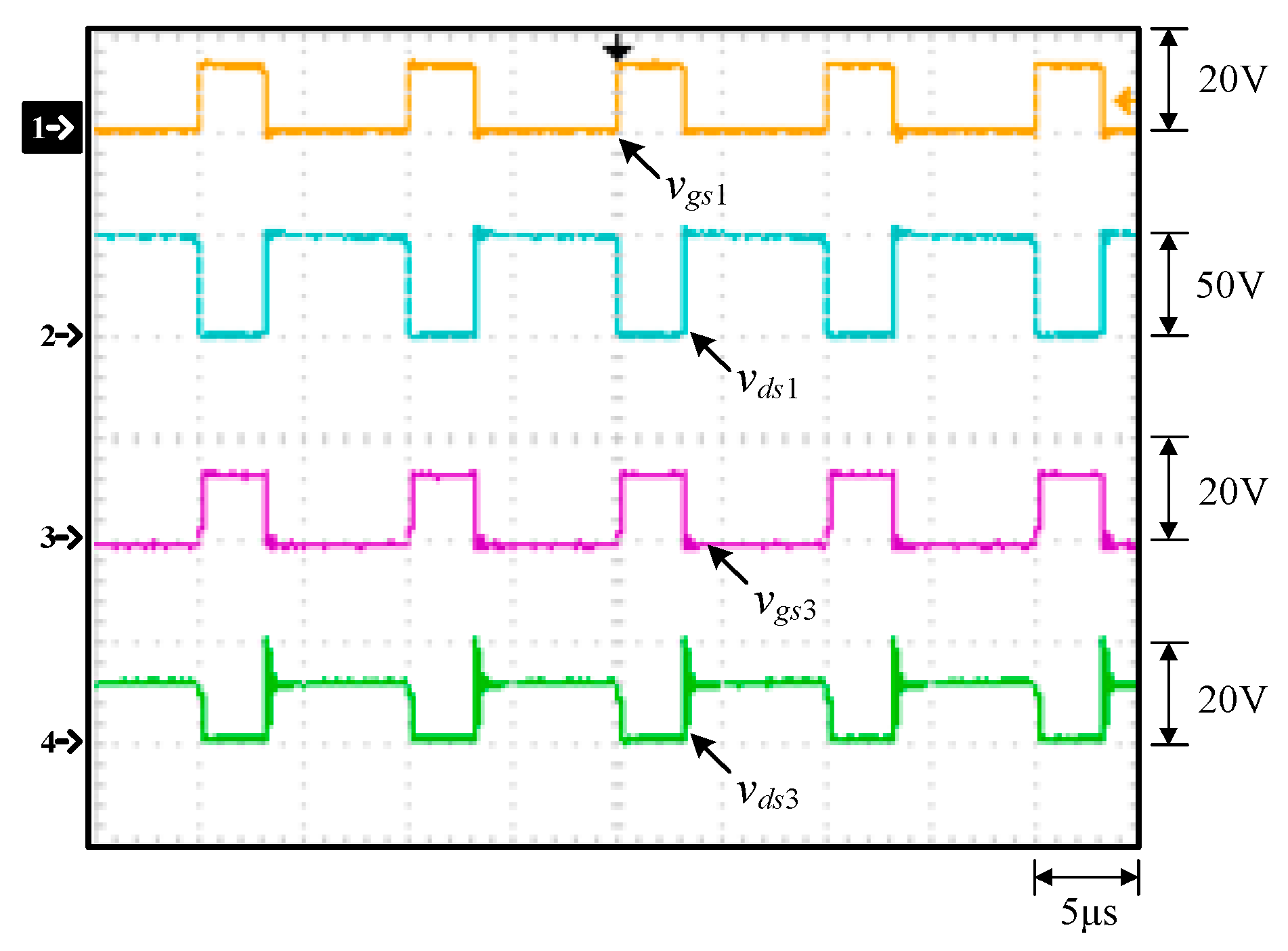

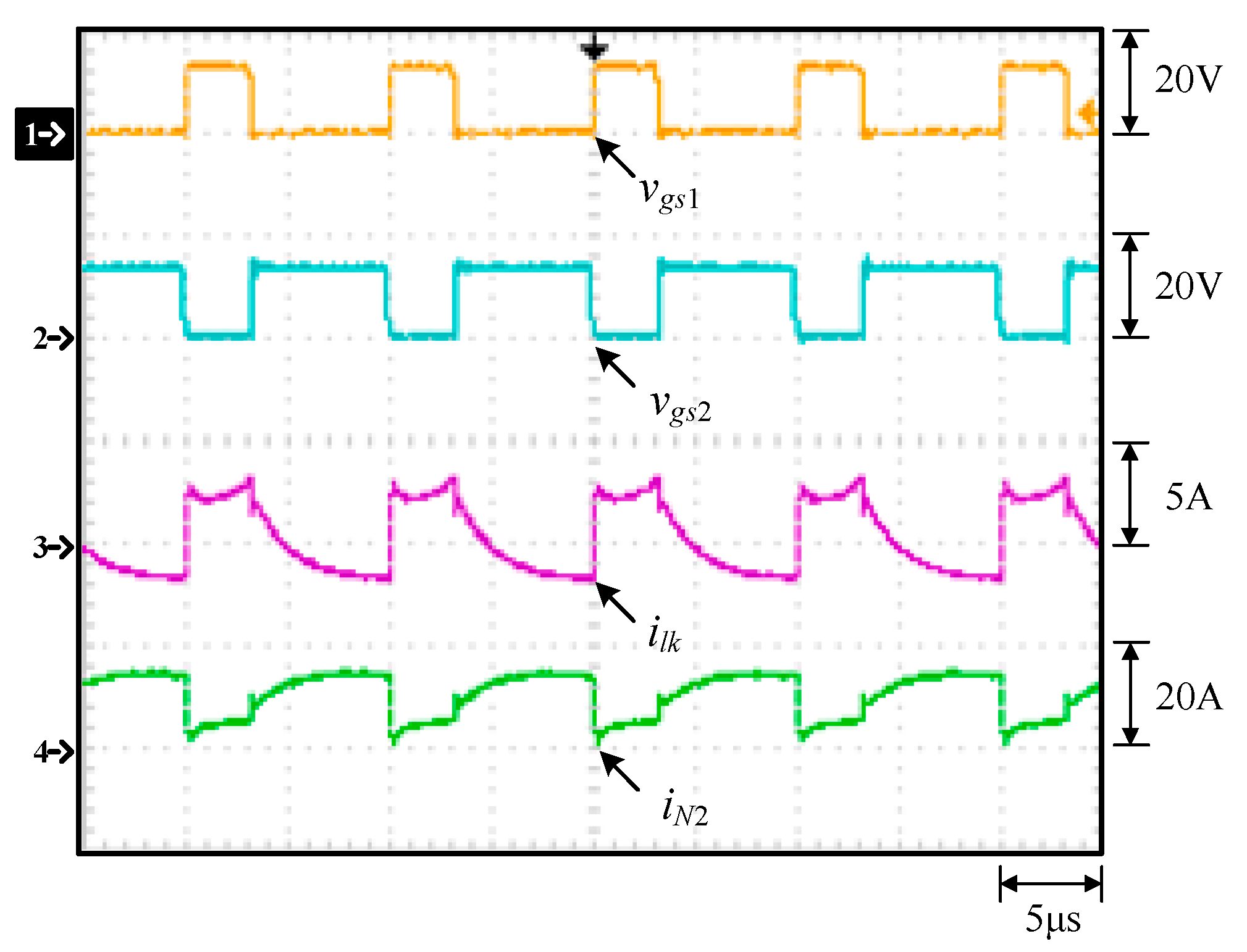

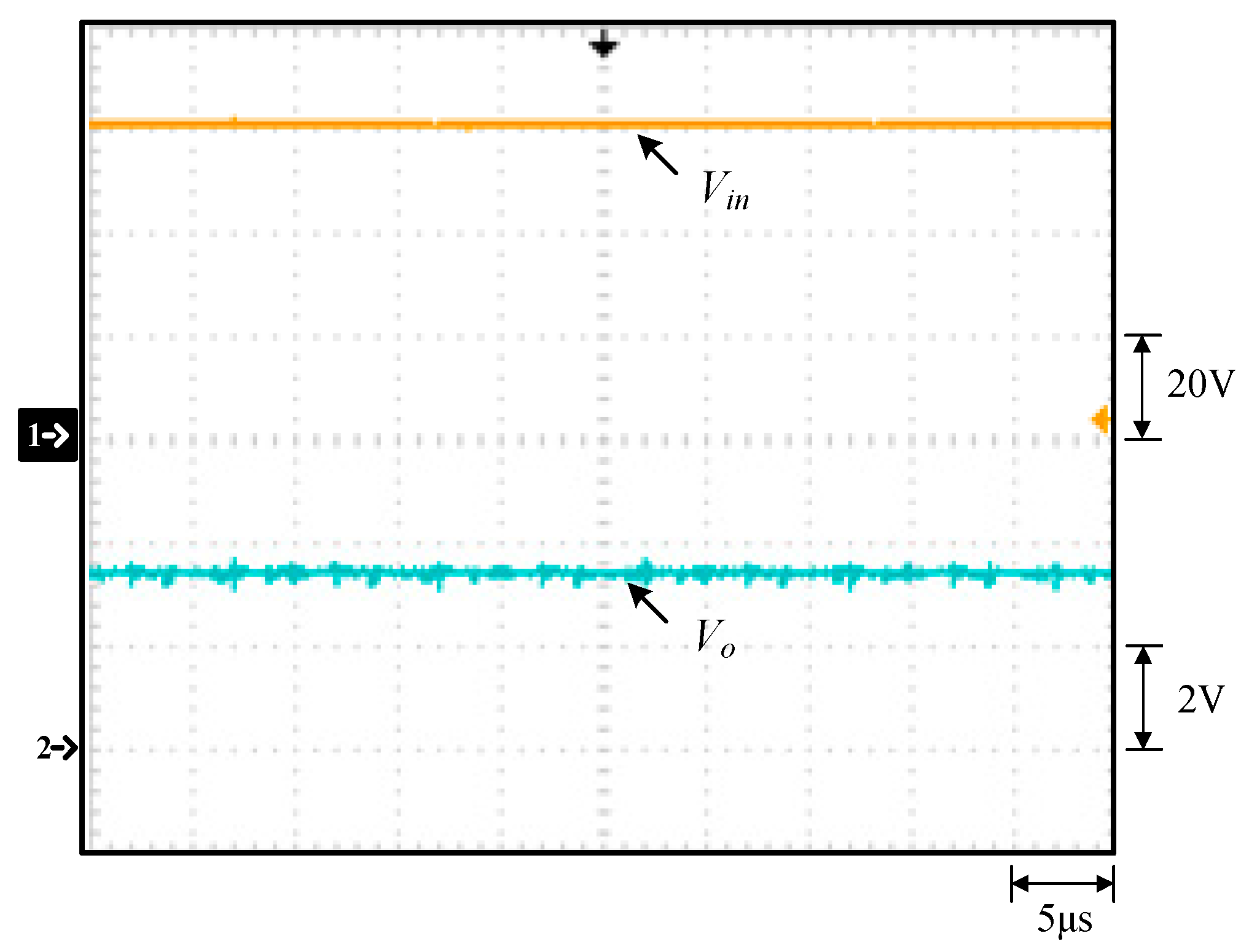

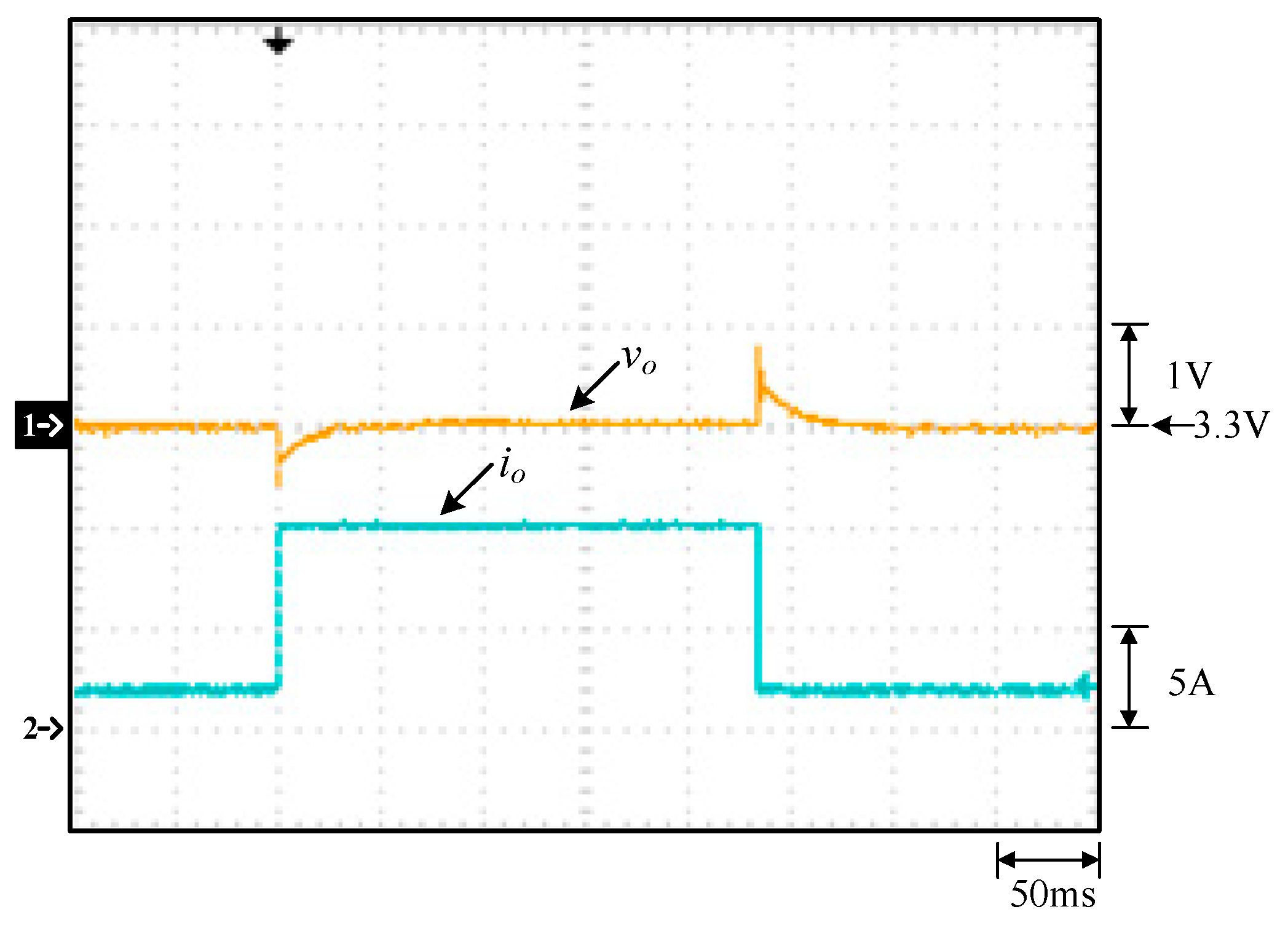

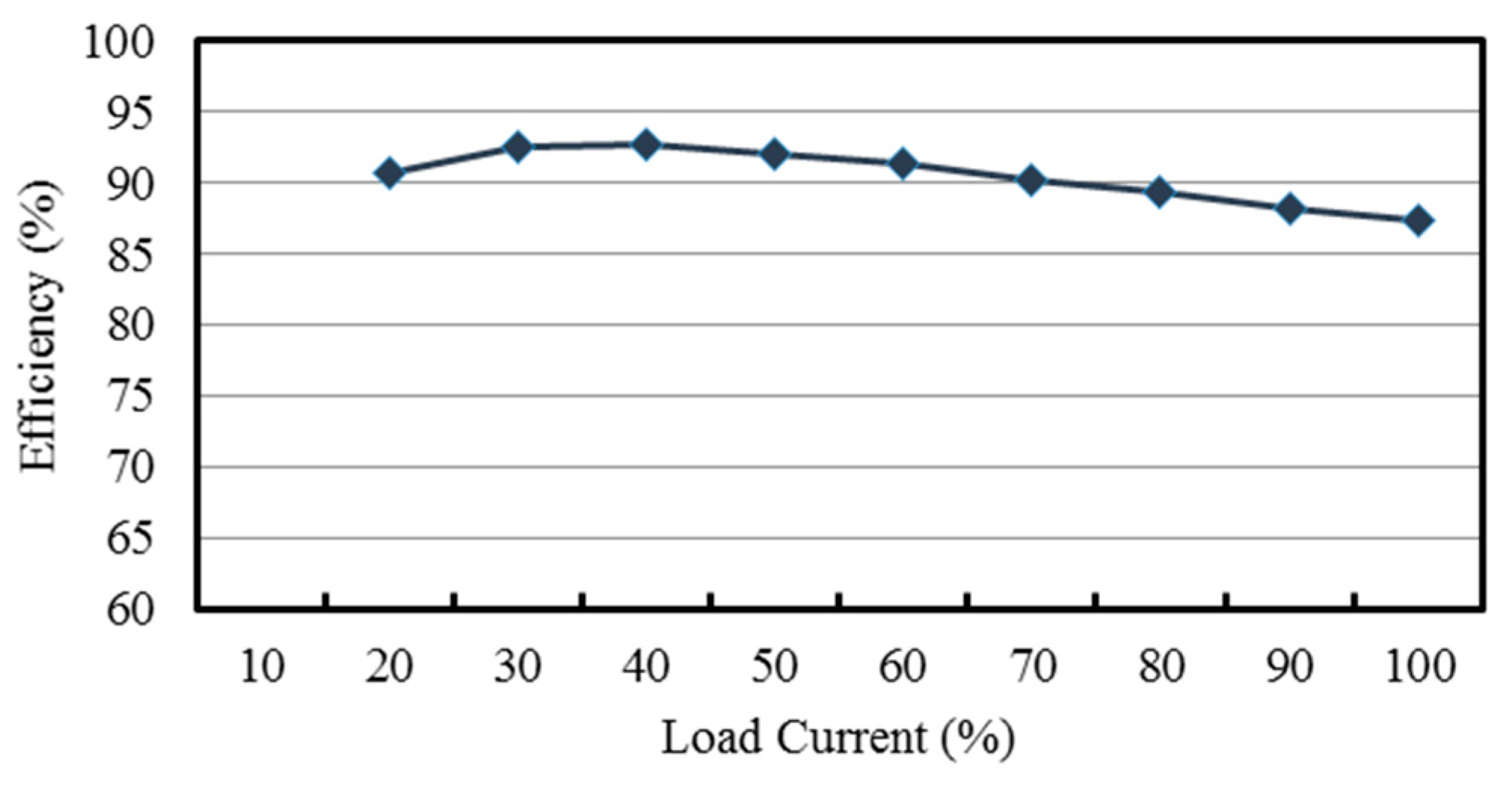

5.2. Measured Waveforms and Efficiency

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Yang, Z.; Ye, S.; Liu, Y.F. A new transformer-based non-isolated topology optimized for VRM application. In Proceedings of the 2005 IEEE 36th Power Electronics Specialists Conference, Recife, Brazil, 12–16 June 2005; pp. 447–453. [Google Scholar]

- Miyawaki, S.; Itoh, J.I.; Iwaya, K. A high-efficiency isolated DC/DC converter using series connection on the secondary side. In Proceedings of the 2010 International Power Electronics Conference-ECCE Asia (IPEC-Sapporo 2010), Sapporo, Japan, 21–24 June 2010; pp. 620–625. [Google Scholar]

- Uno, M. High step-down converter integrating switched capacitor converter and PWM synchronous buck converter. In Proceedings of the 35th International Telecommunications Energy Conference, Hamburg, Germany, 13–17 October 2013; pp. 1–6. [Google Scholar]

- Xiong, S.; Wong, S.C.; Tan, S.C.; Chi, K.T. A family of exponential step-down switched-capacitor converters and their applications in two-stage converters. IEEE Trans. Power Electron. 2014, 29, 1870–1880. [Google Scholar] [CrossRef]

- Xiong, S.; Huang, Y.; Tan, S.C.; Hui, S.Y. Morphing switched-capacitor step-down dc-dc converters with variable conversion ratio. In Proceedings of the 2016 IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 20–24 March 2016; pp. 1888–1893. [Google Scholar]

- Ruan, X.; Li, B.; Chen, Q.; Tan, S.C.; Chi, K.T. Fundamental considerations of three-level dc-dc converters: Topologies, analyses, and control. IEEE Trans. Circuits Syst. 2008, 55, 3733–3743. [Google Scholar] [CrossRef]

- Ye, S.; Eberle, W.; Liu, Y.F. A novel non-isolated full bridge topology for VRM applications. IEEE Trans. Power Electron. 2008, 23, 427–437. [Google Scholar] [CrossRef]

- Li, P.; Li, W.; Zhao, Y.; Yang, H.; He, X. ZVS three-level phase-shift high step-down dc-dc converter with two transformers. In Proceedings of the 14th European Conference on Power Electronics and Applications, Birmingham, UK, 30 August–1 September 2011; pp. 1–10. [Google Scholar]

- Lin, B.R.; Chen, H.R. Soft switching dc-dc converter with high voltage conversion ratio and less current ripple. Int. J. Circuit Theory Appl. 2017, 45, 338–353. [Google Scholar] [CrossRef]

- Rodrigues, J.P.; Mussa, S.A.; Heldwein, M.L.; Perin, A.J. Three-level ZVS active clamping PWM for the dc-dc buck converter. IEEE Trans. Power Electron. 2009, 24, 2249–2258. [Google Scholar] [CrossRef]

- Xu, P.; Wei, J.; Lee, F.C. The active couple-buck converter-A novel high efficiency voltage regulator modules. In Proceedings of the APEC 2001. Sixteenth Annual IEEE Applied Power Electronics Conference and Exposition, Anaheim, CA, USA, 4–8 March 2001; Volume 1, pp. 252–257. [Google Scholar]

- Yao, K.; Ye, M.; Xu, M.; Lee, F.C. Tapped-inductor buck converter for high-step-down dc-dc conversion. IEEE Trans. Power Electron. 2005, 20, 775–780. [Google Scholar] [CrossRef]

- Cheng, K.W.E. Tapped inductor for switched-mode power converters. In Proceedings of the 2nd International Conference on Power Electronics Systems and Applications, Hong Kong, China, 12–14 November 2006; pp. 14–20. [Google Scholar]

- Nishijima, K.; Ishida, D.; Harada, K.; Nabeshima, T.; Sato, T.; Nakano, T. A novel two-phase buck converter with two cores and four windings. In Proceedings of the INTELEC 07-29th International Telecommunications Energy Conference, Rome, Italy, 30 September–4 October 2007; pp. 861–866. [Google Scholar]

- Grant, D.A.; Darroman, Y.; Suter, J. Synthesis of tapped-inductor switched-mode converters. IEEE Trans. Power Electron. 2007, 22, 1964–1969. [Google Scholar] [CrossRef]

- Kim, S.H.; Cha, H.; Ahmed, H.F.; Choi, B.; Kim, H.G. Isolated double step-down dc-dc converter with improved ZVS range and no transformer saturation problem. IEEE Trans. Power Electron. 2017, 32, 1792–1804. [Google Scholar] [CrossRef]

- Tsai, C.T.; Shen, C.L. Interleaved soft-switching coupled-buck converter with active-clamp circuits. In Proceedings of the International Conference on Power Electronics and Drive Systems (PEDS), Taipei, Taiwan, 2–5 November 2009; pp. 1113–1118. [Google Scholar]

- Lee, S.S. Step-down converter with efficient ZVS operation with load variation. IEEE Trans. Power Electron. 2014, 61, 591–597. [Google Scholar] [CrossRef]

- Cheshmdehmam, D.; Adib, E.; Farzanehfard, H. Structure improvement of active-clamp to achieve high step-down conversion. In Proceedings of the 24th Iranian Conference on Electrical Engineering (ICEE), Shiraz, Fars, Iran, 10–12 May 2016; pp. 670–675. [Google Scholar]

- Do, H.L. Zero-voltage-switching synchronous buck converter with a coupled inductor. IEEE Trans. Power Electron. 2011, 58, 3440–3447. [Google Scholar] [CrossRef]

- Hwu, K.I.; Jiang, W.Z.; Yau, Y.T. Ultra high step-down converter. In Proceedings of the 2014 International Power Electronics Conference-ECCE ASIA-IPEC-Hiroshima 2014, Hiroshima, Japan, 18–21 May 2014; pp. 3392–3396. [Google Scholar]

- Wai, R.J.; Liaw, J.J. High-efficiency step-down converter via coupled inductor. In Proceedings of the 2016 IEEE 8th International Power Electronics and Motion Control Conference (IPEMC 2016-ECCE Asia), Hefei, China, 22–25 May 2016; pp. 1184–1189. [Google Scholar]

- Yau, Y.T.; Jiang, W.Z.; Hwu, K.I. Ultrahigh step-down converter with wide input voltage range based on topology exchange. IEEE Trans. Power Electron. 2017, 32, 5341–5364. [Google Scholar] [CrossRef]

- Yau, Y.T.; Jiang, W.Z.; Hwu, K.I. Bidirectional operation of high step-down converter. IEEE Trans. Power Electron. 2015, 30, 6829–6844. [Google Scholar] [CrossRef]

- Lo, Y.K.; Lin, C.Y.; Lin, J.Y.; Chiu, H.J. Analysis and design of a two-transformer active-clamping forward converter with parallel-connected current doubler rectifiers. Int. J. Circuit Theory Appl. 2011, 39, 501–514. [Google Scholar] [CrossRef]

- Tibola, G.; Duarte, J.L.; Blinov, A. Multi-cell dc-dc converter with high step-down voltage ratio. In Proceedings of the 2015 IEEE Energy Conversion Congress and Exposition (ECCE), Montreal, QB, Canada, 20–24 September 2015; pp. 2010–2016. [Google Scholar]

- Wu, H.; Lu, Y.; Chen, L.; Xu, P.; Xiao, X.; Xing, Y. High step up/step-down non-isolated BDC with built-in dc-transformer for energy storage systems. IET Power Electron. 2016, 9, 2571–2579. [Google Scholar] [CrossRef]

- Hwu, K.I.; Jiang, W.Z. Nonisolated coupled-inductor-based high-step-down converter with zero DC magnetizing inductance current and non-pulsating output current. IEEE Trans. Power Electron. 2016, 31, 4362–4377. [Google Scholar] [CrossRef]

| Converter | Voltage Conversion Ratio | Component Number | Switch Voltage Stress | Output Inductor |

|---|---|---|---|---|

| Proposed | 9 | No | ||

| [24] | 8 | No | ||

| [28] | 8 | Yes |

| Parameters | Specifications |

|---|---|

| Converter Operating Mode | CCM |

| Input Voltage (Vin) | 60 V |

| Rated Output Voltage (Vo,rated) | 3.3 V |

| Rated Output Current (Io,rated)/Power (Po,rated) | 10 A/33 W |

| Minimum Output Current (Io,min)/Power (Po,min) | 2 A/6.6 W |

| Switching Frequency (fs)/Period (Ts) | 100 kHz/10 μs |

| Parameters | Specifications |

|---|---|

| Product name | PQ20/16-3C90 |

| Inductor constant (AL) | 3250 nH/N2 ± 25% |

| Saturation flux density (Bs) | 380 mT |

| Residual flux density (Br) | 60 mT |

| Effective area (Ae) | 0.619 cm2 |

| Effective volume (Ve) | 2.33 cm3 |

| Effective magnetic length (le) | 3.76 cm |

| Components | Specifications | |

|---|---|---|

| MOSFET | Q1, Q2 | STP120NF10 |

| Q3, Q4 | IRF3205Z | |

| Energy-TransferringCapacitor | C1 | 220 μF/100 V Rubycon Electrolytic Capacitor |

| C2, C3 | 680 μF/35 V Rubycon Electrolytic Capacitor | |

| Capacitor | Co | 1000 μF/16 V Rubycon Electrolytic Capacitor |

| Coupled Inductor | Core: PQ20/16-3C90 N = 1/3, Lm = 81.6 μH, Llk = 0.82 μH | |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hwu, K.-I.; Jiang, W.-Z.; Tu, H.-H. Improvement in Voltage Conversion Ratio of Ultrahigh Step-Down Converter. Energies 2019, 12, 3896. https://doi.org/10.3390/en12203896

Hwu K-I, Jiang W-Z, Tu H-H. Improvement in Voltage Conversion Ratio of Ultrahigh Step-Down Converter. Energies. 2019; 12(20):3896. https://doi.org/10.3390/en12203896

Chicago/Turabian StyleHwu, Kuo-Ing, Wen-Zhuang Jiang, and Hsiang-Hao Tu. 2019. "Improvement in Voltage Conversion Ratio of Ultrahigh Step-Down Converter" Energies 12, no. 20: 3896. https://doi.org/10.3390/en12203896