1. Introduction

A hardware in the loop (HIL) simulation is the implementation of a system model in embedded hardware, which represents part of a real system. The main requirement of HIL simulation is that it has to be in real-time [

1]. HIL simulation plays a significant role in the development of technology for many applications, presenting advantages such as the short time to market for new products; low cost of prototyping; and risk reduction of damaging test equipment and, more importantly, of harming people during testing.

There are commercial HIL real-time simulators available, such as RTDS

® (Winnipeg, MB, Canada), OPAL-RT

® (Montreal, QC, Canada), Typhoon

® (Somerville, MA, USA), and dSPACE

® (Paderborn, Germany), to name a few. The software used by these simulators allows the user to implement the system through a graphical interface; these types of equipment are used for the simulation of complex models and are tools that help designers and engineers all over the world. A review of the state-of-the-art of Real-Time Simulation (RTS) technologies, both hardware and software, is presented in [

2]. Many examples of the use of this technology can be found in the literature, including simulating power electronics converters. In [

3], the simulation of a Voltage Source Converter (VSC), used in a High Voltage Direct Current (HVDC) system for distributed generation and power quality regulation, is presented. In [

4], it is used to test a new sliding mode controller for a standalone system based on photovoltaic (PV) generation. In [

5], it is used for evaluating modular multilevel converters. Additionally, in [

6], the authors propose an ultralow latency platform for the RTS, which can be used for complex power electronics systems and, as a case study for this particular platform, a driver for a Permanent Magnet Synchronous Generator (PMSG) is simulated. As shown in these references, RTS is employed to test the controller used in power electronics converters and all simulations use a commercial HIL system.

A drawback of these products is their high cost, which can amount to tens of thousands of dollars. As a result, many universities or research centers cannot afford the acquisition of this kind of equipment. Due to this issue, some researchers have developed ad-hoc solutions using low-cost hardware.

For research purposes, three types of hardware are mainly used to achieve RTS: Digital Signal Processors (DSP), Graphic Processing Units (GPU), and Field-Programmable Gate Arrays (FPGA). At present, FPGA is the most used hardware for RTS [

7]. The use of FPGA for HIL testing of power converters can be found in the references, such as [

8,

9,

10,

11,

12,

13,

14]. This is due to its inherent characteristic of parallel processing, which allows the fast resolution of many equations simultaneously, with short times of integration, in the order of tens of nanoseconds.

Often, the preferred language for the implementation of the system model is Very High-Speed Integrated Circuit Hardware Description Language (VHDL). This language is the best option when the objective is to minimize the FPGA resources and allows the time step to be minimized. However, the use of VHDL requires an expert designer, capable of optimizing the capabilities and the implementation of a proper FPGA application. Some FPGA manufacturers are beginning to offer a more user-friendly Integrated Development Environment (IDE) tool for their FPGA. These IDEs permit the development of FPGA applications using high-level programming languages such as C. In addition, some manufacturers use third-party software, such as MATLAB or LabVIEW, for FPGA applications [

15,

16]. Some authors have proposed the fast development of power electronics models for HIL simulations using these programs. In [

17], the authors develop a new RTS method to test nonlinear control techniques and a methodology to implement the RTS is described, but it is based in a Digital Signal Processor (DSP), which is slower than an FPGA. In [

18], the authors propose a methodology for the development of a fast HIL simulation based in MATLAB, but it includes just a small part of the work and is not detailed enough. In [

19], the authors suggest fast HIL development based in MATLAB; however, the methodology is only for the design of PV converters. In [

20], a high-performance real-time simulator for power electronics based in a novel massively parallel computational engine implemented in low-cost FPGA hardware using VHDL is presented, but there is not enough detail in the implementation. In [

21], the HIL implementation of a validation system for an energy management system used in microgrids is presented. This HIL simulation is performed on a PC and has an overall time step of 100 ms, which is slower than the one reached using an FPGA. As a major advantage, the use of a PC means a lower implementation cost.

The company National Instruments (NI) offers reconfigurable industrial controllers, known as Reconfigurable Input Output (RIO) controllers. This platform has huge potential for the development of control systems for power electronics applications and for the development of HIL systems. It is based on an FPGA combined with a microprocessor, although recently, RIO systems were implemented using System on Chip (SoC) technology, which has been demonstrated to work properly in industrial environments.

LabVIEW is the name of the generic NI software development tool. There is a specific module for developing FPGA applications: the LabVIEW FPGA module. It facilitates the generation of FPGA applications using a graphical language that helps non-expert users to create complex and efficient FPGA applications [

22].

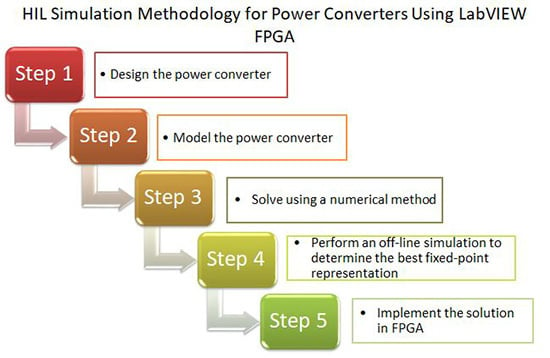

In this paper, a step-by-step methodology for HIL power converter simulation using the LabVIEW FPGA module is shown. The main difference between this approach and those reported in the literature is that, in the latter, the methodologies used to perform this type of simulation are not clearly explained or do not include enough details for implementation; the advantage of the proposal is that it employs the pipelined technique of LabVIEW and results in a small time step. This methodology is intended to be simple, in order to allow researchers with no experience in languages such as VHDL for RTS to carry out HIL simulations with a reduced cost compared to other tools, but with an accuracy high enough to obtain an appropriate real converter model. In the proposal, LabVIEW is used to allow relatively easy and fast implementation. The methodology consists of five steps: The first step is the design of the power converter; in the second one, the converter model is obtained; during the third step, the model is solved using a numerical method; the fourth step consists of programming an off-line simulation of the model using fixed-point representation; and finally, implementation of the numerical method in the FPGA is conducted. In order to verify the results, a comparison of simulation software such as PSIM, the HIL simulation proposed, and a real converter was carried out using a buck converter and a three-phase voltage source inverter (VSI) as a case study.

3. Results

In order to verify the proposed methodology, a real-time HIL simulation was implemented and compared against an off-line simulation using PSIM as a reference simulator and also against a real converter.

Table 6 indicates the measured parameters of the buck converter.

The hardware used for the RTS is implemented in an NI cRIO-9067 that includes an FPGA Zynq-7020 using a 40 MHz clock. In order to convert the RTS into an HIL simulation, the addition of two modules is necessary: one is a digital I/O (NI9401) used for acquiring the control signals and the other is a DAC module (NI6292) used to generate the output signals. In

Figure 13, the front panel of the main VI program for the buck converter is shown. It can be noticed that the loop rate is 6 clock cycles, so the time required to find every solution of the numerical method, with a 40 MHz clock, is 150 ns. The same parameters, which are shown in

Figure 7b for the off-line simulation, were used to perform the real-time simulation.

In

Figure 14 and

Figure 15, the result of

iL and

vO for the real buck converter, the proposed methodology, and the PSIM simulation can be observed. It can be seen that the signal obtained from the converter and the signal obtained from the Real-Time simulation have a similar behavior, such as the shape,

ΔiL or

ΔvO, and steady-state value.

In

Table 7, the Mean Absolute Error (MAE) from the real converter signals against the Real-Time simulated signals and PSIM waveforms is calculated. These results show that RTS is very accurate compared with a real buck converter and is similar to the off-line simulation by using PSIM with the same parameters.

In

Figure 16, the inductor current per phase for the three-phase VSI can be seen. For this converter, the time required to solve the model is 750 ns due to the model’s complexity.

As mentioned above, in order to make the RTS an HIL simulation, the calculated output signals can be externally monitored by means of the DAC module outputs.

Figure 17 shows an oscilloscope image comparing the signals obtained from the real buck converter and the HIL simulation.

Figure 18 is a zoom under a steady-state, in which a time delay of 4 μs between the real converter and the HIL simulation can be observed, which corresponds to the conversion time of the DAC converter used in this test.

In

Figure 19, the response of the real three-phase VSI and HIL simulation can be observed. The test was conducted under a modulation index change (0.5 to 0.9). In

Figure 20, a time zoom is shown; as can be noticed, the behavior of the HIL simulation is close to the real currents (

ia and

ib).

These results show that the methodology proposed in this article can be used for a real-time HIL simulation of power converters. This may help to produce a fast and cost-effective test cycle for the development of new controllers. In addition, the proposed methodology for real-time HIL simulation using LabVIEW can be used by students and researchers with basic knowledge regarding numerical methods and LabVIEW programming. The paper is focused on providing an understandable methodology for people with no experience in HIL simulation and text-based languages. The proposal is very easy to follow due to its simplicity; however, accurate results can be obtained.

Another advantage of the proposal is the use of low-cost FPGA hardware (

Table 8). The HIL simulation was tested using the CompactRIO platform, which certainly has a lower cost compared to other HIL platforms. However, a MyRIO board could also be employed to obtain similar results; the difference would be the DAC converter included, which is slower than the hardware available in the CompactRIO. In the case of the MyRIO board, switching frequencies should be limited to 20 kHz or below.

An additional advantage is the creation of SubVI that can be shared between the community of scientists and researchers around the world and can enrich this work with other contributions. Once a SubVI is created, it can be used as many times as desired with a simple copy and paste operation.

4. Conclusions

In this paper, an understandable methodology for users with no experience in HIL simulation is presented, in order to simulate power converters using a real-time HIL technique. This methodology is based on NI hardware and software, allowing any non-VHDL expert to optimize power electronics converters and their controllers. Besides the simplicity of the proposal, accurate results are obtained.

Using the hardware and following the detailed methodology proposed here, a good HIL simulation for dc/dc converters and three-phase inverters was obtained, the time step of 150 ns for a buck converter and 750 ns for a three-phase VSI was achieved, and both cases used the main clock of 40 MHz. The experimental result and the measured error (

Table 7) allowed us to establish that the HIL simulation developed with the use of the proposed methodology is accurate and close to the real converters, so the HIL simulator can be employed satisfactorily by using LabVIEW.

The advantages provided by the proposed method are that the simulation is more realistic since it can be used to evaluate a controller in real-time. Additionally, it is safe for components and people, and the cost of controller implementation and testing, and the development time are reduced. The proposed methodology facilitates understanding of the programming process and it is also an easy and cost-effective way to validate power electronics controllers.

As a drawback of the proposed methodology and tool, it should be mentioned that the modeling technique used would be complex for converters with many switches, which determines the number of equations. A higher number of equations implies more programming, greater hardware resources use, and a long time to calculate a solution. This may mean that the implementation does not fit in the FPGA target and the time step is not short enough to minimize the error presented by the Euler method.

As future work, the connection of more than one digital platform could be made, in order to increase the capacity to simulate more complex systems. Furthermore, a study of different integration methods could be pursued, in order to compare them and verify their performance. Additionally, a bank of power converter models in LabVIEW software may be generated, which could be shared between researchers and students.